# Laser Crystallization and Dopant Activation of a-Si:H Carrier-Selective Layer in TOPCon Si Solar Cells

George C. Wilkes , *Graduate Student Member, IEEE*, Ajay D. Upadhyaya, *Member, IEEE*, Ajeet Rohatgi, *Life Fellow, IEEE*, and Mool C. Gupta, *Fellow, IEEE*

Abstract—Herein, we present a pulsed-laser processing method for crystallization and dopant activation of a highly n-doped amorphous silicon (a-Si:H) carrier-selective layer in a tunnel oxide passivated contact (TOPCon) Si solar cell structure. The laser method provides enhanced conductivity and implied open circuit voltage while reducing emitter saturation current density and surface heating, as opposed to conventional high-temperature furnace annealing of the bulk Si wafer with a TOPCon structure. We identify an appropriate laser wavelength, fluence, and layer thickness using modeling and simulations. Raman and Hall effect measurements demonstrate increased crystallinity and dopant activation, whereas photoconductive decay shows enhanced surface and interface passivation quality. Additionally, we examine the role of subsequent SiN<sub>x</sub> deposition on further improving the passivation of laserprocessed TOPCon layers to achieve a 5.9 k $\Omega$ /sq film sheet resistance, 2 ms effective carrier lifetime, 718 mV implied open-circuit voltage (iV<sub>OC</sub>), and 8.6 fA/cm<sup>2</sup> one-side recombination current density  $(J_0)$  with the potential for further passivation improvement via laser process and a-Si layer thickness optimization.

*Index Terms*—Carrier-selective contact, dopant activation, laser annealing, laser processing, silicon crystallization, surface passivation, tunnel oxide passivated contact (TOPCon).

# I. INTRODUCTION

ARRIER recombination in silicon solar cells can be greatly reduced by using passivating and carrier-selective interlayers between silicon and its metal electrodes to enhance cell efficiency. Highly doped amorphous silicon (a-Si:H), well studied as an interlayer in various Si devices, is receiving increasing interest as a carrier-selective layer for high-efficiency Si solar cells [1]–[7]. When coupled with a thin (<2 nm) passivating layer (such as SiO<sub>2</sub>), surface passivation can be achieved without negatively impacting carrier transport. Additionally, tunnel-oxide passivating contacts are one of the few viable methods for eradicating diffusion and metal-contact-induced

Manuscript received April 8, 2020; revised May 28, 2020; accepted June 22, 2020. Date of publication July 9, 2020; date of current version August 20, 2020. This work was supported by the NASA Langley Professor Program and the National Science Foundation (NSF) under Grant ECCS-2005098 and Grant I/UCRC-1338917. (Corresponding author: Mool C. Gupta.)

George C. Wilkes and Mool C. Gupta are with the University of Virginia, Charlottesville, VA 22904 USA (e-mail: gcw5qu@virginia.edu; mgupta@virginia.edu).

Ajay D. Upadhyaya and Ajeet Rohatgi are with the Georgia Institute of Techology, Atlanta, GA 30332 USA (e-mail: ajay.upadhyaya@ece.gatech.edu; ajeet.rohatgi@ece.gatech.edu).

Color versions of one or more of the figures in this article are available online at https://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/JPHOTOV.2020.3006273

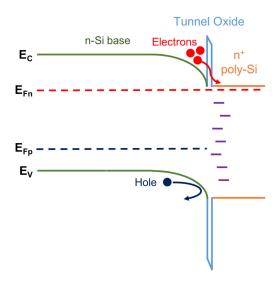

Fig. 1. Energy diagram showing carrier transport.

recombination because they relocate heavily doped diffused regions and metallized contacts outside of the absorbing base. The band alignment of the base, thin passivation layer, and carrier selective layer work together to create a high barrier for one carrier and low barrier for the other, providing carrier selectivity for low minority carrier recombination and efficient majority carrier transport [8], [9]. The energy diagram of this system is shown in Fig. 1.

Typically, the highly doped a-Si or nanocrystalline silicon layer is deposited via plasma-enhanced chemical vapor deposition (PECVD) or low-pressure chemical vapor deposition (LPCVD) at low temperatures (between 200° and 600 °C) and a subsequent 30-min high-temperature anneal between 800° and 1000 °C is used to further crystallize the as-deposited layer [1]– [3], [5]–[7], increase structural and electrical stability [2]–[4], [6], [7], activate dopants within the layer [1], [6], [7], reduce short wavelength parasitic absorption by increasing crystallinity [10], and possibly generate pinholes in the interfacial oxide for carrier transport [3], [4]. Amorphous Si can reduce short-circuit current density values by as much as 9 mA/cm<sup>2</sup> for a 100 nm thick layer, which is reduced to 4 mA/cm<sup>2</sup> for poly-Si [10], emphasizing the need for layer crystallization. Dopant activation will decrease the sheet resistance of the poly-Si, enabling a low series resistance for subsequent metallization. However, high-temperature furnace anneals lead to several problems: first, degradation of the tunnel oxide and its interfaces [3]; second, dopant diffusion from the poly-Si into the base which increases Auger recombination; third, incomplete dopant activation in the poly-Si; and finally, degradation of the absorber lifetime due to prolonged high-temperature exposure.

To alleviate these issues and grant further control over the processing, we investigated the use of ultraviolet pulsedlaser annealing to replace the secondary furnace-based hightemperature anneal. Laser-based solar cell manufacturing has gained increased interest in recent years, allowing for easy adoption [11], [12]. Pulsed-laser annealing allows for selective control over dopant activation and crystallization of the poly-Si layer while preventing oxide degradation, absorber degradation, and excessive diffusion. This is due to the short laser pulse (25 ns), which can activate dopants and crystallize the poly-Si in nanoseconds, and the shallow absorption depth (10 nm for Si) enabling the processing to only affect the desired layer. Coupled with the low thermal diffusivity of amorphous (0.10 cm<sup>2</sup>/s) and polycrystalline silicon (0.14 cm<sup>2</sup>/s) when compared to crystalline silicon (0.90 cm<sup>2</sup>/s) [13], it is possible to reach the high temperatures required for activation and crystallization while preventing tunnel oxide break-up at 900 °C [14] under nanosecond pulsed-laser heating [15]. This gives us a unique advantage in preventing oxide break-up while annealing the poly-Si layer.

Herein, we investigate the change in passivation, crystallization, and dopant concentration of laser-processed a-Si:H, carrierselective passivating contacts, and the impact of subsequent SiN<sub>x</sub> deposition to replace the furnace-based high temperature anneal for tunnel oxide passivated contact (TOPCon) for high efficiency Si solar cells. This work enhances our earlier conference proceeding [16] by providing modeling and simulation results, Raman and Hall effect studies, and improved passivation of a 718 mV implied open circuit voltage. The investigations were carried out with a 355 nm laser wavelength. We also report the results of the effect of passivating layer thickness (12 and 200 nm), as the 355 nm wavelength will have a different impact on these layers given the fixed absorption depth. Due to the short absorption depth ( $\sim$ 10 nm) of the ultraviolet laser wavelength, the temperature of c-Si/SiO<sub>2</sub>/a-Si interface may not be high enough to improve the passivation. Thicker films can be used if a longer wavelength laser is utilized.

#### II. OPTICAL MODELING AND LASER SIMULATION

In order to understand the impact of the laser wavelength and fluence on the absorption and resultant temperature increase in the TOPCon structure, the spectral optical properties of amorphous and crystalline silicon were modeled and the laser-material interaction was simulated to provide a conceptual background for the study.

#### A. Choice of Laser Wavelength From Optical Modeling

The optical properties of amorphous and crystalline silicon were modeled to assess an appropriate wavelength for laser annealing using Essential Macleod optical modeling software. While laser wavelengths can vary greatly, high-power lasers based on Nd:YAG are typically restricted to 1064, 532, 355, and 266 nm wavelengths based on the first, second, third, and fourth

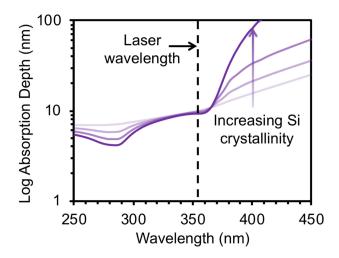

Fig. 2. Log plot of the ultraviolet absorption depth of silicon of various degrees of crystallinity from amorphous to single crystal [17]. The arrow direction indicates the trend of increasing crystallinity. The dashed line indicates the selected laser wavelength, which will have identical absorption regardless of the silicon's degree of crystallinity.

harmonic generation. We looked at the absorption properties of silicon with varying degrees of crystallinity from amorphous to single crystal using data from Sopra SA [17]. Throughout the visible spectrum, the absorption coefficient can shift by an order of magnitude across the aforementioned allotropes, but is relatively constant belowmentioned 360 nm and abovementioned 940 nm. A constant absorption depth across allotropes ensures consistent laser energy absorption regardless of the crystallinity of the Si, and is therefore desired to ensure film homogeneity. However, abovementioned 940 nm the absorption depth reaches 100  $\mu$ m, indicating the majority of the laser energy will be absorbed in the bulk wafer and not in the film. Therefore, a laser wavelength of 355 nm was chosen to ensure sufficient energy absorption in the a-Si film without large amounts of c-Si substrate absorption. Fig. 2 shows a log plot of the absorption depth of silicon with various states of crystallinity from amorphous to single crystal for ultraviolet wavelengths.

## B. Simulation of Laser-Si Interaction

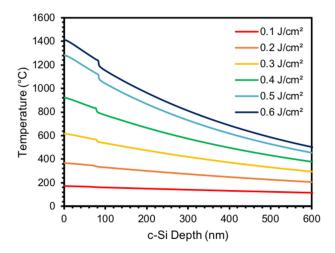

LCPSim, a finite differences code programmed in MATLAB and developed by Andreas Fell at Fraunhofer ISE, can simulate laser optical effects such as reflection and absorption as well as thermodynamic effects such as heat transport and phase change within various materials [18], [19]. This simulation was used to assess the effect of laser fluence on the temperature versus depth within silicon to support our experimental results. Only the laser interaction with crystalline silicon could be reliably modeled, because the varying film density of a-Si means it does not have consistent thermal diffusivity or optical properties. An enthalpy-based heat transfer model was used along with the laser wavelength set to 355 nm, pulse width to 25 ns, and pulse shape to Gaussian. Fig. 3 shows the simulated temperature versus depth in crystalline silicon for single laser pulses of increasing fluence. Additionally, the substrate temperature after times of 20, 10, and 7  $\mu$ s, which correspond to the time between pulses for repetition rates of 50, 100, and 150 kHz, respectively, were investigated.

Fig. 3. Modeled results of temperature versus crystalline silicon depth for increasing laser fluences of a single laser pulse. The simulated laser had a 355 nm wavelength and 25 ns pulse width and was modeled using LCPSim from Fraunhofer ISE with permission from Andreas Fell [18].

We found that despite the high repetition rates (50-150 kHz) used in laser raster processing, substrate temperature returns to near 25 °C between pulses for the fluences assessed, suggesting that there is no thermally induced increase in absorption between pulses and each pulse has its own discrete, isolated effect on the sample. The thermal diffusivities for crystalline, polycrystalline, and a-Si are 0.90, 0.10-0.14, and  $<0.10 \, \text{cm}^2/\text{s}$ , respectively [13]. Therefore, the true temperatures at increasing depths in our a-Si may be lower.

### III. DEVICE FABRICATION AND LASER PROCESSING

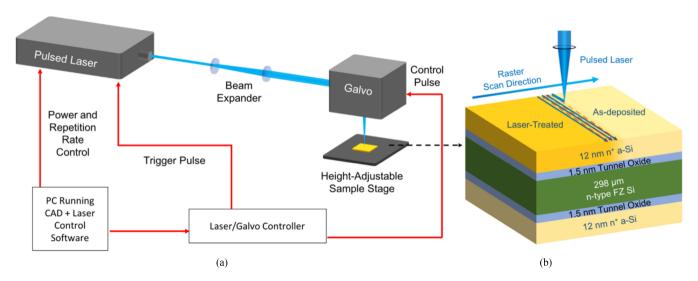

This study used high lifetime, 100 mm, 500  $\Omega$ -cm resistivity, 298  $\mu$ m thick, textured, n-type FZ wafers so that the J<sub>0</sub> variation better reflects the change in surface passivation, and sheet resistance measurements reflect the change in film resistivity. The wafers are planarized and etched using a KOH solution and then cleaned in an RCA solution. Next, a 1.4–1.5 nm-thick tunnel oxide is grown symmetrically on both sides of the wafer using an HNO<sub>3</sub> solution at 100 °C, verified by ellipsometry. After this, we deposit a 12 nm-thick phosphorus-doped a-Si:H layer on both sides of the structure using a UNAXIS PECVD at a deposition temperature of 300 °C. Deposition details can be found in Rohatgi et al. [9]. This layer is subjected to a furnace anneal at 875 °C for 30 min or pulsed laser annealing to further crystallize the layer, activate dopants, and improve its interface with SiO<sub>2</sub> [6]. Using a 355 nm wavelength, 25 ns pulse width, Coherent MATRIX-355, diode-pumped solid-state laser with a spot size of 160  $\mu$ m, and a computer-controlled galvanometric scan head, we optimized the laser fluence and pulse overlap. The pulsed laser is raster scanned across the entire surface of the 25  $\times$  25 mm sample with a repetition rate of 50 kHz, a scan speed between 2–8 m/s, and a raster line spacing of 40–160  $\mu$ m. Fig. 4 shows a schematic of the laser setup, device structure, and laser raster pattern.

Due to the 12 nm film thickness and sample roughness, characterization with Raman and Hall effect measurement becomes

difficult because the majority of the Raman signal would come from the bulk Si substrate, and Hall effect measurements on rough samples with ultrathin films leads to inconsistent results. Therefore, 200 nm a-Si films were deposited and similarly furnace or laser annealed to characterize the crystallization and dopant activation via those methods. Due to the increased film thickness, the ultraviolet laser wavelength was unable to reach the c-Si/SiO<sub>2</sub>/a-Si interface and influence the passivation, but Raman and Hall effect characterization was simplified.

To examine how SiNx further improves the passivation properties, 60 nm of  $\text{SiN}_x$  was deposited symmetrically on a prelaser processed sample with a Trion Orion PECVD system. Films were deposited at a substrate temperature of  $350 \,^{\circ}\text{C}$  and pressure of  $600 \,^{\circ}\text{mTorr}$  using  $600 \,^{\circ}\text{sccm}$  of  $2\% \,^{\circ}\text{SiH}_4$  balanced with  $N_2$  and  $15 \,^{\circ}\text{sccm}$  of  $NH_3$ . The films were annealed at  $350 \,^{\circ}\text{C}$  for  $30 \,^{\circ}\text{min}$  after deposition to ensure suitable film adhesion.

#### IV. LASER PARAMETER OPTIMIZATION

To evaluate the passivation parameters of the symmetric structures shown in Fig. 4(b), we used the method developed by Kane and Swanson [20] using a Sinton Instruments WCT-120 quasisteady-state photoconductance decay (QSSPCD) measurement at a specified minority carrier density of  $1.0 \times 10^{15}$  cm<sup>-3</sup> in generalized (1/1) analysis mode. We divided  $J_0$  values by two to reflect the saturation current of one of the two layers in the symmetric structure which is designated by  $1 \times J_0$ . We measured sheet resistances of the deposited films with a Jandel multiposition probe with a linear 1.00 mm probe spacing and a 25  $\mu$ m tip radius.

After deposition of the 12 nm n<sup>+</sup> a-Si:H films but before any subsequent anneal, the as-deposited films had an average sheet resistance exceeding 10 k $\Omega/\text{sq}$ , active dopant concentration on the order of  $10^{16}$  cm $^{-3}$ , lifetime fit of 733  $\mu s$ , implied open circuit voltage (iV $_{\rm OC}$ ) of 679 mV, and 1  $\times$  J $_0$  of 25.6 fA/cm $^2$ . One sample was conventionally annealed in a furnace at 875 °C for 30 min in inert nitrogen to activate the dopants, crystallize the a-Si, and improve the interface it shares with SiO $_2$ . After annealing, the sheet resistance dropped to 0.6 k $\Omega/\text{sq}$  and the active dopant concentration increased to 7.7  $\times$  10 $^{19}$  cm $^{-3}$ , indicating phosphorus moving from interstitial to substitutional lattice sites and solid-phase crystallization of the n $^+$  a-Si. The lifetime and iV $_{\rm OC}$  increase to 3586  $\mu s$  and 719 mV, respectively, whereas the 1  $\times$  J $_0$  decreased to 5.2 fA/cm $^2$ , indicating excellent surface passivation.

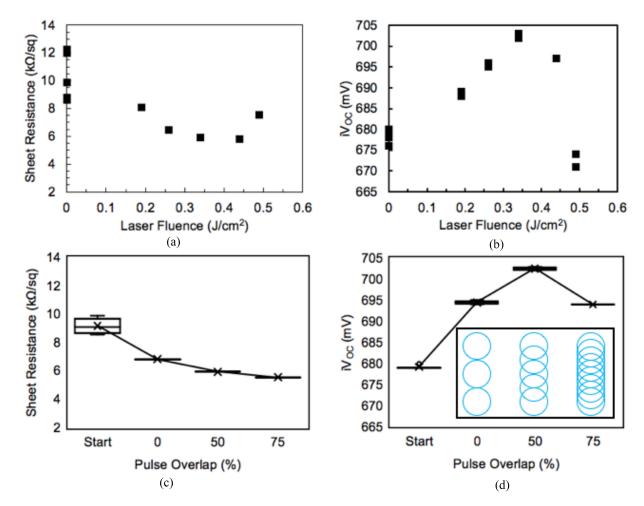

To reduce the thermal budget for this process and the amount of time at which the structure stays at elevated temperatures, as-deposited samples were laser-processed across a variety of laser fluences and pulse overlap percentages on both sides of the symmetric structure. The process optimization results are shown in Fig. 5 and do not include subsequent SiN $_{\rm x}$  deposition. Initially, as the laser fluence increases, the film sheet resistance decreases and the iV $_{\rm OC}$  increases, suggesting simultaneous dopant activation and passivation improvement. The iV $_{\rm OC}$  peaks at 703 mV at a fluence of 0.34 J/cm $^2$ , which corresponds to a temperature range near 800 °C from the simulation and coincides well with conventional furnace annealing temperatures at

Fig. 4. (a) Schematic of pulsed-laser processing setup with scanning galvanometer. (b) Symmetric carrier-selective passivating-contact device structure for QSSPCD evaluation of passivation showing laser raster scan pattern.

Fig. 5. (a) Fluence of a single laser pulse versus film sheet resistance. (b) Device  $iV_{\rm OC}$ . The optimal fluence occurs at  $0.34~\rm J/cm^2$  based on low sheet resistance and high  $iV_{\rm OC}$ . (c) Percentage of pulse overlap at the optimal laser fluence versus film sheet resistance. (d) Device  $iV_{\rm OC}$ . While greater overlap resulted in a lower sheet resistance, the peak device  $iV_{\rm OC}$  occurred at a pulse overlap of 50%. (d, inset) A top-down illustration of how pulse overlap of a Gaussian beam influences the number of pulses per area. All poly-Si films used in this figure were 12 nm thick. Optimization data does not include subsequent  $SiN_x$  deposition.

TABLE I ELECTRICAL PARAMETERS OF TOPCON TEST STRUCTURES

| Sample                                                                 | $\begin{array}{c} R_{Sheet} \\ (k\Omega/sq) \end{array}$ | N <sub>D</sub><br>(cm <sup>-3</sup> ) | $\tau_{fit}$ ( $\mu s$ ) | iV <sub>OC</sub><br>(mV) | $\begin{array}{c} 1 \times J_0 \\ (fA/cm^2) \end{array}$ |

|------------------------------------------------------------------------|----------------------------------------------------------|---------------------------------------|--------------------------|--------------------------|----------------------------------------------------------|

| As-Deposited, Pre-<br>annealing                                        | > 10 <sup>a</sup>                                        | $\sim 10^{16}$                        | 733                      | 679                      | 25.6                                                     |

| 875 °C, 30 min, N <sub>2</sub><br>Furnace anneal                       | 0.6                                                      | $7.7 \times 10^{19}$                  | 3586                     | 719                      | 5.2                                                      |

| Optimal Laser<br>Processed <sup>b</sup> Sample                         | 5.9                                                      | $7.1 \times 10^{18}$                  | 1333                     | 703                      | 15.5                                                     |

| Laser Processed<br>Sample with Post-<br>Deposition of SiN <sub>x</sub> | 5.9                                                      | 7.1×10 <sup>18</sup>                  | 2001                     | 718                      | 8.6                                                      |

Sheet resistance, active dopant concentration, lifetime fit, implied open-circuit voltage, and one side recombination current density for the starting as-deposited, furnace annealed, champion laser annealed, and laser annealed with subsequent  $SiN_{\rm x}$  deposition samples. All poly-Si films used in this table were 12 nm thick.

800 °C. For instance, Rohatgi et al. [9] obtained a 702 mV iV<sub>OC</sub> when furnace annealing at 800 °C for 1 h, whereas their iV<sub>OC</sub> increased to 720 mV at 875 °C. Above this fluence, the drop in sheet resistance flattens out with a minimum of 5.8  $k\Omega$ /sq and begins to increase again at even higher fluences. This suggests that laser activation of dopants may saturate at this density for 12 nm n<sup>+</sup> poly-Si films and the sheet resistance increase at fluences abovementioned 0.45 J/cm<sup>2</sup> may indicate dopant loss or a-Si film ablation. Similarly, the drop in iV<sub>OC</sub> at higher fluences could indicate damage to the underlying tunnel oxide interfaces and reduced band bending as a result of dopant or film loss. The laser fluence has to be very precisely controlled to achieve the higher 720 mV  $iV_{\rm OC}$  demonstrated at 875 °C annealing, which is difficult with a Gaussian beam profile due to the nonconstant intensity throughout the beam area. Therefore, the optimal fluence was chosen as 0.34 J/cm<sup>2</sup> for laser annealing and was used to optimize the pulse overlap. The pulse overlap was adjusted by changing the galvanometer scanning speed to 2, 4, and 8 m/s and the scan line spacing to 40, 80, and 160  $\mu$ m, respectively, at a fixed repetition rate of 50 kHz and laser spot size of 160  $\mu$ m. The pulse and scan line spacing were kept identical for simplicity. The inset of Fig. 5(d) shows a top-down illustration of the pulse overlap. The film sheet resistance continued to decrease with increasing overlap, reaching a minimum value of 5.5 k $\Omega$ /sq at an overlap percentage of 75%. However, the iV<sub>OC</sub> peaked at an overlap percentage of 50% and decreased at higher overlap percentages. This indicates that while a higher overlap percentage could grant increased dopant activation, it may cause minor damage to the tunnel oxide interfaces from photomechanical stress. Therefore, 50% (4000 mm/s scan speed and 80  $\mu$ m scan line spacing) was selected as the optimal pulse overlap.

Table I summarizes the dopant activation and passivation of the as-deposited, furnace annealed, optimally laser-processed sample, and optimally laser-processed sample with 60 nm of  $\mathrm{SiN}_{x}$  symmetrically deposited on both sides of the sample.

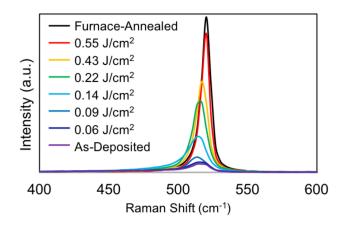

Fig. 6. Raman spectra of 200 nm thick as-deposited, furnace annealed and a-Si films that were laser processed under a single pulse at increasing laser fluence. As the laser fluence increases, the intensity of the 520 cm<sup>-1</sup> Si peak increases, demonstrating increased crystallinity under increasing laser fluence. Thicker films were used to ensure the Raman signal only comes from the deposited film and not the wafer.

# V. CHARACTERIZATION OF A-SI:H LAYER CRYSTALLIZATION AND DOPANT ACTIVATION

To assess the degree to which ultraviolet laser annealing of n<sup>+</sup> a-Si activates dopants and crystallizes the a-Si, thicker, 200 nm films were deposited via a Tystar tube furnace LPCVD tool at 588 °C on top of a 1.4–1.5 nm HNO<sub>3</sub> grown tunnel oxide. Details of this process are published elsewhere by Upadhyaya et al. [6]. Raman spectra were taken with a Renishaw inVia confocal Raman microscope with an 1800 lines/mm grating (2.93 cm<sup>-1</sup> resolution) at an excitation wavelength of 405 nm to reduce the signal coming from the substrate. Fig. 6 shows the Si Raman peak for as-deposited, furnace annealed, and laser annealed samples at increasing laser fluence where each laser annealed spectra is from a single laser pulse on an as-deposited sample. Amorphous Si has a broad Raman band based on the wide variety of different bond lengths in its amorphous state, whereas c-Si has a sharp Raman peak centered at 520.5 cm<sup>-1</sup> corresponding to a high count of similar short-length bonds. With increasing fluence, the peak intensity increases and the peak width decreases indicating increased crystallinity. Part of the signal intensity increase with crystallinity will be the result of an increased interaction volume with an increased absorption depth of c-Si (100 nm) versus a-Si (11 nm) at 405 nm as shown in Fig. 2. While the high 0.55 J/cm<sup>2</sup> fluence spectra shows crystallinity on par with that of the furnace annealed poly-Si, that fluence is too high for thinner 12 nm a-Si samples, as it causes a large drop in iV<sub>OC</sub> from oxide interface disruption. The thickness of the deposited a-Si layer could potentially be optimized to allow for a higher fluence without impacting the tunnel oxide interface.

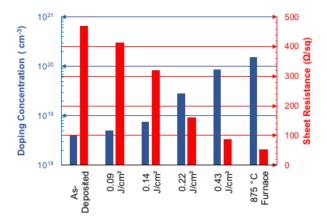

Carrier concentration and sheet resistance were calculated from the Hall mobility, measured at room temperature with an Ecopia HMS-3000 hall measurement system using a 0.55 T permanent magnet and spring probes configured to the van der Pauw arrangement on square samples and the results are shown

<sup>&</sup>lt;sup>a</sup>Sheet resistance is unmeasurable above 10 k $\Omega$ /sq.

<sup>&</sup>lt;sup>b</sup>Optimal condition is at a laser fluence of 0.34 J/cm<sup>2</sup>.

Fig. 7. Hall-effect measurement of doping concentration (left axis, blue bars) and sheet resistance (right axis, red bars) for 200 nm thick as-deposited, furnace annealed, and laser annealed a-Si films, showing an increase in doping concentration and decrease in sheet resistance with increasing laser fluence that is comparable to furnace annealing.

in Fig. 7. As-deposited samples begin with a carrier concentration of  $4.0 \times 10^{18} \text{ cm}^{-3}$  and sheet resistance of 470  $\Omega/\text{sq}$ . Since most of the phosphorus dopant is in interstitial sites and few lattice sites exist in the amorphous state, it contributes little to the electrical properties of the film. As the laser fluence increases, dopant activation continues to rise, increasing the measured dopant concentration and decreasing the film sheet resistance as the amorphous film crystallizes and the phosphorus dopant enters the crystalline lattice. The highest fluence evaluated, 0.43 J/cm<sup>2</sup>, has a measured dopant concentration of 8.7  $\times$  10<sup>19</sup> cm<sup>-3</sup> and sheet resistance of 87  $\Omega$ /sq comparable to the furnace annealed 200 nm poly-Si sample's  $1.5 \times 10^{20}$  cm<sup>-3</sup> concentration and 52  $\Omega$ /sq sheet resistance, indicating successful activation of dopant and film crystallization with room for future improvement through laser annealing optimization. Dopant concentration profiles for thermally annealed films can be found in Upadhyaya et al. [6].

The a-Si:H film thickness must be carefully chosen for improved performance at a given laser wavelength. Thicker a-Si:H films, in the range of 100-200 nm, will absorb the laser light in the upper part of the film and the thermal annealing of interface defects does not occur due to the temperature gradient in the film. If the a-Si:H film thickness is too low (~10 nm), then part of the laser light will be absorbed by the Si substrate, inducing defects. For a 355 nm wavelength laser, an optimum a-Si:H film thickness appears to be around 20–40 nm to achieve higher performance from laser annealing. Poly-Si layers with a 20-40 nm thickness may be suitable for front surface TOPCon, but is currently not suitable for screen printing applications on the rear surface, which require 100-200 nm thick poly-Si layers for firing. However, by using a longer pulse width of 50–100 ns or a longer laser wavelength of 400–450 nm, effective and uniform annealing of a thicker poly-Si for screen printing becomes feasible [6]. We have demonstrated the feasibility of laser crystallization and dopant activation of a-Si:H in TOP-Con carrier-selective contacts, and further improvements can be made by optimizing the layer thickness and corresponding annealing fluence.

#### VI. CONCLUSION

We have demonstrated a novel laser processing concept to replace the high-temperature furnace anneal for n-type TOPCon carrier-selective passivating contacts for silicon solar cells. By utilizing laser processing, the polysilicon layer increases in crystallinity, electrical conductivity due to dopant activation, and passivation due to the shallow absorption depth of the laser wavelength and the nano-timescale from the laser pulsewidth, with minimal thermal impact on the interfacial oxide. Optical modeling and LCPSim simulations help shape our knowledge of the laser-material interaction process and provide a foundation for experimental work. Combined with a SiN<sub>x</sub> layer, we demonstrate a well-passivated SiN<sub>x</sub>/poly-Si/tunnel oxide/Si structure with a low 5.9 k $\Omega$ /sq poly-Si sheet resistivity, over 2001 ms effective carrier lifetime, 718 mV iV<sub>OC</sub>, and 8.6 fA/cm<sup>2</sup> J<sub>0</sub> demonstrating the viability of our approach. Raman and Hall effect characterization of 200-nm laser-annealed a-Si films show that a degree of crystallinity and dopant activation comparable to 875 °C furnace-annealed films can be achieved.

A thicker a-Si film, potentially in the range of 20–40 nm would allow for a higher fluence to be used, granting increased crystallinity and dopant activation but reducing damage to the tunnel oxide interfaces due to the temperature decrease at increased thickness. By adapting the laser processing to a solar cell device, high-efficiency and well-passivated carrier selective silicon solar cells could be fabricated at a reduced thermal budget and without the heating of the entire wafer under furnace annealing. Thicker a-Si films and use in a full device structure will be the subject of future study.

#### ACKNOWLEDGMENT

The authors would like to thank A. Fell and Fraunhofer ISE for provision of and assistance with LCPSim software.

# REFERENCES

- E. Yablonovitch, T. Gmitter, R. M. Swanson, and Y. H. Kwark, "A 720 mV open circuit voltage SiO<sub>x</sub>:c-Si:SiO<sub>x</sub> double heterostructure solar cell," *Appl. Phys. Lett.*, vol. 47, 1985, Art. no. 1211.

- [2] W. Füssel, W. Henrion, and R. Scholz, "Structural, optical and electrical properties of SIPOS passivation layers," *Microelectron. Eng.*, vol. 22, pp. 355–358, 1993.

- [3] F. Feldmann et al., "Carrier-selective contacts for Si solar cells." Appl. Phys. Lett., vol. 104, 2014, Art. no. 181105.

- [4] R. Peibst et al., "Building blocks for back-junction back-contacted cells and modules with ion-implanted poly-Si junctions," in Proc. IEEE 40th Photovolt. Specialist Conf., 2014, pp. 8–13.

- [5] P. Stradins et al., "Passivated tunneling contacts to n-type wafer silicon and their implementation into high performance solar cells: Preprint," in Proc. 6th World Conf. Photovolt. Energy Convers., Kyoto, Japan, 2014, pp. 1–4.

- [6] A. D. Upadhyaya et al., "Ion-implanted screen-printed n-type solar cell with tunnel oxide passivated back contact," *IEEE J. Photovolt.*, vol. 6, no. 1, pp. 153–158, Jan. 2016.

- [7] B. Nemeth et al., "Polycrystalline silicon passivated tunneling contacts for high efficiency silicon solar cells," J. Mater. Res., vol. 31, pp. 671–791, 2016

- [8] Y. Tao et al., "Carrier selective tunnel oxide passivated contact enabling 21.4% efficient large-area N-type silicon solar cells," in Proc. IEEE 43rd Photovolt. Specialists Conf., 2016, pp. 2531–2535.

- [9] A. Rohatgi et al., "Fabrication and modeling of high-efficiency front junction N-type silicon solar cells with tunnel oxide passivating back contact," *IEEE J. Photovolt.*, vol. 7, no. 5, pp. 1236–1243, Sep. 2017.

- [10] S. Reiter et al., "Parasitic absorption in polycrystalline Si-layers for carrier-selective front junctions." Energy Procedia, vol. 92, pp. 199–204, 2016.

- [11] M. C. Gupta and D. E. Carlson, "Laser processing of materials for renewable energy applications." MRS Energy Sustain., vol. 2. E2, pp. 1–15, 2015

- [12] Z. Sun and M. C. Gupta, "Laser annealing of silicon surface defects for photovoltaics applications." *Surf. Sci.*, vol. 652, pp. 344–349, 2016.

- [13] L. Wei et al., "Heat conduction in silicon thin films: Effects of microstructure." J. Mater. Res., vol. 10, pp. 1889–1896, 1995.

- [14] G. R. Wolstenholme, N. Jorgensen, P. Ashburn, and G. R. Booker, "An investigation of the thermal stability of the interfacial oxide in polycrystalline silicon emitter bipolar transistors by comparing device results with high-resolution electron microscopy observations." *J. Appl. Phys.*, vol. 61, pp. 225–233, 1987.

- [15] D. Sands, "Pulsed laser heating and melting," Heat Transfer Engineering Applications, V. Vikhrenko, Ed. Rijeka, Croatia: InTech, 2011.

- [16] G. C. Wilkes, A. D. Upadhyaya, A. Rohatgi, and M. C. Gupta, "Laser crystallization and dopant activation for a-Si:H film in carrier-selective contacts for silicon solar cells," in *Proc. IEEE 46th Photovolt. Specialists Conf.*, 2019, pp. 2709–2712.

- [17] Optical Data from Sopra SA. [Online]. Available: http://sspectra.com/sopra.html, Accessed: Feb. 18, 2020.

- [18] A. Fell and G. P. Willeke, "Fast simulation code for heating, phase changes and dopant diffusion in silicon laser processing using the alternating direction explicit (ADE) method," *Appl. Phys. A*, vol. 98, no. 2, pp. 435–440, 2010.

- [19] A. Fell, "Modelling and simulation of laser chemical processing (LCP) for the manufacturing of silicon solar cells," Ph.D. Dissertation, Dept. Physik, Univ. Konstanz, Konstanz, Germany, 2010.

- [20] D. E. Kane and R. M. Swanson, "Measurement of the emitter saturation current by a contactless photoconductivity decay method," in *Proc.* 18th IEEE Photovolt. Specialists Conf., Las Vegas, NV, USA, 1985, pp. 578–583.

George C. Wilkes (Graduate Student Member, IEEE) received the B.S. degree in physics with a minor in mathematics from James Madison University in Harrisonburg, Harrisonburg, VA, USA, in 2015. Since 2015, he has been working toward the Ph.D. degree with National Institute of Aerospace and the University of Virginia, Charlottesville, VA, USA.

He is currently a Graduate Research Assistant with the National Institute of Aerospace, University of Virginia. He has written and co-authored four publications on low-temperature and laser applications

for perovskite and silicon solar cells. His research interests include selective carrier transport and passivation layers for solar cells and how laser processing can enable increased performance with selective energy deposition at low temperatures, increasing throughput, and reducing manufacturing costs.

Mr. Wilkes was a finalist in the 2018 NASA Big Idea competition for his work on a photovoltaic balloon for energy generation on Mars. He also received the award for Best Student Paper at the National Institute of Aerospace, in 2019.

**Ajay D. Upadhyaya** (Member, IEEE) received the B.S. degree in electrical and computer engineering with an emphasis on semiconductors from the Georgia Institute of Technology in Atlanta, Atlanta, GA, USA, in August 2001, and the MBA degree with a focus in marketing from Mercer University, Atlanta, GA, USA, in 2006.

He has been with the Georgia Institute of Technology since 2001 in many capacities. He a Senior Research Engineer and Operations Manager with the University Center of Excellence for Photovoltaics

Research and Education, Georgia Institute of Technology. He has authored or co-authored more than 50 publications in journals and conference proceedings. His current interests are to make large-area, high-efficiency n- and p-type monocrystalline silicon solar cells at lower cost through technology innovations such as passivating contact, selective emitter, laser processes, and plating. In the past, he has worked to enhance lower quality silicon materials such as multicrystalline, ribbon, and Edge-defined film-fed growth (EFG) silicon to enhance the quality and performance of solar cells through existing processing steps.

Mr. Upadhyaya was the recipient of the Best Researcher Award at Georgia Tech. He is on award committees at Georgia Tech and has chaired several sessions at the IEEE Photovoltaic Specialist Conference.

**Ajeet Rohatgi** (Life Fellow, IEEE) received the Ph.D. degree in metallurgy and material science from Lehigh University, Bethlehem, PA, USA, in 1977.

He is a Regents Professor and John H. Weitnauer, Jr., Chair with the College of Engineering and a Georgia Research Alliance Eminent Scholar. He is the Founding Director of the University Center of Excellence for Photovoltaic Research and Education, Georgia Institute of Technology, Atlanta, GA, USA, in 1982 and the Founder and CTO of Suniva Inc., in 2008. He has authored more than 500 technical papers

in this field and has been awarded 17 patents. His current research interests include the development of cost and efficiency roadmaps for attaining grid parity with silicon photovoltaics (PV), the design and fabrication of low-cost high-efficiency cells on mono and multicrystalline silicon, and the performance and economics of PV systems.

Prof. Rohatgi is very active on various award committees with the Georgia Institute of Technology. He was the recipient of the IEEE PVSC William Cherry Award, the NREL's Department of Energy Rappaport Award, the Outstanding Research Program Development Award, and the Hoyt Clark Hottel Award for outstanding educator and innovator in the field of PV from the American Solar Energy Society.

**Mool C. Gupta** (Fellow, IEEE) received his Ph.D. degree in physics from Washington State University, Pullman, WA, USA, in 1973.

He was a Postdoctoral Fellow with Cornell University and a Senior Research Fellow with the California Institute of Technology. From 1998 to 2005, he was the Director of the Applied Research Center with Old Dominion University. Since 2005, he has been the Langley Distinguished Professor with the Electrical and Computer Engineering Department with the University of Virginia. He is the Founding Director

of the NSF Industry/University Cooperative Research Center for Lasers and Plasmas at the University of Virginia. He has authored 250 scientific publications in various technical journals and has been awarded 28 US and international patents. His current research interests include the applications of high-powered lasers for solar cell manufacturing, thermophotovoltaics, photonic devices, laser microtexturing of surfaces, and infrared detectors.

Prof. Gupta is the Editor-in-Chief of the *Handbook of Photonics*, CRC Press, 1st and 2nd edition. He is a Fellow of the Optical Society of America, an Inductee of the Kodak Inventor's Gallery, Chair of the NRC NASA Technology Roadmap Materials Panel, and Principal Investigator for DARPA, ARO, NASA, NSF, DOE, and NRL.