### 6.3 A 0.9V Dual-Channel Filtering-by-Aliasing Receiver Front-End Achieving +35dBm IIP<sub>3</sub> and <-81dBm LO Leakage Supporting Intra- and Inter-Band Carrier Aggregation

Shi Bu, Sudhakar Pamarti

University of California, Los Angeles, CA

Programmable receivers have drawn a lot of attention in recent years, especially those exploiting periodically time-varying (PTV) circuits.  $N$ -path filters and mixer-first receivers [1–3] achieve sharp filtering and good linearity but can suffer from high LO leakage (>-70dBm), which is not compliant with the FCC requirements [4]. In addition, they do not support multi-carrier operation very well [5].

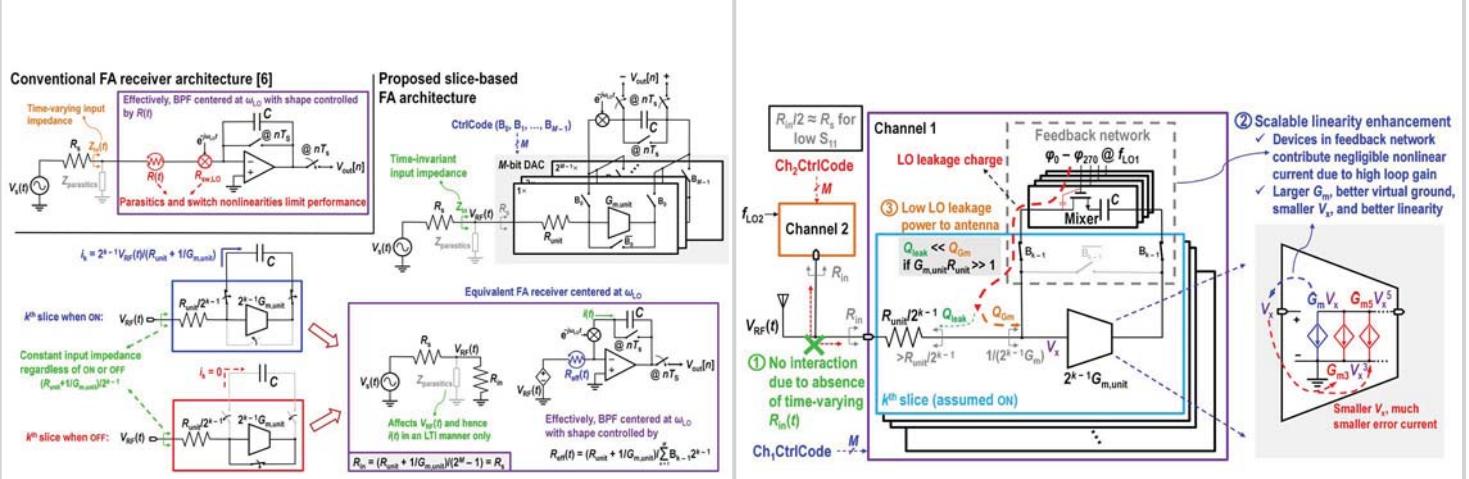

The filtering-by-aliasing (FA) receiver front-end in [6] uses a resistor DAC to realize a PTV resistor,  $R(t)$ , followed by a passive mixer and an integrate-and-dump circuit to achieve sharp analog FIR filtering and moderate linearity (Fig. 6.3.1). However, the PTV resistor presents a time-varying impedance at the RF node,  $V_{RF}$ . While low  $S_{11}$  can be achieved in an average sense [6], it is difficult to guarantee desired filter response in the presence of complex source impedances, e.g., from parasitics. More importantly, if FA were applied in multi-carrier systems, it causes undesirable inter-channel corruption. Furthermore, achievable filter attenuation and linearity are limited by parasitics and switch resistance nonlinearities of the resistor DAC and the mixer.

This work presents a slice-based FA receiver architecture to address these issues without sacrificing the sharp filtering offered by FA. As shown in Fig. 6.3.1, the  $k^{\text{th}}$  slice is made of a resistor,  $R_{\text{unit}}/2^{k-1}$ , a transconductance ( $G_m$ ) cell,  $2^{k-1}G_{m,\text{unit}}$ , and selection switches. The switches in the slice steer the current into a common integrating capacitor,  $C$ , when  $B_{k-1}=1$  (i.e., slice is on) or into the  $G_m$  cell's output in unity-gain configuration when  $B_{k-1}=0$  (i.e., slice is off). Binary-weighted slices effectively make up a resistor DAC that can realize a PTV resistor,  $R_{\text{eff}}(t)$ , by selecting the *CtrlCode* appropriately to achieve desired sharp FA filtering. The passive mixer in the feedback enables filtering at  $\omega_{\text{LO}}$ . Meanwhile, note that, whether on/off, the  $k^{\text{th}}$  slice presents the same input resistance since its  $G_m$  cell is always in negative feedback. Therefore, the input resistance of the entire circuit is time-invariant and can be readily matched to  $R_s$  and not just in an average sense as in [6]. More importantly, FA operation is now tolerant of any complex impedances at  $V_{RF}$ . In effect, while the overall operation is PTV, the circuit can be treated and analyzed on a slice-by-slice basis in a time-invariant sense.

The proposed architecture offers several crucial benefits (Fig. 6.3.2). Firstly, the time-invariant input impedance enables multi-carrier FA operation free of interference between channels. This is because no time-dependent impedance interaction occurs, and the current to be integrated in each channel is not affected by others' operations. Secondly, all switches are placed in feedback, so switch non-idealities have negligible effect on filter shape and linearity. This is because the current from the  $k^{\text{th}}$  slice to the integrating capacitor is independent of the feedback network's impedance (recall Fig. 6.3.1). Furthermore,  $G_m$ -induced nonlinearity can also be easily made small by using a larger  $G_m$  to form a better virtual ground. This offers a scalable way of enhancing linearity. Thirdly, most of any LO leakage charge will go to the virtual ground rather than through the large resistors of the slices and onward to the antenna, thereby lowering LO leakage power significantly. The proposed architecture increases the noise figure (NF) slightly since the off slices act as an equivalent shunt resistor at  $V_{RF}$ . This can be mitigated to a certain extent as described later. Switch parasitics may also degrade filter response at much higher LO frequencies.

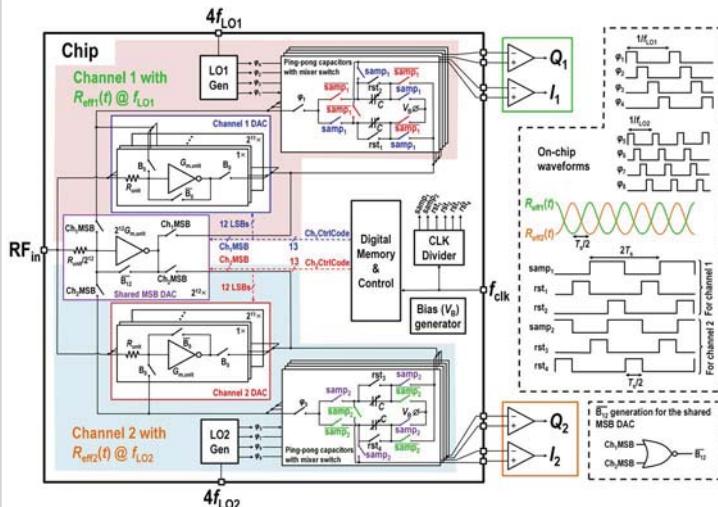

A dual-channel RF front-end was implemented, whose block diagram is shown in Fig. 6.3.3. Each channel is realized by a 4-path passive mixer and a 13b binary-weighted slice-based DAC; 13b ensures the DAC resolution does not limit filter shape. The DACs switch at  $f_{\text{clk}}/2$  and the effective PTV resistor variations,  $R_{\text{eff1}}(t)$  and  $R_{\text{eff2}}(t)$ , with a period of  $T_s$ , are sketched. The sampling and reset clocks are derived synchronously from the same  $f_{\text{clk}}$  signal. While not required,  $R_{\text{eff2}}(t)$  is deliberately chosen to be an equal but shifted version of  $R_{\text{eff1}}(t)$ . This bestows the same filter shape on both channels; the shift guarantees that  $R_{\text{eff1}}(t)$  and  $R_{\text{eff2}}(t)$  are never simultaneously small, allowing the MSB slice to be shared thereby saving power and area, and reducing the NF penalty from the off-slice shunt resistance. The integrating capacitor is realized in ping-pong fashion to allow one capacitor to be integrating signal current while the other is being read and then reset. The 4-path passive mixers are integrated with the ping-pong capacitor banks. They are driven by two sets of 25% duty-cycled clock signals at  $f_{\text{LO1}}$  and  $f_{\text{LO2}}$ , respectively, to mix the RF current to baseband for integration. Note that  $f_{\text{LO1}}$  and  $f_{\text{LO2}}$  can be any value within the RF range.

The IC was fabricated in TSMC 28nm CMOS technology. The  $G_m$  cells are implemented as inverters and  $G_{m,\text{unit}}R_{\text{unit}}$  is designed to be about 15, as an optimal trade-off between  $G_m$  linearity,  $R_{\text{unit}}$  noise, and power. All switches are implemented using transmission gates with equally sized NMOS and PMOS transistors, with LO switches designed to have an on-resistance of  $4\Omega$ . The DACs are DC calibrated at start-up to compensate for mismatches; simulations suggest PVT variability has minimal impact on filter performance. MOM capacitors serve as the integrating capacitors, tunable from 10 to 80pF. The entire chip uses a single supply voltage of 0.9V, and the DC bias of the chain is about 0.45V set by  $G_m$  cells' biasing at reset and their buffer configuration. An on-chip generated 0.45V  $V_b$  is used to provide common mode for the capacitors during sampling. For 10MHz bandwidth (BW) filters centered at  $f_{\text{LO1}}=500\text{MHz}$  and  $f_{\text{LO2}}=740\text{MHz}$ , a current of 60mA is drawn by the entire chip at  $f_{\text{clk}}=2\text{GHz}$ . The system was verified to work up to  $f_{\text{clk}}=4\text{GHz}$ . In addition to the default high-performance (HP) operation mode, a low-noise (LN) mode can be enabled by disabling the shorting switches,  $B_{k-1}$ . This decreases the net off-slice shunt resistance thereby reducing the NF by about 3dB at the cost of slightly degraded filtering and linearity. The HP or LN modes can be chosen for strong- and weak-blocker scenarios, respectively [7], using blocker-level detection, e.g., with an integrated blocker detector [8] or a spectrum scanner [9].

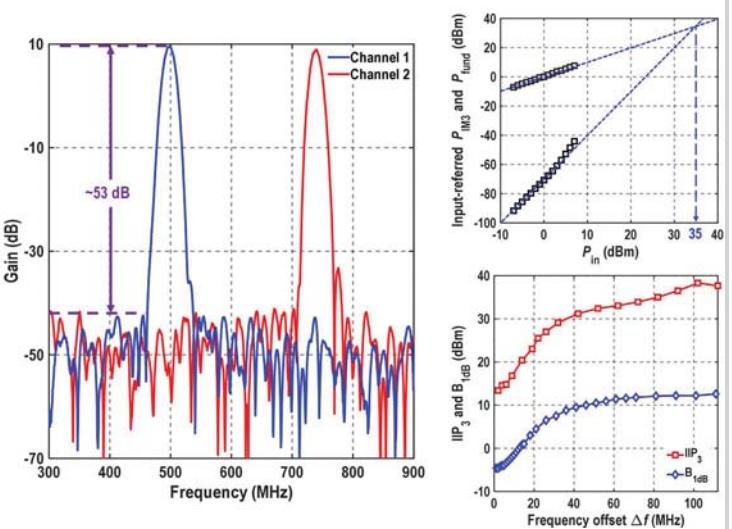

The sampled outputs are buffered externally for measurement. Fig 6.3.4 shows the measured concurrent filter responses with 10MHz BW at  $f_{\text{LO1}}=500\text{MHz}$  and  $f_{\text{LO2}}=740\text{MHz}$  in HP mode. All measurements were performed with both channels on and with  $f_{\text{LO1}}$  and  $f_{\text{LO2}}$  spaced by 240MHz. The transition BW is 32MHz with a stopband rejection ( $A_{\text{stop}}$ ) of 53dB. The out-of-band (OOB) and in-band (IB) IIP<sub>3</sub> are 35dBm and 13.4dBm, and the blocker 1dB compression point ( $B_{1\text{dB}}$ ) is 12dBm with a supply of mere 0.9V, since all nonlinearities are suppressed by the feedback loop. The filtering and linearity performance are similar for the two channels and do not vary appreciably across different LO frequencies.

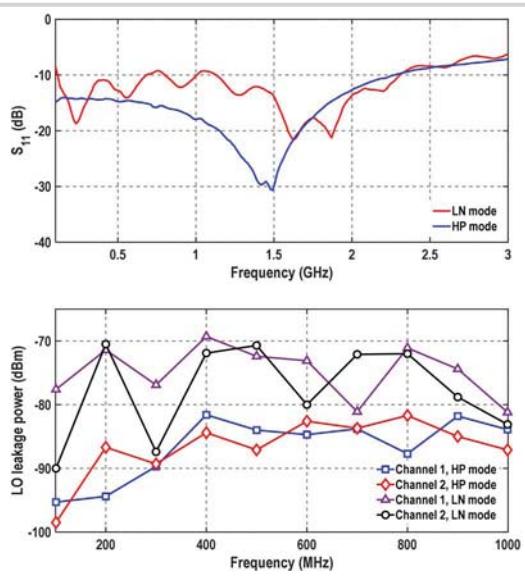

Figure 6.3.5 shows the measured  $S_{11}$  and LO leakage power. A wideband  $S_{11}$  better than -14dB for the entire range of operation (0.1 to 1GHz) is achieved in HP mode and it is smaller than -10dB up to 2.3GHz. In contrast, the  $S_{11}$  is more poorly controlled and only <-8.5dB in LN mode. The worst-case LO leakage, measured over two chips, is less than -81dBm in HP mode, much smaller than the FCC requirements [4]. Even in LN mode, it is still below -69dBm. The rejection of signals in the other channel is roughly the same as  $A_{\text{stop}}$ .

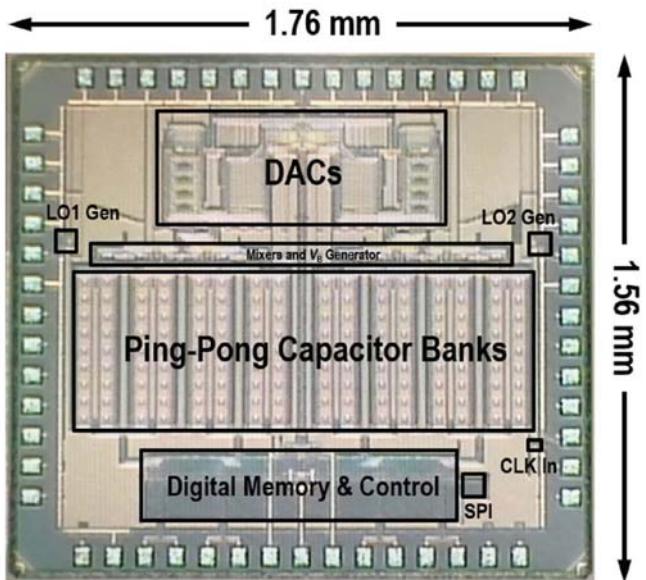

Figure 6.3.6 compares this work with recent single- and multi-carrier designs. This work maintains the sharp filtering of single-carrier FA [6] even in a dual-carrier configuration. Compared to other multi-carrier works, the NF is slightly higher, while it achieves at least 19dBm better IIP<sub>3</sub> with only 0.9V supply. The achieved performance is comparable to or even better than the single-carrier ones with higher supplies. Figure 6.3.7 shows the die photo of the fabricated IC. The active area is 1.3mm<sup>2</sup>.

#### Acknowledgement:

This work was supported in part by the National Science Foundation under grant ECCS 1810268, the Qualcomm Innovation Fellowship and the Broadcom Foundation Fellowship programs.

#### References:

- [1] Y. Lien et al., "A High-Linearity CMOS Receiver Achieving +44dBm IIP3 and +13dBm B<sub>1dB</sub> for SAW-Less LTE radio," *ISSCC*, pp. 412–414, Feb. 2017.

- [2] P. Song and H. Hashemi, "A 13<sup>th</sup>-Order CMOS Reconfigurable RF BPF with Adjustable Transmission Zeros for SAW-Less SDR Receivers," *ISSCC*, pp. 416–417, Feb. 2018.

- [3] S. Krishnamurthy and A. M. Niknejad, "Design and Analysis of Enhanced Mixer-First Receivers Achieving 40-dB/Decade RF Selectivity," *IEEE JSSC*, vol. 5, no. 5, pp. 1165–1176, May 2020.

- [4] S. Jayasuriya et al., "A Baseband Technique for Automated LO Suppression Achieving <-80dBm In Wideband Passive Mixer-First Receivers," *CICC*, pp. 1–4, Sept. 2014.

- [5] G. Han et al., "A Multi-Branch Receiver with Modulated Mixer Clocks for Concurrent Dual-Carrier Reception and Rapid Compressive-Sampling Spectrum Scanning," *IEEE JSSC*, early access, doi: 10.1109/JSSC.2020.3014063.

- [6] S. Hameed and S. Pamarti, "A Time-Interleaved Filtering-By-Aliasing Receiver Front-End with >70dB Suppression at <4x Bandwidth Frequency Offset," *ISSCC*, pp. 418–419, Feb. 2017.

- [7] D. Murphy et al., "A Blocker-Tolerant, Noise-Cancelling Receiver Suitable for Wideband Wireless Applications," *IEEE JSSC*, vol. 47, no. 12, pp. 2943–2963, Dec. 2012.

- [8] Y. Xu and P. R. Kinget, "A Chopping Switched-Capacitor RF Receiver with Integrated Blocker Detection," *IEEE JSSC*, vol. 53, no. 6, pp. 1607–1617, June 2018.

- [9] N. Sinha et al., "Design and Analysis of an 8 mW, 1 GHz Span, Passive Spectrum Scanner with >+31 dBm Out-Of-Band IIP3 Using Periodically Time-Varying Circuit Components," *IEEE JSSC*, vol. 52, no. 8, pp. 2009–2025, Aug. 2017.

Figure 6.3.1: Conventional FA receiver (top-left), slice-based FA receiver architecture (top-right), operation of one slice (bottom-left), and the overall receiver model (bottom-right).

Figure 6.3.2: Illustration, using one ON slice, of 1) elimination of channel interaction; 2) scalable linearity enhancement; 3) and LO leakage suppression.

Figure 6.3.3: Block diagram of the implemented two-channel receiver front-end IC using the slice-based FA architecture.

Figure 6.3.4: Measured concurrent-receiving filter shapes (left), input-referred  $P_{IM3}$  and  $P_{IIP3}$  versus  $P_{in}$  at offset frequency  $\Delta f = 82$  MHz (top-right), and  $IIP_3$  and  $B_{1dB}$  at different  $\Delta f$  (bottom-right) in high-performance (HP) mode.

Figure 6.3.5: Measured  $S_{11}$  (top) and LO leakage power at different LO frequencies (bottom) in both high-performance (HP) and low-noise (LN) modes.

|                         | Single-channel receivers/filters |                         |                                     |                        | Carrier aggregation receivers         |                       |                                      |                                      | This work                |                          |

|-------------------------|----------------------------------|-------------------------|-------------------------------------|------------------------|---------------------------------------|-----------------------|--------------------------------------|--------------------------------------|--------------------------|--------------------------|

|                         | [6] ISSCC'17                     | [1] ISSCC'17            | [2] ISSCC'18                        | [3] JSSC'20            | [10] ISSCC'15                         | [11] JSSC'18          | [5] JSSC'20*                         | Multi-branch mod.-mixer-clock        | LN mode                  | HP mode                  |

| Architecture            | TI-FA                            | N-path                  | N-path                              | N-path                 | Current-domain signal process.        | Code-domain N-path    | 65 nm                                | 28 nm                                |                          | Slice-based FA           |

| CMOS technology         | 65 nm                            | 28 nm                   | 65 nm                               | 28 nm                  | 65 nm                                 | 65 nm                 | 65 nm                                | 65 nm                                |                          |                          |

| RF freq. (GHz)          | 0.1-1                            | 0.1-2                   | 0.8-1                               | 0.2-2                  | 0.5-3                                 | 0.5-1.4               | 0.3-1.3                              | 0.1-1                                |                          |                          |

| RF input                | Differential                     | Differential            | Single-ended                        | Differential           | Differential                          | Differential          | Differential                         | Differential                         |                          |                          |

| BW (MHz)                | 2.5-40                           | 13                      | 30-50                               | 18                     | 1-30                                  | 2                     | 10-66                                | 5-20                                 |                          |                          |

| No. of channels         | 1                                | 3                       | 2                                   | 2                      | <100                                  | <700                  | 200-600                              | 30-900 <sup>1</sup>                  |                          |                          |

| Carrier spacing         | $A_{sp}$ (transition BW)         | >58 (2.5 $\times$ BW)   | >47 <sup>2</sup> dB (6 $\times$ BW) | >17 (0.5 $\times$ BW)  | >27 <sup>2</sup> dB (1.5 $\times$ BW) | >30 (3 $\times$ BW)   | >28 <sup>2</sup> dB (10 $\times$ BW) | >60 <sup>2</sup> dB (12 $\times$ BW) | >44 dB (3.2 $\times$ BW) | >53 dB (3.2 $\times$ BW) |

| $S_{11}$ (dB)           | <-9                              | <-8 <sup>2</sup>        | <-7 <sup>2</sup>                    | <-10 <sup>2</sup>      | <-10 <sup>2</sup>                     | <-11 <sup>2</sup>     | <-8 <sup>2</sup>                     | <-8.5                                | <-14                     |                          |

| IB $IIP_3$ (dBm)        | +8.2                             | +5 <sup>2</sup>         | +25                                 | +1.5 <sup>2</sup>      | -28                                   | -26                   | -6.9                                 | +11.5                                | +13.4                    |                          |

| OOB $IIP_3$ (dBm)       | +24                              | +44                     | +24                                 | +33                    | -4.8                                  | -15                   | +16                                  | +25                                  | +35                      |                          |

| OOB $IIP_3$ (dBm)       | ( $\Delta f$ BW = 6)             | ( $\Delta f$ BW = 12.3) | ( $\Delta f$ BW = 4.4)              | ( $\Delta f$ BW = 10)  | ( $\Delta f$ BW = 12)                 | ( $\Delta f$ BW = 8)  | ( $\Delta f$ BW = 8)                 | ( $\Delta f$ BW = 8)                 | ( $\Delta f$ BW = 8)     |                          |

| OOB $B_{1dB}$ (dBm)     | +12                              | +13                     | +9                                  | +12                    | -1                                    | -11.8                 | +4                                   | +12.6                                | +12.1                    |                          |

| OOB $B_{1dB}$ (dBm)     | ( $\Delta f$ BW = 6)             | ( $\Delta f$ BW = 12.3) | ( $\Delta f$ BW = 1)                | ( $\Delta f$ BW = 4.4) | ( $\Delta f$ BW = 1)                  | ( $\Delta f$ BW = 12) | ( $\Delta f$ BW = 8)                 | ( $\Delta f$ BW = 8)                 | ( $\Delta f$ BW = 8)     |                          |

| LO leakage (dBm)        | N/A                              | N/A                     | -45                                 | N/A                    | N/A                                   | N/A                   | N/A                                  | +71                                  | +82                      |                          |

| Sideband rej. (dB)      | N/A                              | N/A                     | N/A                                 | N/A                    | N/A                                   | N/A                   | N/A                                  | +12.6                                | +12.1                    |                          |

| Supply voltage (V)      | 1.2/1                            | 1.2/1                   | 1                                   | 1.2                    | 1.2/2.5                               | N/A                   | 1.2                                  | <69                                  | <81                      |                          |

| Power (mW)              | 75-99                            | 34-96                   | 80-97                               | 146.5-179              | 84/channel                            | 18/channel            | 19.6/channel                         | 16.25-25/channel                     | 21-31/channel            |                          |

| NF (dB)                 | 7                                | 8.1                     | 7.6 <sup>2</sup>                    | 4.3-7.6                | 4.8                                   | 3.4-4.9               | 12.8                                 | 7.9                                  | 10.8                     |                          |

| Gain (dB)               | 23                               | 16                      | -4.2                                | 13                     | 50                                    | 38.5                  | 53.2                                 | 12                                   | 10                       |                          |

| Area (mm <sup>2</sup> ) | 2.3                              | 0.8                     | 1.9                                 | 0.48                   | 7.8 <sup>2</sup>                      | 0.31                  | 1.8                                  | 1.3                                  |                          |                          |

\*Estimated from reported data. <sup>2</sup>High-linearity mode only. <sup>1</sup> Including on-chip frequency synthesizer. For achieving a rejection of the other carrier by more than 40dB. Otherwise the spacing can be arbitrarily small till the two channels become adjacent.

Figure 6.3.6: Performance summary and comparison to state-of-the-art single-channel tunable receivers/filters and multi-channel receivers.

Figure 6.3.7: Die micrograph.

**Additional References:**

- [10] R. Chen and H. Hashemi, "Reconfigurable SDR Receiver with Enhanced Front-End Frequency Selectivity Suitable for Intra-Band and Inter-Band Carrier Aggregation," *ISSCC*, pp. 346-347, Feb. 2015.

- [11] A. Agrawal and A. Natarajan, "An Interferer-Tolerant CMOS Code-Domain Receiver Based on *N*-Path Filters," *IEEE JSSC*, vol. 53, no. 5, pp. 1387-1397, May 2018.