pubs.acs.org/NanoLett Letter

# Tuning Supercurrent in Josephson Field-Effect Transistors Using h-BN Dielectric

Fatemeh Barati, <sup>⊥</sup> Josh P. Thompson, <sup>⊥</sup> Matthieu C. Dartiailh, <sup>⊥</sup> Kasra Sardashti, William Mayer, Joseph Yuan, Kaushini Wickramasinghe, Kenji Watanabe, Takashi Taniguchi, Hugh Churchill,\* and Javad Shabani\*

Cite This: Nano Lett. 2021, 21, 1915-1920

ACCESS

III Metrics & More

Article Recommendations

s Supporting Information

**ABSTRACT:** Epitaxial Al-InAs heterostructures appear as a promising materials platform for exploring mesoscopic and topological superconductivity. A unique property of Josephson junction field effect transistors (JJ-FETs) fabricated on these heterostructures is the ability to tune the supercurrent using a metallic gate. Here, we report the fabrication and measurement of gate-tunable Al-InAs JJ-FETs in which the gate dielectric in contact with the InAs is produced by mechanically exfoliated hexagonal boron nitride (h-BN) followed by dry transfer. We discuss a versatile fabrication process that enables compatibility between layered material transfer and Al-InAs heterostructures that allows us to achieve full gate-tunability of supercurrent by using only 5 nm thick h-BN flakes. Our study shows that pristine properties of epitaxial Josephson junctions, such as product of normal resistance and critical current,  $I_c R_n$ , are preserved. Furthermore, complementary measurements confirm that using h-BN dielectric changes the channel density less when compared to atomic layer deposition of  $Al_2O_3$ .

KEYWORDS: Josephson junction, two-dimensional materials, hexagonal boron nitride, dielectric, Josephson transistor

Inderstanding and engineering JJ-FETs fabricated on semiconductors with highly transparent contacts can yield a gate-controllable supercurrent. 1-9 Tuning the conductivity of the semiconductor part of a JJ-FET affects superconducting properties. For example, JJ-FETs fabricated on Al-InAs have been used for tunable superconducting qubits, the so-called "gatemon", where the qubit frequency, which depends on the value of the supercurrent, can be tuned in situ with an applied electric field. 10 Furthermore, since InAs has large spin-orbit coupling, the Al-InAs system can host topological superconductivity and Majorana bound states. 11-13 In this work we discuss a novel fabrication process for gating semiconductor-based JJ-FETs with 2D h-BN dielectric to study their quantum transport properties. This hybrid approach can reduce the unintentional doping of JJ-FETs similar to earlier work in 2D materials using h-BN encapsulation in graphene<sup>14</sup> and MoS<sub>2</sub> devices. 15

JJ-FET devices on III-V materials above the superconducting critical temperature behave practically like a III-V transistor. Historically, performance enhancement of these devices has been achieved through shrinking the gate length of transistors. However, the constant electrostatic scaling rule was not sufficient when the gate lengths of transistors reached the nanoscale. To revive the voltage scaling in order to reduce the power consumption of the integrated circuits, new materials for the gate dielectric were explored. The advent of high-k dielectrics offered one encouraging solution. However, it was

found out that special care had to be taken to produce devices with sufficiently low density of charge traps at the interface of the surface channel and dielectric for reliable device operation. While the standard atomic layer deposition of high-k oxides, e.g., Al<sub>2</sub>O<sub>3</sub>, is widely used and optimized, the research for minimizing the trap states on III/V materials continues. <sup>16–19</sup>

The ability to pick and place an ultrathin insulator flake with no chemical bonding to the InGaAs/InAs channel can minimize the trap states at the interface. In addition small flakes could be very useful when Al<sub>2</sub>O<sub>3</sub> lift off is impractical. This can be used for example as a solution for using tunable elements in microwave circuits and Gatemon qubits. <sup>10,20–22</sup> Among two-dimensional (2D) materials, h-BN, with a bandgap of 5.9 eV, has been widely used as an insulating layer. It has dangling-bond-free surface, low density of charge traps, high surface optical phonon frequency, and low microwave absorption. <sup>23–27</sup> In this Letter, we integrate h-BN as a gate dielectric for epitaxial Al/InAs JJ-FETs.

The InAs heterostructures are grown on semi-insulating InP (100) substrates using a modified Gen II molecular beam

Received: August 3, 2020 Revised: January 14, 2021 Published: February 22, 2021

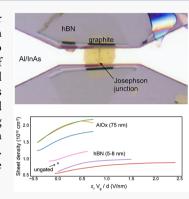

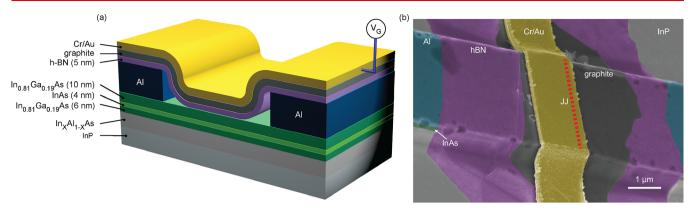

Figure 1. (a) Schematic of the gated JJ-FET geometry. The gate stack comprises a thin layer of h-BN as a gate dielectric with Cr/Au-contacted graphite as the gate electrode. (b) Scanning electron microscopy image of the JJ-FET. The location of the JJ-FET channel is shown by the red dashed line.

epitaxy machine. The step graded buffer layer, In,Al1-,As, is grown at low temperature to minimize dislocations formation due to the lattice mismatch between the active region and the InP substrate. 28,29 The quantum well consists of a 4 nm layer of InAs grown on a 6 nm layer  $In_{0.81}Ga_{0.19}As$ . The surface InAs quantum wells have relatively low electron mobilities mostly due to the direct contact of electrons to scattering impurities at the surface. A top InGaAs barrier can improve the situation by separating the quantum well from the Al interface. InGaAs is a suitable choice because it provides a soft confinement, allowing sufficient overlap of electrons with superconductor for proximity effect as well as moving the wave function away form the surface resulting in a mobility increase.<sup>30</sup> In this study, 10 nm of In<sub>0.81</sub>Ga<sub>0.19</sub>As is grown on an InAs strained quantum well. After the quantum well is grown, the substrate is cooled to below zero centigrade to promote the growth of epitaxial Al (111).31

The JJ-FET fabrication process is performed by electron beam lithography using poly(methyl methacrylate) (PMMA) as the resist. Device mesas are defined and etched using Transene type-D Al etchant followed by a III-V etch solution (see the Supporting Information (SI) for additional details). In the active region of the junction, the mesa is 4  $\mu m$  wide. In a second step, the gap between superconducting contacts of the JJ was patterned by selective etching of Al over InGaAs/InAs using Transene type-D. All presented samples have a gap of ~100 nm. To form the gate stack, h-BN and graphite flakes were mechanically exfoliated from bulk crystals onto 90 nm SiO<sub>2</sub>/Si substrates at 100 °C using a heated exfoliation method. Using an optical microscope, we selected appropriate graphite (~30 nm) and thin h-BN (~6 nm) flakes based on optical contrast and thickness uniformity. The gate stack was then transferred onto the JJ and finally contacted on top by Cr/Au. Figure 1(a) illustrates the JJ-FET schematics from substrate to the gate stack using h-BN. Voltage  $(V_G)$  can be applied to the graphite top gate (gray in Figure 1(a)) which controls the carrier density of the InAs surface channel. Figure 1(b) shows a scanning electron microscope image of the JJ-FET device with false color representing the schematic layers.

During initial device fabrication attempts, a stamp made of a thin polycarbonate (PC) film on polydimethylsiloxane (PDMS) was used to construct the graphite/h-BN stack and transfer it onto aluminum contacts. However, the chloroform used to remove the PC after transfer etched the aluminum contacts and destroyed the Al/InAs junctions, likely because of

a small concentration of HCl created in the chloroform by a reaction with oxygen. To eliminate chloroform from the fabrication process, a modified version of this technique was used to create stamps with polypropylene carbonate (PPC), which was dissolved in anisole.

Here, we focus on two JJ-FET devices A and B fabricated on nominally identical heterostructures. The only difference between these two samples is the gate dielectric. In sample A, 6 nm of hBN are used as the gate dielectric while sample B has 50 nm of Al<sub>2</sub>O<sub>3</sub> instead. The 2DEGs in these heterostructures were characterized separately by magnetoresistance measurements in van der Pauw geometry. Both samples have a density of  $7 \times 10^{11}$  cm<sup>-2</sup>. They also have an estimated mean free path  $l_e$  of 200 nm. As a consequence with the superconducting electrode gap of L = 100 nm both samples are expected to be close to the ballistic regime  $L < l_e$ . The superconducting gap of the Al was estimated to be about 210  $\mu$ eV from the critical temperature of the film in both samples  $(T_c \sim 1.4 \text{ K})$ . In both samples, the Thouless energy  $E_{\text{Thouless}} = \frac{\hbar \nu_F l_e}{2L^2}$ , where  $\nu_F$  is the Fermi velocity and L the gap of the JJ, is larger than 1 meV, which implies that our junctions are in the short limit ( $\Delta = E_{\text{Thouless}}$ ).

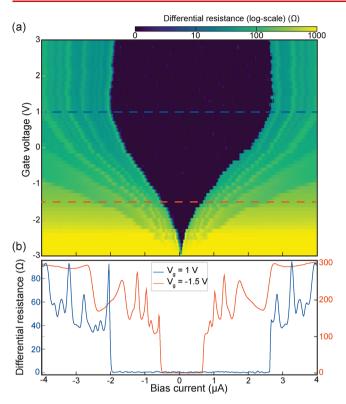

Figure 2a shows the differential resistance (dV/dI) versus measured dc bias current as a function of applied top gate voltage at 30 mK. We observed that the critical current remains nearly unchanged above  $V_{\rm G}$  > 1 V while it decreases below this value, similar to IJ-FET devices with Al<sub>2</sub>O<sub>3</sub> as the gate dielectric. As we tune the gate voltage toward more negative values, the window with zero resistance state (dark blue) becomes narrower and reaches zero at  $V_{\rm G}$  = -3 V. Figure 2b shows the differential resistance as a function of bias current extracted from panel (a). The line traces in blue and red are for  $V_{\rm G}$  = 1 V and -1.5 V, respectively. The critical current shows an asymmetric behavior that can be associated with the JJ hysteresis (see SI). The critical current is consistently higher on the cold branch where the cold branch goes from zero bias to high bias and corresponds to a lower effective electronic temperature before the transition out of the superconducting state. For example, at  $V_G = 1$  V, the critical current exhibits -2 $\mu A$  on the hot branch and 2.7  $\mu A$  on the cold branch. We observe several peaks and valleys in the region above the critical current. In the Supporting Information, we plot the conductance as a function of the voltage which allows us to interpret those as multiple Andreev reflection processes up to the fourth order.<sup>32,33</sup> These observations support a highly

**Figure 2.** (a) Differential resistance (dV/dI) of the JJ as a function of bias current and gate voltage. (b) Two line traces of panel (a) at  $V_G = 1$  and -1.5 V shown in blue and red, respectively.

transparent boundary with the superconducting contacts. In each Andreev reflection, two electrons are transferred across the junction and contribute to the current to drop the resistance, with peaks in resistance corresponding to transitions between successive orders of reflection processes in the high-transparency limit. These reflections are observed across the whole range of gate voltages and only disappear around  $V_{\rm G} = -2.5$  V, just above when supercurrent in the JJ ceases,  $V_{\rm G} = -3$  V.

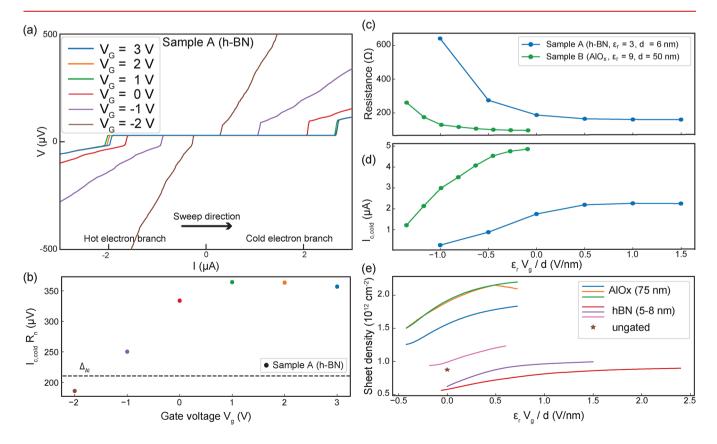

Figure 3a shows the dc transport measurement of voltage versus bias current as a function of top gate voltage. As the gate is used to deplete the 2DEG, by tuning the gate voltage from 3 V toward -2 V (color coded from blue to brown), the voltage increases and the critical current decreases. A figure of merit of JJ devices is considered to be their product of critical current multiplied by their normal state resistance. Theoretically this product is related to the induced superconducting gap and can reach  $\pi$  for a ballistic junction with perfect interfaces.<sup>34</sup> Figure 3b illustrates the gate dependence of the  $I_cR_n$  products for sample A. The negative voltage trend is very similar to JJ devices with Al<sub>2</sub>O<sub>3</sub> dielectrics. Data presented in the Supporting Information suggests that the induced gap does not vary widely with gate and is close to the parent Al gap, which allows us to evaluate the maximum of the product  $I_c R_n$  $\Delta_{\rm Al} \sim 1.7$ . While we cannot resolve changes in the induced gap, high-order MAR appear to be affected by gate voltage, suggesting that the decrease of the  $I_cR_p$  product we observe may be imparted both to the reduced mobility of the 2DEG at low density and to reduced transparency between the gated and Al-covered sections of the 2DEG.

Figure 3. (a) Voltage—current curve as a function of gate voltages from 3 V to -2 V in 1 V steps. (b)  $I_{c,cold}R_n$  as a function of gate voltage for sample A. (c)  $R_n$  as a function of gate voltage for sample A with h-BN and sample B with  $Al_2O_3$  dielectrics. (d)  $I_{c,cold}$  as a function of gate voltage for sample A with h-BN and sample B with an  $Al_2O_3$  dielectrics.

For comparison we provide data from sample B with 50 nm of Al<sub>2</sub>O<sub>3</sub> dielectric. Figure 3c makes a comparison between gate dependence of normal resistance (at high current bias) of two JJ-FETs with h-BN (sample A) and Al<sub>2</sub>O<sub>3</sub> (sample B) dielectric. Sample B shows a smaller normal resistance compared to Sample A, which suggests a higher density for Sample B. The gate efficiency of the device defined by  $\delta I_c/\delta V_C$ can also be evaluated by plotting supercurrent as a function of electric displacement field (to normalize for different thicknesses and dielectric constants of h-BN and Al<sub>2</sub>O<sub>3</sub>) which is shown in Figure 3d. Although the supercurrent is smaller in the h-BN device by a factor of 2, the overall  $I_c R_n$ values are closer (within 30%) due to higher  $R_n$ . In terms of efficiency while h-BN can be made a few monolayers, the low dielectric constant of h-BN makes the gate efficiency similar to Al<sub>2</sub>O<sub>3</sub>. While the curves overall look similar, the shift in the electric field is evident. At zero gate bias, the device with Al<sub>2</sub>O<sub>3</sub> dielectric places the curve in saturation (as seen in Figure 3c and d) while the device with h-BN dielectric is away from this region. This could be the result of a higher density in devices with Al<sub>2</sub>O<sub>3</sub> dielectric. To test whether Al<sub>2</sub>O<sub>3</sub> deposition and h-BN modify the carrier density of 2DEGs, we have made multiple small Hall bars and have deposited Al<sub>2</sub>O<sub>3</sub> and transferred larger flakes of h-BN on them. We have described the details of the Hall bar samples in the Supporting Information. The summary of our study is shown in Figure 3e. For reference, we have also added a data point from a Hall bar with no dielectric noted as ungated, which matches another measurement made on an ungated van der Pauw. While there are some variations, devices with Al<sub>2</sub>O<sub>3</sub> dielectric show an increase in density compared to the ungated reference sample up to 2-fold. On the other hand, the devices with h-BN dielectric show a smaller density change, some above and some below the reference sample. This confirms our hypothesis that h-BN introduces less doping through interface states compared to Al<sub>2</sub>O<sub>3</sub>. This becomes an important factor in the study of device physics and especially in study of topological superconductivity where interfaces play a crucial role.

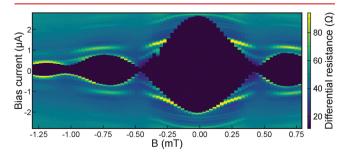

By applying an external magnetic field to the junction, the critical current of the junction is found to follow a characteristic Fraunhofer pattern. As illustrated in Figure 4 for sample A, the differential resistance oscillates as a function of the out-of-plane magnetic field. The pattern is periodic with a double-width central lobe, which suggests that the current is distributed uniformly in the junction and is not affected by distortion or wrinkles in the h-BN dielectric. We observe a slight increase of the period with the magnetic field which we

**Figure 4.** Differential resistance of sample A as a function of the bias current and out-of-plane magnetic field. The critical current presents the typical Fraunhofer pattern of a JJ in the presence of an out-of-plane magnetic field.

attribute to the reduction of the field focusing effect caused by the Al contacts. Similar observations have been reported in ref 36 and can be attributed to the large width of our contacts.

In conclusion, we have demonstrated a versatile fabrication of thin h-BN flakes with Al-InAs JJ-FET with a h-BN/graphite gate stack. These JJ-FET devices with h-BN dielectric exhibit equally pristine Josephson properties when compared to JJ-FET with  $Al_2O_3$  dielectric. Through complementary Hall bar studies we show that while the  $Al_2O_3$  deposition process increases the density of the 2DEG channel the h-BN transfer is introducing less dopants. The small footprint of the process and its flexibility in positioning the flakes together with minimal perturbation of the 2DEG density make these new devices useful for applications in superconducting logic  $^{37}$  and quantum information technologies.

#### ASSOCIATED CONTENT

## Supporting Information

The Supporting Information is available free of charge at https://pubs.acs.org/doi/10.1021/acs.nanolett.0c03183.

Additional details regarding the fabrication process along with additional measurements supporting our conclusions (PDF)

#### AUTHOR INFORMATION

## **Corresponding Authors**

Hugh Churchill – Department of Physics, University of Arkansas, Fayetteville, Arkansas 72701, United States; Email: churchill@uark.edu

Javad Shabani — Center for Quantum Phenomena, Department of Physics, New York University, New York City, New York 10003, United States; ● orcid.org/0000-0002-0812-2809; Email: js10080@nyu.edu

## **Authors**

Fatemeh Barati — Center for Quantum Phenomena, Department of Physics, New York University, New York City, New York 10003, United States

Josh P. Thompson – Department of Physics, University of Arkansas, Fayetteville, Arkansas 72701, United States

Matthieu C. Dartiailh – Center for Quantum Phenomena, Department of Physics, New York University, New York City, New York 10003, United States

Kasra Sardashti – Center for Quantum Phenomena, Department of Physics, New York University, New York City, New York 10003, United States

William Mayer – Center for Quantum Phenomena, Department of Physics, New York University, New York City, New York 10003, United States

Joseph Yuan — Center for Quantum Phenomena, Department of Physics, New York University, New York City, New York 10003, United States

Kaushini Wickramasinghe — Center for Quantum Phenomena, Department of Physics, New York University, New York City, New York 10003, United States

Kenji Watanabe — Research Center for Functional Materials, National Institute for Materials Science, Tsukuba 305-0044, Japan; © orcid.org/0000-0003-3701-8119

Takashi Taniguchi — International Center for Materials Nanoarchitectonics, National Institute for Materials Science, Tsukuba 305-0044, Japan; orcid.org/0000-0002-1467-3105

Complete contact information is available at: https://pubs.acs.org/10.1021/acs.nanolett.0c03183

## **Author Contributions**

<sup>⊥</sup>These authors contributed equally.

#### **Notes**

The authors declare no competing financial interest.

## ACKNOWLEDGMENTS

The NYU team acknowledges support from Army Research Office Agreements W911NF1810067 and W911NF1810115. J.Y. acknowledges funding from the QUACRG (BAA W911NF-17-S-0002). The Arkansas team acknowledges support from the NSF under awards DMR-1610126 and DMR-1848281. K.W. and T.T. acknowledge support from the Elemental Strategy Initiative conducted by the MEXT, Japan (JPMXP0112101001), JSPS KAKENHI (JP20H00354), and CREST (JPMJCR15F3), JST.

#### REFERENCES

- (1) Mayer, W.; Yuan, J.; Wickramasinghe, K. S.; Nguyen, T.; Dartiailh, M. C.; Shabani, J. Superconducting proximity effect in epitaxial Al-InAs heterostructures. *Appl. Phys. Lett.* **2019**, *114*, 103104.

- (2) Lee, K.; Chakram, S.; Kim, S.; Mujid, F.; Ray, A.; Gao, H.; Park, C.; Zhong, Y.; Muller, D. A.; Schuster, D. I.; Park, J. Two-Dimensional Material Tunnel Barrier for Josephson Junctions and Superconducting Qubits. *Nano Lett.* **2019**, *19*, 8287–8293.

- (3) Mayer, W.; Dartiailh, M. C.; Yuan, J.; Wickramasinghe, K. S.; Rossi, E.; Shabani, J. Gate controlled anomalous phase shift in Al/InAs Josephson junctions. *Nat. Commun.* **2020**, *11*, 1–6.

- (4) Clark, T. D.; Prance, R. J.; Grassie, A. D. C. Feasibility of hybrid Josephson field effect transistors. J. Appl. Phys. 1980, 51, 2736–2743.

- (5) Richter, A.; Koch, M.; Matsuyama, T.; Merkt, U. Transport properties of Nb/InAs(2DEG)/Nb Josephson field-effect transistors. *Supercond. Sci. Technol.* **1999**, *12*, 874–876.

- (6) Kroemer, H.; Nguyen, C.; Hu, E. L. Electronic interactions at superconductor-semiconductor interfaces. *Solid-State Electron.* **1994**, 37, 1021–1025.

- (7) Heida, J. P.; van Wees, B. J.; Klapwijk, T. M.; Borghs, G. Nonlocal supercurrent in mesoscopic Josephson junctions. *Phys. Rev. B: Condens. Matter Mater. Phys.* 1998, *57*, R5618–R5621.

- (8) Akazaki, T.; Takayanagi, H.; Nitta, J.; Enoki, T. A Josephson field effect transistor using an InAsinsertedchannel In0.52Al0.48As/In0.53Ga0.47As inverted modulation-doped structure. *Appl. Phys. Lett.* **1996**, *68*, 418–420.

- (9) Calado, V. E.; Goswami, S.; Nanda, G.; Diez, M.; Akhmerov, A. R.; Watanabe, K.; Taniguchi, T.; Klapwijk, T. M.; Vandersypen, L. M. K. Ballistic Josephson junctions in edge-contacted graphene. *Nat. Nanotechnol.* **2015**, *10*, 761–764.

- (10) Casparis, L.; Connolly, M. R.; Kjaergaard, M.; Pearson, N. J.; Kringhøj, A.; Larsen, T. W.; Kuemmeth, F.; Wang, T.; Thomas, C.; Gronin, S.; et al. Superconducting gatemon qubit based on a proximitized two-dimensional electron gas. *Nat. Nanotechnol.* **2018**, *13*, 915–919.

- (11) Fornieri, A.; et al. Evidence of topological superconductivity in planar Josephson junctions. *Nature* **2019**, *569*, 89–92.

- (12) Suominen, H.; Kjaergaard, M.; Hamilton, A.; Shabani, J.; Palmstrøm, C.; Marcus, C.; Nichele, F. Zero-Energy Modes from Coalescing Andreev States in a Two-Dimensional Semiconductor-Superconductor Hybrid Platform. *Phys. Rev. Lett.* **2017**, *119*, 176805.

- (13) Nichele, F.; Drachmann, A. C.; Whiticar, A. M.; O'Farrell, E. C.; Suominen, H. J.; Fornieri, A.; Wang, T.; Gardner, G. C.; Thomas, C.; Hatke, A. T.; Krogstrup, P.; Manfra, M. J.; Flensberg, K.; Marcus, C. M. Scaling of Majorana Zero-Bias Conductance Peaks. *Phys. Rev. Lett.* 2017, 119, 136803.

- (14) Dean, C. R.; Young, A. F.; Meric, I.; Lee, C.; Wang, L.; Sorgenfrei, S.; Watanabe, K.; Taniguchi, T.; Kim, P.; Shepard, K. L.;

- Hone, J. Boron nitride substrates for high-quality graphene electronics. *Nat. Nanotechnol.* **2010**, *5*, 722–726.

- (15) Lee, G.-H.; Cui, X.; Kim, Y. D.; Arefe, G.; Zhang, X.; Lee, C.-H.; Ye, F.; Watanabe, K.; Taniguchi, T.; Kim, P.; Hone, J. Highly Stable, Dual-Gated MoS2 Transistors Encapsulated by Hexagonal Boron Nitride with Gate-Controllable Contact, Resistance, and Threshold Voltage. ACS Nano 2015, 9, 7019–7026.

- (16) Chobpattana, V.; Son, J.; Law, J. J. M.; Engel-Herbert, R.; Huang, C.-Y.; Stemmer, S. Nitrogen-passivated dielectric/InGaAs interfaces with sub-nm equivalent oxide thickness and low interface trap densities. *Appl. Phys. Lett.* **2013**, *102*, 022907.

- (17) Shahrjerdi, D.; Tutuc, E.; Banerjee, S. K. Impact of surface chemical treatment on capacitance-voltage characteristics of GaAs metal-oxide-semiconductor capacitors with Al2O3 gate dielectric. *Appl. Phys. Lett.* **2007**, *91*, 063501.

- (18) Shahrjerdi, D.; Nah, J.; Hekmatshoar, B.; Akyol, T.; Ramon, M.; Tutuc, E.; Banerjee, S. K. Hall mobility measurements in enhancement-mode GaAs field-effect transistors with Al2O3 gate dielectric. *Appl. Phys. Lett.* **2010**, *97*, 213506.

- (19) Burek, G. J.; Hwang, Y.; Carter, A. D.; Chobpattana, V.; Law, J. J. M.; Mitchell, W. J.; Thibeault, B.; Stemmer, S.; Rodwell, M. J. W. Influence of gate metallization processes on the electrical characteristics of high-k/In<sub>0.53</sub>Ga<sub>0.47</sub>As interfaces. *J. Vac. Sci. Technol., B: Nanotechnol. Microelectron: Mater., Process., Meas., Phenom.* **2011**, 29, 040603.

- (20) Casparis, L.; Pearson, N. J.; Kringhøj, A.; Larsen, T. W.; Kuemmeth, F.; Nygård, J.; Krogstrup, P.; Petersson, K. D.; Marcus, C. M. Voltage-controlled superconducting quantum bus. *Phys. Rev. B: Condens. Matter Mater. Phys.* **2019**, *99*, 085434.

- (21) Wang, J. I.-J. Coherent control of a hybrid superconducting circuit made with graphene-based van der Waals heterostructures. *Nat. Nanotechnol.* **2019**, *14*, 120.

- (22) Sardashti, K.; Dartiailh, M. C.; Yuan, J.; Hart, S.; Gumann, P.; Shabani, J. Voltage-Tunable Superconducting Resonators: A Platform for Random Access Quantum Memory. *IEEE Transactions on Quantum Engineering* **2020**, *1*, 1–7.

- (23) Jang, S. K.; Youn, J.; Song, Y. J.; Lee, S. Synthesis and Characterization of Hexagonal Boron Nitride as a Gate Dielectric. *Sci. Rep.* **2016**, *6*, 1–9.

- (24) Huang, Z.; Alharbi, A.; Mayer, W.; Cuniberto, E.; Taniguchi, T.; Watanabe, K.; Shabani, J.; Shahrjerdi, D. Versatile construction of van der Waals heterostructures using a dual-function polymeric film. *Nat. Commun.* **2020**, *11*, 3029.

- (25) Alharbi, A.; Huang, Z.; Taniguchi, T.; Watanabe, K.; Shahrjerdi, D. Effect of Substrate Coupling on the Performance and Variability of Monolayer MoS2 Transistors. *IEEE Electron Device Lett.* **2019**, 40, 135–138.

- (26) Wang, J. I.; Rodan-Legrain, D.; Bretheau, L.; Campbell, D. L.; Kannan, B.; Kim, D. J.; Kjaergaard, M.; Krantz, P. e. a.; et al. Coherent control of a hybrid superconducting circuit made with graphene-based van der Waals heterostructures. *Nat. Nanotechnol.* **2019**, *14*, 120–125.

- (27) Jekat, F.; Pestka, B.; Car, D.; Gazibegović, S.; Flöhr, K.; Heedt, S.; Schubert, J.; Liebmann, M.; Bakkers, E. P. A. M.; SchäPers, T.; Morgenstern, M. Exfoliated hexagonal BN as gate dielectric for InSb nanowire quantum dots with improved gate hysteresis and charge noise. *Appl. Phys. Lett.* **2020**, *116*, 253101.

- (28) Shabani, J.; McFadden, A. P.; Shojaei, B.; Palmstrøm, C. J. Gating of high-mobility InAs metamorphic heterostructures. *Appl. Phys. Lett.* **2014**, *105*, 262105.

- (29) Shabani, J.; Das Sarma, S.; Palmstrøm, C. J. An apparent metalinsulator transition in high-mobility two-dimensional InAs heterostructures. *Phys. Rev. B: Condens. Matter Mater. Phys.* **2014**, *90*, 161303.

- (30) Wickramasinghe, K. S.; Mayer, W.; Yuan, J.; Nguyen, T.; Jiao, L.; Manucharyan, V.; Shabani, J. Transport properties of near surface InAs two-dimensional heterostructures. *Appl. Phys. Lett.* **2018**, *113*, 262104.

- (31) Shabani, J.; Kjaergaard, M.; Suominen, H. J.; Kim, Y.; Nichele, F.; Pakrouski, K.; Stankevic, T.; Lutchyn, R. M.; Krogstrup, P.;

- Feidenhans'l, R.; Kraemer, S.; Nayak, C.; Troyer, M.; Marcus, C. M.; Palmstrøm, C. J. Two-dimensional epitaxial superconductor-semi-conductor heterostructures: A platform for topological superconducting networks. *Phys. Rev. B: Condens. Matter Mater. Phys.* **2016**, 93, 155402.

- (32) Kjaergaard, M.; Suominen, H. J.; Nowak, M. P.; Akhmerov, A. R.; Shabani, J.; Palmstrøm, C. J.; Nichele, F.; Marcus, C. M. Transparent Semiconductor-Superconductor Interface and Induced Gap in an Epitaxial Heterostructure Josephson Junction. *Phys. Rev. Appl.* **2017**, *7*, 034029.

- (33) Pankratova, N.; Lee, H.; Kuzmin, R.; Vavilov, M.; Wickramasinghe, K.; Mayer, W.; Yuan, J.; Shabani, J.; Manucharyan, V. E. Multiterminal Josephson effect. *Phys. Rev. X* **2020**, 1.

- (34) Ambegaokar, V.; Baratoff, A. Tunneling Between Superconductors. *Phys. Rev. Lett.* **1963**, *10*, 486–489.

- (35) Likharev, K. K. Superconducting weak links. *Rev. Mod. Phys.* **1979**, *51*, 101–159.

- (36) Suominen, H. J.; Danon, J.; Kjaergaard, M.; Flensberg, K.; Shabani, J.; Palmstrøm, C. J.; Nichele, F.; Marcus, C. M. Anomalous Fraunhofer interference in epitaxial superconductor-semiconductor Josephson junctions. *Phys. Rev. B: Condens. Matter Mater. Phys.* **2017**, 95, 035307.

- (37) Wen, F.; Shabani, J.; Tutuc, E. Josephson Junction Field-Effect Transistors for Boolean Logic Cryogenic Applications. *IEEE Trans. Electron Devices* **2019**, *66*, 5367–5374.