# How Good Are 2D Transistors? An Application-specific Benchmarking Study

Hattan Abuzaid, 1) Nicholas X. Williams, 1) and Aaron D. Franklin 1,2,a)

<sup>1</sup>Department of Electrical and Computer Engineering, Duke University, Durham, North Carolina, 27708, USA

<sup>2</sup>Department of Chemistry, Duke University, Durham, North Carolina 27708, USA

## **ABSTRACT**

The research community has invested heavily in semiconducting two-dimensional (2D) materials, such as transition metal dichalcogenides (TMDs). Their stability when scaled down to a few atoms thick makes them attractive candidates to replace or supplement silicon in many future technologies. Although this sentiment is prevalent, demonstrations of 2D field-effect transistors (FETs) often do not present their data in a way that enables a straightforward comparison. For example, some papers solely use mobility as the figure of merit, while others focus on unnormalized device on-current. Here, we benchmark the performance of a selection of 2D FETs with field-corrected metrics that allow a more accurate projection of their potential; while the demonstrated methods are by no means comprehensive, they provide insight into improved benchmarking of 2D FETs going forward. Importantly, we show that appropriate benchmarking requires consideration of the specific application, with the three dominant potential application areas of front-end-of-line (FEOL) high-performance FETs, back-end-of-line (BEOL) 3Dintegrated FETs, and low-cost thin-film FETs (or TFTs) each demonstrated. We find that 2D materials have the potential to compete with silicon as the channel in scaled FEOL high-performance devices. Meanwhile, in BEOL applications, FETs from *in-situ* synthesized 2D materials have performance limited by their low crystal quality - a result of the stringent thermal budget of BEOL fabrication, which necessitates use of transferred 2D materials. In the TFT area, 2D materials are simpler to fabricate than their silicon-based counterparts and they are competitive with other material alternatives. As promising as these findings are, there remain many hurdles for 2D materials to overcome, including poor reliability, performance variability, and fabrication scalability. Continued research effort, combined with appropriate benchmarking, is strongly encouraged.

a) Author to whom correspondence should be addressed. Electronic mail: aaron.franklin@duke.edu.

Semiconducting two-dimensional (2D) materials, including transition metal dichalcogenides (TMDs) and X-enes such as black phosphorous (BP), are promising candidates for next-generation, aggressively scaled field-effect transistors (FETs).<sup>1-3</sup> Their layered nature preserves their general behavior down to a monolayer and their atomic thinness enables excellent electrostatic gating control of the channel.<sup>4-9</sup> Among 2D materials, the TMD, molybdenum disulfide (MoS<sub>2</sub>), stands out as a strong choice for n-type transistors towards complementary logic, as evidenced by the numerous experimental demonstrations in the literature.<sup>10-13</sup> Being the front-runner of 2D FETs, high-performance MoS<sub>2</sub> FETs are often employed as the indicator for 2D FETs progress towards replacing or supplementing state-of-art silicon technology. However, published reports frequently make that comparison using metrics that touch upon limited aspects of device performance instead of forming a holistic picture. For example, mobility is widely used as an ultimate figure of merit for the intrinsic quality of 2D channels, <sup>14-19</sup> even though devices with the highest reported mobilities do not necessarily have the highest on-state performance in terms of on-current (Io<sub>N</sub>).

There are two main concerns for placing a high value on mobility in scaled, high-performance 2D transistors. First, the process of extracting field-effect mobility is known for being unreliable<sup>20,21</sup> due to the high contact resistance (forming at metal-2D interfaces),<sup>22-25</sup> which dominates the total resistance of the device and obscures the intrinsic channel performance. Although most reports point to the likelihood of mobility underestimation, some also predict mobility overestimation from contact gating and other effects.<sup>26,27</sup> These complications manifest in a broad range of experimentally reported mobilities from as low as 0.02 cm<sup>2</sup>/(V•s)<sup>28</sup> to as high as 320 cm<sup>2</sup>/(V•s)<sup>29</sup> for monolayer MoS<sub>2</sub>. Second, because mobility describes the frequency of scattering events during carrier transport, its relevance in ultra-scaled devices with ballistic

channels is questionable.<sup>30</sup> Combined, these two issues demonstrate that the widely adopted mobility metric is inadequate for singularly describing the promise of 2D FETs.

For evaluating the off-state performance of 2D devices, it is useful to look at the subthreshold swing (SS) and the on/off-current ratio (I<sub>ON</sub>/I<sub>OFF</sub>). <sup>31-35</sup> Nevertheless, these two metrics alone are not comprehensive indicators. The IEEE International Roadmap for Devices and Systems (IRDS)<sup>36</sup> specifies absolute current value requirements such that I<sub>OFF</sub> is small enough for an acceptable leakage power consumption and I<sub>ON</sub> is large enough for a sufficient switching speed. Hence, ratios and swings are most meaningful when the terminal values are considered. Reporting I<sub>ON</sub> as a measure for active device performance is a good starting point, but there needs to be a thoughtful normalization to enable comparison across various technology platforms and different device configurations. For instance, it is unrealistic to compare the I<sub>ON</sub> magnitude of a dual-gated, high-k dielectric encapsulated, short-channel device to a SiO<sub>2</sub> back-gated, long-channel one. <sup>37,38</sup> It is also unmethodical to compare the performance of devices at largely disparate gate voltage overdrives (gate-source voltage minus threshold voltage, V<sub>GS</sub> – V<sub>th</sub>) or drain-source voltages.

In addition to the important considerations for on- and off-state performance metrics, it is also critical to focus on the most relevant deliverables for a particular application. 2D devices have been motivated as having broad applicability in the transistor space, yet their performance requirements differ significantly between areas from high-performance computing to thin-film applications. The most effective benchmarking approach must make appropriate comparisons amongst 2D device options while also putting these in the context of the target application.

In this work, we propose and demonstrate a benchmarking approach utilizing relevant and cross-compatible metrics to investigate the potential of 2D materials for use in high-performance (HP) transistors, back-end-of-line (BEOL, 3D-integrated) transistors, and thin-film transistors

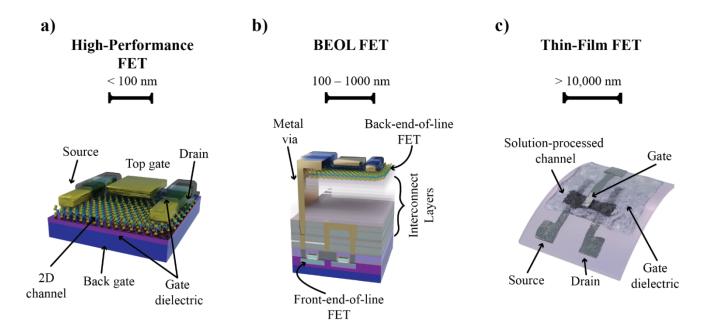

(TFTs), all of which have disparate processing and performance requirements (see Fig. 1). HP transistors power the most demanding applications, like server chipsets or state-of-the-art CPUs – maximizing performance and minimizing size is of paramount importance in these applications.<sup>30</sup> BEOL transistors are embedded during the final chip processing steps for added functionality or enhanced performance.<sup>39</sup> By utilizing 3D monolithic integration, BEOL transistors are added in the upper interconnect layers on top of the finished front-end-of-line (FEOL) stack. Process compatibility is the main consideration for this device category because of process thermal budget and fabrication cost limits. Finally, TFTs sacrifice high performance and miniaturization for low cost and versatility, with fabrication simplicity being a major requirement.<sup>30</sup> TFTs are better suited for applications like large-area and flexible electronics. An example of improved benchmarking for each of these 2D device application areas is provided herein, drawing from recently reported advances in the literature, including from the *Applied Physics Letters* special collection.

FIG. 1. Schematic illustration of different device applications where 2D materials can be employed. Scale bars indicate typical channel length dimensions. a) HP transistor. b) BEOL transistor. c) TFT.

It has been common practice to normalize I<sub>ON</sub> by dividing it by device width. Expressing  $I_{ON}$  in mA/ $\mu$ m or  $\mu$ A/ $\mu$ m makes it possible to correlate devices with unequal width or integration density and is a critical part of proper benchmarking; however, this normalization is still insufficient for a straightforward comparison. Si FinFETs are extremely miniaturized owing to state-of-the-art fabrication capabilities, which are not available to scientists creating researchgrade nanoelectronics; thus, 2D FETs typically have longer channels. This device geometry disparity is still not captured by expressing current per unit width. On the other hand, densely integrated, commercial Si FinFETs must adhere to the power density limit, which caps their drainsource voltage supply to a low value (0.7V at the 5-nm technology node as per IEEE IRDS<sup>36</sup>), while 2D FETs are frequently reported with large drain-source voltages to display their saturation behavior or compensate for their high total device resistance. We propose that these disparities can be normalized through extracting I<sub>ON</sub> from the saturation regime and including source-to-drain electric field (E<sub>SD</sub>) averaged across the channel length, which is expressed in V/μm, in the oncurrent metric. Hence, the maximum width-normalized on-current (I<sub>Max</sub>,  $\mu$ A/ $\mu$ m) over E<sub>SD</sub> has units of  $[\mu A/\mu m]/[V/\mu m] = \mu A/V = \mu S$ . Although  $I_{ON}$  can also be extracted from the linear region, that approach would introduce subjectivity into the selection of the point of extraction (the point of highest I<sub>max</sub>/E<sub>SD</sub> in the linear regime could have impractically low I<sub>ON</sub>). Devices that do not saturate will also have their performance exaggerated versus ones that saturate as desired for logic transistors. While there are shortcomings to this metric, including the nonuniformity of the electric field from source-to-drain particularly in short-channel devices, the improvements it provides in including the impact of applied fields and relative lengths are considerable. This proposed benchmarking performance metric is used throughout this paper to analyze the potential of 2D FETs in each of the previously mentioned device categories.

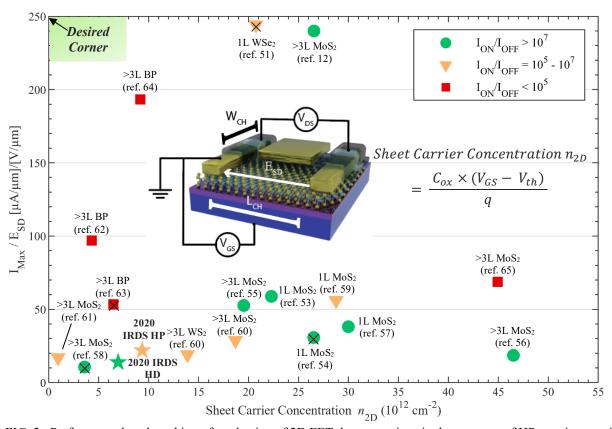

To begin, we investigated 2D FETs targeted for applications as scaled, HP transistors. Benchmarking of the performance of a selection of HP 2D FET demonstrations is shown in Fig. 2 against the 2020 IEEE IRDS projection for Si FinFETs.  $I_{Max}/E_{SD}$  is presented (as extracted from the saturation regime) with regards to the average sheet carrier concentration in the channel,  $n_{2D} = C_{ox} \times (V_{GS} - V_{th})/q$ , where  $C_{ox}$  is the gate oxide capacitance and q is the elementary charge. The use of  $n_{2D}$  streamlines comparison of devices with dissimilar gate dielectric thickness, gate dielectric constant, gating configuration, and gate voltage overdrive. Finally, the legend in Fig. 2 highlights the device's on/off-current ratio. This whole benchmarking scheme provides a basic, yet insightful, way to examine how devices with quite distinctive dimensions and configurations compare to one another.

The BP devices (ref. 62-64) reported in Fig. 2 clearly outperform silicon in terms of normalized drive current; unfortunately, they suffer from a poor on/off-current ratio (less than 10<sup>4</sup> for these specific devices) due to the small bandgap of BP. This has been a fundamental limitation of BP along with its instability in air. There is still promise for BP as researchers tackle these problems, 40-45 and further investment in BP is warranted due to its unique position as a proven p-type 2D material. 46 Quantum transport simulations on sub-10 nm monolayer BP FETs predict that they have the potential to meet the requirements of future technology nodes. 47

Another promising p-type material is WSe<sub>2</sub>, which unlike BP, has a sizable bandgap. WSe<sub>2</sub> exhibits ambipolar conduction (having similar electron and hole Schottky barriers) that can be pushed towards favorable hole transport using high work-function metals such as Pd and Au.<sup>48-50</sup> The monolayer WSe<sub>2</sub> device reported by Liu et al.<sup>51</sup> comfortably exceeds 2020 IRDS HP requirements, albeit at a higher  $n_{2D}$ . That result indicates hope for p-type 2D FETs to compete with current technology. In comparison, n-type 2D FETs demonstrations are dominated by MoS<sub>2</sub> as it

is the highest performing TMD thus far.<sup>52</sup> The majority of MoS<sub>2</sub> devices depicted in Fig. 2 had high  $I_{ON}/I_{OFF}$  ratios that met or exceeded the 2020 IRDS HD requirement. Notably, the device demonstrated by Das et al.<sup>12</sup> had substantial normalized drive current that outperformed its silicon counterpart. Further, that device<sup>12</sup> is still expected to maintain its superior position at the same reduced  $n_{2D}$  of IRDS projections. This is all assuming its current does not saturate as its  $E_{SD}$  increases (moving downwards in the plot). This assumption seems feasible considering MoS<sub>2</sub> FETs are projected to have  $I_{sat} > 1$  mA/ $\mu$ m for  $n_{2D} \ge 20$  x  $10^{12}$  cm<sup>-2</sup> at room temperature.<sup>53</sup> This is higher than the  $I_{ON}$  of 0.854 mA/ $\mu$ m for 2020 IRDS HP.

FIG. 2. Performance benchmarking of a selection of 2D FET demonstrations in the category of HP transistors using the width-normalized on-current divided by the source-to-drain electric field versus the gate field-induced carrier concentration. 1L: monolayer. >3L: more than three layers thick. 2020 IRDS HP: IRDS projected specifications for high-performance logic transistors at the 5-nm node. 2020 IRDS HD: IRDS projected specifications for high-density or low-power logic transistors at the 5-nm node. The data points with a superimposed '×' indicate cases where the  $I_{Max}/E_{SD}$  was extracted from the linear region of the output characteristics ( $I_{DS}$  vs.  $V_{DS}$ ) and thus may be exaggerated compared to the other points, which are from the saturation regime. Inset: schematic of a bottom-gated 2D FET (with added top gate which is used in some reported devices) with key parameters highlighted.  $I_{SD}$  12,51,53-65

While this benchmarking example for HP 2D FETs is not comprehensive, it does have distinct advantages compared to traditional approaches; for instance, if we were to use mobility as a sole performance indicator, the device described by Liu et al.<sup>58</sup> - with a reported field-effect mobility of 517 cm<sup>2</sup>/V•s - would be deemed the best device even though it has a low active on-state performance, as per the y-axis in Fig. 2. This inflated mobility likely stems from an extraction error, which is the main drawback for the adoption of mobility as a reliable metric despite its appeal as a material-related property. It is important to note that this benchmarking exercise ideally utilizes transistors that are operating in the same regime. If all benchmarked devices had their  $I_{Max}$ E<sub>SD</sub> extracted from the linear regime of the output characteristics then the relationship between the y-axis and x-axis in the Fig. 2 plot would include isometric lines of constant mobility, which should be extracted in the linear regime. However, most devices in Fig. 2 have I<sub>Max</sub>/E<sub>SD</sub> extracted from the saturation regime, making their comparison to the saturated silicon benchmarks reasonable, and any comparison to mobility unrealistic. Only the devices by Zhang et al.<sup>54</sup>, Liu et al.<sup>58</sup>, Liu et al.51 and Wang et al.63 have metrics from the linear regime, which could suggest that their performance is overestimated; nevertheless, their incorporation in the comparison does not alter the findings. Use of the I<sub>Max</sub>/E<sub>SD</sub> metric does carry the risk of negatively impacting devices where  $I_{Max}$  is extracted at  $V_{DS} > V_{DS,sat}$ , particularly if the current truly does completely saturate (i.e., zero output resistance). However, there are several factors that mitigate this risk: 1) most 2D FETs do not completely saturate; 2) extraction of I<sub>Max</sub> in the saturation regime is most often done just after V<sub>DS,sat</sub> (true for all devices in Fig. 2 except for Bolshakov et al.<sup>61</sup>); and 3) even when changing the extraction of  $I_{Max}/E_{SD}$  for the 5 nm node Si FinFETs to occurr at  $V_{DS} = V_{t,sat}$ , they still fall below 50 on the I<sub>Max</sub>/E<sub>SD</sub> axis, which is still below many of the 2D FET demonstrations. Overall, it is best if I<sub>Max</sub> is extracted as close to V<sub>DS,sat</sub> as possible for this benchmarking approach, but it is also

not absolutely critical. Hence, the use of this  $I_{Max}/E_{SD}$  versus  $n_{2D}$  approach alleviates some of the confusion stemming from incorrectly extracted mobility values and focuses more on on-current performance for a particular drain and gate field, with some consideration of different channel lengths.

There is still a long road ahead with hurdles and obstacles for 2D materials to overcome before they are considered a worthy replacement to incumbent HP technologies.<sup>66</sup> In fact, in the near future, it might be more practical for 2D materials to augment rather than supplant silicon technology. Scaled 2D FETs could initially find their way in applications with less stringent performance requirements, such as memory (e.g. SRAM, eDRAM). One prominent area to integrate 2D FETs on silicon platforms is BEOL fabrication. 2D transistors could be embedded within the top layers of a chip during the final metallization processes to interconnect all the individual components in an integrated circuit (IC). Being in the final steps in the process, BEOL implementation is a low-temperature step with a strict thermal budget of 400 - 500 °C.39,67,68 At elevated temperatures, the already fabricated FEOL and other components would be adversely affected. This limitation is detrimental to the crystalline quality of 2D materials grown directly onto the BEOL layers, as evidenced by the compromised condition of 2D materials grown at low temperatures using scalable synthesis techniques like chemical vapor deposition (CVD).<sup>69-72</sup> Nevertheless, there are some reports of 2D devices that are synthesized at temperatures below the process thermal limit.<sup>73-75</sup>

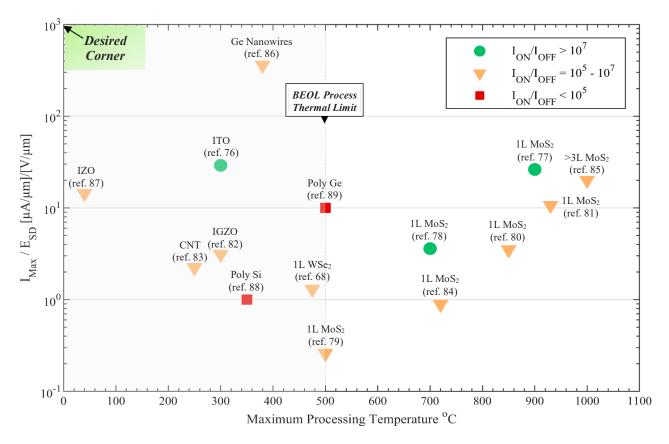

The active performance of a collection of BEOL-compatible FETs are benchmarked in Fig. 3 in relation to their maximum processing temperature. Here, BEOL compatibility is defined in two ways: 1) either the device can be processed at a temperature below the process limit (left side of figure) or 2) it can be grown with full coverage on a sacrificial substrate and subsequently

transferred and patterned on the target chip (right side of figure). The transfer approach appears to be more promising for 2D materials due to the aforementioned temperature constraint. The BEOL stack performance requirement depends on the FEOL stack it is integrated onto and there is more focus on functionality for this type of application. Therefore, it is more informative to benchmark 2D FETs against other alternatives rather than a fixed roadmap projection.

FIG. 3. Performance benchmarking of a selection of 2D FET demonstrations for potential use as BEOL transistors. The maximum process temperature will also depend on thermal exposure time, which is not captured in this plot. 1L: monolayer. >3L: more than three layers thick. CNT: carbon nanotube. ITO: indium tin oxide. IGZO: indium gallium zinc oxide. IZO: indium zinc oxide. 68,76-89

The left-hand side of Fig. 3 (with maximum processing temperatures <500 °C) indicates the difficulty of *in-situ* synthesis of 2D channels for BEOL FETs. It is important to note that the y-axis in Fig. 3 is in logarithmic scale due to the wide range of reported performance. ITO seems like an attractive option for low-temperature, low-performance BEOL implementations with its

high  $I_{ON}/I_{OFF}$  ratio. Li et al.<sup>76</sup> achieved this competitive result at an efficient  $n_{2D}$  of 0.84 x  $10^{12}$  cm<sup>-2</sup>. Greytak et al.<sup>86</sup> scored the highest active performance while observing thermal budget limits, albeit at a lower  $I_{ON}/I_{OFF}$  than ITO that is still acceptable for high-performance applications. Moving to the higher processing temperatures in the figure, an apparent upward trend in performance is observed for  $MoS_2$  devices as processing temperature goes up. This suggests that *ex-situ* synthesis is a more viable path for 2D materials in this category, where improved crystalline quality is achievable thanks to the higher thermal energy syntheses. Note that these high-temperature synthesized 2D materials will require further work to realize sufficient coverage, consistency, and transferability for BEOL FET applications.

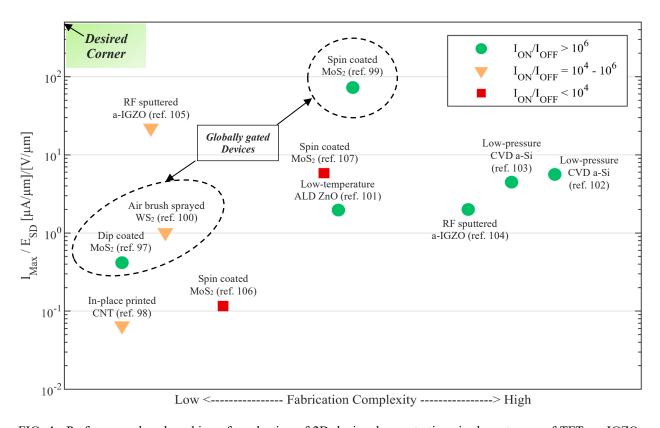

Beyond their suitability for aggressively scaled transistors, 2D layered materials enjoy a multitude of unique electronic, optoelectronic, and mechanical properties. 90-92 Those traits, coupled with the ability to form functional, solution-processed 2D films paves the path for their incorporation in thin-film transistors (TFTs). 93-96 TFTs do not have to meet stringent high-performance requirements; instead, they need to offer such benefits as low-cost fabrication, large-area synthesis, or substrate agnosticism. With cost being a dominant factor for TFT relevance, we present a similar benchmarking analysis as with the HP and BEOL FETs, but with fabrication complexity as the variable against active performance, as shown in Fig. 4.

Fabrication complexity for reported TFTs was derived by breaking down the major processing steps in each paper and scoring those quantitatively for difficulty. Scoring was done based on the sophistication of equipment used in the fabrication, along with required time and energy for processing (see supplementary material for detailed scoring of steps in each reference). Interestingly, a spin-coated MoS<sub>2</sub> TFT accomplished the highest performance in this survey of TFTs. Although the authors used a simple spin coating step to deposit the films initially, their use

of high-temperature annealing and e-beam evaporation for contact metal formation pushed their fabrication complexity towards the mid-range. The superiority of spin-coated MoS<sub>2</sub> TFTs here is made a bit uncertain as other demonstrations in the collection (ref. 106,107) fall short in active performance and I<sub>ON</sub>/I<sub>OFF</sub>. While the dip-coated MoS<sub>2</sub> device in Xi et al.<sup>97</sup> did not reach the same performance level, its simple fabrication process could make it desirable for specific applications. As a less-established process, further work is needed to optimize dip-coated MoS<sub>2</sub>-based devices and investigate proper post-processing steps to increase I<sub>Max</sub>/E<sub>SD</sub>. The same could be said about the in-place printed carbon nanotube (CNT) demonstration by Lu et al. 98 It is important to highlight that the devices reported by Gomes et al., 99 Xi et al., 97 and Higgins et al. 100 were controlled using a global gate. While that configuration is common in research demonstrations due to its simplicity, it is not viable in commercial circuits where individual control via a local gate is compulsory. Therefore, the fabrication complexity of these demonstrations might actually be higher if they follow that mandate. Moreover, globally-gated devices falsely enjoy lower contact resistance through the effect of contact gating. Consequently, their performance is slightly exaggerated. The widely used amorphous silicon (a-Si) (ref. 102,103) provided reasonable performance yet suffered from a high fabrication complexity with a lengthy and complicated procedure. Overall, 2D materials show some promise for TFT applications owing to their fabrication simplicity; though, there are some key factors still to overcome in terms of reproducibility and scalability of the processes. Hence, significant further research is needed to optimize their processing to elevate their performance to viable levels.

To summarize, we benchmarked the performance of 2D FETs across three distinct device categories using proposed, field-corrected metrics. Our proposed scheme made it possible to compare devices with dissimilar structure and under varying bias conditions. Even though these

benchmarking exercises were not exhaustive and do have shortcomings, we were able to extract useful insight into the competitiveness of 2D-layered materials in distinct future technologies by taking the specific needs of each technology into consideration. An even more comprehensive approach to appropriate benchmarking that may address lingering challenges with the approach herein would be welcome; in the meantime, the proposed benchmarking methods provide a distinct improvement over benchmarking with a single performance metric, such as unnormalized oncurrent or mobility.

FIG. 4. Performance benchmarking of a selection of 2D device demonstrations in the category of TFTs. a-IGZO: amorphous IGZO. a-Si: amorphous silicon. CNT: carbon nanotube. ALD: atomic layer deposition. Globally gated devices are indicated as these would require additional fabrication complexity in order to achieve local gates for virtually any application. 97-107

When 2D FETs are scaled down to the same dimensions as state-of-art Si FinFETs, we expect them to be a viable contender in HP transistors. MoS<sub>2</sub> looks to be the frontrunner for n-type devices, while more work is needed to pinpoint a p-type material that offers similar performance.

While this says nothing of the challenges related to synthesis, reproducibility, and process integration, at least from a device performance perspective the vision is clearer with this benchmarking approach.

A more feasible implementation for 2D materials in the nearer term is in BEOL applications. However, the crystal quality of 2D materials suffers from the thermal constraint of a BEOL process. *Ex-situ* synthesis at higher temperatures and subsequent transfer appears to be a promising route towards commercial implementation. With growing interest in the added functionality of monolithic 3D-integrated devices, 2D materials are strong contenders for continued consideration.

The advantageous properties of 2D materials and their compatibility with solution-phase processing makes them a strong candidate for TFTs. Their fabrication cost efficiency and satisfactory performance in that category are a powerful combination. However, there are many requisites for technological success that could not be captured in our analysis. 2D materials are notorious for their performance variability<sup>108</sup> and their scalable fabrication techniques are not completely mature. A paradigm shift in current fabrication approaches might be needed instead of striving to fit the mold of incumbent methods. Nonetheless, the results reported so far by the community of researchers are encouraging and they warrant substantial investment into the betterment of this exciting class of semiconductor materials. We propose that researchers perform more targeted benchmarking in the analysis of their 2D devices, by considering the impact of relative electric fields and focusing on the appropriate metrics for a specific application.

# SUPPLEMENTARY MATERIAL

Please see supplementary material for a detailed breakdown on fabrication complexity scoring for reported TFTs in Fig. 4.

## **ACKNOWLEDGMENTS**

The authors would like to acknowledge the usefulness of the 2D Device Trends database (<a href="http://2d.stanford.edu/2D\_Trends">http://2d.stanford.edu/2D\_Trends</a>) created by researchers in the Pop Lab at Stanford in preparing this work. This work was supported in part by the National Science Foundation (Grant ECCS-1915814). This work was performed in part at the Duke University Shared Materials Instrumentation Facility (SMIF), a member of the North Carolina Research Triangle Nanotechnology Network (RTNN), which is supported by the National Science Foundation (Grant ECCS-1542015) as part of the National Nanotechnology Coordinated Infrastructure (NNCI).

#### **DATA AVAILABILITY STATEMENT**

The data that support the findings of this study are available from the corresponding author upon reasonable request.

### **REFERENCES**

- <sup>1</sup> KS Novoselov, A Mishchenko, A Carvalho, and AH Castro Neto, Science **353** (6298) (2016).

- Wei Cao, Junkai Jiang, Xuejun Xie, Arnab Pal, Jae Hwan Chu, Jiahao Kang, and Kaustav Banerjee, IEEE Transactions on Electron Devices **65** (10), 4109 (2018).

- Yang Su, Chaitanya U Kshirsagar, Matthew C Robbins, Nazila Haratipour, and Steven J Koester, 2D Materials **3** (1), 011006 (2016).

- <sup>4</sup> Zeyuan Ni, Meng Ye, Jianhua Ma, Yangyang Wang, Ruge Quhe, Jiaxin Zheng, Lun Dai, Dapeng Yu, Junjie Shi, and Jinbo Yang, Advanced Electronic Materials **2** (9), 1600191 (2016).

- Ruge Quhe, Qiuhui Li, Qiaoxuan Zhang, Yangyang Wang, Han Zhang, Jingzhen Li, Xiuying Zhang, Dongxue Chen, Kaihui Liu, and Yu Ye, Physical Review Applied **10** (2), 024022 (2018).

- <sup>6</sup> Zhihui Cheng, Katherine Price, and Aaron D Franklin, IEEE Transactions on Electron Devices **65** (10), 4073 (2018).

- Han Liu, Adam T Neal, and Peide D Ye, ACS nano **6** (10), 8563 (2012).

- Youngki Yoon, Kartik Ganapathi, and Sayeef Salahuddin, Nano letters 11 (9), 3768 (2011).

- <sup>9</sup> Marta Perucchini, Enrique G. Marin, Damiano Marian, Giuseppe Iannaccone, and Gianluca Fiori, Applied Physics Letters **113** (18), 183507 (2018).

- <sup>10</sup> Branimir Radisavljevic, Aleksandra Radenovic, Jacopo Brivio, Valentina Giacometti, and Andras Kis, Nature nanotechnology **6** (3), 147 (2011).

- Sujay B Desai, Surabhi R Madhvapathy, Angada B Sachid, Juan Pablo Llinas, Qingxiao Wang, Geun Ho Ahn, Gregory Pitner, Moon J Kim, Jeffrey Bokor, and Chenming Hu, Science **354** (6308), 99 (2016).

- Saptarshi Das, Hong-Yan Chen, Ashish Verma Penumatcha, and Joerg Appenzeller, Nano letters **13** (1), 100 (2013).

- Yuan Liu, Jian Guo, Yecun Wu, Enbo Zhu, Nathan O Weiss, Qiyuan He, Hao Wu, Hung-Chieh Cheng, Yang Xu, and Imran Shakir, Nano letters **16** (10), 6337 (2016).

- Wenzhong Bao, Xinghan Cai, Dohun Kim, Karthik Sridhara, and Michael S Fuhrer, Applied Physics Letters **102** (4), 042104 (2013).

- Jingli Wang, Qian Yao, Chun-Wei Huang, Xuming Zou, Lei Liao, Shanshan Chen, Zhiyong Fan, Kai Zhang, Wei Wu, and Xiangheng Xiao, Advanced materials **28** (37), 8302 (2016).

- Deep Jariwala, Vinod K Sangwan, Dattatray J Late, James E Johns, Vinayak P Dravid, Tobin J Marks, Lincoln J Lauhon, and Mark C Hersam, Applied Physics Letters **102** (17), 173107 (2013).

- Wei Wu, Debtanu De, Su-Chi Chang, Yanan Wang, Haibing Peng, Jiming Bao, and Shin-Shem Pei, Applied Physics Letters **102** (14), 142106 (2013).

- Henan Li, Jing-Kai Huang, Yumeng Shi, and Lain-Jong Li, Advanced Materials Interfaces **6** (24), 1900220 (2019).

- <sup>19</sup> Jingsi Qiao, Xianghua Kong, Zhi-Xin Hu, Feng Yang, and Wei Ji, Nature communications 5 (1), 1 (2014).

- <sup>20</sup> Hsiao-Yu Chang, Weinan Zhu, and Deji Akinwande, Applied Physics Letters **104** (11), 113504 (2014).

- Michael S Fuhrer and James Hone, Nature nanotechnology 8 (3), 146 (2013).

- Stephen McDonnell, Rafik Addou, Creighton Buie, Robert M Wallace, and Christopher L Hinkle, ACS nano **8** (3), 2880 (2014).

- <sup>23</sup> Filippo Giubileo and Antonio Di Bartolomeo, Progress in Surface Science **92** (3), 143 (2017).

- Yuchen Du, Han Liu, Yexin Deng, and Peide D Ye, ACS nano 8 (10), 10035 (2014).

- Dongjea Seo, Dong Yun Lee, Junyoung Kwon, Jea Jung Lee, Takashi Taniguchi, Kenji Watanabe, Gwan-Hyoung Lee, Keun Soo Kim, James Hone, and Young Duck Kim, Applied Physics Letters **115** (1), 012104 (2019).

- <sup>26</sup> Chuan Liu, Gongtan Li, Riccardo Di Pietro, Jie Huang, Yong-Young Noh, Xuying Liu, and Takeo Minari, Physical Review Applied **8** (3), 034020 (2017).

- Joseph R Nasr, Daniel S Schulman, Amritanand Sebastian, Mark W Horn, and Saptarshi Das, Advanced Materials **31** (2), 1806020 (2019).

- Yi-Hsien Lee, Xin-Quan Zhang, Wenjing Zhang, Mu-Tung Chang, Cheng-Te Lin, Kai-Di Chang, Ya-Chu Yu, Jacob Tse-Wei Wang, Chia-Seng Chang, and Lain-Jong Li, Advanced materials **24** (17), 2320 (2012).

- <sup>29</sup> Branimir Radisavljevic, Michael Brian Whitwick, and Andras Kis, ACS nano 5 (12), 9934 (2011).

- <sup>30</sup> Aaron D Franklin, Science **349** (6249) (2015).

- Quoc An Vu, Sidi Fan, Sang Hyup Lee, Min-Kyu Joo, Woo Jong Yu, and Young Hee Lee, 2D Materials **5** (3), 031001 (2018).

- Yu Pan, Kunpeng Jia, Kailiang Huang, Zhenhua Wu, Guobin Bai, Jiahan Yu, Zhaohao Zhang, Qingzhu Zhang, and Huaxiang Yin, Nanotechnology **30** (9), 095202 (2019).

- Shubhadeep Bhattacharjee, Kolla Lakshmi Ganapathi, Sangeneni Mohan, and Navakanta Bhat, Applied Physics Letters **111** (16), 163501 (2017).

- Chao Li, Xiao Yan, Wenzhong Bao, Shijin Ding, David Wei Zhang, and Peng Zhou, Applied Physics Letters 111 (19), 193502 (2017).

- Felicia A McGuire, Zhihui Cheng, Katherine Price, and Aaron D Franklin, Applied Physics Letters **109** (9), 093101 (2016).

- <sup>36</sup> IEEE International Roadmap for Devices and Systems 2020 Edition <a href="https://irds.ieee.org/editions/2020/more-moore">https://irds.ieee.org/editions/2020/more-moore</a>.

- Pavel Bolshakov, Peng Zhao, Angelica Azcatl, Paul K Hurley, Robert M Wallace, and Chadwin D Young, Applied Physics Letters **111** (3), 032110 (2017).

- Durjoy Dev, Adithi Krishnaprasad, Hirokjyoti Kalita, Sonali Das, Victor Rodriguez, Jean Calderon Flores, Lei Zhai, and Tania Roy, Applied Physics Letters **112** (23), 232101 (2018).

- <sup>39</sup> Suman Datta, Sourav Dutta, Benjamin Grisafe, Jeff Smith, Srivatsa Srinivasa, and Huacheng Ye, IEEE Micro **39** (6), 8 (2019).

- Yohannes Abate, Deji Akinwande, Sampath Gamage, Han Wang, Michael Snure, Nirakar Poudel, and Stephen B Cronin, Advanced Materials **30** (29), 1704749 (2018).

- Yury Yuryevich Illarionov, Michael Waltl, Gerhard Rzepa, Joon-Seok Kim, Seohee Kim, Ananth Dodabalapur, Deji Akinwande, and Tibor Grasser, ACS nano **10** (10), 9543 (2016).

- Steven P Koenig, Rostislav A Doganov, Hennrik Schmidt, AH Castro Neto, and Barbaros Özyilmaz, Applied Physics Letters **104** (10), 103106 (2014).

- <sup>43</sup> Xi-Bo Li, Pan Guo, Teng-Fei Cao, Hao Liu, Woon-Ming Lau, and Li-Min Liu, Scientific reports **5**, 10848 (2015).

- Bingchen Deng, Vy Tran, Yujun Xie, Hao Jiang, Cheng Li, Qiushi Guo, Xiaomu Wang, He Tian, Steven J Koester, and Han Wang, Nature communications **8**, 14474 (2017).

- <sup>45</sup> Jin-Wu Jiang and Harold S Park, Physical Review B **91** (23), 235118 (2015).

- Qiyuan He, Yuan Liu, Chaoliang Tan, Wei Zhai, Gwang-hyeon Nam, and Hua Zhang, ACS nano **13** (11), 12294 (2019).

- Ruge Quhe, Xiyou Peng, Yuanyuan Pan, Meng Ye, Yangyang Wang, Han Zhang, Shenyan Feng, Qiaoxuan Zhang, Junjie Shi, and Jinbo Yang, ACS applied materials & interfaces **9** (4), 3959 (2017).

- Hui Fang, Steven Chuang, Ting Chia Chang, Kuniharu Takei, Toshitake Takahashi, and Ali Javey, Nano letters **12** (7), 3788 (2012).

- Philip M Campbell, Alexey Tarasov, Corey A Joiner, Meng-Yen Tsai, Georges Pavlidis, Samuel Graham, W Jud Ready, and Eric M Vogel, Nanoscale **8** (4), 2268 (2016).

- Hailong Zhou, Chen Wang, Jonathan C Shaw, Rui Cheng, Yu Chen, Xiaoqing Huang, Yuan Liu, Nathan O Weiss, Zhaoyang Lin, and Yu Huang, Nano letters **15** (1), 709 (2015).

- Wei Liu, Jiahao Kang, Deblina Sarkar, Yasin Khatami, Debdeep Jena, and Kaustav Banerjee, Nano letters **13** (5), 1983 (2013).

- <sup>52</sup> Siyuan Zhang, Son T Le, Curt A Richter, and Christina A Hacker, Applied physics letters **115** (7), 073106 (2019).

- Kirby KH Smithe, Chris D English, Saurabh V Suryavanshi, and Eric Pop, Nano letters **18** (7), 4516 (2018).

- <sup>54</sup> Zhenfeng Zhang, Xiaole Xu, Jian Song, Qingguo Gao, Sichao Li, Qianlan Hu, Xuefei Li, and Yanqing Wu, Applied Physics Letters **113** (20), 202103 (2018).

- Xuming Zou, Jingli Wang, Chung-Hua Chiu, Yun Wu, Xiangheng Xiao, Changzhong Jiang, Wen-Wei Wu, Liqiang Mai, Tangsheng Chen, and Jinchai Li, Advanced materials **26** (36), 6255 (2014).

- Mengwei Si, Chun-Jung Su, Chunsheng Jiang, Nathan J Conrad, Hong Zhou, Kerry D Maize, Gang Qiu, Chien-Ting Wu, Ali Shakouri, and Muhammad A Alam, Nature nanotechnology **13** (1), 24 (2018).

- <sup>57</sup> Dominik Lembke and Andras Kis, ACS nano **6** (11), 10070 (2012).

- Han Liu and D Ye Peide, IEEE electron device letters **33** (4), 546 (2012).

- <sup>59</sup> Connor J McClellan, Eilam Yalon, Kirby KH Smithe, Saurabh V Suryavanshi, and Eric Pop, presented at the 2017 75th Annual Device Research Conference (DRC), 2017 (unpublished).

- Lingming Yang, Kausik Majumdar, Han Liu, Yuchen Du, Heng Wu, Michael Hatzistergos, PY Hung, Robert Tieckelmann, Wilman Tsai, and Chris Hobbs, Nano letters **14** (11), 6275 (2014).

- Pavel Bolshakov, Ava Khosravi, Peng Zhao, Paul K Hurley, Christopher L Hinkle, Robert M Wallace, and Chadwin D Young, Applied Physics Letters **112** (25), 253502 (2018).

- Han Liu, Adam T Neal, Zhen Zhu, Zhe Luo, Xianfan Xu, David Tománek, and Peide D Ye, ACS nano 8 (4), 4033 (2014).

- <sup>63</sup> Ching-Hua Wang, Jean Anne C Incorvia, Connor J McClellan, Andrew C Yu, Michal J Mleczko, Eric Pop, and H-S Philip Wong, Nano Letters **18** (5), 2822 (2018).

- <sup>64</sup> Ling Li, Michael Engel, Damon B Farmer, Shu-jen Han, and H-S Philip Wong, ACS nano **10** (4), 4672 (2016).

- <sup>65</sup> Jiahao Kang, Wei Liu, and Kaustav Banerjee, Applied Physics Letters **104** (9), 093106 (2014).

- Natalie Briggs, Shruti Subramanian, Zhong Lin, Xufan Li, Xiaotian Zhang, Kehao Zhang, Kai Xiao, David Geohegan, Robert Wallace, and Long-Qing Chen, 2D Materials **6** (2), 022001 (2019).

- <sup>67</sup> Daniel Neumaier, Stephan Pindl, and Max C Lemme, Nature Materials **18** (6), 525 (2019).

- Azimkhan Kozhakhmetov, Joseph R Nasr, Fu Zhang, Ke Xu, Natalie C Briggs, Rafik Addou, Robert Wallace, Susan K Fullerton-Shirey, Mauricio Terrones, and Saptarshi Das, 2D Materials 7 (1), 015029 (2019).

- Dong Zhou, Haibo Shu, Chenli Hu, Li Jiang, Pei Liang, and Xiaoshuang Chen, Crystal Growth & Design **18** (2), 1012 (2018).

- Fei Chen and Weitao Su, CrystEngComm **20** (33), 4823 (2018).

- Min-Woo Kim, Ja-Yeon Kim, Yoo-Hyun Cho, Hyun-Sun Park, and Min-Ki Kwon, Journal of nanoscience and nanotechnology **18** (3), 2140 (2018).

- <sup>72</sup> Zusong Zhu, Shengbao Zhan, Jie Zhang, Guisheng Jiang, Mingfang Yi, and Jun Wen, Materials Research Express **6** (9), 095011 (2019).

- <sup>73</sup> Jihun Mun, Yeongseok Kim, Il-Suk Kang, Sung Kyu Lim, Sang Jun Lee, Jeong Won Kim, Hyun Min Park, Taesung Kim, and Sang-Woo Kang, Scientific reports **6** (1), 1 (2016).

- Yongji Gong, Zhong Lin, Gonglan Ye, Gang Shi, Simin Feng, Yu Lei, Ana Laura Elías, Nestor Perea-Lopez, Robert Vajtai, and Humberto Terrones, ACS nano 9 (12), 11658 (2015).

- Yuxi Zhao, Jeong-Gyu Song, Gyeong Hee Ryu, Kyung Yong Ko, Whang Je Woo, Youngjun Kim, Donghyun Kim, Jun Hyung Lim, Sunhee Lee, and Zonghoon Lee, Nanoscale **10** (19), 9338 (2018).

- <sup>76</sup> Shengman Li, Mengchuan Tian, Chengru Gu, Runsheng Wang, Mengfei Wang, Xiong Xiong, Xuefei Li, Ru Huang, and Yanqing Wu, presented at the 2019 IEEE International Electron Devices Meeting (IEDM), 2019 (unpublished).

- Xiangming Xu, Gobind Das, Xin He, Mohamed Nejib Hedhili, Enzo Di Fabrizio, Xixiang Zhang, and Husam N Alshareef, Advanced Functional Materials **29** (32), 1901070 (2019).

- <sup>78</sup> Connor J McClellan, C Yu Andrew, Ching-Hua Wang, H-S Philip Wong, and Eric Pop, presented at the 2019 Device Research Conference (DRC), 2019 (unpublished).

- Yu Pan, Huaxiang Yin, Kailiang Huang, Zhaohao Zhang, Qingzhu Zhang, Kunpeng Jia, Zhenhua Wu, Kun Luo, Jiahan Yu, and Junfeng Li, IEEE Journal of the Electron Devices Society 7, 483 (2019).

- <sup>80</sup> Kishan Ashokbhai Patel, Ryan W Grady, Kirby KH Smithe, Eric Pop, and Roman Sordan, 2D Materials 7 (1), 015018 (2019).

- Hua Yu, Mengzhou Liao, Wenjuan Zhao, Guodong Liu, XJ Zhou, Zheng Wei, Xiaozhi Xu, Kaihui Liu, Zonghai Hu, and Ke Deng, ACS nano **11** (12), 12001 (2017).

- K Kaneko, N Inoue, S Saito, N Furutake, H Sunamura, J Kawahara, M Hane, and Y Hayashi, presented at the 2011 International Electron Devices Meeting, 2011 (unpublished).

- <sup>83</sup> Chao-Ching Cheng, Chun-Chieh Lu, Tsu-Ang Chao, Ang-Sheng Chou, Hung-Li Chiang, Tzu-Chiang Chen, Tianqi Gao, Jianwen Zhao, Zheng Cui, and Lain-Jong Li, presented at the 2019 IEEE International Electron Devices Meeting (IEDM), 2019 (unpublished).

- Pengfei Yang, Xiaolong Zou, Zhepeng Zhang, Min Hong, Jianping Shi, Shulin Chen, Jiapei Shu, Liyun Zhao, Shaolong Jiang, and Xiebo Zhou, Nature communications **9** (1), 1 (2018).

- Ifat Jahangir, Goutam Koley, and MVS Chandrashekhar, Applied Physics Letters 110 (18), 182108 (2017).

- Andrew B Greytak, Lincoln J Lauhon, Mark S Gudiksen, and Charles M Lieber, Applied Physics Letters **84** (21), 4176 (2004).

- Yu-Lin Wang, F Ren, Wantae Lim, DP Norton, SJ Pearton, II Kravchenko, and JM Zavada, Applied physics letters **90** (23), 232103 (2007).

- A Pecora, L Maiolo, M Cuscunà, D Simeone, A Minotti, L Mariucci, and G Fortunato, Solid-state electronics **52** (3), 348 (2008).

- <sup>89</sup> Taizoh Sadoh, H Kamizuru, A Kenjo, and M Miyao, Applied physics letters **89** (19), 192114 (2006).

- <sup>90</sup> Qing Hua Wang, Kourosh Kalantar-Zadeh, Andras Kis, Jonathan N Coleman, and Michael S Strano, Nature nanotechnology 7 (11), 699 (2012).

- Jinbing Cheng, Chunlan Wang, Xuming Zou, and Lei Liao, Advanced Optical Materials 7 (1), 1800441 (2019).

- <sup>92</sup> Hao Zhan, Dan Guo, and GuoXin Xie, Nanoscale **11** (28), 13181 (2019).

- <sup>93</sup> Xiangxiang Gao, Gang Bian, and Jian Zhu, Journal of Materials Chemistry C 7 (41), 12835 (2019).

- Guohua Hu, Joohoon Kang, Leonard WT Ng, Xiaoxi Zhu, Richard CT Howe, Christopher G Jones, Mark C Hersam, and Tawfique Hasan, Chemical Society Reviews 47 (9), 3265 (2018).

- <sup>95</sup> Zhongcheng Zhu, Imran Murtaza, Hong Meng, and Wei Huang, RSC advances 7 (28), 17387 (2017).

- <sup>96</sup> Chaoliang Tan, Zhengdong Liu, Wei Huang, and Hua Zhang, Chemical society reviews 44 (9), 2615 (2015).

- <sup>97</sup> Yang Xi, Martha Isabel Serna, Lanxia Cheng, Yang Gao, Mahmoud Baniasadi, Rodolfo Rodriguez-Davila, Jiyoung Kim, Manuel A Quevedo-Lopez, and Majid Minary-Jolandan, Journal of Materials Chemistry C **3** (16), 3842 (2015).

- <sup>98</sup> Shiheng Lu, Jorge A Cardenas, Robyn Worsley, Nicholas X Williams, Joseph B Andrews, Cinzia Casiraghi, and Aaron D Franklin, ACS nano **13** (10), 11263 (2019).

- Francis Oliver Vinay Gomes, Anuj Pokle, Marko Marinkovic, Torsten Balster, Ralf Anselmann, Valeria Nicolosi, and Veit Wagner, Solid-State Electronics **158**, 75 (2019).

- Thomas M Higgins, Sean Finn, Maik Matthiesen, Sebastian Grieger, Kevin Synnatschke, Maximilian Brohmann, Marcel Rother, Claudia Backes, and Jana Zaumseil, Advanced Functional Materials **29** (4), 1804387 (2019).

- SJ Lim, Soon-ju Kwon, Hyungjun Kim, and Jin-Seong Park, Applied Physics Letters 91 (18), 183517 (2007).

- <sup>102</sup> Chen-Ming Lee and Bing-Yue Tsui, IEEE Electron Device Letters **31** (7), 683 (2010).

- Jae Hyo Park, Gil Su Jang, Hyung Yoon Kim, Sol Kyu Lee, and Seung Ki Joo, IEEE Electron Device Letters **36** (9), 920 (2015).

- Minkyu Kim, Jong Han Jeong, Hun Jung Lee, Tae Kyung Ahn, Hyun Soo Shin, Jin-Seong Park, Jae Kyeong Jeong, Yeon-Gon Mo, and Hye Dong Kim, Applied Physics Letters **90** (21), 212114 (2007).

- <sup>105</sup> CJ Chiu, SP Chang, and Shoou-Jinn Chang, IEEE Electron Device Letters **31** (11), 1245 (2010).

- Jaehyun Yang, Yeahyun Gu, Eunha Lee, Hyangsook Lee, Sang Han Park, Mann-Ho Cho, Yong Ho Kim, Yong-Hoon Kim, and Hyoungsub Kim, Nanoscale 7 (20), 9311 (2015).

- Kuanchen Xiong, Lei Li, Roderick J Marstell, Asher Madjar, Nicholas C Strandwitz, James CM Hwang, Zhaoyang Lin, Yu Huang, Xiangfeng Duan, and Alexander Göritz, IEEE Electron Device Letters **39** (9), 1453 (2018).

- Woong Choi, Demin Yin, Sooho Choo, Seok-Hwan Jeong, Hyuk-Jun Kwon, Youngki Yoon, and Sunkook Kim, Applied Physics Letters **115** (3), 033501 (2019).

Dharmraj Kotekar-Patil, Jie Deng, Swee Liang Wong, Chit Siong Lau, and Kuan Eng Johnson Goh, Applied Physics Letters **114** (1), 013508 (2019).

John Robertson, Daniel Blomdahl, Kazi Islam, Timothy Ismael, Maxwell Woody, Jacqueline Failla, Michael Johnson, Xiaodong Zhang, and Matthew Escarra, Applied Physics Letters **114** (16), 163102 (2019).