# RSSI Amplifier Design for a Feature Extraction Technique to Detect Seizures with Analog Computing

Yuqing Zhang, Nikita Mirchandani, Marvin Onabajo, Aatmesh Shrivastava

Dept. of Electrical and Computer Engineering

Northeastern University, Boston, USA

{zhang.yuq, mirchandani.n}@husky.neu.edu, {monabajo, aatmesh}@ece.neu.edu

**Abstract**—Advances of machine learning algorithms have led to improvements of seizure detection capabilities in monitoring systems based on electroencephalography (EEG). Seizure detection hardware requires accurate feature extraction, which is conventionally done in the digital domain by extracting power in different EEG frequency bands over a particular time window. This paper presents an analog counterpart to digital feature extraction. A received signal strength indicator (RSSI) circuit is used for extracting EEG power features in the analog domain. A high-precision RSSI circuit was designed in the sub-threshold domain with ultra-low power consumption and low sensitivity to process-voltage-temperature variations with CMOS technology. Simulation results show that the RSSI circuit consumes 24 nW power, and has a dynamic range of 53 dB with a linearity error of  $\pm 0.5$  dB, sufficient to accurately extract features for seizure classification. The analysis of 16 hours of patient EEG data indicates a seizure classification accuracy of 94%, and a non-seizure classification of 86%.

**Keywords**—Machine learning, analog computing, EEG-based seizure detection, support-vector machine, received signal strength indicator (RSSI), switched capacitor circuit.

## I. INTRODUCTION

Epilepsy is a neurological disorder that affects almost 2% of the world's population [1]. Epilepsy causes recurrent seizures which, apart from causing significant discomfort and poor quality of life for patients, can also lead to dangers of accidents, fall, and even death. An accurate treatment of epilepsy involves tracking and profiling of seizures to administer the correct medication. However, current treatment strategies, which include interviewing patients or keeping them in the hospital for a long period to capture a seizure episode, are either inaccurate or impractical [2]. For an accurate characterization of the onset of seizures, not only do we need to continuously monitor the EEG signals, but we also have to do it in an unobtrusive fashion such that the day to day activity of a patient is not affected.

A wearable device that can continuously monitor EEG outside of a hospital will suit this need. However, wearable devices can monitor EEG only for a limited duration due to the relatively high power consumption involved in EEG acquisition and processing. In recent years, several wearable devices and integrated circuit design methods have been introduced to acquire and process EEG signals [3]–[6]. Once the EEG signals have been acquired, the data can be used for the detection of seizures.

This work was supported in part by the National Science Foundation under award #1812588.

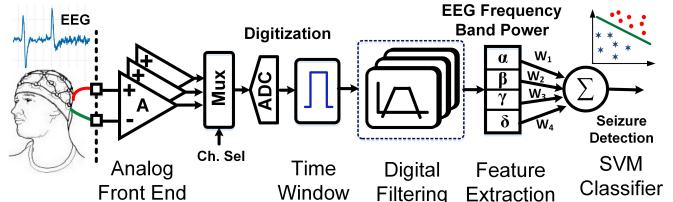

Fig. 1: Seizure classification overview of a conventional EEG processing system using a digital computing based SVM classifier.

Often, the raw EEG data is directly presented to a doctor. However, recent advances in machine learning have led to the development of seizure detection capability within EEG monitoring systems. Seizure onset detection involves the acquisition of EEG signals, and the extraction of features that show abnormal activity. Once features have been extracted, they can be fed to a linear support-vector machine (SVM) classifier to differentiate between seizure and non-seizure observations [7]–[9]. Fig. 1 shows the conventional system-on-chip (SoC) architecture for seizure detection. The processing chain consists of an analog front end (AFE) with relatively high power, followed by an analog-to-digital converter (ADC) and digital signal processing (DSP).

DSP requirements often dictate the SoC architecture, which can involve large memory requirements for data storage and digital filtering needs, significant computing infrastructure such as parallel multiplier and adders (for multiply and accumulate (MAC) operations [10]) and high fidelity data acquisition. Such SoCs using feature extraction and classification capabilities can consume power in the  $\mu\text{W}$  range and chip sizes up to  $5\text{mm}^2$  [9], [11]. There is a need to enable seizure classification engines that can operate continuously from harvested energy with power consumption less than 100s of nW for state-of-the-art internet-of-things (IoT) sensors [12], [13]. In this paper, we present an ultra-low power (ULP) EEG classification system using an analog computing based feature extraction technique. The proposed solution overcomes the variability issues of analog computing to leverage its potential to realize an SVM classification engine with low area and power overhead.

## II. ANALOG COMPUTING BASED SEIZURE CLASSIFIER

Analog computing incorporates vast amount of information processing per transistor to realize a few orders of magnitude higher power and area efficiency compared to digital computing [14]–[16]. Recently, an EEG monitoring device was reported that achieves a power consumption of 950 nW

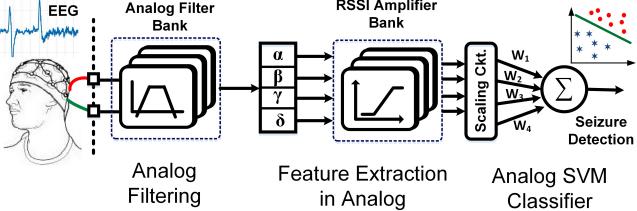

Fig. 2: Proposed seizure classification technique for an EEG system using analog computing based SVM classifier.

by employing an analog feature extraction technique [17]. We propose an analog feature extraction technique that will significantly reduce the power consumption and area of an EEG classification engine. Fig. 2 shows the architecture of our proposed EEG system using analog computing based feature extraction and classification engine.

The accuracy of seizure classification depends on the features being fed to the SVM Classifier. Typically, EEG signals are studied by dividing the EEG power spectra in different frequency bands (called delta ( $\delta$ ), theta ( $\theta$ ), alpha ( $\alpha$ ), beta ( $\beta$ ), and gamma ( $\gamma$ )). Each spectral band exhibits characteristic patterns based on the level of consciousness, external stimuli, and other neural responses. Disorders such as epilepsy can alter the power spectrum of the EEG frequency bands [18]–[20]. Conventionally, the energy in different EEG frequency bands is used as a feature for classification. EEG data from all channels is sent through a filter bank consisting of 5 to 7 bandpass filters. Energy in each spectral band is calculated for a given time window, and a feature vector is formed [7], [8].

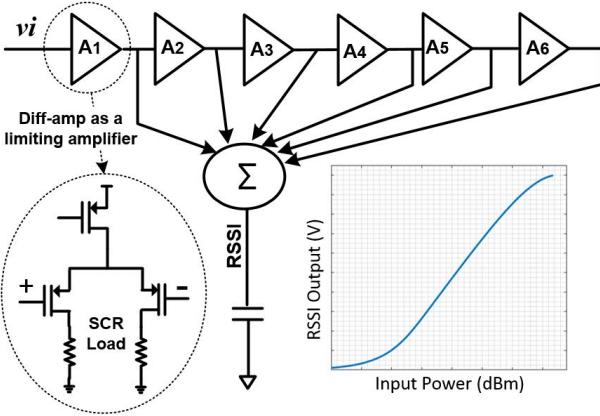

We propose to extract features, i.e. the power in EEG spectral bands, using analog based received signal strength indicator (RSSI) circuit as detailed in Fig. 2 to present to the classifier. RSSI circuit consists of several cascaded differential amplifier stages to constitute a cascaded limiting amplifier structure to realize a logarithmic amplifier [21]. This circuit, therefore, provides the power level of an incoming signal in analog. The RSSI circuit can consume a small amount of power when biased in the sub-threshold domain. Further, a high accuracy sub-threshold based constant  $g_m$  biasing technique can be leveraged to limit process, voltage, and temperature (PVT) variations [22].

We establish the viability of the analog RSSI-based feature extraction by utilizing it to detect the onset of seizures in patient EEG data. A MATLAB model of the RSSI transfer function is used to provide a feature vector to a linear SVM classifier. Analysis of 16 hours of patient EEG data shows a seizure classification accuracy of 94%, and a non-seizure classification of 86%. The following sections explain the design and simulation results of the proposed RSSI amplifier.

### III. ANALOG COMPUTING CIRCUITS

The RSSI circuit is composed of a series of cascaded limiting amplifiers. In this paper, we use a switched capacitor differential amplifier (diff-amp) as the limiting amplifier for the RSSI circuit. Six such diff-amps are cascaded to realize enough gain and linearity for the RSSI. Typically, the amplitude of EEG signal is from a few  $\mu$ V to 100s of  $\mu$ V [23]. The

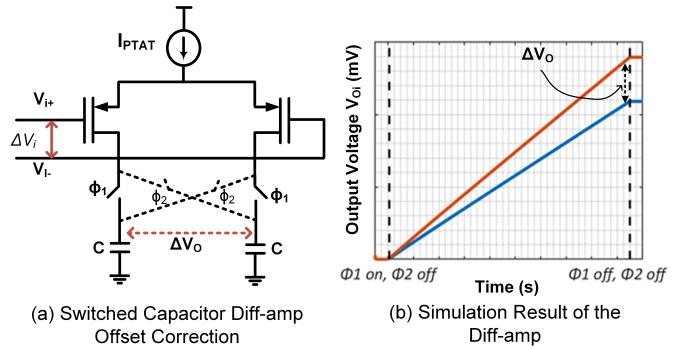

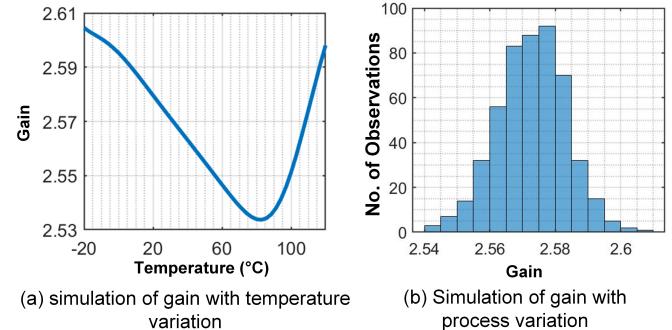

Fig. 3: Switched capacitor differential amplifier circuit with its simulation results.

dynamic range of RSSI circuit should be over 40 dB to meet the EEG signal variation [11]. Further, the AFE and filters will provide additional gain to set the minimum input voltage for RSSI around 0.25mV. We also achieve low linearity error ( $\pm 0.5$  dB) in RSSI to realize accurate classification results.

#### A. Switched Capacitor Differential Amplifier

ULP differential amplifiers with nano-amp bias current cannot use a resistive load due to unrealizable resistor values needed (100s of  $M\Omega$ ). For this reason, we use a switched capacitor load to emulate a resistor. A large resistor can be emulated with a small capacitor. Fig. 3(a) shows the circuit architecture of our diff-amp circuit that utilizes capacitor C as the load. This circuit operates in the following manner: The capacitor is at reset before  $t=0$  with it being discharged to ground. When input voltage  $\Delta V_i$  is applied, the load capacitors will start charging. However due to differential input voltage, each capacitor will charge with different current, and the output voltage after time  $t=T_{ON}$  will be given by

$$\Delta V_O = \Delta V_i \frac{g_m T_{ON}}{C} \quad (1)$$

Equation 1 reveals that the desired resistor can be realized using the capacitor C and time  $T_{ON}$  with  $R=T_{ON}/C$ . Further, the diff-amps are designed to be PVT invariant. To that end, the input transistors are operated in the sub-threshold region, and are biased with a PTAT (proportional to absolute temperature) current source. This ensures that the transconductance of the input transistors is constant:

$$g_m = \frac{I_{PTAT}}{\eta V_t} \quad (2)$$

With this biasing configuration, the PTV variation of the diff-amp can be reduced significantly. The only process dependent component that remains in the circuit's operation is C. However, the effect of C can also be minimized if the PTAT current reference is realized using a switched capacitor bias [22]. Consequently, the diff-amp exhibits a very small gain variation. We designed our diff-amp to have a gain of 2.57 with a  $T_{ON}$  of 20  $\mu$ s with a load cap of 1  $pF$ .

#### B. Offset Correction

The precision of the amplifier circuit is affected by the offset arising from device mismatches. Since the output of each diff-amp stage is fed as input to the next stage in the RSSI circuit,

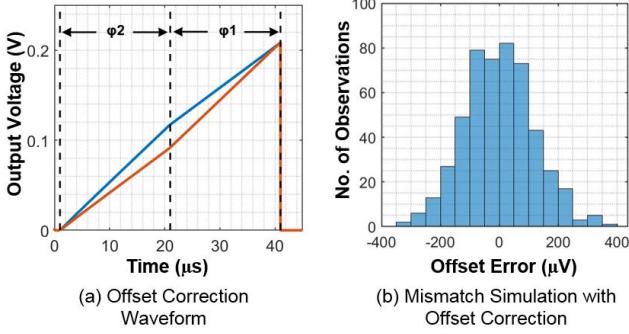

**Fig. 4:** Offset correction waveform and error simulation. the error introduced by offset grows exponentially with the number of stages. The error at the RSSI output is

$$\Delta V_{OUT,err} = \sum_{i=1}^6 k^i (V_{OS}) \quad (3)$$

where  $k = g_m T_{ON} / C$  is the gain of the amplifier, and  $V_{OS}$  is the offset of the amplifier. Hence, an offset correction technique is needed to ensure precision of the RSSI output. Figure 3 also includes an offset cancellation technique that is implemented in the differential amplifier stage by adding phase  $\phi_2$ . If no input signal is applied in phase  $\phi_2$ , then the voltage on the load capacitors at the end of phase  $\phi_2$  is

$$\Delta V_O = \frac{g_m T_{ON}}{C} (V_{OS}) \quad (4)$$

In the next phase  $\phi_1$ , normal operation is resumed. The load voltage of the capacitors with inputs reversed is now given by,

$$\Delta V_O = \frac{g_m T_{ON}}{C} (-V_{OS}) \quad (5)$$

which is added to the voltage given by (4), hence cancelling the offset.

Fig. 4(a) shows the simulated output voltage in phase  $\phi_2$  and  $\phi_1$  when an offset of 10mV is introduced at the input. At the end of phase  $\phi_1$ , the difference in the output voltage is reduced to 250μV, suppressing the input offset by 32dB.

Functionality of the offset cancellation circuit was tested by running Monte Carlo mismatch simulations with zero input. Fig 4(b) shows the output voltage at the end of phase  $\phi_1$ . The  $3\sigma$  error was found to be 351μV.

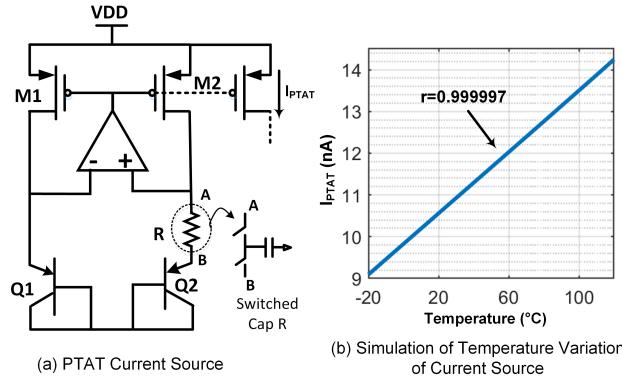

### C. Current Source

We explained in Section III.A that the differential amplifier's input transistors are biased to obtain a constant  $g_m$ . This is achieved by biasing them with a PTAT current source, shown in Fig. 5. A conventional BJT based current source was modified to replace the poly resistor with a switched capacitor based resistor (SCR). Since capacitors are less prone to variations with process and temperature, the PTAT current obtained is very linear. The SCR resistance is given by,

$$R = \frac{1}{f_1 C_1} \quad (6)$$

where  $f_1$  is the reference clock frequency. The PTAT current is given by,

$$I_{PTAT} = V_T \ln(K) f_1 C_1 \quad (7)$$

**Fig. 5:** PTAT Current Source and its simulation with temperature.

It can be seen that the gain of the diff-amp will be constant with the above biasing configuration using equations 1 and 2. We simulated our proposed diff-amp circuit. Fig. 6(a) shows the variation of the gain with temperature for a range of  $-20^{\circ}\text{C}$  to  $120^{\circ}\text{C}$ . The temperature variation of the gain of the single stage differential amplifier is 2.88%. The temperature variation of the gain is increased due to non-idealities of switches  $\phi_1$ .

The parasitic capacitances of the switch cause the current through the switches to increase slowly when it is switched on. This introduces an error in the output voltage. Small switches are designed to reduce the effect of parasitic capacitances. Another source of error is charge sharing due to switches  $\phi_1$  and  $\phi_2$  switching simultaneously. A small 'dead' time of 1  $\mu\text{s}$  is introduced to reduce error due to charge sharing. Fig 6(b) shows the gain variation with process variability. The  $3\sigma$  variation is found to be 0.033 for an average gain of 2.57.

### IV. RSSI CIRCUIT ARCHITECTURE

The RSSI circuit is composed of six diff-amps cascaded together as shown in Fig. 7. The first differential amplifier provides an output after time  $T_{ON}$ , after which the second differential amplifier is enabled. Similarly, amplifier  $A_3$  is enabled after time  $2T_{ON}$ , and the output at the end of amplifier  $A_6$  is obtained after  $6T_{ON}$ . The output of each stage is collected on the capacitors of the differential amplifiers. These output capacitors are then connected in parallel at the end of  $6T_{ON}$  to sum the outputs of each stage. The RSSI output voltage corresponding to the signal strength can be given as,

$$V_{RSSI} = \frac{1}{6} \sum_{i=1}^6 \Delta V_{O_i} \quad (8)$$

**Fig. 6:** Process and temperature variation of the diff-amp gain.

Fig. 7: Circuit architecture and operation of the RSSI.

The amplitude of EEG signals can vary greatly between seizure and non-seizure activity, and from patient to patient. Thus, the RSSI circuit requires an adequate dynamic range to process these signals which depends on the gain and number of stages of the amplifiers cascaded together.

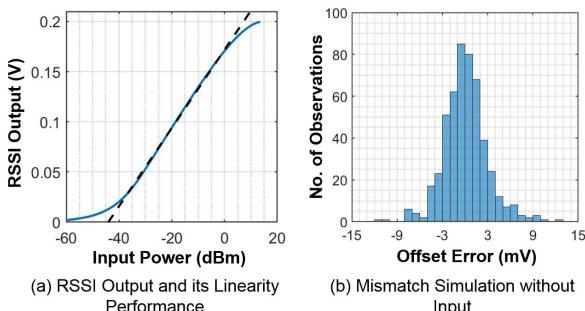

## V. SIMULATION RESULTS

Fig. 8(a) shows the RSSI output waveform with varying levels of input power. The dynamic range achieved is 53 dB, which enables the RSSI circuit to detect an input signal level of 250  $\mu$ V. Apart from the voltage compression at both ends, the maximum error observed is  $\pm 0.5$  dB for the linear range. High linearity is achieved in this architecture because the outputs at every stage are summed together, regardless of the input power. This improves the linearity in comparison to conventional architectures, where the amplifiers that are not saturated introduce an error [21].

The output error of the complete RSSI circuit was estimated with the help of Monte Carlo simulations. Fig. 8(b) shows that the  $3\sigma$  variation after 500 runs is 9mV. The total power consumption was found to be 24nW. The amplifiers are turned on only for the duration of  $T_{ON}$ , thus saving power. Table I lists the simulated performance metrics in comparison to other state-of-the art RSSI circuits.

## VI. FEATURE EXTRACTION WITH RSSI BLOCKS

The proposed RSSI circuit was used for a seizure detection application using EEG data [28]. The complete analog front-end, along with the RSSI circuit was modelled in MATLAB

Fig. 8: Linearity and mismatch performance of the RSSI circuit.

TABLE I: PERFORMANCE COMPARISON

|                          | This work | [24]     | [25]     | [26]     | [27]      | [21]      |

|--------------------------|-----------|----------|----------|----------|-----------|-----------|

| Process                  | 65 nm     | 180 nm   | 600 nm   | 65 nm    | 350 nm    | 350 nm    |

| VDD (V)                  | 1         | 1.8      | 2        | 1 or 3   | 3         | 2         |

| Dynamic Range (dB)       | 53        | 70       | 75       | 60       | 80        | 65        |

| Power                    | 24 nW     | 20 mW    | 6.2 mW   | 8 mW     | 5mA-13mA  | 2.2 mW    |

| Linearity Error (dB)     | $\pm 0.5$ | $\leq 1$ | $\leq 1$ | $\leq 1$ | $\pm 0.7$ | $\pm 0.7$ |

| Settling Time ( $\mu$ s) | 120       | 20       | N/A      | N/A      | N/A       | N/A       |

to extract features for the detection of seizure onsets. As visualized in Fig. 2, the front end consists of a bank of analog bandpass filters to split the incoming EEG data into four different frequency bands. The filters provide a gain of 30 dB, and the output signals are provided to the bank of RSSI amplifiers to obtain the signal strength in each frequency band.

The RSSI circuit was modelled as a moving RMS function followed by the transfer function of the RSSI. Data from 23 EEG channels, acquired over 16 hours was provided to the linear SVM classifier. A classification accuracy of 94% and 86% were obtained for classifying the seizures and non-seizures respectively.

Table II compares the proposed RSSI based feature extraction (FE) technique with other reported works. Here, we focus on the performance of our computing circuit compared to the computing circuits of other works. The power consumption of the peripheral circuits such as the AFE and ADC is removed, and only the computing power consumption is compared. Since the RSSI circuit consumes a power of 24 nW, we can achieve a lower power of 96 nW per channel while dividing the EEG signal into four frequency bands for FE. The proposed approach has a classification accuracy comparable to other reported works.

TABLE II: FEATURE EXTRACTION PARAMETERS

|                             | This work* | [11]     | [8]   | [29]  | [30]      |

|-----------------------------|------------|----------|-------|-------|-----------|

| FE Power ( $\mu$ W/Channel) | 0.096      | 0.48     | 100   | 7     | 33        |

| % of Seizure Detected       | 94%        | 98.5%    | 84.4% | 95.1% | 96%       |

| False Positive Rate         | 14%        | 4.4/hour | 4.5%  | 0.94% | 0.15/hour |

| # of Channel Used           | 23         | 8        | 8     | 8     | 18        |

\* Simulation based results

## VII. CONCLUSION

The paper presented an analog alternative to conventional feature extraction. Analog feature extraction was performed based on the model of an RSSI circuit to extract signal strength in the incoming EEG frequency bands. The RSSI circuit was designed by cascading differential amplifiers with switched capacitor loads to reduce the effects of PVT variations. A low-power, high-linearity RSSI circuit consuming 24 nW power and 53 dB dynamic range was designed and simulated.

## REFERENCES

- [1] D. Hirtz, D. J. Thurman, K. Gwinn-Hardy, M. Mohamed, A. R. Chaudhuri, and R. Zalutsky, "How common are the "common" neurologic disorders?," *Neurology*, vol. 68, no. 5, pp. 326–337, 2007.

- [2] R. S. Fisher, D. E. Blum, B. DiVentura, J. Vannest, J. D. Hixson, R. Moss, S. T. Herman, B. E. Fureman, and J. A. French, "Seizure diaries for clinical research and practice: limitations and future prospects," *Epilepsy Behavior*, pp. 304–310, May. 2012.

- [3] T. R. Mullen, C. A. E. Kothe, Y. M. Chi, A. Ojeda, T. Kerth, S. Makeig, T. Jung, and G. Cauwenberghs, "Real-time neuroimaging and cognitive monitoring using wearable dry EEG," *IEEE Transactions on Biomedical Engineering*, vol. 62, pp. 2553–2567, Nov 2015.

- [4] G. Li, B. Lee, and W. Chung, "Smartwatch-based wearable EEG System for Driver Drowsiness Detection," *IEEE Sensors Journal*, vol. 15, pp. 7169–7180, Dec 2015.

- [5] J. Xu, S. Mitra, C. Van Hoof, R. F. Yazicioglu, and K. A. A. Makinwa, "Active Electrodes for Wearable EEG Acquisition: Review and Electronics Design Methodology," *IEEE Reviews in Biomedical Engineering*, vol. 10, pp. 187–198, 2017.

- [6] C. Chang, S. A. Zahrai, K. Wang, L. Xu, I. Farah, and M. Onabajo, "An Analog Front-End Chip With Self-Calibrated Input Impedance for Monitoring of Biosignals via Dry Electrode-Skin Interfaces," *IEEE Transactions on Circuits and Systems I: Regular Papers*, vol. 64, pp. 2666–2678, Oct 2017.

- [7] N. Verma, A. Shoeb, J. Bohorquez, J. Dawson, J. Guttag, and A. P. Chandrakasan, "A Micro-Power EEG Acquisition SoC With Integrated Feature Extraction Processor for a Chronic Seizure Detection System," *IEEE Journal of Solid-State Circuits*, vol. 45, pp. 804–816, April 2010.

- [8] J. Yoo, L. Yan, D. El-Damak, M. A. B. Miyazaki, A. H. Shoeb, and A. P. Chandrakasan, "An 8-Channel Scalable EEG Acquisition SoC With Patient-Specific Seizure Classification and Recording Processor," *IEEE Journal of Solid-State Circuits*, vol. 48, pp. 214–228, Jan 2013.

- [9] M. A. B. Miyazaki and J. Yoo, "A 1.52  $\mu$ J/classification patient-specific seizure classification processor using Linear SVM," in *Proc. IEEE International Symposium on Circuits and Systems (ISCAS)*, pp. 849–852, May 2013.

- [10] J. T. Kao, M. Miyazaki, and A. R. Chandrakasan, "A 175- $mv$  multiply-accumulate unit using an adaptive supply voltage and body bias architecture," *IEEE Journal of Solid-State Circuits*, vol. 37, pp. 1545–1554, Nov 2002.

- [11] B. G. Do Valle, S. S. Cash, and C. G. Sodini, "Low-Power, 8-Channel EEG Recorder and Seizure Detector ASIC for a Subdermal Implantable System," *IEEE Transactions on Biomedical Circuits and Systems*, vol. 10, pp. 1058–1067, Dec 2016.

- [12] N. Shafiee, S. Tewari, B. Calhoun, and A. Shrivastava, "Infrastructure Circuits for Lifetime Improvement of Ultra-Low Power IoT Devices," *IEEE Transactions on Circuits and Systems I: Regular Papers*, vol. 64, pp. 2598–2610, Sep. 2017.

- [13] D. Blaauw, D. Sylvester, P. Dutta, Y. Lee, I. Lee, S. Bang, Y. Kim, G. Kim, P. Pannuto, Y. . Kuo, D. Yoon, W. Jung, Z. Foo, Y. . Chen, S. Oh, S. Jeong, and M. Choi, "IoT design space challenges: Circuits and systems," in *2014 Symposium on VLSI Technology (VLSI-Technology): Digest of Technical Papers*, pp. 1–2, June 2014.

- [14] N. Guo, Y. Huang, T. Mai, S. Patil, C. Cao, M. Seok, S. Sethumadhavan, and Y. Tsividis, "Corrections to "Energy-Efficient Hybrid Analog/Digital Approximate Computation in Continuous Time" [jul 16 1514–1524]," *IEEE Journal of Solid-State Circuits*, vol. 53, pp. 1870–1870, June 2018.

- [15] K. Jia, Z. Liu, F. Qiao, X. Liu, Q. Wei, and H. Yang, "AICNN: Implementing Typical CNN Algorithms with Analog-to-Information Conversion Architecture," in *2017 IEEE Computer Society Annual Symposium on VLSI (ISVLSI)*, pp. 80–85, July 2017.

- [16] N. Mirchandani and A. Shrivastava, "Cmos based ultra-low power high-precision analog vector matrix multiplication circuit with 0.1for vision application," in *2019 IEEE 62nd International Midwest Symposium on Circuits and Systems (MWSCAS)*, pp. 1139–1142, Aug 2019.

- [17] S. Iranmanesh and E. Rodriguez-Villegas, "A 950 nW Analog-Based Data Reduction Chip for Wearable EEG Systems in Epilepsy," *IEEE Journal of Solid-State Circuits*, vol. 52, pp. 2362–2373, Sep. 2017.

- [18] C. Nystrom, M. Matousek, and T. Hallstrom, "Relationships between EEG and clinical characteristics in major depressive disorder," *Acta Psychiatrica Scandinavica*, vol. 73, no. 4, pp. 390–394, 1986.

- [19] C. Herrmann and T. Demiralp, "Human EEG gamma oscillations in neuropsychiatric disorders," *Clinical Neurophysiology*, vol. 116, no. 12, pp. 2719 – 2733, 2005.

- [20] P. Perros, E. S. Young, J. J. Ritson, G. W. Price, and P. Mann, "Power spectral EEG analysis and EEG variability in obsessive-compulsive disorder," *Brain Topography*, vol. 4, pp. 187–192, Mar 1992.

- [21] J. Ramos, J. L. Ausín, J. F. Duque-Carrillo, and G. Torelli, "Design of limiting/logarithmic amplifier for wideband bioimpedance measuring devices," in *2010 Biomedical Circuits and Systems Conference (BioCAS)*, pp. 290–293, Nov 2010.

- [22] N. Mirchandani and A. Shrivastava, "High Stability Gain Structure and Filter Realization with less than 50 ppm/° C Temperature Variation with Ultra-low Power Consumption using Switched-capacitor and Sub-threshold Biasing," in *Proc. IEEE International Symposium on Circuits and Systems (ISCAS)*, pp. 1–5, May 2018.

- [23] P. Campisi, D. La Rocca, and G. Scarano, "EEG for Automatic Person Recognition," *Computer*, vol. 45, pp. 87–89, July 2012.

- [24] S. Lee, Y. Song, and S. Nam, "Fast RSSI circuit using novel power detector for wireless communication," in *2008 International SoC Design Conference*, vol. 01, pp. I–9–I–12, Nov 2008.

- [25] Po-Chiun Huang, Yi-Huei Chen, and Chorng-Kuang Wang, "A 2-V 10.7-MHz CMOS limiting amplifier/RSSI," *IEEE Journal of Solid-State Circuits*, vol. 35, pp. 1474–1480, Oct 2000.

- [26] J. Jang, J. Lee, K. Lee, J. Lee, M. Kim, Y. Lee, J. Bae, and H. Yoo, "A Four-Camera VGA-Resolution Capsule Endoscope System With 80-Mb/s Body Channel Communication Transceiver and Sub-Centimeter Range Capsule Localization," *IEEE Journal of Solid-State Circuits*, vol. 54, pp. 538–549, Feb 2019.

- [27] Chun-Pang Wu and Hen-Wai Tsao, "A 110-MHz 84-dB CMOS programmable gain amplifier with integrated RSSI function," *IEEE Journal of Solid-State Circuits*, vol. 40, pp. 1249–1258, June 2005.

- [28] A. Shoeb and J. Guttag, "Application of Machine Learning to Epileptic Seizure Detection," in *Proceedings of the 27th International Conference on International Conference on Machine Learning, ICML'10*, (USA), pp. 975–982, Omnipress, 2010.

- [29] M. A. Bin Miyazaki and J. Yoo, "A 1.83  $\mu$ J/Classification, 8-Channel, Patient-Specific Epileptic Seizure Classification SoC Using a Non-Linear Support Vector Machine," *IEEE Transactions on Biomedical Circuits and Systems*, vol. 10, pp. 49–60, Feb 2016.

- [30] M. Shoaib, N. K. Jha, and N. Verma, "A compressed-domain processor for seizure detection to simultaneously reduce computation and communication energy," in *Proceedings of the IEEE 2012 Custom Integrated Circuits Conference*, pp. 1–4, Sep. 2012.