# Heterogeneous Integration for Silicon Photonic Systems: Challenges and Approaches

John M. Dallesasse, <sup>1</sup> John A. Carlson, <sup>1</sup> Manaav Ganjoo, and Leah Espenhahn <sup>1</sup>University of Illinois at Urbana-Champaign, Champaign, IL USA, jdallesa@illinois.edu

## **Abstract**

The promise of silicon integrated circuits with their electronic or photonic functionality enhanced via heterogeneous integration has motivated significant work in understanding and overcoming the barriers to realizing such an IC. Additional hurdles must be overcome when integrating devices that are highly temperature variation sensitive to such as semiconductor lasers. Challenges in the heterogeneous integration process will be reviewed, and approaches for heterogeneous integration that have the potential to enable silicon ICs with enhanced functionality will be discussed in the context of integrated photonic systems.

(Keywords: Heterogeneous Integration, Silicon Photonics, Manufacturing, CMOS)

# Introduction

Enhancing the functionality of silicon through the integration of other materials such as III-V semiconductors has been recognized as a path to overcoming limitations imposed by characteristics fundamental to silicon's material physics while still capitalizing on properties that have enabled the success of the global integrated circuit industry [1-3]. High-speed electronic devices, devices with high breakdown voltages, light emitting/detecting devices, and devices for photon control can all be integrated with conventional CMOS to perform specialized electronic or photonic functions if suitable methods for forming such heterogeneously integrated regions are available that provide high yield and are compatible with fabrication processes that occur subsequent to the heterogeneous integration process. Technical challenges include lattice mismatch, thermal expansion coefficient differences, having the capability to form low-resistance electrical contacts using materials that are compatible with CMOS, more generally managing cross-contamination in tools used for front-end-of-line processing after III-V regions are established on the silicon wafers, and thermal management for the heterogeneously integrated devices or circuits. These together create formidable obstacles, but there is also the obstacle of defining a business case for creating hybrid wafer

fabs given the applications that would be served by ICs with enhanced functionality. Bringing functions that are off chip onto the chip needs to be justified both technically and financially.

# **Heterogeneous Integration Methods Over Time**

A variety of approaches have been explored over time to achieve the function and performance of nonnative devices on silicon. Early attempts at direct growth of III-V materials on silicon yielded devices that functioned, but the high defect density resulting from the growth of epitaxial layers thicker than the critical thickness resulted in devices with impaired performance or limited lifetime [4-5]. Even with the use of thick buffer layers and strained superlattice structures intended to keep defects away from the device active region, the combination of light and heat provide sufficient energy for defect propagation, especially dark line defects [5]. Beyond a certain point, limited progress was made on direct growth. Around the same time, the idea of using a patterned silicon wafer as an optical bench was advanced. In this method, precision placement tools were used to accurately bond fabricated III-V die onto a silicon wafer having patterned alignment features and Vgrooves for fiber attach. This method was successful and is still used today, but the low throughput of the process given the time needed to place die with micron-scale tolerance limited scalability. Additionally, the vision of integrating CMOS electronics onto the silicon optical bench was never commercially justified given the performance-costyield trade-off. More recent efforts on heterogeneous integration have explored growth on transferred "seed" crystals [6], growth of quantum wires [7], and growth of quantum dots [8]. These techniques have yielded promising device results but have the challenge of being higher-temperature processes that complicate CMOS compatibility. Other methods specific to silicon photonics have either used evanescent coupling to bonded III-V gain material [9] or edge coupling of metal-bonded III-V gain material [10] to form lasers. These techniques have the advantage of eliminating the need for precision alignment at the individual device level, and have shown promise for defining a path forward for wafer-

2021 Electron Devices Technology and Manufacturing Conference (EDTM)

scale integration of photonic functions.

#### **Heterogeneous Integration at UIUC**

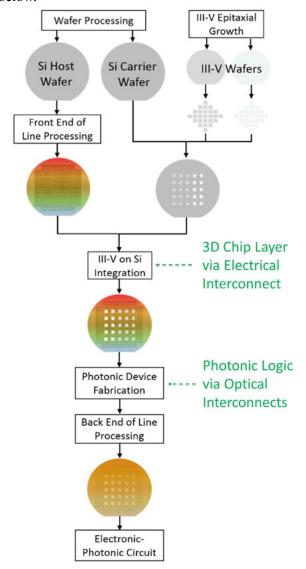

Work on heterogeneous integration methods at the University of Illinois at Urbana-Champaign have focused on epitaxial transfer, as depicted in Fig. 1 below.

Fig. 1. Depiction of high-level process flow for heterogenous integration via epitaxial transfer using a silicon carrier wafer.

In this method, a first silicon wafer is processed in a standard CMOS wafer fab through the full front-end-of-line process while a second wafer is used as a transfer wafer for other materials such as laser gain structures, modulator structures, detector structures, passive waveguide structures, isolator crystals, or other materials needed to effect a specific device function. Multiple distinct materials can be transferred in a single transfer step. The transfer step

may also be repeated to create a 3-D stack of heterogeneously integrated material above the plane of the CMOS host wafer surface. The transfer wafer is prepared by depositing a temporary bonding material such as spin-coat bonding films from AI Technologies. Pieces of III-V epitaxial wafers or other materials are coarsely bonded to the transfer wafer, and lapping, polishing, and plasma or wet chemical thinning are used to reduce the thickness of the bonded material to typically a few microns – approximately the thickness of the epitaxial layers. A hard mask then deposited photolithographically defined, and the bonded material is fully removed via wet or dry etching in all unmasked regions. What is left on the transfer wafer are islands of material such as III-V epitaxial device structures defined on the wafer and relative to each other with photolithographic precision.

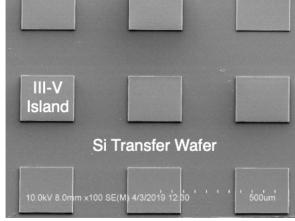

A scanning electron microscope (SEM) photomicrograph of such an island is shown in Fig. 2 below.

Fig. 2. SEM image of III-V islands of epitaxial material on silicon transfer wafer after patterning and etching to precisely define location.

The III-V islands are composed of an epitaxial layer structure used for photonic devices.

A single wafer bonding step using a permanent bonding material can then be used to bond all of the material on the transfer wafer onto the CMOS host wafer. Given the capability of modern wafer bonding tools, this can be done with micron-level precision at production scale. Fabrication of photonic devices takes place on the silicon CMOS host wafer after the epitaxial transfer process. Optical alignment of individual devices is not required, as all photonic elements are defined within the layer registration specification of the photolithography tool.

Using the above method, light-emitting transistors (LETs) were fabricated on epitaxial material after transfer from a first silicon wafer to a second using the described method [11]. A SEM image of a LET fabricated on transferred material is shown in Fig. 3 below.

Fig. 3. Light-emitting transistor fabricated on transferred III-V epitaxial material.

The LET devices fabricated via epitaxial transfer have reasonable performance characteristics, and could eventually be used for the integration of onchip or chip-to-chip optical interconnects.

## Conclusion

A review of approaches for the integration of material such as III-V epitaxial device structures onto silicon has been provided, and various challenges have been discussed. A method to overcome these challenges in a wafer-scale process has been explored.

#### Acknowledgments

The authors gratefully acknowledge the support of the National Science Foundation under award number ECCS 16-40196.

# References

- [1] M. Bohr, "The evolution of scaling from the homogeneous era to the heterogeneous era," in Electron Devices Meeting (IEDM), 2011 IEEE International, pp. 1-1, Washington, DC, 2011.

- [2] O. Mountanabbir and U. Gosele, "Heterogeneous Integration of Compound Semiconductors," Ann. Rev. Mater. Res., vol. 40, pp. 469-500, August

- 2010.

- [3] J.A. del Alamo, "Nanometre-scale electronics with III-V compound semiconductors," Nature, Vol. 479, pp. 317-323, November 2011.

- [4] M. Akiyama, Y. Kawarada, K. Kaminishi, "Growth of GaAs on Si by MOVCD," Journal of Crystal Growth ,Vol. 68, pp. 21-26 1984.

- [5] D.G. Deppe, N. Holonyak, Jr., D.W. Nam, K.C. Hsieh, and G.S. Jackson, "Room-temperature continuous operation of p-n AlxGa1-xAs-GaAs quantum well heterostructure lasers grown on Si," Appl. Phys. Lett. 51, 637, 1987.

- [6] T.E. Kazior, "Beyond CMOS: heterogeneous integration of III-V devices, RF MEMs and other dissimilar materials/devices with Si CMOS to create intelligent microsystems," Phil. Trans. R. Soc. A, 372.20130105, December 2014.

- [7] A. Hazari, F.-C. Hsiao, L. Yan, J. Heo, J.M. Millunchick, J. Dallesasse, and P. Bhattacharya, "1.3 μm Optical Interconnect on Silicon: A Monolithic III-Nitride Nanowire Photonic Integrated Circuit," IEEE J. Quantum Electron. 53, 6300109, 2017.

- [8] D. Jung, Z. Zhang, J. Norman, R. Herrick, M.J. Kennedy, P. Patel, K. Turnlund, C. Jan, Y. Wan, A.C. Gossard, and J.E. Bowers, "Highly Reliable Low-Threshold InAs Quantum Dot Lasers on On-Axis (001) Si with 87% Injection Efficiency," ACS Photonics 5 (3), 1094-1100, 2018.

- [9] A.W. Fang, H. Park, O. Cohen, R. Jones, M.J. Paniccia, and J.E. Bowers, "Electrically pumped hybrid AlGaInAs-silicon evanescent laser," Opt. Express, vol. 14, pp. 9203-9210, 2006.

- [10] T. Creazzo, E. Marchena, S.B. Krasulick, P.K.L. Yu, D. Van Orden, J.Y. Spann, C.C. Blivin, L. He, H. Cai, J.M. Dallesasse, R.J. Stone, and A. Mizrahi, "Integrated tunable CMOS laser," Opt. Express, vol. 21, pp. 28048-28053, 2013.

- [11] J. Carlson, C. Williams, M. Ganjoo, and J. Dallesasse, "Epitaxial Bonding and Transfer Processes for Large-Scale Heterogeneously Integrated Electronic-Photonic Circuitry," J. Electrochem. Soc. 166, D3158, 2019.