# High-k Oxide Field-Plated Vertical (001) $\beta$ -Ga<sub>2</sub>O<sub>3</sub> Schottky Barrier Diode With Baliga's Figure of Merit Over 1 GW/cm<sup>2</sup>

Saurav Roy<sup>✉</sup>, Arkka Bhattacharyya<sup>✉</sup>, Praneeth Ranga<sup>✉</sup>, Heather Splawn, Jacob Leach, and Sriram Krishnamoorthy<sup>✉</sup>, *Member, IEEE*

**Abstract**— We report a vertical (001)  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> field-plated (FP) Schottky barrier diode (SBD) with a novel extreme permittivity dielectric field oxide. A thin drift layer of 1.7  $\mu m$  was used to enable a punch-through (PT) field profile and very low differential specific on-resistance ( $R_{on-sp}$ ) of 0.32 m $\Omega$ ·cm<sup>2</sup>. The extreme permittivity field plate oxide facilitated the lateral spread of the electric field profile beyond the field plate edge and enabled a breakdown voltage ( $V_{br}$ ) of 687 V. The edge termination efficiency increases from 13.2 % for non-field plated structure to 61 % for high permittivity field plate structure. The surface breakdown electric field was extracted to be 5.45 MV/cm at the center of the anode region using TCAD simulations. The high permittivity field plated SBD demonstrated a record high Baliga's figure of merit (BFOM) of 1.47 GW/cm<sup>2</sup> showing the potential of Ga<sub>2</sub>O<sub>3</sub> power devices for multi-kilovolt class applications.

**Index Terms**—  $\text{Ga}_2\text{O}_3$ , field plate, high-k, Schottky diode, edge termination, power device, HVPE.

## I. INTRODUCTION

THE rise of  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> as the next generation power electronic material due to its large bandgap ( $\sim$ 4.6 eV) and very high Baliga's figure of merit (3400<sub>Si</sub>) [1] has enabled researchers to demonstrate multi-kV class devices. The estimated critical electric field of  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> (8 MV/cm) is significantly higher than GaN (3.3 MV/cm) and SiC (2.4 MV/cm). Various power devices including SBDs and transistors in both lateral and vertical geometry have been demonstrated with high breakdown voltages [2]–[16].

Manuscript received May 26, 2021; revised June 11, 2021; accepted June 14, 2021. Date of publication June 16, 2021; date of current version July 26, 2021. This work was supported in part by the National Science Foundation (NSF) under Grant DMR-1931652 and in part by the Air Force Office of Scientific Research under Award FA9550-21-0078. The work of Heather Splawn and Jacob Leach was supported in part by the Air Force Research Laboratory (AFRL)/Air Force Materiel Command (AFMC) through the Small Business Innovation Research (SBIR) under Contract FA8650-19-C-2902. The review of this letter was arranged by Editor R.-H. Horng. (*Corresponding author: Saurav Roy.*)

Saurav Roy, Arkka Bhattacharya, Praneeth Ranga, and Sriram Krishnamoorthy are with the Department of Electrical and Computer Engineering, The University of Utah, Salt Lake City, UT 84112 USA (e-mail: saurav.roy@utah.edu).

Heather Splawn and Jacob Leach are with Kyma Technologies Inc., Raleigh, NC 27617 USA.

Color versions of one or more figures in this letter are available at <https://doi.org/10.1109/LED.2021.3089945>.

Digital Object Identifier 10.1109/LED.2021.3089945

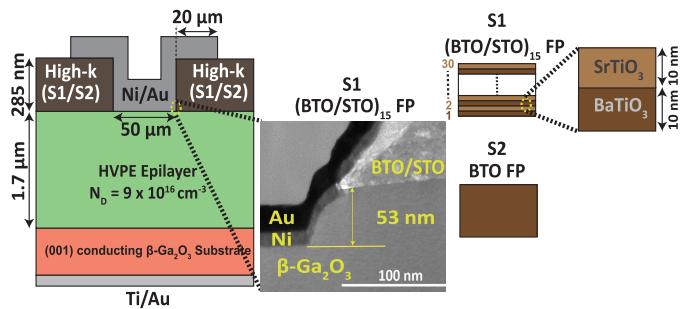

**Fig. 1.** Schematic of  $\text{Ga}_2\text{O}_3$  SBD with high-k dielectric field plate, where S1 is the  $(\text{BTO}/\text{STO})_{15}$  dielectric field oxide for  $(\text{BTO}/\text{STO})_{15}$  FP SBD and S2 is the BTO dielectric field oxide for BTO FP SBD. The expanded region shows the TEM image of the anode edge of the  $(\text{BTO}/\text{STO})_{15}$  FP SBD.

Despite its huge potential,  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> poses several challenges regarding the management of electric field at the device corners and edges, causing premature breakdown of devices. The lack of p-type doping, which is widely used in GaN and SiC devices for edge field management also poses a fundamental challenge in device design and complicated hetero-integration is needed for  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> [17]. Even with non p-type edge terminations, the average electric field for demonstrated  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> devices are far lower than the theoretical material limit which makes the search of robust and efficient alternative edge termination techniques extremely necessary.

In this letter, we demonstrate a field-plated vertical SBD with an extreme permittivity ( $\text{BaTiO}_3/\text{SrTiO}_3$ ) [18] field plate oxide [19] with PT design. By achieving a high dielectric constant of  $\sim 325$ , we have managed to increase the surface electric field at breakdown to 5.45 MV/cm. A breakdown voltage of 687 V in conjunction with a very low  $R_{\text{on-sp}}$  (0.32  $\text{m}\Omega\text{-cm}^2$ ) has resulted in a record BFOM of 1.47  $\text{GW/cm}^2$ .

## II. DEVICE FABRICATION

Device fabrication of the field plated SBD as shown in Fig. 1 started with the growth of the (001)  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> epilayers in a custom-designed subatmospheric vertical HVPE reactor using GaCl and O<sub>2</sub> precursors [20]. GaCl is produced in-situ by flowing Cl<sub>2</sub> over liquid Ga (7N purity), and is subsequently transported to the wafer surface through a quartz injector. Growth rate of  $\sim$ 5  $\mu$ m/hr is controlled by the GaCl molar flow rates. The as-grown samples were dipped in HF followed by HCl for 5 minutes. 15 layers of 10 nm thick BaTiO<sub>3</sub>

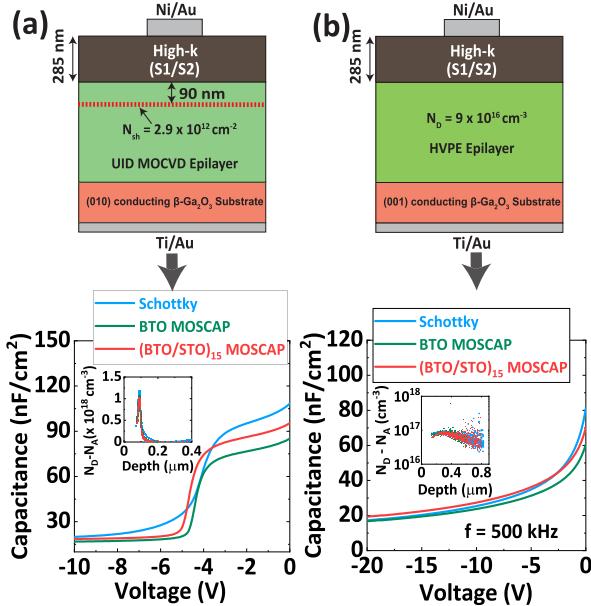

Fig. 2. (a) CV characteristics for an MOCVD grown delta doped sample with and without the dielectrics. (b) CV characteristics for the actual samples with and without the dielectrics. The inset of (a) and (b) shows the apparent charge density for the two samples.

and SrTiO<sub>3</sub> (BTO/STO)<sub>15</sub> (Measured total  $\sim 285$  nm) were sputter deposited on the sample in oxygen ambient at room temperature. After the dielectric deposition, the sample was annealed at 700 °C in oxygen ambient for 30 minutes to increase the dielectric constant. The sample was then patterned using standard photolithography and the active regions were opened-up using SF<sub>6</sub>/Ar dry etching. About 50 nm of overetching is performed to ensure the complete removal of the dielectrics which was confirmed using transmission electron microscope imaging (Fig. 1). EDS chemical map of the (BTO/STO)<sub>15</sub> dielectric layer indicated intermixing of Strontium and Barium, possibly due to the high temperature annealing. Ni/Au (20/40 nm) metal stacks were then deposited on the sample using e-beam evaporation. Finally, Ti/Au (50/100 nm) ohmic contacts were sputter deposited on the back side of the sample. Additional samples with BaTiO<sub>3</sub> (BTO) dielectric as field plate oxide and a reference SBD with no FP were also fabricated for comparison using the process flow described above.

### III. RESULTS AND DISCUSSIONS

Dielectric constants of the deposited (BTO/STO)<sub>15</sub> and BTO layer were extracted by depositing the dielectrics on an MOCVD grown (010)  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> with a  $\delta$ -doped layer [21] using the method reported by Xia *et al.* [10]. The capacitance of the dielectrics were calculated by comparing the capacitance corresponding to the peak of the  $\delta$ -doped layer with and without the dielectrics as shown in Fig. 2(a). The capacitance per unit area of the dielectric ( $C_{dielectric}$ ) can be written as,  $C_{dielectric} = (C_{ds}C_{dM})/(C_{ds}-C_{dM})$ , where  $C_{ds}$  is the capacitance per unit area corresponding to the peak of the  $\delta$  doping without the dielectric and  $C_{dM}$  is the capacitance per unit area corresponding to the peak of the  $\delta$  doping with the dielectric. Using  $\epsilon_r = C_{dielectric} \times t_{dielectric}/\epsilon_0$ , the dielectric constant is extracted to be  $\sim 325$  and  $\sim 142$  for the (BTO/STO)<sub>15</sub> and

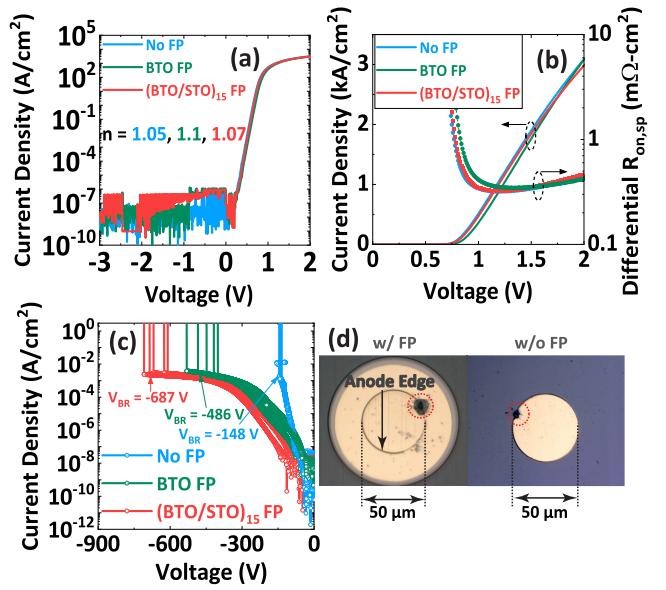

Fig. 3. (a) Log scale, & (b) linear scale IV characteristics of non-FP SBD, BTO FP SBD, and (BTO/STO)<sub>15</sub> FP SBD. (c) Breakdown characteristics of the three different SBD structures, and (d) Microscope image of the fabricated device showing breakdown location for the representative SBDs with and without FP.

BTO layer respectively, where  $\epsilon_r$  is the dielectric constant of the dielectrics,  $t_{dielectric}$  is the thickness of the dielectrics, and  $\epsilon_0$  is the permittivity of free space.

To understand effects of the dielectric deposition and the thermal annealing on the apparent charge density, capacitance voltage (CV) measurements were performed on the actual samples using the extracted dielectric constants as shown in Fig. 2(b) for the schottky diode, BTO MOSCAP, and (BTO/STO)<sub>15</sub> MOSCAP. A net doping concentration of  $8-9 \times 10^{16} \text{ cm}^{-3}$  is extracted from the CV plot as shown in the inset of Fig. 2(b).

The typical current voltage plots in log and linear scale are shown in Fig. 3(a) and 3(b) respectively. The ideality factor (n) is extracted to be 1.04, 1.1 and 1.07 for the non-field plated SBD, BTO FP SBD, (BTO/STO)<sub>15</sub> FP SBD respectively. The normalized current is calculated by considering the area of the anode active region for the non-field plated and the field plated SBD since the current through the dielectric is found to be negligible for the operating voltage range (0-2 V) in the MOSCAP structures. The  $R_{on-sp}$  for the non-field plated, BTO FP, and (BTO/STO)<sub>15</sub> SBDs from the linear fit of the IV characteristics are extracted to be 0.33, 0.34, and 0.35 mΩ·cm<sup>2</sup> respectively and the lowest differential  $R_{on-sp}$  are 0.32, 0.34, and 0.32 mΩ·cm<sup>2</sup> respectively. Nominally similar values of ideality factor and on-resistance measured in all the three samples indicates that the dielectric deposition and the dry etching process of the dielectric did not degrade the drift layer and the metal/semiconductor interface.

The reverse breakdown characteristics for the SBDs measured using Keysight B1505A with no FP, BTO FP, and (BTO/STO)<sub>15</sub> FP are shown in Fig. 3(c). The destructive breakdown voltages for the three devices are extracted to be 148 V, 486 V and 687 V respectively. The breakdown craters were observed at the anode edges as shown in the optical microscope image of Fig. 3(d) for the FP and non-FP SBDs

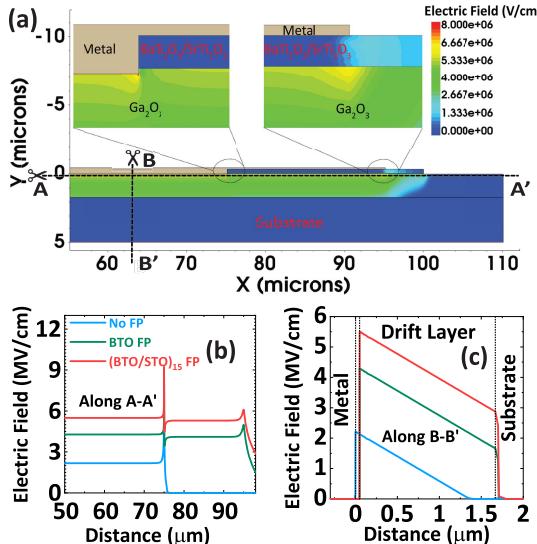

Fig. 4. (a) Electric field contour plot of the (BTO/STO)<sub>15</sub> FP SBD, (b) & (c) Simulated electric field profile for the three different SBDs for cutlines along the lateral and vertical directions respectively.

indicating the location of the breakdown. The increase in breakdown voltages for the high permittivity dielectric field plate oxide suggests the effectiveness of the edge termination and reduction in field crowding at the device edges due to the high permittivity of the FP dielectric.

The electric field simulations for the three SBD structures are also performed using Sentaurus TCAD software [22] and results are plotted in Fig. 4(a), (b), and (c). Except for the non-field plated SBD, the other two devices reach PT condition at breakdown as can be seen from Fig. 4(c). The calculated surface electric field ( $E_{surf}$ ) for the non-punch-through (NPT) and punch-through devices can be calculated as  $E_{surf-npt} = \sqrt{\frac{2qN_D V_{br}}{\epsilon}}$  and  $E_{surf-pt} = \frac{V_{br}}{t_{drift}} + \frac{qN_D t_{drift}}{2\epsilon}$  respectively, where  $q$  is the electron charge,  $N_D$  is the donor concentration,  $\epsilon$  is the permittivity of the dielectric, and  $t_{drift}$  is the thickness of drift layer. Using the above two expressions, the surface electric fields can be calculated for SBD with no FP as 2.2 MV/cm, with BTO FP as 4.2 MV/cm, with (BTO/STO)<sub>15</sub> FP as 5.42 MV/cm. The calculated values for electric field match exactly with the simulation values as can be seen in Fig. 4(b). This maximum surface electric field at hard breakdown of 5.45 MV/cm for SBD with (BTO/STO)<sub>15</sub> FP is the highest value reported to date for all the Schottky barrier diodes. A peak electric field of 8-9 MV/cm was estimated at anode edges suggesting the location of the breakdown, thus, confirming the weak points for each type of device as seen in the microscope images shown in Fig. 3(d).

If a perfect etching control is achieved, then based on simulations of the identical structure with no 50 nm over etching, we expect the peak electric field to be 6.1 MV/cm at the anode edge, with (BTO/STO)<sub>15</sub> FP at the anode bias of -687 V (32% reduction compared to the structure with etched Ga<sub>2</sub>O<sub>3</sub>). The edge termination efficiency ([Real  $V_{br}$ /Ideal  $V_{br}$ ]  $\times$  100%) increases from 43.2% for the BTO FP to 61% for (BTO/STO)<sub>15</sub> FP, where Ideal  $V_{br}$  is calculated as  $V_{BR,Ideal} = E_C t_{drift} - \frac{qN_D t_{drift}^2}{2\epsilon}$ , where  $E_C$  is the predicted critical electric field for  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> (8 MV/cm).

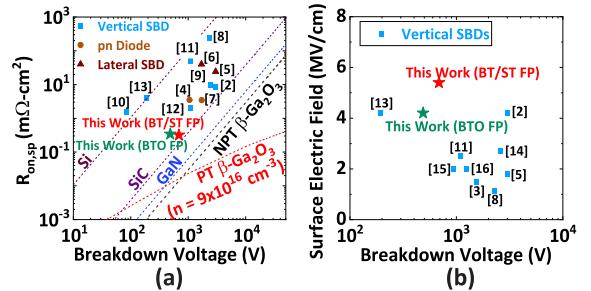

Fig. 5. Benchmark plot for (a)  $R_{on-sp}$  vs  $V_{br}$  and (b) Surface electric field vs  $V_{br}$  comparing our device with other reported vertical and lateral diodes.

The extremely low  $R_{on-sp}$  of 0.32 mΩ·cm<sup>2</sup> (0.35 mΩ·cm<sup>2</sup> from linear fit) and the breakdown voltage of 687 V for the (BTO/STO)<sub>15</sub> FP SBD results in a record high figure of merit of 1.47 GW/cm<sup>2</sup> (1.34 GW/cm<sup>2</sup> for the linear fit  $R_{on-sp} = 0.35 \text{ m}\Omega\text{-cm}^2$ ). Fig. 5(a) shows the benchmark plots of  $R_{on-sp}$  and breakdown voltage comparing performance of the (BTO/STO)<sub>15</sub> FP SBD with the existing literature reports. The performance metrics of our device is significantly better compared to the other reported devices. The surface breakdown electric field of 5.45 MV/cm is the highest electric field reported to date for  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> based SBDs as can be seen from Fig. 5(b). It should be noted that  $E_{surf}$  extraction depends on the exact doping profile. For uniform doping in the range of  $6 \times 10^{16} \text{ cm}^{-3}$  to  $1 \times 10^{17} \text{ cm}^{-3}$ , the calculated  $E_{surf}$  is 4.96 to 5.57 MV/cm and the simulated  $E_{surf}$  is 4.97 to 5.6 MV/cm. Clearly the results demonstrated here represents the highest  $E_{surf}$  achieved in any SBD.

The demonstrated device structure can be designed for high voltage applications by appropriately choosing the thickness and doping concentration of the drift layer. If the surface breakdown electric field of 5.45 MV/cm is maintained as demonstrated for the high-k FP SBD, then using a drift layer thickness of 36 μm and doping concentration of  $8.2 \times 10^{16} \text{ cm}^{-3}$ , the breakdown voltage can be extended to 10 kV. For such voltage ranges,  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> based devices have significant advantages compared to SiC based devices as SiC based devices require more than 100 μm of drift layer thickness for 10 kV breakdown voltages [23], [24], which in turn increases the on-resistance of the SiC devices.

#### IV. CONCLUSION

In summary we have demonstrated a vertical (001) oriented  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> SBD with high permittivity dielectric field plate oxide showing extremely low  $R_{on-sp}$  of 0.32 mΩ·cm<sup>2</sup> and a high breakdown voltage of 687 V resulting in a BFOM value of 1.47 GW/cm<sup>2</sup> surpassing all the reported SBDs. The extracted surface breakdown electric field of 5.45 MV/cm is the highest electric field reported to date for  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> SBDs. This demonstration indicates that the use of such high-k dielectric field-plated structure enables high edge field termination efficiency and also enable studying the intrinsic critical field limits of ultra-wide band-gap semiconductors.

#### ACKNOWLEDGMENT

Device fabrication was performed at the Utah Nanofab at The University of Utah and electron microscopy was performed at the Surface Analysis Lab at The University of Utah.

## REFERENCES

[1] S. Pearson, J. Yang, P. H. Cary, IV, F. Ren, J. Kim, M. J. Tadje, and M. A. Mastro, "A review of Ga<sub>2</sub>O<sub>3</sub> materials, processing, and devices," *Appl. Phys. Rev.*, vol. 5, no. 1, 2018, Art. no. 011301.

[2] W. Li, K. Nomoto, Z. Hu, D. Jena, and H. G. Xing, "Field-plated Ga<sub>2</sub>O<sub>3</sub> trench Schottky barrier diodes with a  $BV^2/R_{on,sp}$  of up to 0.95 GW/cm<sup>2</sup>," *IEEE Electron Device Lett.*, vol. 41, no. 1, pp. 107–110, Jan. 2020.

[3] H. Zhou, Q. Yan, J. Zhang, Y. Lv, Z. Liu, Y. Zhang, K. Dang, P. Dong, Z. Feng, Q. Feng, J. Ning, C. Zhang, P. Ma, and Y. Hao, "High-performance vertical  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> Schottky barrier diode with implanted edge termination," *IEEE Electron Device Lett.*, vol. 40, no. 11, pp. 1788–1791, Nov. 2019.

[4] X. Lu, X. Zhou, H. Jiang, K. W. Ng, Z. Chen, Y. Pei, K. M. Lau, and G. Wang, "1-kV sputtered p-NiO/n-Ga<sub>2</sub>O<sub>3</sub> heterojunction diodes with an ultra-low leakage current below 1  $\mu$ A/cm<sup>2</sup>," *IEEE Electron Device Lett.*, vol. 41, no. 3, pp. 449–452, Mar. 2020.

[5] Z. Hu, H. Zhou, Q. Feng, J. Zhang, C. Zhang, K. Dang, Y. Cai, Z. Feng, Y. Gao, X. Kang, and Y. Hao, "Field-plated lateral  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> Schottky barrier diode with high reverse blocking voltage of more than 3 kV and high DC power figure-of-merit of 500 MW/cm<sup>2</sup>," *IEEE Electron Device Lett.*, vol. 39, no. 10, pp. 1564–1567, Oct. 2018.

[6] Z. Hu, H. Zhou, K. Dang, Y. Cai, Z. Feng, Y. Gao, Q. Feng, J. Zhang, and Y. Hao, "Lateral  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> Schottky barrier diode on sapphire substrate with reverse blocking voltage of 1.7 kV," *IEEE J. Electron Devices Soc.*, vol. 6, pp. 815–820, 2018.

[7] Y. Lv, Y. Wang, X. Fu, S. Dun, Z. Sun, H. Liu, X. Zhou, X. Song, K. Dang, S. Liang, J. Zhang, H. Zhou, Z. Feng, S. Cai, and Y. Hao, "Demonstration of  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> junction barrier Schottky diodes with a Baliga's figure of merit of 0.85 GW/cm<sup>2</sup> or a 5A/700 V handling capabilities," *IEEE Trans. Power Electron.*, vol. 36, no. 6, pp. 6179–6182, Jun. 2021.

[8] J. Yang, F. Ren, M. Tadje, S. J. Pearson, and A. Kuramata, "2300V reverse breakdown voltage Ga<sub>2</sub>O<sub>3</sub> Schottky rectifiers," *ECS J. Solid State Sci. Technol.*, vol. 7, no. 5, p. Q92, 2018.

[9] W. Li, Z. Hu, K. Nomoto, R. Jinno, Z. Zhang, T. Q. Tu, K. Sasaki, A. Kuramata, D. Jena, and H. G. Xing, "2.44 kV Ga<sub>2</sub>O<sub>3</sub> vertical trench Schottky barrier diodes with very low reverse leakage current," in *IEDM Tech. Dig.*, Dec. 2018, pp. 5–8.

[10] Z. Xia, H. Chandrasekar, W. Moore, C. Wang, A. J. Lee, J. McGlone, N. K. Kalarickal, A. Arehart, S. Ringel, F. Yang, and S. Rajan, "Metal/BaTiO<sub>3</sub>/ $\beta$ -Ga<sub>2</sub>O<sub>3</sub> dielectric heterojunction diode with 5.7 MV/cm breakdown field," *Appl. Phys. Lett.*, vol. 115, no. 25, 2019, Art. no. 252104.

[11] Z. Jian, S. Mohanty, and E. Ahmadi, "Temperature-dependent current-voltage characteristics of  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> trench Schottky barrier diodes," *Appl. Phys. Lett.*, vol. 116, no. 15, Apr. 2020, Art. no. 152104.

[12] N. Allen, M. Xiao, X. Yan, K. Sasaki, M. J. Tadje, J. Ma, R. Zhang, H. Wang, and Y. Zhang, "Vertical Ga<sub>2</sub>O<sub>3</sub> Schottky barrier diodes with small-angle beveled field plates: A Baliga's figure-of-merit of 0.6 GW/cm<sup>2</sup>," *IEEE Electron Device Lett.*, vol. 40, no. 9, pp. 1399–1402, Sep. 2019.

[13] C. Joishi, S. Rafique, Z. Xia, L. Han, S. Krishnamoorthy, Y. Zhang, S. Lodha, H. Zhao, and S. Rajan, "Low-pressure CVD-grown  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> bevel-field-plated Schottky barrier diodes," *Appl. Phys. Exp.*, vol. 11, no. 3, 2018, Art. no. 031101.

[14] W. Li, K. Nomoto, Z. Hu, T. Nakamura, D. Jena, and H. G. Xing, "Single and multi-fin normally-off Ga<sub>2</sub>O<sub>3</sub> vertical transistors with a breakdown voltage over 2.6 kV," in *IEDM Tech. Dig.*, Dec. 2019, pp. 4–12.

[15] Y. Wang, Y. Lv, S. Long, X. Zhou, X. Song, S. Liang, T. Han, X. Tan, Z. Feng, S. Cai, and M. Liu, "High-voltage (201)  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> vertical Schottky barrier diode with thermally-oxidized termination," *IEEE Electron Device Lett.*, vol. 41, no. 1, pp. 131–134, Jan. 2020.

[16] W. Li, Z. Hu, K. Nomoto, Z. Zhang, J.-Y. Hsu, Q. T. Thieu, K. Sasaki, A. Kuramata, D. Jena, and H. G. Xing, "1230 V  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> trench Schottky barrier diodes with an ultra-low leakage current of <1  $\mu$ A/cm<sup>2</sup>," *Appl. Phys. Lett.*, vol. 113, no. 20, Nov. 2018, Art. no. 202101.

[17] S. Roy, A. Bhattacharyya, and S. Krishnamoorthy, "Design of a  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> Schottky barrier diode with p-type III-nitride guard ring for enhanced breakdown," *IEEE Trans. Electron Devices*, vol. 67, no. 11, pp. 4842–4848, Nov. 2020.

[18] L. Kim, D. Jung, J. Kim, Y. S. Kim, and J. Lee, "Strain manipulation in BaTiO<sub>3</sub>/SrTiO<sub>3</sub> artificial lattice toward high dielectric constant and its nonlinearity," *Appl. Phys. Lett.*, vol. 82, no. 13, pp. 2118–2120, 2003.

[19] H.-S. Lee, N. K. Kalarickal, M. W. Rahman, Z. Xia, W. Moore, C. Wang, and S. Rajan, "High-permittivity dielectric edge termination for vertical high voltage devices," *J. Comput. Electron.*, vol. 19, no. 4, pp. 1538–1545, Dec. 2020.

[20] J. Leach, K. Udwary, J. Rumsey, G. Dodson, H. Splawn, and K. Evans, "Halide vapor phase epitaxial growth of  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> and  $\alpha$ -Ga<sub>2</sub>O<sub>3</sub> films," *APL Mater.*, vol. 7, no. 2, 2019, Art. no. 022504.

[21] P. Ranga, A. Bhattacharyya, A. Rishinaramangalam, Y. K. Ooi, M. A. Scarpulla, D. Feezell, and S. Krishnamoorthy, "Delta-doped  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> thin films and  $\beta$ -(Al<sub>0.26</sub>Ga<sub>0.74</sub>)<sub>2</sub>O<sub>3</sub>/ $\beta$ -Ga<sub>2</sub>O<sub>3</sub> heterostructures grown by metalorganic vapor-phase epitaxy," *Appl. Phys. Exp.*, vol. 13, no. 4, 2020, Art. no. 045501.

[22] *Sentaurus Device User Manual*, Version N-2017.09, Synop., Mountain View, CA, USA, Mar. 2017.

[23] J. H. Zhao, P. Alexandrov, and X. Li, "Demonstration of the first 10-kV 4H-SiC Schottky barrier diodes," *IEEE Electron Device Lett.*, vol. 24, no. 6, pp. 402–404, Jun. 2003.

[24] B. Asllani, H. Morel, L. V. Phung, and D. Planson, "10 kV silicon carbide PiN diodes—From design to packaged component characterization," *Energies*, vol. 12, no. 23, p. 4566, Nov. 2019. [Online]. Available: <https://www.mdpi.com/1996-1073/12/23/4566>