# Performance Evaluation and Analysis for Resonant Switched Capacitor Converter

Mengxuan Wei<sup>a</sup>, Ze Ni<sup>b</sup>, Shuai Yang<sup>a</sup>, Maohang Qiu<sup>a</sup>, Xiaoyan Liu<sup>a</sup> Dong Cao<sup>a</sup>

Electrical and Computer Engineering Department

a.University of Dayton, Dayton, OH

b.Monolithic Power System Inc, San Jose,CA

dcao02@udayton.edu

Abstract— In this paper, a new method helps compare and analysis different topology is proposed. Also, a new method that can analyze and derive the minimum device power loss for the resonant switched capacitor topology is developed. By applying total semiconductor power loss index (TSLI), the optimum total die size needed for the specific topology with fixed power level and switching frequency can be calculated. Thus, the minimum device power loss can be reached at same time. Besides, TSLI can also help to determine which topology has a lower semiconductor device power loss when operating under same condition.

Keywords— Switched-capacitor converter, Die area, Figure of Merit, Topology comparison, Power loss analysis

#### I. INTRODUCTION

Resonant switched capacitor converters have received more attention due to the high power density and efficiency compared with the traditional approaches. Different topologies will use various voltage ratings device and operating at different optimized output power. Thus, it is important to evaluate these topologies deliberately. In [1], VA rating comparison which using the product of the average current flows through the device and the maximum voltage across it as the indicator for the converter device power loss index. The comparison is not considering the gate drive loss and the output capacitance loss. Besides the VA rating is not accurately shows the conduction loss. A new Figure-of Merit of multi-level converter properties is proposed in [2]. The power loss analysis is based on bridge-leg. However only the switching loss and conduction loss are included. In [3] the FoM based loss analysis for choosing the most appropriate GaN device is demonstrated. But the method is limited only to the device level selection. PDFOM is proposed in [4] for selecting the better device to achieve a better converter power density. However, the effect factors could be further reduced. [5]-[7] mention another resonant and soft-switching Figure-of Merit, however it is simplified to converter ZVS operation using GaN device.

In this paper, a new method which composed by the total device power rating (TDPR) and the total semiconductor power loss index (TSLI). TDPR is proposed in [8]-[10]. It is offering a more direct and instantons method to compare different topology. TSLI is proposed to reflect the relationship between converter device power loss and the total device die area. By utilizing TSLI, the best operating total die size of converter can be derived. This can achieve lowest device power lost under the

fixed operating power and frequency. The theoretical derived process of TSLI is shown in the next section followed by the real application case and test result verification.

## II. PROPOSED CONVERTER EVALUATION METHOD

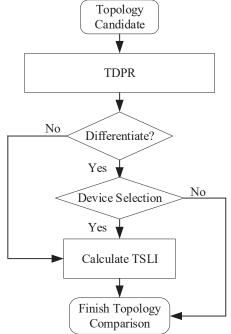

Fig. 1 shows the proposed method mechanism. When comparing different topologies, the first step is deriving the TDPR. This is a faster topology evaluation method than TSLI. If TDPR can differentiate the topologies and no device selection is need, then the topology comparison is finished. However, if the TDPR gives the same result for different topologies or the device selection is needed, then the calculation of TSDL is required. This can help figure out which is the appropriate topology for certain application.

Fig. 1: Proposed topology comparison method

### A. Total Device Power Rating(TDPR)

Total device rating is first proposed in [11]. The device rating is defined as the device voltage stress times the device current stress. By adding up all device rating, the total device rating for the converter is derived. TDPR is the proposed in [8]-[10]. It is defined as the product of the device voltage stress and the average current flowing through the device. In this paper, a normalized value is adopted by using the converter output power. The TDPR can be calculated using (1) where P<sub>o</sub> is the converter output power, N is the total number of devices, Vi is the voltage stress of the *i*-th device and the  $I_{avg i}$  is the average current flow though the *i*-th device.

$$TDPR = \frac{1}{P_0} \sum_{i=1}^{N} V_i I_{avg_i}$$

(1)

## B. Total power loss index (TSLI)

Total power loss index (TSLI) is first proposed in [12] to describe the relationship between the device power loss and the total the area usage. By reaching the minimum TSLI, the optimized semiconductor device die area usage of the topology operating under certain condition can be achieved. Since most of the resonant switched capacitor converter can achieve ZCS operation, the power loss on the device is consist of conduction loss, gate drive loss and the output capacitor loss. TSLI is derived based on these losses.

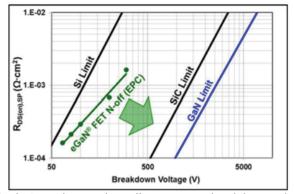

Fig. 2: On-resistance times die area versus breakdown voltage

To generate the connection between the device power loss and the die area, the production of on-resistance  $R_{ds(on)}$  and die area  $A_{die}$  is used. It is an index that company use to reflect the device technology [5]. It is the similar definition of B-FOM [13]. Fig. 1 [5] shows the theoretical limit of  $R_{ds(on)} \cdot A_{die}$  versus breakdown voltage  $V_B$  for Si, SiC and GaN. Also, the relationship for current EPC eGaNFET  $R_{ds(on)} \cdot A_{die}$  versus breakdown voltage  $V_B$  is demonstrated. Based on the curves, the theoretical Si and GaN limits and current EPC eGaNFET properties are presented in Eq. (1), (2) and (3), respectively.

$$\begin{array}{ll} R_{ds(on)} \cdot A_{die} = 1 \times 10^{-5} \cdot (V_B)^2 & (2) \\ R_{ds(on)} \cdot A_{die} = 3 \times 10^{-7} \cdot (V_B)^{1.983} & (3) \\ R_{ds(on)} \cdot A_{die} = 3 \times 10^{-6} \cdot (V_B)^2 & (4) \end{array}$$

$$R_{ds(on)} \cdot A_{die} = 3 \times 10^{-7} \cdot (V_R)^{1.983}$$

(3)

$$R_{ds(on)} \cdot A_{die} = 3 \times 10^{-6} \cdot (V_R)^2$$

(4)

Thus, the general relationship of  $R_{ds(on)}$  and  $A_{die}$  can represent in Eq. (4) where k is the constant corresponding to different semiconductor material and X is an exponent that close to 2. The unit for  $R_{ds(on)} \cdot A_{die}$  is  $\Omega \cdot mm^2$  and  $V_B$  is V. In this way, the  $R_{ds(on)}$  could be represented by Eq. (5).

$$R_{ds(on)} \cdot A_{die} = \alpha(k, V_B) = k \cdot (V_B)^X$$

$$R_{ds(on)} = \frac{k \cdot (V_B)^2}{A_{die}}$$

(6)

$$R_{ds(on)} = \frac{R \cdot (V_B)^2}{A_{die}} \tag{6}$$

Therefore, the device conduction loss  $P_{cond}$  can be defined by the device die area  $A_{die}$  using Eq. (6),  $I_{RMS\_S}$  is the switch RMS current. It is related to the converter operating condition.

$$P_{cond} = (I_{RMS\_S})^2 \cdot R_{ds(on)} = (I_{RMS\_S})^2 \cdot \frac{\alpha(k_v V_B)}{A_{die}}$$

(7)

In [14], the new device FOM is proposed to describe the relationship between  $R_{ds(on)}$  and  $Q_g$  for different manufacturer technologies and it is shown in Eq. (7). Then, the device gate drive loss  $P_{gate}$  can be defined by the device die area  $A_{die}$  using Eq. (8),  $V_{gs}$  is gate-source voltage and  $f_s$  is the switching frequency.

$$HDFOM = \sqrt{R_{ds(on)} \cdot Q_g}$$

(8)

$$\begin{split} \text{HDFOM} &= \sqrt{R_{ds(on)} \cdot Q_g} \\ P_{gate} &= Q_g \cdot f_s \cdot V_{gs} = \frac{A_{die} \cdot (\text{HDFOM})^2}{k \cdot (V_B)^2} \cdot f_s \cdot V_{gs} \end{split} \tag{8}$$

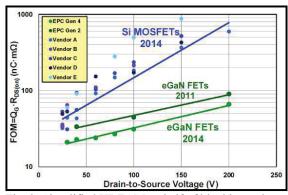

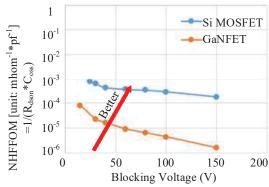

Fig.3 [7] shows the simplified version of HDFOM for the EPC GaNFET and the state of art Si MOSFET. It displays the relationship between the HDFOM<sup>2</sup> and half of the blocking voltage with 20A rated current.

Fig. 3: Simplified HDFOM vs half of blocking voltage

In [15], another device FOM is proposed to describe the relationship between  $R_{ds(on)}$  and  $C_{oss}$  with certain manufacturer technologies and it is shown in Eq. (9). The device output capacitance loss  $P_{coss}$  and the device die area  $A_{die}$  can be defined by using Eq. (10),  $V_{ds}$  is device voltage stress and assume is the half of the  $V_B$ .

$$P_{\text{Coss}} = C_{\text{oss}} \cdot f_{\text{s}} \cdot V_{\text{ds}}^2 = \frac{A_{\text{die}}}{NHFFOM.k.(V_p)^2} \cdot f_{\text{s}} \cdot (0.5V_B)^2 (10)$$

For the specific device operating in ZCS mode, the power loss will be

$$P_{loss} = P_{cond} + P_{gate} + P_{Coss}$$

(11)

To make a reasonable analysis, in one converter assuming all device is using same manufacture technology. Different voltage stress device will have the same property in terms of power loss, which means the power loss per unit area should be the same. We define  $\tau$  as the power loss per unit area, then as shown in Eq. (12)

$$\begin{split} \tau &= P_{loss}/A_{die} = (P_{cond} + P_{gate} + P_{Coss})/A_{die} \\ &= \left(I_{RMS\_S}\right)^2 \cdot \frac{\alpha(k,V_B)}{A_{die}^2} + \frac{(\text{HDFOM})^2}{k \cdot (V_B)^2} \cdot f_s \cdot + \cdot \end{split}$$

$$\frac{1}{\text{NHFFOM} \cdot k \cdot (V_B)^2} \cdot f_s \cdot (0.5V_B)^2 \cdot \tag{12}$$

For one topology working under the certain condition, when all device using the same manufacturer technologies, the relationship between the die area  $A_{die}$  and the device voltage stress  $V_{ds}$  can be derived, as shown in Eq. (13). Assuming  $V_{ds}$  is the half of the  $V_B$ .

$$A_{die} = \beta(V_B) \tag{13}$$

Therefore, for a specific switched capacitor topology, if the operation condition is fixed, the TSLI is the normalized power loss for every switching device and it can be generated as Eq. (14), N is the number of switching device.

$$TSLI = (14)$$

$$\frac{1}{P_0} \sum_{i=1}^{N} (P_{cond} \left\{ \beta(V_B) \right\} + P_{gate} \left\{ \beta(V_B) \right\} + P_{Coss} \left\{ \beta(V_B) \right\})$$

Thus, the most optimized total device die area with the minimum power loss can be derived when the  $\frac{dTSLI}{dA_{die}} = 0$ . The optimized A<sub>die optimized</sub> is shown as Eq. (15)

$$A_{die\_optimized} =$$

(15)

$$\sqrt{\frac{\text{HDFOM}^2 f_s V_{gs}/(V_B)^X + f_s/4\text{NHFFOM} \cdot k \cdot (V_B)^{X - 2}}{I_{RMS\_S}^* k \cdot (V_B)^X}}$$

As analyzed above, TSLI is related to the output power, switching frequency, conversion ratio and the device manufacture technology. For one fixed topology, when the output power, switching frequency and conversion ratio are fixed, theoretically it is possible to derive an optimized total die area to achieve the minimized total device power loss with the certain device manufacture technology. In other words, for different topologies, assuming using the same device manufacture technology, when the total device power loss is the under same operating conditions, the one with smaller total die area can achieve more efficient die utilization and potentially lower device manufacturing costs.

Besides, TSLI can also be used to figure out the minimum device power loss operating frequency when the converter operating power conversion ratio is fixed. Similarly, the best operating conversion ratio can also be derived when the converter is working under certain frequency and power. These two different evaluation perspectives based on the above TSLI parameter can provide more comprehensive understandings for switch capacitor topologies to achieve smallest total device power loss with an optimized total semiconductor die area.

#### III. APPLICATION EXAMPLES

## A. Total Device Power Rating Application

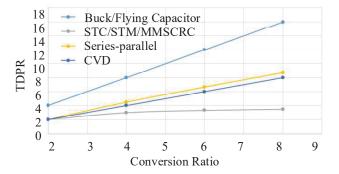

The TDPR is derive for buck, flying capacitor, ZCS-series parallel [16], cascaded voltage divider (CVD) [17], switch-tank converter (STC) [18], switch-tank modular converter (STM) [19] and multilevel modular switched-capacitor resonant converter (MMSCRC) [20] topology with 2X,4X,6X and 8X. All the converters operate with the 48V input voltage, 250kHz and 480W condition.

As shown in the Fig3. The TDPR for the flying capacitor and the buck is the same. TDPR cannot differentiate the two topologies. Similarly, the STC, STM and the MMSCRC also have the same TDPR. In this case, TSLI should be used as the

Fig. 3: TDPR vs converter conversion ratio

comparison method. And with the increase of the conversion ratio, the TDPR of the STC increment is the smallest. This is indicating that STC will be a better choice.

#### B. Total power loss index (TSLI) Application

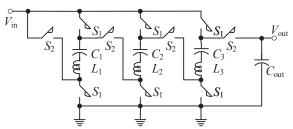

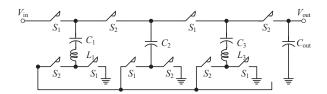

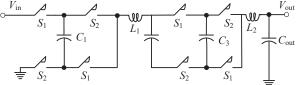

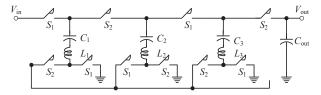

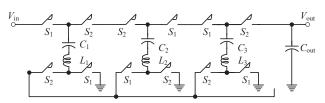

Five types of switch capacitor resonant convert: ZCS-series-parallel, STC, CVD, MMSCRC and STM are selected to verify TSLI. The converter topology is shown in Fig. 4, Fig. 5 Fig. 6, Fig. 7 and Fig.8 respectively. All converters are operating at 480W,48V-12V and 250kHz.ZCS is achieved for all converters.

Fig. 4: 4 to 1 series-parallel converter

Fig. 5: 4 to 1 STC converter

Fig. 6: 4 to 1 cascaded voltage divider converter

Fig. 7: 4 to 1 MMSCRC converter

Fig. 8: 4 to 1 STM converter

Fig.9 is obtained from Infineon OptiMOS 5 series and EPC GaNFET. It shows the relationship between the NHFFOM and the device blocking voltage and the following analysis is based on it.

Fig. 9: NHFFOM for OptiMOS 5 and eGaNFET

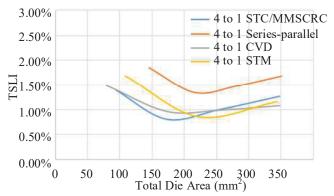

Fig.10 shows the trend for TSLI regarding total device die area for STC, MMSCRC, series-parallel, CVD and STM converter when following the ideal Si device properties described in Eq. (2). As shown in the figure, under the given operating conditions, when using the ideal Si devices, the STC and MMSCRC have the smallest TSLI when total die area is less than 220mm<sup>2</sup>. This indicates the better device power loss

performance and less device power loss. When the total device die area is larger than 220mm<sup>2</sup>, the STM will have a better performance. Besides, when the total semiconductor device die area is around 170 mm<sup>2</sup>, the STC and MMSCRC convert will have the best performance in terms of device power loss. The STM convert best operating point occurs when total die area is

Fig. 10: TSLI vs total die area for ideal Si device

Fig. 11: TSLI vs total die area for 6 to 1 STC

around 240 mm<sup>2</sup>. The CVD converter most optimized total die area occurs at around 200mm<sup>2</sup>. For series parallel around 225 mm<sup>2</sup> is the best operation point.

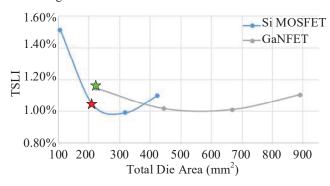

The example of using TSLI to find the topology best die area usage with fixed operation condition is shown in Fig.11. The design target is to design a 6 to 1 STC with 330 kHz, 600W. The figure is generated based on the real device information. Using the Infineon BSZ013NE2LS5I datasheet as the Si device technology reference and the EPC2023 as the GaNFET technology reference. Assuming the device HDFOM and NHFFOM is a fixed number if the same device technology is used. Also, the  $R_{ds(on)}$  consider to be a positive correlation with the  $V_{ds}$  and a negative correlation to the  $A_{die}$ . The device information under the design criteria for the analysis is shown in Table I.

TABLE I. DEVICE INFORMATION

| Part#         | $A_{die}(mm^2)$ | $R_{dson}(mhom)$ | $Q_g(nC)$ | Coss(nF) |

|---------------|-----------------|------------------|-----------|----------|

| BSZ013NE2LS5I | 6.6             | 1.25             | 18        | 1.2      |

| EPC2023       | 13.92           | 1.45             | 19        | 1.53     |

Based on the figure cand the table, several conclusions can be drawn:

- For the given operating condition and the device technology, the best operating point for the Si device converter occurs when total die area is 350mm<sup>2</sup> and for the GaNFET, the optimized total die area is around 550mm<sup>2</sup>.

- The Si device will only have better performance than GaNFET when the total die area is between 250~450mm<sup>2</sup>.

- TSLI can also help to decide whether the interleaved version should be adopted. It is possible that the interleaved version converter with larger total die area is closer to the A<sub>die\_optimized</sub> point, which means it will have less power loss.

Si version prototype is built as shown in Fig.12. The equivalent operating point of the prototype is the red star in Fig.11. It is a 2-phase interleaved version design, and the equivalent total die area is 211.1 mm<sup>2</sup>. It is not reaching the best operating point since considering the device count has to be integer and a 3-phase design will pass the best operating point. Passing the best operating point will lead to the cost increasing and the decrease of the converter power density.

Fig. 12: 6 to 1 Si prototype

A GaNFET version prototype is also developed. It is a single-phase design, and the total die area is 222.72mm<sup>2</sup>, the green star in Fig.9. The converter will have less power loss if a 2-phase design is adopted.

# IV. CONCLUSION

In this paper, a new method to evaluate and compare different topologies is described. It combines the TDPR and TSLI and provide different path for different level of comparison. Also, TSLI is discussed in this paper. It is a tool for selecting proper topology for certain application. Besides, it can be used as a most suitable device selection tool for certain topology under given operation condition. Moreover, design the converter total die area by approaching the optimized values from the left, the best total die area of the converter is achieved. This can help decide the number of interleaving phases of the design converter.

#### REFERENCES

- M. Shen, F. Z. Peng and L. M. Tolbert, "Multilevel DC-DC Power Conversion System With Multiple DC Sources," in *IEEE Transactions on Power Electronics*, vol. 23, no. 1, pp. 420-426, Jan. 2008

- [2] Anderson, J. Azurza, G. Zulauf, J. W. Kolar, and G. Deboy. "New Figure-of-Merit Combining Semiconductor and Multi-Level Converter Properties." *IEEE Open Journal of Power Electronics* 1 (2020): 322–38.

- [3] Wu, J., and X. Wu. "FoM Based Optimal Frequency and Voltage Level Design for High Efficiency High Density Multilevel PFC with GaN Device." In 2020 IEEE (APEC), 1911–15, 2020.

- [4] Wang, H., F. Wang, and J. Zhang. "Power Semiconductor Device Figure of Merit for High-Power-Density Converter Design Applications." *IEEE Transactions on Electron Devices* 55, no. 1 (January 2008): 466–70

- [5] Reusch, D., and J. Strydom. "Evaluation of Gallium Nitride Transistors in High Frequency Resonant and Soft-Switching DC-DC Converters." In 2014 IEEE - APEC 2014, 464–70, 2014.

- [6] Reusch, D., and J. Strydom. "Evaluation of Gallium Nitride Transistors in High Frequency Resonant and Soft-Switching DC–DC Converters." *IEEE Transactions on Power Electronics* 30, no. 9 (September 2015): 5151–58. Y. Yorozu, M. Hirano, K. Oka, and Y. Tagawa,

- [7] Reusch, D., and J. Strydom. "Effectively Paralleling Gallium Nitride Transistors for High Current and High Frequency Applications." In 2015 IEEE APEC, 745–51, 2015.

- [8] M. Shen, et al, "Comparison of traditional inverters and Z-source inverter for fuel cell vehicles," *Power Electronics in Transportation (IEEE Cat. No.04TH8756)*, Novi, MI, USA, 2004, pp. 125-132

- [9] W. Qian, D. Cao, J. G. Cintron-Rivera, M. Gebben, D. Wey and F. Z. Peng, "A Switched-Capacitor DC–DC Converter With High Voltage Gain and Reduced Component Rating and Count," in *IEEE Transactions on Industry Applications*, vol. 48, no. 4, pp. 1397-1406, July-Aug. 2012

- [10] Y. Zhang, Y. Cong, X. Li and J. Wang, "Comparative Study of Variable-Ratio Modular Multilevel Switched Capacitor Dc/dc Converter Topologies," WiPDA, Raleigh, NC, USA, 2019, pp. 99-105

- [11] F. Z. Peng, Hui Li, Gui-Jia Su and J. S. Lawler, "A new ZVS bidirectional DC-DC converter for fuel cell and battery application," in *IEEE Transactions on Power Electronics*, vol. 19, no. 1, pp. 54-65, Jan. 2004

- [12] Z. Ni, Y. Li, C. Liu, M. Wei and D. Cao, "A 100-kW SiC Switched Tank Converter for Transportation Electrification," in *IEEE Transactions on Power Electronics*, vol. 35, no. 6, pp. 5770-5784, June 2020

- [13] B. J. Baliga, "Semiconductors for high-voltage, vertical channel field effect transistors," *J. Appl. Physics*, vol. 53, no. 3, pp. 1759–17 644, Mar. 1989.

- [14] A. Q. Huang, "New unipolar switching power device figures of merit," in *IEEE Electron Device Letters*, vol. 25, no. 5, pp. 298-301, May 2004

- [15] Il-Jung Kim, S. Matsumoto, T. Sakai and T. Yachi, "New power device figure of merit for high-frequency applications," *Proceedings of International Symposium on Power Semiconductor Devices and IC's: ISPSD '95*, Yokohama, Japan, 1995, pp. 309-314

- [16] Cao, D., & Peng, F. Z. (2010). A family of zero current switching switched-capacitor DC-DC converters. Conference APEC1365–1372

- [17] Liu, Wen et al. "A 97% Peak Efficiency and 308 A/In3 Current Density 48-to-4 V Two-Stage Resonant Switched-Capacitor Converter for Data Center Applications." In 2020 IEEE APEC, 468–74, 2020.

- [18] Y.Li et al, "A 98.55% Efficiency Switched-Tank Converter for Data Center Application." IEEE Transactions on Industry Applications 54, no. 6 (November 2018): 6205–22.

- [19] M. Wei et al, "Zero Voltage Switching Switched-Tank Modular Converter for Data Center Application," 2019 IEEE 7th WiPDA, Raleigh, NC, USA, 2019, pp. 245-250

- [20] Y. Li, B. Curuvija, X. Lyu and D. Cao, "Multilevel modular switched-capacitor resonant converter with voltage regulation," 2017 IEEE Applied Power Electronics Conference and Exposition (APEC), Tampa, FL, USA, 2017, pp. 88-93