## **LETTER**

High-current recessed gate enhancement-mode ultrawide bandgap  $Al_xGa_{1-x}N$  channel MOSHFET with drain current 0.48 A mm $^{-1}$  and threshold voltage +3.6 V

To cite this article: Shahab Mollah et al 2021 Appl. Phys. Express 14 014003

View the article online for updates and enhancements.

## LETTER

## High-current recessed gate enhancement-mode ultrawide bandgap $AI_xGa_{1-x}N$ channel MOSHFET with drain current 0.48 A mm<sup>-1</sup> and threshold voltage +3.6 V

Shahab Mollah \* 0, Kamal Hussain 0, Abdullah Mamun 0, Mikhail Gaevski 0, Grigory Simin, MVS Chandrashekhar, and Asif Khan 0

<sup>1</sup>Department of Electrical Engineering, University of South Carolina, Columbia, SC-29208, United States of America

Received December 10, 2020; accepted December 20, 2020; published online January 7, 2021

We report a recessed-gate enhancement-mode  $Al_2O_3$ - $ZrO_2/Al_{0.6}Ga_{0.4}N/Al_{0.4}Ga_{0.6}N$  metal-oxide-semiconductor heterostructure field-effect transistor (MOSHFET) with drain current as high as 0.48 A mm<sup>-1</sup> at a gate-source voltage of +12 V. This was enabled by a pseudomorphic HFET structure with graded back barrier for strain management and to screen the growth interface from the channel. The device exhibited a threshold-voltage ( $V_{TH}$ ) of 2.75  $\pm$  0.57 V with absolute maximum  $V_{TH} = 3.6$  V, a +12.2 V shift from that for a depletion-mode MOSHFET fabricated on the same wafer. A 3-terminal breakdown voltage of 700 V was measured in the off-state, showing the viability of E-mode UWBG AlGaN for power electronics. © 2021 The Japan Society of Applied Physics

Supplementary material for this article is available online

ince the first demonstration of depletion and enhancement-mode AlGaN/GaN high electron mobility transistors (HEMTs), significant progress has been made in increasing their performance. 1-3) These advances have resulted from improving the material quality in the lattice mismatched growth of Al<sub>x</sub>Ga<sub>1-x</sub>N over sapphire/SiC/Si, the adoption of new device designs and the ability to form insulating gates on the  $Al_xGa_{1-x}N$  barrier layers.<sup>4-6)</sup> The depletion-mode (D-mode) HEMTs a.k.a heterostructure fieldeffect transistors (HFETs) and metal-oxide semiconductor HEMTs (MOS-HEMTs), a.k.a. MOSHFETs are now established commercial products with applications in RF/microwave power amplifiers. In a number of applications, enhancement-mode (E-mode) HFETs are preferable as they provide short-circuit protection power switches,<sup>7)</sup> eliminate the need of negative bias,8) and are useful in direct-coupled field-effect-transistor logic<sup>9)</sup> etc.

Achieving E-mode operation in AlGaN-GaN HFETs has been accomplished by: (i) decreasing the barrier thickness,  $^{2,10,11)}$  (ii) adding cap layers,  $^{12,13)}$  and (iii) using fluoride-based treatment. Kanamura et al. reported GaN MOSHFET with the highest peak drain current of 0.8 A mm $^{-1}$  (at  $V_{\rm G}=+10$  V) and OFF-state breakdown voltage of 320 V at  $V_{\rm G}=0$  V. Using linear extrapolation for threshold-voltage ( $V_{\rm THLE}$ ) they obtained  $V_{\rm THLE}=+3$  V. Asubar et al. demonstrated GaN MOSHFETs with  $V_{\rm THLE}\sim+5$  V and a peak current of 425 mA mm $^{-1}$ .  $^{16}$

Several research groups are developing ultrawide bandgap (UWBG)  $Al_xGa_{1-x}N$  channel HFETs for high-temperature, high-voltage, and high-power applications. UWBG  $Al_xGa_{1-x}N$  layers have higher breakdown field high-power applications. UWBG  $Al_xGa_{1-x}N$  layers have higher breakdown field high-power applications. UWBG  $Al_xGa_{1-x}N$  layers have higher breakdown field high-power applications. UWBG  $Al_xGa_{1-x}N$  layers have higher have been reported,  $a_x^{22-26}$  with currents as high as  $a_x^{22-26}$  Recently using fluorine treatment, Klein et al. reported E-mode UWBG  $a_x^{22-26}$  with a peak current of only  $a_x^{22-26}$  with  $a_x^{22-26}$

Here, we report a novel pseudomorphic  $Al_{0.6}Ga_{0.4}N/Al_{0.4}Ga_{0.6}N$  HEMT structure with graded back barrier to manage strain arising from lattice mismatch between AlN and  $Al_{0.4}Ga_{0.6}N$  without releasing strain through dislocations and cracks. This is in contrast with traditional AlGaN/GaN

HEMTs which are metamorphic in nature, with the GaN channel ideally being fully relaxed.

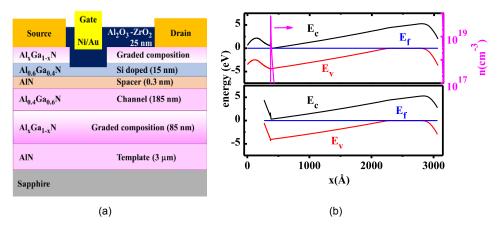

This structure was grown over a  $3 \mu m$  thick, high-quality AlN/sapphire template [Fig. 1(a)]. To achieve pseudomorphic registry, the total thickness beginning from the AlN template to the top surface was reduced to approximately half of our past design to reduce the total built-in strain.<sup>24)</sup> The back interface is now closer to the channel, potentially causing more traps. To solve this problem, the graded back barrier  $Al_xGa_{1-x}N$  (x from 1 to 0.4) layer was introduced to screen the growth interface from the channel while serving as a strain management layer by gradually varying the alloy composition as opposed to an abrupt junction. It was followed by an 1850 Å thick undoped Al<sub>0.4</sub>Ga<sub>0.6</sub>N channel and a silicon doped *n*-Al<sub>0.6</sub>Ga<sub>0.4</sub>N barrier layer. A 20 nm thick reverse composition graded Si-doped  $Al_xGa_{1-x}N$  (x from 0.6 to 0.3) layer was also deposited on top of the barrier to assist with ohmic contact formation, by presenting an effective Schottky barrier of 0.62 eV for Al<sub>0.3</sub>Ga<sub>0.7</sub>N compared to 2.7 eV<sup>29)</sup> for Al<sub>0.6</sub>Ga<sub>0.4</sub>N. The epilayer growth was carried out using low pressure metalorganic chemical vapor deposition (LP-MOCVD) as described elsewhere. 30) The backbarrier design enables a reduction in leakage currents by screening the substrate-epilayer growth interface, which improves the ON-OFF ratios, drain-currents, and the sub-threshold swing (SS).<sup>31,32)</sup> Figure 1(b) shows the simulated energy band diagram of structure epilayer structure of Fig. 1(a) in the cases of barrier recess (bottom) and without barrier recess (top). For recessed barrier structure, the bottom of the conduction band is above  $E_{\rm f}$ , indicating absence of 2DEG at  $V_{\rm G} = 0$  V which means normally-off operation, while for structure without barrier recessing there is clear dip of  $E_c$  below  $E_f$ .

The processing consisted of inductively coupled plasma reactive ion etching (ICP-RIE) for mesa-isolation followed by the formation of source drain ohmic-contacts. Zr/Al/Mo/Au (150/1000/400/300 Å) was deposited with E-beam evaporation and annealed for 30 s at 950 °C under  $N_2$  ambient using rapid thermal annealing.<sup>33)</sup>

For this study, perforated channel (PC) layout, <sup>34,35)</sup> was used to reduce access resistances. In the PC design, the gate area consists of the alternating regions of conducting straits separated by non-conducting islands where the channel material is completely removed (only under the gate but

<sup>\*</sup>E-mail: mmollah@email.sc.edu

Fig. 1. (Color online) (a) Schematic layout of recessed gate MOSHFET and (b) band diagram for epilayer structure of Fig. 1(a): without recessed barrier (top) and recessed barrier (bottom).

not in the G-S and G-D regions). The current flowing out of the gate straits therefore spreads out into larger area G-S and G-D regions which leads to smaller gap and contact access resistances (see supplementary information for more details available online at stacks.iop.org/APEX/14/014003/mmedia). The maximum reduction of the access resistances, by a factor of 2–3, occurs when the gap between the straits is around twice the width of the straits and the gate-drain distance is larger or comparable to the strait width.34) Accordingly, for the PC design we selected the width of the straits  $W_{\rm S} \approx 3.75 \, \mu \rm m$ , with blocking gaps between them  $W_{\rm B} \approx 8.25 \,\mu{\rm m}$  (see supplementary information). These dimensions were confirmed using scanning electron micrographs. This geometry corresponds to an optimal island/gap ratio of 2-2.5 as was determined following the procedure outlined in Refs. 27, 34, 35. In addition, in the PC layout, the reduction in average power density reduces the device temperature and also enables higher channel currents. The 250 nm deep current blocking islands were formed using a Cl<sub>2</sub> based RIE process with an etch rate of  $\sim 10 \,\mathrm{nm \, s^{-1}}$  after the formation of the source-drain ohmic contacts. Measurement on test structure shows that islands are completely insulating. The threshold voltage of PC device was found to be same as that of non-perforated control device.

Next the barrier was recessed to  ${\sim}10$  nm thickness using a slow ICP-RIE etching process with BCl<sub>3</sub>/Cl<sub>2</sub> gas mixture

followed by chemical treatment of etched surface with tetramethylammonium hydroxide (TMAH) solution to smooth out the surface as has been done with III-nitrides previously  $^{27)}$  The etch rate of 1 nm s  $^{-1}$  was calibrated using atomic force microscopy. Then a 25 nm thick  $ZrO_2-Al_2O_3$  insulator (ZrO2 followed by  $Al_2O_3$ ) stack was deposited in the recess region using atomic layer deposition technique before the formation of the Ni/Au gates. The gate-length, gate-source and gate-drain spacings were respectively  $L_G\approx 2.0~\mu\text{m},~L_{SG}\approx 1.5~\mu\text{m}$  and  $L_{GD}\approx 2.5~\mu\text{m}$ . The transistor surface was protected with PECVD deposited 400 nm thick SiO2 film for high-voltage breakdown measurements.

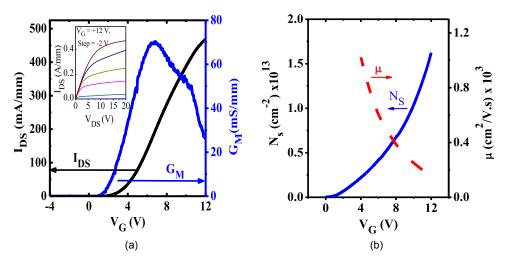

TLM was used to estimate the sheet-resistance ( $R_{\rm S}$ ) and the contact resistance to be  $\sim$ 1700  $\Omega/\Box$  and  $\sim$ 1.7  $\Omega$ -mm respectively. The  $R_{\rm S}$  value was within 10% of that measured using rfeddy current approach. Then PC devices were measured and the drain currents were normalized to the conducting portion of the channel width which is 15.6  $\mu$ m ( $W_{\rm S}$ ) for a 50  $\mu$ m ( $W_{\rm S}+W_{\rm B}$ ) width unperforated device.  $^{27,34,35}$ ) Figure 2(a) inset shows the source-drain characteristic curves for the recessed-gate Al<sub>2</sub>O<sub>3</sub>–ZrO<sub>2</sub>/PC-MOSHFET with  $L_{\rm G}\approx$  2.0  $\mu$ m,  $L_{\rm SG}\approx$  1.5  $\mu$ m and  $L_{\rm GD}\approx$  2.5  $\mu$ m. A peak current of 0.48 A mm<sup>-1</sup> was measured at a gate bias of +12 V while it is 0.15 A mm<sup>-1</sup> when normalized to the full channel width ( $W_{\rm S}+W_{\rm B}$ ). Even

Fig. 2. (Color online) (a) Transfer characteristics of a recessed-gate E-mode Al<sub>2</sub>O<sub>3</sub>–ZrO<sub>2</sub>/PC-MOSHFET with  $L_G = 2 \mu m$ ,  $L_{SD} = 6 \mu m$  and gate-width  $W_G = 50 \mu m$ . Inset shows the source-drain I–V characteristics and (b) Ns and  $\mu$ - $V_G$  dependencies for the device of Fig. 2(a).

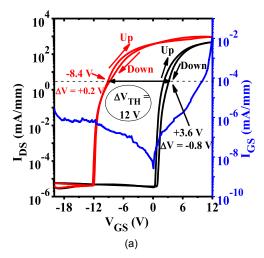

Fig. 3. (Color online) (a) Semi-log double-sweep transfer characteristics measured at  $V_{\rm DS} = +20$  V for the E-mode device of Fig. 3. The transfer curve for a D-mode device at  $V_{\rm DS} = +20$  V is shown for comparison. Also plotted is the gate leakage current of the E-mode device. (b) Breakdown voltage data for the E-mode device of this study.

with normalized to full channel width, the current density is the highest reported value till date for UWBG AlGaN channel Emode devices. Pulsed I-V measurement was done using DIVA D-265 dynamic IV analyzer with a pulse duration of 500 ns and low duty cycle of 0.1% to avoid self-heating. At  $V_G = +10$  V, the pulsed current was found to be  $0.38~\mathrm{A}\,\mathrm{mm}^{-1}$  (see supplementary information), a slight increase 0.36 A mm<sup>-1</sup> DC current. We estimated an ON-resistance  $(R_{\rm ON})$  of 18  $\Omega$  mm. In Fig. 2(a) we find  $V_{\rm TH} = +3.6$  V, from linear extrapolation, with a transconductance of 70 mS mm<sup>-1</sup>  $(L_{\rm G} \approx 2.0 \ \mu {\rm m})$ . To estimate the  $V_{\rm TH}$  variation, ten random devices were measured, spread over 1.5 cm to be representative of the whole quarter of a 2" wafer. The mean  $V_{\rm TH} = 2.75$  V with a standard deviation of 0.57 V (Fig. 4). The  $V_{\rm TH}$  variation across the wafer could be due to following two reasons: (i) recess depth variation (ii) variation of sheet resistance across the wafer. The most likely cause is recess depth variation  $\sim$ 2 nm, which would cause  $\sim 0.6$  V  $V_{\rm TH}$  shift, 36 potentially accounting for the observed variation. The sheet resistance variation is most likely caused by variations in carrier mobility across the wafer, as C-V measurements on the as-grown wafers showed similar  $N_s$  across the sample.

To determine the factors leading to the high drain current we extracted the gate voltage dependencies of  $N_{\rm S}$  and  $\mu$  as described in. <sup>33,37)</sup> Figure 2(b) shows  $N_{\rm S}$  reaching  $1.6\times10^{13}$  cm<sup>-2</sup> at  $V_{\rm G}=+12$  V.  $\mu$  is as high as 1050 cm<sup>2</sup> V<sup>-1</sup>. s<sup>-1</sup> near threshold  $V_{\rm G}=4$  V and decreases to 200 cm<sup>2</sup> V<sup>-1</sup>. s<sup>-1</sup> at  $V_{\rm G}$ +12 V, consistent with past reports.<sup>38)</sup> Figure 3(a) compares the semi-log transfer characteristics for the device of Fig. 2(a) measured at  $V_{\rm DS} = +20$  V with that for an identical geometry D-mode device (no gate-recess) fabricated on the same wafer, showing a  $V_{\rm TH}$  shift of +12.2 V due to the gate recess. The Emode device shows a hysteresis of 0.8 V between forward and reverse sweep of gate voltage, higher than that of D-mode (0.2 V) indicating higher trap charges at semiconductor/oxide interface or bulk. 39) We speculate this higher trap density might be from barrier recessing. This is supported by the slight increase in SS) increase after barrier recess from  $105 \pm 8$  mV/ decade for the non-recessed control devices to  $138 \pm 19$  mV mV/decade. The best E-mode device showed SS = 128 mV/ decade and an ON/OFF ratio >  $1.5 \times 10^8$ , while  $I_{GS} < 10$  $\mu$ A mm<sup>-1</sup> over the entire  $V_G$  range [Fig. 3(a)]. Three terminal

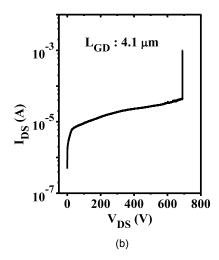

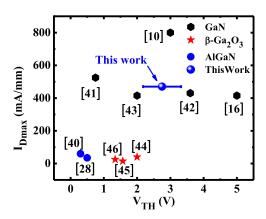

Fig. 4. (Color online) Comparison of our reported results with  $I_{\rm DMAX}$  and  $V_{\rm TH}$  of some normally-off wide bandgap GaN as well as UWBG AlGaN and Ga<sub>2</sub>O<sub>3</sub> channel HEMTs reported in literature.

breakdown voltage at  $V_{\rm G}=0$  V for a device with  $L_{\rm GD}=4.1$   $\mu{\rm m}$ , was found to be +700 V [Fig. 3(b)] which is above +600 V, required for power devices in automotive applications, and has not been reported for UWBG AlGaN E-mode devices. <sup>28,40)</sup>

We benchmark the  $Al_2O_3$ – $ZrO_2/Al_{0.4}Ga_{0.6}N$  channel E-mode devices against other wide (GaN) and UWBG ( $\beta$ -Ga<sub>2</sub>O<sub>3</sub> and AlGaN) channel E-mode devices in Fig. 4, where for GaN channel we only included devices with  $I_{DS}$  > 400 mA mm<sup>-1</sup>.<sup>41–46)</sup> Our results show highest current density among UWBG materials while compare favorably to some of the best values for GaN despite the greater maturity of GaN-channel HFET technology.

In summary, using recessed gate technology in combination with a new pseudomorphic back barrier structure with reverse graded top contacts and PC design, we have reported an Al<sub>2</sub>O<sub>3</sub>–ZrO<sub>2</sub>/Al<sub>0.6</sub>Ga<sub>0.4</sub>N/Al<sub>0.4</sub>Ga<sub>0.6</sub>N E-mode MOSHFET with drain currents as high as 0.48 A mm<sup>-1</sup>. This demonstrates that UWBG AlGaN channel E-mode devices are promising for power electronics.

Acknowledgments This research was supported by ARO contract W911NF-18-1-0029 monitored by Dr. M. Gerhold, and by AFOSR through Dr. K. Goretta. Part of the AlN template work was supported by ONR MURI program monitored by Dr. Lynn Petersen and the DARPA DREAM contract (ONR N00014-18-1-2033), Program Manager Dr. Young-Kai Chen, monitored by Dr.

Paul Maki. The characterization was partially supported by the National Science Foundation (NSF), ECCS Award nos. 1711322, 1810116, and 1831954.

ORCID iDs

Shahab Mollah ib https://orcid.org/0000-0002-2848

2959

Kamal Hussain ib https://orcid.org/0000-0001-7344

345X

Abdullah Mamun ib https://orcid.org/0000-0002-6210

7829

Mikhail Gaevski ib https://orcid.org/0000-0003-1172-0516

Asif Khan

ib https://orcid.org/0000-0002-4542-6553

- M. A. Khan, A. Bhattarai, J. N. Kuznia, and D. T. Olson, Appl. Phys. Lett. 63, 1214 (1993).

- M. A. Khan, Q. Chen, C. J. Sun, J. W. Yang, M. Blasingame, M. S. Shur, and H. Park, Appl. Phys. Lett. 68, 514 (1995).

- 3) U. K. Mishra, P. Parikh, and Y. Wu, Proc. IEEE 90, 1022 (2002).

- M. A. Khan, X. Hu, G. Simin, A. Lunev, J. Yang, R. Gaska, and M. S. Shur, IEEE Electron Device Lett. 21, 63 (2000).

- A. Tarakji, H. Fatima, X. Hu, J. P. Zhang, G. Simin, M. Asif Khan, M. Shur, and R. Gaska, IEEE Electron Device Lett. 24, 369 (2003).

- T. Palacios, A. Chakraborty, S. Heikman, S. Keller, S. P. DenBaars, and U. K. Mishra, IEEE Electron Device Lett. 27, 13 (2006).

- X. Lyu, H. Li, Y. Abdullah, K. Wang, B. Hu, Z. Yang, J. Liu, J. Wang, L. Liu, and S. Bala, IEEE Trans. Power Electron. 35, 8926 (2020).

- 8) K. J. Chen and C. Zhou, Phys. Status Solidi A 208, 434 (2011).

- 9) Y. Kong, J. Zhou, C. Kong, Y. Zhang, X. Dong, H. Lu, T. Chen, and N. Yang, IEEE Electron Device Lett. 35, 336 (2014).

- M. Kanamura, T. Ohki, T. Kikkawa, K. Imanishi, T. Imada, A. Yamada, and N. Hara, IEEE Electron Device Lett. 31, 189 (2010).

- T. Palacios, C. Suh, A. Chakraborty, S. Keller, S. P. DenBaars, and U. K. Mishra, IEEE Electron Device Lett. 27, 428 (2006).

- 12) X. Hu, G. Simin, J. Yang, M. Asif Khan, R. Gaska, and M. S. Shur, IEEE Electronics Lett. 36, 753 (2000).

- T. Mizutani, M. Ito, S. Kishimoto, and F. Nakamura, IEEE Electron Device Lett. 28, 549 (2007).

- 14) Y. Cai, Y. Zhou, K. J. Chen, and K. M. Lau, IEEE Electron Device Lett. 26, 435 (2005).

- L. Shen, T. Palacios, C. Poblenz, A. Corrion, A. Chakraborty,

N. Fichtenbaum, S. Keller, S. P. Denbaars, J. S. Speck, and U. K. Mishra,

IEEE Electron Device Lett. 27, 214 (2006).

- 16) J. T. Asubar, S. Kawabata, H. Tokuda, A. Yamamoto, and M. Kuzuhara, IEEE Electron Device Lett. 41, 693 (2020).

- 17) A. A. Allerman, A. M. Armstrong, A. J. Fischer, J. R. Dickerson, M. H. Crawford, M. P. King, M. W. Moseley, J. J. Wierer, and R. J. Kaplar, Electron. Lett 52, 1319 (2016).

- 18) A. Nishikawa, K. Kumakura, and T. Makimoto, Jpn. J. Appl. Phys. 46, 2316 (2007)

- 19) T. Razzak et al., Appl. Phys. Lett. 116, 023507 (2020).

- 20) J. Y. Tsao et al., Adv. Electron. Mater. 4, 1600501 (2018).

- 21) T. Nanjo, A. Imai, Y. Suzuki, Y. Abe, T. Oishi, M. Suita, E. Yagyu, and Y. Tokuda, IEEE Trans. Electron Devices 60, 1046 (2013).

- 22) S. Muhtadi, S. Hwang, A. L. Coleman, F. Asif, and A. Khan, 75th Annual Device Research Conf. (DRC), 2017 (South Bend, IN, USA), p. 143.

- 23) H. Xue, K. Hussain, T. Razzak, M. Gaevski, S. H. Sohel, S. Mollah, V. Talesara, A. Khan, S. Rajan, and W. Lu, IEEE Electron Device Lett. 41, 677 (2020)

- 24) M. U. Jewel, M. D. Alam, S. Mollah, K. Hussain, V. Wheeler, C. Eddy, M. Gaevski, G. Simin, M. V. S. Chandrashekhar, and A. Khan, Appl. Phys. Lett. 115, 213502 (2019).

- 25) A. G. Baca, A. M. Armstrong, A. A. Allerman, E. A. Douglas, C. A. Sanchez, M. P. King, M. E. Coltrin, T. R. Fortune, and R. J. Kaplar, Appl. Phys. Lett. 109, 033509 (2016).

- 26) N. Yafune, S. Hashimoto, K. Akita, Y. Yamamoto, H. Tokuda, and M. Kuzuhara, Electron. Lett 50, 211 (2014).

- 27) M. Gaevski, S. Mollah, K. Hussain, J. Letton, A. Mamun, M. U. Jewel, M. V. S. Chandrashekhar, G. Simin, and A. Khan, Appl. Phys. Express 13, 094002-1 (2020).

- 28) B. A. Klein, E. A. Douglas, A. M. Armstrong, A. A. Allerman, V. M. Abate, T. R. Fortune, and A. G. Baca, Appl. Phys. Lett. 114, 112104 (2019).

- 29) S. Mollah et al., Semicond. Sci. Technol. 34, 125001 (2019).

- S. Muhtadi, S. Hwang, A. Coleman, F. Asif, A. Lunev, M. V.

S. Chandrashekhar, and A. Khan, Appl. Phys. Lett. 110, 171104 (2017).

- 31) X. Liu, H. Y. Wang, H. C. Chiu, Y. Chen, D. Li, C. R. Huang, H. L. Kao, H. C. Kuo, and S. W. H. Chen, J. Alloys Compd. 814, 152293 (2020).

- 32) C. Ren, H. Shen, Z. Li, T. Chen, B. Zhang, and T. Gao, J. Semicond. 36, 014008 (2015).

- 33) X. Hu, S. Hwang, K. Hussain, R. Floyd, S. Mollah, F. Asif, G. Simin, and A. Khan, IEEE Electron Dev. Lett. 39, 1568 (2018).

- 34) G. S. Simin, M. Islam, M. Gaevski, J. Deng, R. Gaska, and M. S. Shur, IEEE Electron Device Lett. 35, 449 (2014).

- 35) S. Mollah, M. Gaevski, K. Hussain, A. Mamun, G. Simin, and A. Khan, Appl. Phys. Lett. 117, 232105 (2020).

- 36) Y. Cai, Y. Zhou, K. M. Lau, and K. J. Chen, IEEE Trans. Electron Devices 53, 2207 (2006).

- 37) P. A. Ivanov, M. E. Levinshtein, G. Simin, X. Hu, J. Yang, M. Asif Khan, L. Rumyantsev, M. S. Shur, and R. Gaska, IEEE Electron. Lett. 37, 1479 (2001).

- 38) S. Mollah et al., Phys. Status Solidi A 217, 1900802 (2020).

- 39) X. Sun, Y. Zhang, K. S. C. Liao, T. Palacios, and T. P. Ma, Int. Electron Devices Meeting, 2014 (San Francisco, CA, USA), 10.1109/ IEDM.2014.704707.

- 40) E. A. Douglas, B. Klein, A. A. Allerman, A. G. Baca, T. Fortune, and A. M. Armstrong, J. Vac. Sci. Technol. B 37, 021208 (2019).

- 41) C. S. Suh, Y. Dora, N. Fichtenbaum, L. McCarthy, S. Keller, and U. K. Mishra, Int. Electron Devices Meeting, 2006 (San Francisco, CA, USA), 10.1109/IEDM.2006.346931.

- 42) K. J. Chen, A. M. H. Kwan, and Z. Tang, The 1st IEEE Workshop on Wide Bandgap Power Devices and Applications, 2014, 10.1109/ WiPDA.2013.6695570.

- 43) R. Wang, Y. Cai, C. W. Tang, K. M. Lau, and K. J. Chen, IEEE Electron Device Lett. 27, 793 (2006).

- 44) K. D. Chabak et al., IEEE Electron Device Lett. 39, 67 (2018).

- 45) Z. Feng et al., Appl. Phys. Lett. 116, 243503 (2020).

- 46) Z. Feng et al., IEEE Electron Device Lett. 41, 333 (2020).