# An Overview of Hardware Security and Trust: Threats, Countermeasures and Design Tools

Wei Hu, Member, IEEE, Chip-Hong Chang, Fellow, IEEE, Anirban Sengupta, Senior Member, IEEE, Swarup Bhunia, Senior Member, IEEE, Ryan Kastner, Senior Member, IEEE, and Hai Li, Fellow, IEEE

(Invited Paper)

Abstract—Hardware security and trust have become a pressing issue during the last two decades due to the globalization of the semi-conductor supply chain and ubiquitous network connection of computing devices. Computing hardware is now an attractive attack surface for launching powerful cross-layer security attacks, allowing attackers to infer secret information, hijack control flow, compromise system root-of-trust, steal intellectual property (IP) and fool machine learners. On the other hand, security practitioners have been making tremendous efforts in developing protection techniques and design tools to detect hardware vulnerabilities and fortify hardware design against various known hardware attacks. This paper presents an overview of hardware security and trust from the perspectives of threats, countermeasures and design tools. By introducing the most recent advances in hardware security research and developments, we aim to motivate hardware designers and electronic design automation tool developers to consider the new challenges and opportunities of incorporating an additional dimension of security into robust hardware design, testing and verification.

Index Terms—Hardware security, security threat, security countermeasures, design tools, survey.

# I. INTRODUCTION

ODERN computing hardware devices are usually crafted by vendors with different established levels of trust and at discrete locations. These hardware components, while residing in a mixed-trust computing environment, are often shared among execution contexts of different security levels in a back-to-back manner. In addition, the rich connectivity features of modern computing systems expose critical hardware resources to attackers and open up doors for remote

Manuscript received June 13, 2020; revised October 3, 2020; accepted December 15, 2020. This paper was recommended by Associate Editor Y. Makris.

Corresponding author: Chip-Hong Chang. W. Hu and C. H. Chang contribute equally to this article. This research is supported in part by the National Natural Science Foundation of China under grant 62074131 and the National Research Foundation, Singapore, under its National Cybersecurity R&D Programme/Cyber-Hardware Forensic & Assurance Evaluation R&D Programme (NCR Award CHFA-GC1-AW01).

- W. Hu is with the School of Cybersecurity, Northwestern Polytechnical University, China. E-mail: weihu@nwpu.edu.cn.

- C. H. Chang is with the School of Electrical and Electronic Engineering, Nanyang Technological University, Singapore. E-mail: echchang@ntu.edu.sg.

- A. Sengupta is with the Discipline of Computer Science and Engineering at Indian Institute of Technology (IIT) Indore, India. E-mail: asengupt@iiti.ac.in.

- S. Bhunia is with the Department of Electrical and Computer Engineering, University of Florida, USA. E-mail: swarup@ece.ufl.edu.

- R. Kastner is with the Department of Computer Science and Engineering, University of California San Diego, USA. E-mail: kastner@ucsd.edu.

- H. Li is with the Department of Electrical and Computer Engineering, Duke University, USA. E-mail: hai.li@duke.edu.

attacks without requiring physical access to the victim. As a consequence, our computing hardware is ever closer to the front-line of a burning battle field and confronted with various security threats.

Hardware security threats can arise during various stages of the entire semiconductor life cycle, ranging from specification to fabrication and even recycling. They can result from unintentional design flaws [1]–[3], system side effects [4]–[7] and intended malicious design modifications [8]-[10]. They usually target security assets like cryptographic functions, secure architectures, intellectual property (IP) and machine learning (ML) models. While classic hardware security threats such as covert and side channels, hardware Trojans and reverse engineering (RE) are constantly evolving, recent powerful attacks exploit remote [6], [11], cross-layer [2], [3], [12], specification-compatible [8], [13] attack surfaces to compromise strong cryptographic primitives, isolation mechanisms, memory protection techniques and deep neural networks (DNNs). Understanding the different hardware security threats is an important first step to developing effective security countermeasures and design tools for circumventing them.

Security practitioners have been making tremendous efforts in developing effective hardware security countermeasures. An important first task is to create hardware security primitives that can serve as the building blocks for crafting an architectural level trusted computing environment enhanced with strong isolation mechanisms. Effective side channel protection and Trojan detection techniques are essential for verifying that the security primitives and trusted computing environment are free of design flaws, covert and side channels, and backdoors. Recent advances in ML and artificial intelligence (AI) have shown promise in developing more accurate detection solutions [14], [15]. IP protection techniques [16]–[19], on the other hand, protect security primitives, hardware designs and DNN models from RE, counterfeiting, model extraction and other adversary attacks.

Despite the numerous protection techniques for thwarting hardware security threats, security is still at large an afterthought in hardware design. Most security holes are exposed only after their exploitation by the threat actors. Over-reliance on software patches for hardware flaws also contributed to the trove of zero-day exploits for the attackers. In many ways, the database of common vulnerabilities and exposures (CVE) is just the tip of an iceberg. This is largely due to the lack of effective hardware security tools that allow automated specification, verification and evaluation of security constraints.

Best design practices and tacit knowledge are necessary but inadequate. We need better design tools to enforce hardware security properties for trust assurance. Proactive hardware information flow analyses facilitate vulnerability shielding and on-site monitoring. For example, unintentional hardware flaws and potential security vulnerabilities can be detected early by the recent security-driven hardware design flow [20]–[22]. As the rally of attacks and countermeasures is a neverending recursion, it is important to keep abreast of its latest development to continuously close the productivity gap of secure hardware design. If the tool chain does not constantly update to catch up with the latest design-for-trust and security verification methodologies, at the present rate of growth in hardware design complexity, security may terminate Moore's law before other physical limits.

At present, the hardware security space has grown to a point with many different specialized topics and each topic has been discussed in several focused survey papers. Examples of recent surveys on a few specialized topics are side and covert channels [4], [23], [24], reverse engineering [25], hardware Trojan [26], [27], physical unclonable function [28], logic locking [29] and security verification tools [30]. This paper provides a concise overview of hardware security from three perspectives, namely threats, countermeasures and design tools, with emphasis on niche, uncharted topics and updated recent developments for hardware security in a mixed-trust environment. We also identify potential future research directions with this overarching vision.

The reminder of this paper is organized as follows. A brief description about the common hardware security properties is introduced in Section II. In Section III, an overview of the classic as well as state-of-the-art hardware security attacks is provided. Section IV reviews the frequently used hardware security mechanisms for thwarting these attacks. Section V summarizes various secure hardware design tools from both the academia and industry. Some research challenges and opportunities in the discussed topics are highlighted in Section VI and the paper is concluded in Section VII.

#### II. HARDWARE SECURITY PROPERTIES

Hardware security properties are formal specifications about invariant security-related behaviors of circuit designs. Security threats and attacks usually cause violations of desirable security properties while security countermeasures implement mechanisms for enforcing them. Security properties provide important constraints to security verification tools. In the following, we briefly cover different hardware security properties.

# A. Dependability

Reliability, Availability and Safety are three important attributes to assess the trustworthiness of a computing hardware device to perform the expected function during its service lifespan. Reliability is the ability to produce the intended functions under normal operation and even under small fluctuations in the computing environment for a specified time period. Availability is the percentage of time a system is able to serve its intended function. Safety is the ability to avoid

catastrophic consequences for the user or the environment. Catastrophic failures represent only a small subset of all failures. Hence, safety is a relative and subjective attribute that cannot be measured directly. Critical path timing failures, single-event-upsets and aging effects can be resulted from security exploits, such as fault injection [31] and recent ML attacks [32], to reduce the reliability, increasing the downtime or impose safety hazards upon a system.

## B. Confidentiality

Confidentiality is a general security property stating that secret information should never be obtained or inferred by observing a public output or memory location. While the direct movements of sensitive information can be easily identified, the stealthy leakage through system side effects and backdoors can be more subtle. These include the covert and side channels [4], [33] in cryptographic cores, system bus and high-performance elements such as caches and branch predictors [2], [3] as well as hardware Trojans [34].

#### C. Integrity

Integrity is the dual property of confidentiality. It requires that a trusted data object should never be overwritten by an untrusted entity. Integrity attacks often target critical memory locations, e.g., the cryptographic key, program counter and privilege registers. These attacks are usually a first step for performing further malicious activities, e.g., hijacking the control flow [35] and fooling machine learners [36].

# D. Isolation

Isolation is a two-way property requiring that two hardware components of different security levels should not directly communicate with each other. It is a common security property that needs to be enforced in System-on-Chip (SoC), modern processors and the cloud, where the interaction between the secure and normal worlds are strictly controlled. However, there are still ingenious security exploits that break strong isolation mechanisms such as ARM Trust-Zone [37] and Intel Software Guide Extension (SGX) [38].

# E. Constant Time

The *constant time* security property enforces that the hardware design should take invariant amount of time to compute and produce the result under different input combinations. In other words, we cannot learn any information about the inputs by observing the computation time. Violation of the constant time property creates a timing channel that can leak sensitive information. Such violation can result from performance optimizations [2], [3], e.g., cache and branch predictor as well as fast path in arithmetic units.

# F. Quantitative Security Properties

Quantitative security properties allow more accurate measurement of hardware design security, e.g., assessing the severity of a vulnerability or evaluating the effectiveness of

3

a security protection mechanism. Typical examples of such quantitative properties include randomness of the output of a cryptographic function [20], leakage of side and covert channels [39] and strength of a security mitigation [40]. These security properties are usually measured using statistical and information theoretic security metrics [41]. The security of approximate computing and machine learning are more often measured quantitatively.

#### III. HARDWARE SECURITY THREATS

#### A. Architectural and System Threats

1) Secure Boot Attacks: A secure boot starts by loading code from an immutable boot ROM, correctly initializing critical peripherals, configuring security and system settings, authenticating and properly loading boot images and application code and properly sanitizing data upon reset. Many issues arise due to the system being configured incorrectly, e.g., system memory space not protected. Other issues relate to data not being properly erased (e.g., keyboard strokes stay in buffers). These and many other real-world secure boot attacks are documented by Bulygin et al. [42].

The secure boot process is fairly well-documented making it amenable to formal property specification [43], [44]. Such properties relate to isolation and access control between boot stages (e.g., the next stage can only access a limited subset of the previous stage information), determining if a boot stage completes fully before continuing to the next stage and protecting boot state information properly upon completion (e.g., it cannot be modified and can only be read from boot code). Additionally, there should be a sequence that causes the hardware to fully reset all data, code, configuration and any other state, and the system should only load from the boot ROM upon reset.

2) Firmware Attacks: Firmware is the low-level software that controls the interaction and behavior of a piece of hardware or IP core. Firmware plays a key role in determining the security of the SoC. Incorrectly setting configuration registers can lead to catastrophic consequences and open the door to leaking confidential information, unsafe behaviors and critical flaws that can be exploited by attackers. An analysis in 2014 showed that at least 140,000 devices had a firmware vulnerability [45]. This should not be too surprising as determining the correctness of the firmware is challenging as each hardware core has different configurations that interact with the overall system in a non-obvious manner.

Firmware is particularly important for SoC architectures. Modern SoC architectures are a patchwork of hundreds, sometimes thousands, of different IP cores that are cobbled together from in-house sources, outside vendors and open source repositories. Ensuring that these are functionally correct is a massive undertaking; determining that they lack security flaws is even more challenging. Subramanyan *et al.* [46] provide good motivation and the early work in this space.

Device drivers are typically small, but important pieces of low-level C or assembly code that play an important role in firmware security. They provide an application program interface (API) that is used to deliver data to/from a device,

query the status of the device, or set the device mode. More often than not, device drivers require access to critical parts of the system and thus it is crucial that they execute efficiently, handle real-time constraints and be secure. A first step towards synthesizing correct, efficient and secure device drivers is to create properties around on-chip communication protocols like Advanced Extensible Interface (AXI) and Wishbone [47]. Properly handling access control to the hardware resource is also important for secure computing with devices [48].

3) Dynamic Random Access Memory (DRAM) Threats: The Coldboot [49] and Rowhammer [50] attacks demonstrate the importance of protecting sensitive data stored in DRAM. Coldboot exploits the physical phenomenon that DRAM data persists for a short amount of time even after powering off the memory. This time can be extended by cooling down the memory, which further reduces the leakage of current from the DRAM capacitors. Researchers used this idea to show how to remove a DRAM from one computer, place it into another and grab the data. Other malicious attacks are also possible. Rowhammer exploits another physical vulnerability of DRAM, this time using the fact that DRAM data can be altered by accessing nearby data. The attacker locates some of their data next to some critical data in DRAM. By changing the values of their data, the attacker induces circuit noise that causes the target sensitive data to change.

4) Cache Attacks: Cache attacks [4] exploit information leakage though cache state and are extremely effective at extracting protected information. The cache is a shared resource and any process that uses it can leave traces about their computation, in particular, the memory addresses they accessed.

Cache timing attacks can be categorized as time-driven and access-driven [23]. A time-driven attack measures the execution time of the victim process. The attacker manipulates the contents of a shared cache and observes the timing of another process (e.g., a cryptographic operation). The timing is effected by cache hits and misses, which provides information about the key [51]. An access-driven attack extracts information by measuring the time that it takes the attacker to perform a cache access [52]. If a particular cache line is accessed by the victim process, the attacker would observe a cache hit and vice-versa. For instance, an attacker can identify data access patterns by the victim (e.g., which S-Box entries are being accessed during AES execution) and use this information to extract the confidential information (e.g., the secret key). Cache side channel is a powerful attack that is often used in combination with other attacks, e.g., Meltdown [3] and Spectre [2] as we will discuss.

5) Speculative Execution Attacks: Meltdown [3] and Spectre [2] are the first of a series of attacks that leverage speculative execution, out of order execution, caching and other architectural performance enhancements to break isolation and other security policies.

Meltdown enables unauthorized processes to read data from any address that is mapped to the current process's memory space. Meltdown exploits a race condition where the unauthorized process attempts to access privileged data. A privilege check eventually squashes the execution of that code, but not before the data is temporarily loaded into cache. The attack then uses a cache side-channel attack (SCA) to determine contents of the data.

Spectre is a vulnerability that tricks a victim process to leak its data. Many processors perform speculative execution by branch prediction. Spectre uses the fact that this speculative code leaves traces of its execution in the cache whose information can be extracted using a cache SCA (similar to Meltdown). Spectre trains a branch predictor to make a wrong decision and then wraps code that should not be executed in a condition. The code is speculatively executed since the branch predictor is wrong. It eventually gets squashed but it leaves important information in the cache state, which is extracted via a cache SCA.

6) Code Reuse Attacks: Code reuse attacks carefully use existing snippets of software to perform computation of the attackers choosing. Return oriented programming (ROP) [53] is an example of code reuse attack where existing code fragments (or gadgets) are carefully sequenced to perform a malicious act. The attacker's goal is to divert the control flow by gaining control of the call stack and invocating the first gadget, which in term calls subsequent gadgets. This allows the attacker to perform actions of their choosing.

#### B. Covert and Side Channels

Covert and side channels have emerged as two types of potent information leakage channels. Micro-architectural features targeted towards performance improvement, e.g., shared cache, speculative control, and hyper-threading, create new covert and side-channel security issues. Covert channels use nontraditional communication mechanisms to leak critical information – often between an insider process (e.g., a Trojan Horse program) and an outsider spy process. These two processes do not communicate directly through traditional mechanism, e.g., shared cache. Instead, a Trojan process may communicate with a spy process by modulating timing of specific events on a shared resource or writing/checking if a file is locked. On the other hand, SCAs utilize physical side-channel parameters (supply current, event timing, electromagnetic emission, etc.) to leak on-chip secrets.

While some covert channels require sharing of hardware resources among exchanging parties (e.g., shared cache), others may exist among hardware components that are physically isolated or not even in proximity. Hardware-oriented covert channels are typically initiated by introducing manipulation or exploitation of certain functional (response to a fault) or parametric (e.g., timing, power and electromagnetic radiation, etc.) behavior of the hardware that is observed to decode the secret information being transmitted. Side channels are unintentional information leakage where an attacker tries to extract information from a target computing system utilizing its inherent implementation vulnerabilities. Similar to covert channels, side channel also requires the observation of certain functional or parametric behaviors at runtime.

1) Timing Channel: A timing channel is established through the observation of the execution time of a certain process. Timing-based covert and side channels may exist

due to the sharing of hardware resources across different software processes. Moreover, an IC may contain fast and slow execution paths that reveal information regarding the underlying operation being executed (e.g., arithmetic vs. Boolean operation [54]. While chip designers introduce novel features to improve execution time, more timing channels are being discovered. These channels may facilitate information transfer at a rate of up to few megabits per second [55]. These timing channels are often practical only under certain assumptions regarding the attacker and the victim. For instance, to form a timing channel using some cache-based attack, the victim and the attack processes must execute on the same processor core for a specific amount of time. The attacker's ability to adhere to these assumptions can significantly impact the capacity or sensitivity of the channel.

Over the last few years, researchers have demonstrated the feasibility of a wide range of timing-based covert and side channels. Szefer [4] presents a comprehensive overview of timing attacks that are feasible due to vulnerabilities in processor architecture. Execution time differences for various instructions, resource sharing, impact of functional unit's state on program execution (e.g., branch prediction) and timing behaviors of memory subsystems (e.g., cache and prefetcher, etc.) are some characteristics of modern processors that lead to microarchitectural timing channels.

2) Power Channel: In power SCA [56], [57], an attacker measures the switching power traces of an electronic component during operation and then employ mathematical analysis on the traces to extract secret information. Basic premise of such an attack lies in the fact that the transient power traces of a chip leak its internal switching patterns, thereby leaking data secrets (e.g., cryptographic key) through the switching behavior. Shrinking technology nodes and increasing power density have made it possible for attackers to carry out power SCAs with increasing degree of success.

Attackers have utilized a wide-variety of techniques to extract information. A simple visual inspection of the power signal information known as Simple Power Analysis (SPA) [56] is utilized when the internal implementation is known to the attacker. If the attacker has complete access to a device, he/she resorts to template matching attacks. Template attacks [5] consist of a profiling step and an attack step. The attacker has the freedom to collect many samples in the profiling phase as he/she fully controls the device. In the profiling step, the parameters of the design are learnt from a device and a profile of the device is created. This profile is applied as a template to other copies of the same device in the attack phase.

Differential Power Analysis (DPA) [56] relies on the principles of statistical hypothesis testing, where the attacker measures the power consumption traces of a target device over several time steps by feeding a large number of input vectors. The attacker then partitions the resulting power traces into subsets. The difference in the average values of these subsets reveal the presence or absence of information leakage in the design. In the absence of leakage, the difference in average values tends to be zero as the choice of assigning a trace to a subset is purely random and is uncorrelated with the power measurements. On the other hand, a statistically

significant difference implies that there exists a correlation between the partitioning and trace measurements. Unlike SPA, DPA does not require any knowledge about the underlying implementation and can be carried out in highly noisy environments. Correlation Power Analysis (CPA) [57] relies on using statistical models to estimate the correlation between the secret and the power consumption of the device when the secret is being used for computation. A CPA typically relies on building a model of the device's dynamic power consumption. The activity factor  $\alpha$  is modeled using Hamming distance (HD) or Hamming weight (HW). The change in the bits of the input that cause a change in  $\alpha$  can be modelled by the HD between the initial input and the changed input values or the HW of an input in case of a software implementation (e.g., on smart card). This HD or HW model serves as a good approximation to estimate the power consumption of a device. During a CPA attack, the attacker guesses the value of the secret and obtains as many traces as possible for each guess of the secret.

ML algorithms have also been applied to both profiling-based and non-profiling-based SCAs. In profiling-based approaches, where attackers have access to an exact copy of the attacked hardware, a supervised ML model can be trained based on data points in different profiling traces [58]. In non-profiling based approaches, where attackers do not have access to a copy of the device, unsupervised ML algorithms such as clustering are applied to reveal the secret information [59].

The growth of cloud-based service providers like Amazon and Google has led to an increase in multiple users sharing the same hardware resource, such as a Field Programmable Gate Array (FPGA). In such multi-tenant operating environments, remote power attacks are becoming feasible when an untrusted party shares resources with a trusted one [6], [11]. The attacker can infer information regarding the trusted program executing in the same resource as the attacker by accessing the power delivery network. Furthermore, in cloud settings, new attacks are emerging where malicious power/current surge caused by an untrusted process can create denial of service attack in another process mapped to the same FPGA device [60].

3) Electronmagnetic and Photonic Channels: Unintentional Electronmagnetic (EM) radiation from electronic devices is a well-known concern for semiconductor vendors due to the possibility of interference with wireless communication channels and potential health risks to the end-users [24]. However, EM radiation during a security-critical process could also lead to vulnerabilities due to its potential to leak information regarding the operation. EM emission characteristics are largely device dependent; hence it is difficult to develop break-onebreak-all scenario for the attackers. The effectiveness of small magnetic loop antennas in detecting EM emission from ICs has been evaluated in various studies [61]. The signals captured by magnetic loop antennas are digitized for the extraction of the secret. EM signal for information leakage can be observed in various ways. Visual inspection of the time-domain representation of EM signals is called simple EM analysis (SEMA) [62]. SEMA can be considered as the EM equivalent of the SPA. EM signal can be transformed to frequency domain to perform visual analysis of the spectrogram to reveal information. SEMA approach has been used to extract secret information from various cryptographic processes, including RSA, Elliptic Curve-based Diffie Hellman (ECDH) and Elliptic Curve based Digital Signature Algorithm (ECDSA) [63]. Algorithms like ECDH and ECDSA are suitable for mobile devices and Internet of Things (IoT) platforms where a malicious end-user with complete physical access can compromise the cryptographic process using SEMA approach.

Simple visual observation of EM signal may not be sufficient for revealing information from many applications. A more sophisticated attack vector called Differential EM Analysis (DEMA), a variant of DPA for EM is proposed [64]. However, DEMA requires a large number of EM traces of a given operation to extract the secret bits that are involved in the process by observing the variation in EM emission. With the alteration of signal or register states between logic high and low, energy dissipation in a CPU varies and consequently the EM emission is impacted [61]. Moreover, alteration of signal states in a CPU depends on the instructions and variables. Hence, observation of EM emission for a large number of operations is useful in retrieving the instructions being executed and intermediate states of different variables.

4) Fault Injection: Fault attacks form a potent class of SCAs wherein the attacker can subvert the execution of the hardware by deliberately injecting a fault. A well-placed fault attack could cause the system to reveal secret information, such as the key bits [65]. Fault attacks have also emerged as major threats for a program executed by a processor. For example, precisely flipping the status flags can allow an attacker to bypass the authentication process giving unauthorized control or privilege escalation [7]. These faults can be injected by causing a glitch in the underlying hardware. The attacker typically attempts to manipulate one or more of the devices' power supply or clock or utilizes a highly powerful laser to control the temperature of the device.

Fault attacks have been demonstrated on several cryptofunctions such as Data Encryption Standard (DES), Advanced Encryption Standard (AES), International Data Encryption Algorithm (IDEA), Secure and Fast Encryption Routine (SAFER) and Blowfish. However, not all faults are exploitable. Hence, it requires careful profiling of the fault space to identify the set of exploitable faults. In AES, it has been demonstrated that a well-placed fault injected in between the seventh and ninth round operation could cause the device to reveal the entire key with as few as eight faulty ciphertexts.

More recently, attacks like PlunderVolt [31], VoltJockey [38] and CLKScrew [7] have demonstrated that fault attacks are not restricted to crypto-cores but can also impact general purpose SoCs. Both CLKScrew and Plundervolt are software generated fault attacks. The attacker leverages the access to clock or energy management APIs for injecting the fault. CLKScrew exploits the dynamic voltage frequency scaling utility to extract secrets from ARM Trust-Zone. PlunderVolt utilizes the power management utility to compromise the execution of Intel's SGX.

Apart from the above discussed side and covert channels, test and debug infrastructures usually provide privileged access to critical hardware resources such as machine state and configuration registers. Insecure test and debug ports are potential

attack surfaces for launching powerful low-level attacks. In 2012, a military grade FPGA was reported to have a backdoor in the JTAG port, which allows the attacker to retrieve the AES key for decrypting the protected bitstream [66]. Rajput *et al.* [67] summarized the security attacks and protections for the commonly used JTAG port. Valea *et al.* [68] performed a more complete survey of security threats and countermeasures in different test standards.

# C. IP Theft and Counterfeiting Threats

Modern SoC and IC designs usually involve different forms of IPs, e.g., register transfer level (RTL) design (soft IP), gate level netlist (firm IP) and physical layout (hard IP). The owner's IP is outsourced to trustworthy offshore design houses/foundries for SoC integration or IC fabrication to reduce design complexity, time to market pressure and manufacturing cost. This can lead to various IP security threats.

In IP counterfeiting, an attacker illegally imitates the original design, creates counterfeited versions of the IPs/ICs, and sells them in the brand name of a genuine supplier. In cloning attack, an adversary copies the original design and supplies cloned versions of original IPs/ICs under his/her own label. These attacks result in integration of fake IPs/ICs in the electronics systems used in critical applications such as military, healthcare and banking, etc. The fake designs not only sabotage the genuine vendor's reputation and revenue but also lead to large consequences: (i) affecting the reliability and performance of the critical systems; (ii) containing malicious or backdoor logic that cause leakage of confidential information or assist to override the critical systems [69].

In RE attack, an attacker back engineers the design in order to deduce the design structure or functionality. This can be done by RE its various design forms such as RTL, netlist, layout (GDS-II), mask or a manufactured IC [70]. RE attack allows the adversary to realize his/her intentions of inserting backdoors or Trojans into the design and also enables counterfeiting and IC overbuilding, thereby entails reassessing trust in electronics hardware [70], [71].

# D. Hardware Trojan

1) Classical Digital Trojans: Early HTs typically use a single trigger signal to activate the Trojan under a rare event. The Trust-HUB benchmarks [72] employ such a simple trigger mechanism, which is very sensitive to switching probability analysis. The De-Trust [73] project provides some HT designs that use multiple discrete trigger signals so that each trigger signal will be able to switch normally. These HTs, when activated, will violate explicitly specified design behavior in the design specification.

A comprehensive list of Trojan taxonomies [74], [75], benchmark sets [72], [75] and lessons [27] of these classical HT research have been documented. In what follows, we will discuss some recent HT designs and attacks.

2) Exploitation of Don't Care Conditions: Fern et al. [8] leveraged external don't care conditions (i.e., unspecified functionality) for HT design. For example, the design output may be unspecified under certain "illegal" input conditions or when

the output is not yet valid. Such don't care HTs can be hard to detect since they are out of the functional specification. A more recent work hides HT in the unspecified functionality in obfuscated hardware designs [13]. Based on the fact that the design functionality under incorrect obfuscation keys cannot be explicitly specified in order to protect the correct key, the IP designer has numerous flexibility in implementing the obfuscation logic, including inserting malicious circuitry.

Nahiyan *et al.* [76] proposed a HT design by adding malicious state to the finite state machine (FSM). The idea is to use unoccupied state encoding to insert a floating Trojan state. The FSM will never transit to the dangling Trojan state during normal operation. The Trojan can be activated using fault attack to force the FSM into the malicious state.

Hu *et al.* [34] leveraged satisfiability don't cares for HT insertion. The Trojan uses a pair of signals that will never reach a specific input combination (e.g., cannot be logical '0' simultaneously due to path correlation) under normal operation as triggers. Thus, the Trojan will never be triggered during normal run although each trigger signal is able to switch. Similarly, fault injection is used to force the trigger signals into a desired condition to activate the Trojan. Such Trojan has recently been demonstrated on a multi-tenant FPGA, where the attacker can remotely activate the Trojan by deploying power wasting circuitry to induce considerable fluctuations in the onchip signal delays and, consequently, timing faults [77].

- 3) Analog Trojans: Researchers have also demonstrated how to create analog HTs through slight modifications of the design layout [78]. Becker et al. [79] and Kumar et al. [80] insert analog HTs by changing the dopant polarity or ratio of input to transistors to cause a short circuit. These dopantlevel HTs can be hard to identify since they do not introduce additional transistors but only modify circuit parameter. Liu et al. [10] demonstrate an analog HT that leaks the AES key by slightly modulating the amplitude or frequency of wireless transmission without violating the protocol specification. The HT cannot be detected using routine testing methods since it does not change the design functionality. The A2 Trojan [9] is a small and stealthy malicious analog circuitry. It only adds a single capacitor that siphons charge from nearby wires as they transit. When the capacitor is fully charged, it drives a victim flip-flop to a desired value to perform malicious activities, e.g., elevating privilege. The Trojan will remain dormant if the capacitor resets through leakage current due to inactive switching activities in the charging wires. A more recent work exploits analog/mixed-signal circuits for hardware Trojans, whose trigger mechanism is deployed in the digital domain while the payload is transferred to the analog domain via the on-chip test infrastructure [81].

- 4) Trojans Induced Aging and Performance Degradation: In a nanoscale semiconductor device, physical occurrences such as hot-carrier injection, electromigration, time-driven dielectric breakdown and negative bias temperature instability (NBTI) lead to aging phenomenon [82]. These physical occurrences are the result of the restrained design margins and transistor scaling. Even a small change in the transistor parameter may significantly affect the device performance and reliability [82], [83]. Device aging may result in failure of

semiconductor devices during critical operations. Heavy reliance of SoCs on third party IPs (3PIPs) raises the possibilities of aging attacks. A rouge 3PIP vendor may accelerate the device aging process by covertly making malicious modifications in the design of 3PIPs, with an aim of causing a premature failure of an electronic device within the warranty period [84].

One prevalent way of launching an accelerated aging attack is through NBTI stress. NBTI refers to the increase in threshold voltage of a P-type metal oxide semiconductor (PMOS) transistor over time due to the charges trapped under the gate area by the negative bias applied between its source and gate terminals [82]. As NBTI is heavily dependent on the dynamic operating condition of the device. Attackers can control the supply voltage, temperature and input signal probability to increase a device NBTI stress to accelerate its aging effect. An attacker may force the device into continuous stress even in standby mode, by modifying/adding malicious circuitry. To accelerate the aging process, the attacker can use selected input vectors to maximize the NBTI stress on the target devices.

This attack is demonstrated by Kachave *et al.* [84] on digital signal processor (DSP). In this attack model, an attacker continuously applies NBTI stress during the standby mode of the device to accelerate the aging by either hardware or software modifications. In the hardware-based attack, an attacker introduces some alterations in the DSP hardware such that a rare event (hidden Trojan) triggers the application of input vectors that maximize NBTI stress. In the cross-layer attack, an attacker builds a program that automatically applies the test vectors on the DSP circuit to create the greatest stress during the operational mode.

5) Trojans Insertion Through Malicious EDA Tool: HT threat arises primarily from untrusted design process and supply chain. EDA tools, as an important element in this untrusted environment, can also assist in Trojan attacks.

Krieg et al. [85] demonstrated an automated HT insertion technique through light-weight modification to an open source synthesis tool. The modified FPGA synthesis frontend deploys a special look-up table (LUT), whose simulated design behavior is totally correct. In a second attack phase, the malicious back-end identifies this LUT and changes its functionality when translating the design into bitstream, which acts as a Trojan trigger. The challenge in detecting such HT lies in the lack of bitstream verification tools. In their successive work, the differences in how the don't care 'X' appears in logic simulation and implementation are exploited to create a Trojan trigger. The trigger signal 'X' will be logic 0 during simulation and logic '1' in hardware implementation. Thus, the HT will remain inactive during the design phase and will be automatically activated upon configured onto the FPGA. Similarly, light-weight modification to the synthesis tool will facilitate automated insertion of such HTs.

Besides, several HTs target emerging computing technologies. In [13], a HT is hidden in the obfuscation logic intended for IP protection. In [6], a remote HT attack targeting multitenant FPGAs deployed in the cloud was demonstrated.

# E. Vulnerabilities and Attacks on Deep Learning Networks

1) Adversarial Examples: AI has been promoting fast in the recent decade, thanks to various deep neural networks (DNNs), which learn high-level features from raw data to solve many challenging object recognition problems end-to-end with very high accuracy and without requiring human intervention. Similar to any other fast-advancing fields, the infiltration of deep learning models into safety and security critical applications such as self-driving cars and face recognition payment systems make them an interesting target of attack.

A well-known vulnerability has been exposed in a surprising way by the input of adversarial examples. It was initially demonstrated by Szegedy et al. [86] that small intentionally designed perturbations added to the original input image can create an optical illusion for the DNN classifier at the inference phase. Adversarial example generation algorithms, such as fast gradient sign method [87], universal perturbations [88] and Carlini and Wagner (C&W) attack [89], have succeeded in subverting the deep learning model output with high success rate. Hardware accelerator for the generation of adversarial examples has also been proposed to improve the attack efficiency [36]. The imperceptibility of the perturbation and generalization ability across models further aggravate the damage of such attacks. Recent research suggests that adversarial example attacks can also be applied in the physical world [90] and incorporated with cameras [91]. Adversarial examples work across different media and are recognized by Open AI Inc. as a concrete problem in AI safety. They shatter the confidence of DNN implementation robustness, and extend the DNN attack surface beyond the software boundary. Although conventional techniques such as laser beam interference, memory collision and rowhammer have been deployed as means to attack DNN hardware, they must be subtly and significantly devised to exploit the unique characteristics of DNN. The target asset and threat model of a DNN attack are in many ways different from those of the cryptosystem. DNN has the transferability, noise immunity and graceful degradation properties that are absent in many other domain-specific computing solutions. Effectiveness and efficiency of attacks on DNN are often data, model and application dependent. In general, data plays a more significant role than the model and the model plays a more significant role than parameter optimization in the inference.

2) Hardware-oriented Attacks: Artificial Intelligence of Things (AIoT) is the convergence of AI and IoT infrastructure. Placement of cognitive computing and AI processing at the IoT edges can benefit in terms of privacy maintenance, bandwidth reduction and responsiveness. As a core enabler of innovation, dedicated hardware accelerators for efficient on-device inference are increasingly used for edge AI deployment. Commercially available hardware accelerators for local AI inferencing include Intel Neural Compute Stick 2 (NCS2), Google Coral, Nvidia Jetson Nano and Xilinx edge AI IP core. This new wave of edge intelligence in the AIoT age invites new attack vectors, which are methodologically different from software-oriented DNN attacks like the previously described input of adversarial examples. This is because adversarial examples

that assume any input pixel can be precisely altered to any arbitrary value may not achieve the same desired outcomes when they are presented to a DNN hardware accelerator.

Fault injection attacks such as laser injection [92], glitch disturbance [93], memory collision [94] and rowhammering [95] can impact circuit operations within the DNN and are potential threats to edge intelligence. Straightforward fault injection will cause denial of service, but it also alerts attention. For instance, overheating the DNN hardware will not only affect classification but also suspend the system. Immediate damage control may be triggered to limit the benefits that can be reaped from suck attacks. Existing fault attacks on DNN focus mainly on model weight manipulations [95], [96]. Falsifying model parameters such as saturating last layer's bias [32] to converge the output to one specific class regardless of inputs or constraining modification magnitude on the weights of all layers [96] can be used to create selective input misclassification. These simulated attacks assume that the data stored in memory can be precisely manipulated to arbitrary values through fault injection, which are not realistic for real-world DNN hardware accelerators. Moreover, manipulation and interpolation of model parameters tend to leave footprints in memory or create conspicuous output patterns. Such persistent fault induction in the weights are likely to be directly detected by model readback and bypassed by parameter reloading. Although practical fault injection techniques such as laser beam interference [92] and Rowhammer [95] are able to perturb the output of DNN algorithm running on general purpose hardware, the attacks can be mitigated by low-precision numeral representation, as suggested in [95], which happens to be a common practice of existing deep learning accelerator for edge applications.

HTs pose a real threat for outsourced DNN IC design, fabrication or testing activity or the use of 3PIPs within DNN hardware. Successfully embedded stealthy trigger and payload into the activation layer [97] or memory controller [98] can cause misclassification. Fortunately, hardware attacks on edge deep learning applications have so far been constrained to DNN hardware on small scale (10 categories) classification [92], [94] or are based on simulated instead of physically induced faults [96], [98] on larger network such as ImageNet [99] (1000 categories) classification. One exception is the most recently reported stealthy misclassification attack on deep learning accelerator for ImageNet applications in [100]. This attack induces temporal fault into intermediate results of convolutional layer by introducing infrequent instantaneous glitches into the clock signal. The temporary perturbated data will propagate to the inference stage but they will be overwritten by the correct data after each prediction, leaving no trace for detection.

3) Model Extraction Attacks: Model extraction attack [101] occurs when attackers attempt to replicate a pre-trained model. Because of the amount of costly training data collected, a superior deep learning model trained for a specific task is a precious IP that an enterprise can monetize as a commodity through third party offerings or leverage as a technology barrier to competitors of the market. Unlike cryptosystems, model confidentiality is assumed as a trained DNN is a pricey IP. For this reason, there is strong incentive for opponents to

steal the model so as to build similar performance AI products or solutions at substantially reduced cost. Existing model extraction attacks can be broadly divided into two categories: query-based and implementation-based. Query-based model extraction attack mainly utilizes the input-output relationship of the target model to build a substitute model that has the similar functionality [101]. In the scenario of embedded devices, the internal model is exposed to the risk of being attacked by malicious users who have physical access to the device by observing the I/O dataflow [102]. These users can then train a new model with similar performance based on the I/O pairs, i.e., replicating the original model. Unlike crypto engine, where all computations can be completed fully on chip, edge implementations of DNN models, except a few tiny models, require some off-chip communications for each inference. Implementation-based model extraction attack exploits side channel leakage during model execution. Fine-grained information could be obtained by tracking cache misses, memory access pattern, power consumption and hardware performance counters [103], [104]. Algorithms such as DPA and CPA can be applied to extract the number of parameters in each layer, the value of each parameter, the total number of layers and the type of activation function. Optimization techniques on DNN hardware, such as zero weight pruning, can be utilized to reduce the complexity of reverse engineering [105]. The success of model extraction can enable further exploitation of the security weaknesses of deep learning, such as evading systems thereby forcing incorrect predictions and revealing additional information from the training data to leak sensitive and confidential information.

#### IV. COUNTERMEASURES

# A. Hardware Security Primitives

True random number generator (TRNG) and physical unclonable function (PUF) are two important hardware-intrinsic security primitives that provide built-in instead of bolted-on defense against various emerging threats and vulnerabilities arising at different phases of the IC life cycle or device operation. Compared with TRNG, PUFs have been very well surveyed by many researchers in recent years. For TRNG, we exemplify typical CMOS circuit implementations from four different entropy sources. For PUFs, we focus on the feasibility of its integration with other non-device signatures. Such a unique provenance proof is promising in detecting imposer, tampering, spoofing and fabrication attacks that aim to gain unauthorized access to system, data or premises.

1) TRNG: A random number generator is a device or software that generates sequences of unpredictable numbers. The ancient ways of using dice roll or coin toss to harvest natural randomness are too slow to meet the demands of modern computing systems. A pseudorandom number generator (PRNG) is an algorithm or a mathematical formula that can be used to produce a sequence of random numbers with a sufficiently long but finite period from a seed state. PRNGs that are suitable for the cryptographic applications are called cryptographically secure pseudorandom number generators (CSPRNGs). CSPNGs are designed from cryptographic primitives or hard mathematical problems to pass the next-bit test

such that the (k+1)-th bit of a sequence cannot be successfully predicted in polynomial time from the knowledge of the first k bits. CSPRNG should also be resilient to the "state compromise extensions" attack, which is an attack that makes use of some known internal states to predict future outputs or recover previous outputs. On the contrary, a TRNG is a hardware security primitive that yields unpredictable random numbers even if the internal design details are all known. With infinite period, it provides higher security property than CSPRNG. TRNG designs that originated from solid-state devices typically harvest their randomness from four sources, namely noise, jitter, metastability and chaos.

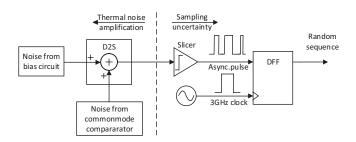

Thermal noise is a good source of randomness because it is frequency- and technology-independent [106]. The weak thermal noise needs to be boosted by a wide-bandwidth amplifier, which can consume significant silicon area and power. Matsumoto et al. [107] added a silicon nitride (SiN) layer in a standard CMOS process to amplify the thermal noise to a measurable level without the amplifier but the extra SiN mask is itself expensive. Recently, Bae et al. [108] proposed a high-speed TRNG by harvesting the thermal noise from the biasing circuit of a common-mode operating comparator and the sampling uncertainty of a Delay Flip Flop (DFF). The idea is illustrated in Fig. 1. Common-mode noise is generated by connecting both inputs of a comparator to the output of a beta-multiplier voltage reference. The thermal noises of the comparator and the biasing circuit are added up and amplified by the differential-to-single ended (D2S) amplifier. The amplified noise is fed into a slicer to generate a full swing output, which is then sampled by a 3 GHz clocked DFF. By combining thermal noise and sampling uncertainty of the asynchronous input, this TRNG has a very high throughput of 3 Gbps. Its power consumption is also very high, 5 mW excluding the power-hungry external high-speed clock generator.

Fig. 1. Design concept of noise-based TRNG [108].

Conventional jitter-based TRNGs [109] use a slower jittery frequency clock to sample a faster clock. Using clock jitters of free running ring oscillators (ROs) as entropy source, the extractor design can be simplified, but additional power-hungry clock generators are required to provide adequate jitter variations. Yang *et al.* [110] proposed a process variation tolerant TRNG by exploiting the oscillation collapse in a double edge injected RO. To achieve the robustness against process variations, 32 stages with 8 selectable inverters per stage are used to provide the tuning space. Recently, a lightweight TRNG consisting of only two 9-stage current-starved ROs (CSROs) with an identical layout, a 3-stage regular RO and

a 2-bit counter was proposed [111]. In order to maximize jitters and reduce power consumption, the inverters in the two CSROs are biased in the weak inversion region and the inverters in the regular RO are operating in the strong inversion region. Systemic biases in the beat frequency are effectively cancelled out by XORing the outputs of the two matched CSROs. The resulting random pulse width is used to clock gate the regular inverter-based RO to the 2-bit counter. This jitter-based TRNG, fabricated in a standard 65 nm, 1.2 V CMOS process, consumes only 260  $\mu$ W at a bit rate of 52 Mbps and has a small footprint of 366  $\mu m^2$ .

Metastability is a stable state of a dynamical system besides the system's state of least energy. Metastabilities in crosscoupled inverters, latches, DFFs and SRAMs [112] have been utilized to produce random bit streams at high bit rate, but complex post-processing units are usually required to eliminate the systematic bias. The key component of metasabilitybased TRNG of [112] is the metastability latch, which is designed based on a cross-coupled inverter pair with equal rise and fall time. A random bit is produced by the metastability latch in each cycle. To assure high entropy, a time-to-digital converter (TDC) is used to measure the settling time and tune the metastable latch against bias introduced by the process and temperature variations. The switching speed of the metastability latch cannot be too fast to prevent the settling time from exceeding the time resolution of the TDC. The latch size and load must also preserve the dominance of thermal noise over flicker noise. By combining three entropy sources of similar cross-coupled inverter pairs that share the same supply and clock, Intel [106] fabricated a fast TRNG in 14nm FinFET CMOS process that produces 3 full-entropy bits per clock cycle. The three bitstreams of at least 0.33 min-entropy/bit each are combined by a Barak-Impagliazzo-Wigderson (BIW) extractor [113]. Correlation suppressors and under-sampled feedback shift registers are used to de-correlate and whitening the raw data to generate 24 uncorrelated bits in every 64 clock cycles with an ultra-low energy consumption of 3 pJ/bit.

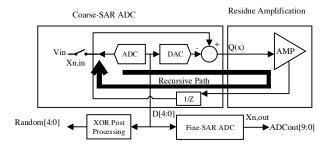

TRNGs can also be designed from chaotic system described by deterministic equations. At first sight, this may sound like God plays dice with complete law and order. Being extremely sensitive to the initial conditions, the disorder states of a chaotic system are very hard to be modeled mathematically even though they are produced by simple systems that obey precise rules. Chaos is, as described by the legendary Lorenz, "when the present determines the future, but the approximate present does not approximately determine the future." [114]. Chaos-based TRNGs [115] are typically designed by a chaotic map and a bit generation function. Unfortunately, the map characteristics are susceptible to process, voltage and temperature (PVT) variations. The optimal bit generation function for achieving the highest possible entropy rate from a map function is costly to implement, and consumes great power. An exceptionally energy-efficient implementation [116] is shown in Fig. 2. It consists of a 10-bit fine-SAR ADC, a 5-bit coarse-SAR ADC, a dynamic residue amplifier, and an XOR postprocessing block. The ADC recursively amplifies the initial state of the system with environmental noise to produce a discrete time chaotic map. Due to quantization errors of the coarse-SAR ADC, the design is highly sensitive to the initial state. The switching power of fine-SAR ADC is reduced by using the coarse-SAR ADC to detect and skip switching. The design consumes only 82 nW of power and 0.3 pJ/bit of energy. A larger portion of the power savings are due to the dynamic residue amplifier and adaptive reset comparator.

Fig. 2. Block diagram of chaos-based TRNG of [116].

As the need for publicly auditable randomness from applications like elections and lotteries increases, so is the demand for randomness beacon. A randomness beacon is a public server that produces completely unpredictable bit strings at regular intervals. During the Crypto Week last year, a new public randomness beacon called "League of Entropy" [117] was released by the American web-infrastructure and websitesecurity titan company Cloudflare. Built upon the provably secure cryptographic architecture of drand [118], this is a network of beacons run by a consortium of global organizations and individual contributors to provide publicly verifiable, decentralized random outputs. Interestingly, Cloudflare actually sources her entropy from a video of a wall of lava lamps. These unpredictable visual data of floating blogs are converted to truly random numbers. Most recently, truly random numbers were also created from growing crystals [119].

2) PUF as Provenance Proof: PUF utilizes intrinsic manufacturing process variations to generate a unique unforgeable device fingerprint. A comprehensive review of PUFs can be found in [28], where different PUF structures, including the conventional delay-based or memory-based PUFs, and the emerging non-volatile memory (NVM) based PUFs, FinFET PUF, quantum secure PUF and sensor PUFs, have been surveved. In the early stage of development, the reproducibility of PUF responses at different time and in different environmental conditions is the main practical issue that limits its industrial adoption. Majority voting, fuzzy extractor and reverse fuzzy extractor are three commonly used techniques to improve the reliability of a PUF. Majority voting votes for the most stable response by repeated application of the same challenge. It is a lightweight technique to enhance the reliability of a PUF at the expense of latency. Fuzzy extractor (FE) [28] increases the noise tolerance and uniformity of PUF response by error correction code (ECC) and hash function. As ECC decoding is too expensive for resource-constrained IoT devices, it is moved from the regeneration phase at the prover (device) side to the verifier (server) side by reverse fuzzy extractor (RFE) [120]. Instead of generating the helper data only once in the PUF enrolment phase, RFE generates helper data on site to different noisy versions of the same PUF response. While this eases the enrollment of strong PUF with a large number of CRPs, the disclosure of multiple helper data also increases the risk of side-channel information leakage. This problem can be mitigated by a well-structured PUF with balanced BER [121] or appending an Z-channel [122]. Today, PUFs have made their presence known in industry, e.g., Xilinx [123], NXP Semiconductor [124] and Qualcomm [125].

As a hardware root of trust, PUF has opened up new horizons for solving IoT security problems. The rise of IoT has created a huge influx of sensors and accelerated sensor standardization towards building a fully connected and cohesive supply chain. With sensors as the data feeder, a direct consequence is the new gloss on pushed media data and distinctively new interactions between human, events and devices. A promising new approach to assure real end point security against the imminent risk of sensor and data analytic attacks is to derive provenance proof from the unification of PUF responses and biometrics or other existing data analytic based security measures. This approach endows PUF systems with the capability to not only identifying the device, but also (i) authenticating the users who have privileged access to the device and its data, (ii) assuring the integrity of the data it generated or acquired, and (iii) responding actively to events occurred in the area of surveillance. Unlike conventional PUF designs, such interactive PUF systems are usually applicationor sensor-specific, and have dedicated authentication protocols.

(i) Typical user and device authentication methods perform user and device authentication sequentially with a substantial message exchange. To protect the sensitive credentials during transmission, encryption keys are required to be stored in the end device, which are vulnerable to NVM key retrieval attacks [25]. In [126], [127], a completely different concept of unified user-device (UD) PUF was proposed to distinguish different users and devices by extracting raw biometric information like touch screen pressure or voice with the innate silicon sensor variations. The challenge to the UD-PUF in [126] is a series of binary coordinates that forms a pattern on the touchscreen. The response is a digital word obtained by quantizing the sequence of sensed pressure values read from an Android APP when the user traces the pattern. Unfortunately, the intrinsic parametric changes contributed by device fabrication process variations are not structurally harnessed, resulting in high identification error rate for the (same user, same challenge, different device) combination. The problem is intrigue as amplifying the parametric deviations to improve device identification will reduce the sensitivity of the user biometric whereas noise reduction in biometric information processing will distort device parametric distribution. Another "UD-PUF" was proposed in [128] for matchon-device applications. A strong PUF is required to generate an obfuscated biometric template by feeding the processed biometric feature into it. As small change in the challenge will cause a dramatic bit flips in the PUF response, the quantized biometric feature-based challenge has to be 100% accurate to ensure reproducibility of template in the authentication phase. This problem is mitigated by selecting the most robust biometric feature for each individual user using noise awareinterval optimized mapping bit allocation (NA-IOMBA). As

NA-IOMBA requires accurate noise samples/models over time for different conditions, the scheme can only generate one determinant template for a (user, device) combination. Once the template is leaked, the security of using the particular device will be compromised. This dilemma is resolved by a "UDhashing" scheme in [129]. UDhashing adopts a "fuseon-device" and "match-on-server" strategy. Machine learning (ML) resilient strong PUF [130] is preferred to prevent the reuse of authentication credentials, and to achieve cancellable biometrics and system reconfigurability. To bind a device to its user, the user live biometric and device PUF response are unified by random projection into a bio-code at the enddevice. The endpoint and the server are mutually authenticated by a zero-knowledge proof of the endpoint's secrets. The server is authenticated by the endpoint through the hashed PUF responses while the endpoint is authenticated by the server through the bio-codes. A correct biometric input of a user to his registered device and a correct response to a query from that device are both required to authenticate the bio-code. Neither the hashed PUF response nor the bio-code reveals the endpoint's secrets. The bio-code can be easily revoked, reissued or refreshed by a different challenge to prevent permanent compromise of the users' biometrics.

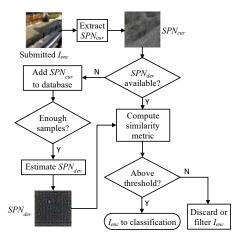

(ii) Similarly, PUF-assisted data-device authentication systems fill the gap of existing data and device independent authentication schemes in digital forensics. Digital images and videos have been increasingly exposed as important information or art carriers. Their easy-to-access and lowcost attributes also escalate image fraudulence. Two related problems are to be solved: detection of image tampering and authentication of the imaging device. Image tampering is typically detected by image watermarking [131], digital image forensics [132] and perceptual image hashing [133]. Of which perceptual image hashing is most effective in tamper detection. It is very sensitive to content-specific modifications and yet robust against normal content-preserving processing. Since such methods depend on a shared secret key for authentication, the security of the whole system will collapse if the secret key is compromised, lost or stolen. Source camera identification is mainly accomplished with ML based methods. By analyzing the structure and processing stages of the digital camera, appropriate features representing the unique device characteristics can be algorithmically extracted with the knowledge of lens aberration, sensor imperfection, color filter array interpolation and salient image features [134]. Existing works focusing on imaging device brand identification achieve very high accuracy but fail to distinguish individual devices from the same model and the same brand. Identifying individual camera devices have been increasingly studied in recent years based on photo response non-uniformity (PRNU) pattern [135], [136]. To achieve high reliability and accuracy, strict conditions in the acquisition process, number and content of training images as well as geometrical synchronization of testing images have to be met. More importantly, the same approach can also be used by a malicious user to extract the device features from publicly available images. To provide dual authentication without the aforementioned shortcomings, PUF-based data device authentication schemes

have been proposed. PUF based perceptual image hash was first conceptualized in [137] for simultaneous tamper detection and source camera identification. This work shares the same PUF reliability problem as [128] since the data features were directly applied as the challenge to the underlying PUF. Alternatively, a data-device PUF (DD PUF) with relaxed reliability requirement was proposed in [138]. The method [138] imprints an indelible birthmark of the camera into its captured images for forgery detection. The robust data-device hash is produced by projecting the rotation-/scaling-invariant image features into the Bernoulli random matrix generated by the PUF responses. This hash is "keyless" and time-, data- and device-dependent. Attestation is non-repudiable as the perceptual image hash can only be generated by the timestamp of the image captured through the camera's tamper-resistant image sensor PUF. To achieve secure and accurate camera identification with reduced hardware overhead, the CMOS image sensor PUF [139] derived from fixed pattern noise of individual active pixel elements is utilized in both schemes [128], [138].

(iii) Existing PUFs, including the CMOS image sensor PUF [139], are typically triggered by server-provided challenges. Since the challenges are independent from the sensing targets, it is difficult to control the attestation frequency, resulting in either redundant or inadequate security tagging. Traditional frame-based imager generates too much redundant background data, which limits its processing bandwidth in high-speed and privacy-preserved video surveillance applications. Dynamic vision sensor (DVS), also known as neuromorphic vision sensor, provides a solution to design PUF system that is capable of responding actively to incidents occurred in the surveillance scene. DVS responds only to temporal intensity change and records only sparse asynchronous addressevents with precise timing information. It has low latency, high dynamic range and significantly reduced data size. These features are exploited to make an event-driven PUF in [140]. It adds only three transistors per DVS pixel to harness the entropy from the fabrication process variability. The PUF response can only be triggered by and is uniquely dependent on the asynchronous addressed event detected in the scene without being interfered by the simultaneous firing of other address events. The package of address events acquired by the DVS camera is tagged by the event-driven PUF response using a keyed Hash-based Message Authentication Code (HMAC). This is believed to be the first event-driven PUF system to fill the forensic gap of simultaneously authenticating the event data integrity and source camera identity.

# B. System and Architectural Protection Techniques

Resource sharing is inevitable as it leads to more efficient computation. Software processes share memories, datapaths, accelerators, monitors, sensors and I/O. Hardware IP cores require shared access to on-chip interconnect and memories. Yet, it is a challenge for security since any entity must consider information leakage through shared resource especially when computing on sensitive data. The cache side channel is a key example of this that has been exploited countless times for nefarious purposes. Resource isolation is a key security mechanism that is often difficult to implement in practice.

- 1) Trusted Execution Environment: One common approach for software isolation is a trusted execution environment (TEE). TEE uses hardware mechanisms to ensure that isolation properties are properly enforced. These properties, in general, enforce rules that provide a fixed set of resources for a sensitive computation, and assurances that those computations are hidden from other system users. There are a number of different TEEs. Intel's SGX [141] uses enclaves a protected environment that contains the code and data of a security-sensitive computation. SGX performs isolation by setting aside a memory for trusted computation and isolating the memory from any other access including kernel, hypervisor and DMA accesses. ARM Trust-Zone [142] has two worlds. Sensitive computations are put into the secure world and are isolated from code running in the normal world.

- 2) Cache Side Channel Mitigations: Cache side channel mitigations attempt to minimize or eliminate information leakage by isolating secure and non-secure accesses to the cache. Cache partitioning is one class of approaches that attempts to separate the cache to avoid conflicts. Partitioning can be performed in various ways, including static locking (PLCache) [143], dynamic locking [144], page coloring [145], and selective cache flushing [146]. Randomization is another class of techniques where of cache access patterns are permuted to minimize any information leakage on conflicts, e.g., RPCache [143]. Other mitigations include DAWG [147], InvisiSpec [148], non-monopolizable caches [149], Intel Cache Allocation Technology [150], and CATalyst [151].

It is difficult to develop and implement a cache mitigation scheme. For example, Ardeshiricham *et al.* [152] showed that the well-known PLCache [143] mitigation was flawed, and developed a fix to the vulnerability that was formally verified to be secure. This points to the need for any mitigation to come with proof that they are correct. Property driven hardware security [20] advocates for such an approach where the threat model is formally specified as properties, e.g., SystemVerilog Assertion (SVA) assertions, information flow properties, etc., and hardware security verification tools provide assurance that the designs adhere to the specified properties.

3) Memory Protection: Many of the system and architectural threats revolve around performing proper access control on memory locations. This includes strict isolation of memory regions (e.g., non-secure processes should never read/write secure memory) and dynamic policies (e.g., a cryptographic key is written during secure boot process and is never accessed by anyone after that). Standard memory protections rely on a memory management unit (MMU). Common protections include access control through segmentation to provide isolation, data encryption to provide confidentiality [153], and hashing to provide integrity [154]. Protecting the memory access information, along with the confidentiality and integrity of the data, is also crucial. Oblivious RAM [155] is an example approach for access pattern protection. 3D integration is a powerful technique for hardware security and can be used for memory protection [156], e.g., embedded DRAM can mitigate threats related to off-chip data accesses. Anti-tamper techniques are also widely adopted by chip makers such as Altera [157], ON Semiconductor [158] and Cypress [159] to secure key storage. The most recent nonvolatile static RAM technology based anti-tamper memory [159] can provide a single or combined features of password protection, data destruction, functional destruction and physical destruction upon tampering.

4) Control Flow Integrity (CFI): Control flow integrity (CFI) defends against code reuse attacks by monitoring the program's flow of execution and attempts to ensure that it performs the correct sequence of operations. CFI is a general class of mitigation strategies that monitor and restrict the control flow decisions that a program makes. While there are many software CFI techniques, including some done in practice [160], there are fewer hardware based CFI techniques as they generally require substantial changes to the underlying microarchitecture. Hardware CFI defenses depend on a trusted hardware monitor integrated into the instruction pipeline or with access to the processor's debugging resources to analyze control flow information. de Clercq and Verbauwhede [161] classify CFI mitigation strategies into the followings: shadow call stack, labels, tables, finite state machine, branch regulation, instruction set randomization, signature modeling, and code pointer integrity. These mitigation strategies aim to monitor execution using a limited number of resources. Their differences are reflected in the resources that they monitor, how they track execution flows, and the type and amount of stateful information that must be stored.

#### C. Side Channel Protection Techniques

1) Timing-channel Countermeasures: Existing countermeasures against SCA explore both software and hardware-level approaches. A countermeasure could be detection of the attack at runtime or analysis of susceptibility during the design stage. It could also be a design approach (both software and hardware) for mitigating the covert or side-channel.

Most timing channels in cryptographic implementations occur due to the difference in execution time for different key and data inputs. As key and data inputs vary, the memory access pattern, branches, and various other operations become different across multiple executions that lead to leakage of information. Researchers have proposed constant-time techniques to eliminate such leakage. However, they are difficult to achieve through hardware-level re-implementation and may cause significant impact on performance [162]. Bitslicing technique has been explored to implement constant-time AES core with improved performance [163].

Researchers have developed compiler-based countermeasures to thwart timing channels. These techniques focus on introducing noise or randomization in the software implementation to eliminate timing leakage. Coppens *et al.* [164] proposed compiler-based automatic elimination of key-dependent control flow by removing conditional move instructions.

2) Power Side-channel Countermeasures: Power SCA countermeasures can be categorized as algorithmic, physical, or system-level. Algorithmic countermeasures insert additional operations that mask [165] or split [166] the sensitive computation. They have the advantage of being provably secure. Physical countermeasures rely on measurements for validating the security of the device. The problem of measuring the side-channel leakage of a device has been addressed in [39], [41],