## Atomic Layer Deposition of TiN/Ru Gate in InP MOSFETs

Hsin-Ying Tseng,<sup>1,a)</sup> Yihao Fang,<sup>1</sup> William James Mitchell,<sup>2</sup> Aidan Arthur Taylor,<sup>3</sup> and Mark J.W. Rodwell<sup>1</sup>

<sup>1</sup>Department of Electrical and Computer Engineering, University of California Santa Barbara, Santa Barbara, California 93106, USA

<sup>2</sup>UCSB Nanofabrication Facility, University of California Santa Barbara, Santa Barbara, California 93106, USA

<sup>3</sup>Department of Materials Science, University of California Santa Barbara, Santa Barbara, California 93106, USA

InP-channel planar and vertical MOSFETs utilizing atomic layer deposition of a TiN/Ru gate are fabricated. The performance of the TiN/Ru gate is compared to a Ru-only gate based on C-V characteristics of MOS (Metal Oxide Semiconductor) Capacitors (MOSCAPs), and peak transconductance  $(g_m)$  and subthreshold swing (SS) in planar MOSFETs. Compared to devices with conventional Ni/Au gate metal, these having a  $70\text{mV/dec}\ SS$ , the long gate length TiN/Ru gate devices exhibit an average  $68\ \text{mV/dec}\ SS$ , a record low value of InP, suggesting a high quality, low-damage high-k/InP interface. A record high peak  $g_m$  of  $0.75\ \text{mS/}\mu\text{m}$  at  $V_{DS}=0.6\ \text{V}$  on an InP channel is achieved in a planar gate length  $(L_g)=80\ \text{nm}$  device. A vertical MOSFET shows a reasonably conformal Ru coverage of the vertical fin, and a high  $0.42\ \text{mS/}\mu\text{m}$  peak  $g_m$  for a  $L_g=50\ \text{nm}$  device. The results of planar and vertical MOSFETs show that TiN/Ru gate metallization via atomic layer deposition is promising for non-planar III-V MOS devices.

III-V MOS structures are of potential interest in III-V MOSHEMTs,  $^{2.3}$  targeting applications in mm-wave receivers, and in the gate structure of tunnel FETs for ultra-low voltage VLSI logic.  $^{4-7}$  MOSFETs with subthreshold swings approaching 60 mV/decade have been demonstrated with ZrO<sub>2</sub> and HfO<sub>2</sub> gate dielectrics on InGaAs, InAs, and InP channels, indicating dielectric/semiconductor interface trap densities ( $D_{tt}$ ) less than  $3\times10^{12}$  cm<sup>-2</sup>eV<sup>-1</sup>.  $^{1.8-10}$  Previous results have generally used gate metals deposited by sputtering or thermal evaporation. For nonplanar finFETs and next generation gate-all-around (GAA) nanowire transistors, a more uniform and conformal high-k metal gate (HKMG) are necessary to ensure a low gate resistance and a consistent threshold voltage distribution.  $^{4,11,12}$  Thus, atomic layer deposited (ALD) HKMG, with its superior uniformity in thickness and conformity, had been demonstrated in InGaAs FinFETs.  $^{13}$  There have been no reports of ALD HKMG with low  $D_{tt}$  on InP channels. Here we present an ALD low  $D_{tt}$  Ru/TiN/ZrO<sub>2</sub> HKMG on InP with a lowest SS of 68mV/dec in long gate length planar devices, as well as comparable peak  $g_m$  on vertical MOSFETs.

Ruthenium has a desirable metal workfunction for III-V N-MOSFETs, as well as low resistivity, and good thermal stability. One key to the successful ALD growth of Ru is controlled nucleation on dissimilar materials. 14 Nucleation and growth initiation of ALD Ru appear to vary with substrates used. Rough and non-uniform growth on SiO<sub>2</sub>, low-k dielectrics, and TaN surfaces has been reported. 15-17 Films with poor nucleation have also exhibited poor electrical properties. 18 Yim et al. reported ALD Ru with an improved nucleation on a thin SiN<sub>x</sub> or heavily NH<sub>3</sub>-plasma activated (50 minute exposure) SiO<sub>2</sub> surface according to TEM analysis. <sup>16</sup> M. Zhang et al., on the other hand, demonstrated improved ALD Ru nucleation with an Al<sub>2</sub>O<sub>3</sub> surface layer. <sup>19</sup> Overall, it was suggested that one can improve the nucleation of Ru growth by surface energy engineering, which helps the adsorption of Ru precursors.<sup>20</sup> The addition of an Al<sub>2</sub>O<sub>3</sub> interlayer and plasma treatment prior to Ru deposition in MOS structures, however, may degrade device electrical performance due to increased effective-oxide-thickness (EOT), increased interface trap density, and a shift in the MOS threshold voltage. Therefore, it is important to consider tradeoffs in ALD Ru HKMG design between Ru film quality and overall device performance. In this work, a thin ALD TiN layer (~2 nm) is deposited as a nucleation/stiction layer in Ru gate devices.<sup>21</sup> TiN/Ru gates and Ru-only gates on InP channel are compared. Capacitance-voltage (C-V) characteristics of MOSCAP structures, and SS and peak  $g_m$  of planar MOSFETs, are employed to evaluate the performance of the two metal gate stacks. Ru growth is further optimized for a better conformity. At last, vertical MOSFETs with conformal TiN/Ru gates are demonstrated. Transfer and output characteristics of vertical MOSFETs are compared to their planar counterpart.

Planar MOSFETs were fabricated on semi-insulating (S.I.) (100) Fe-doped InP substrates. The fabrication started with epitaxial growth of the channel by metal organic chemical vapor deposition (MOCVD). The MOCVD channel growth was performed at 600°C, and consists of a bottom 9 nm, 8×10<sup>17</sup> cm<sup>-3</sup> Zn-doped *P*-InP layer to compensate for the donor impurities at the growth interface, and a top 9 nm unintentionally-doped (U.I.D.) InP layer. After channel growth, a dummy gate was defined by electron beam lithography (EBL) using hydrogen silsesquioxane (HSQ) resist for subsequent self-aligned raised source/drain MOCVD regrowth. A 1-minute dip in HCl: H<sub>2</sub>O 1:10 was done prior to the regrowth. For the source/drain, a 9 nm U.I.D. InP spacer, 10nm, 2×10<sup>19</sup> cm<sup>-3</sup> Si-doped *N*<sup>+</sup>-InP, and 110 nm, 4×10<sup>19</sup> cm<sup>-3</sup> Si-doped *N*<sup>+</sup>-In<sub>0.53</sub>Ga<sub>0.47</sub>As layers were grown at 600°C. Devices were then isolated by selective wet etch using HCl- and H<sub>3</sub>PO<sub>4</sub>:H<sub>2</sub>O<sub>2</sub>-based solutions. After a two minutes buffered HF (BHF) dip followed by one cycle of a HCl-based digital etch to remove the dummy gate and surface oxides, high-k and metal gate layers were deposited in an Oxford FlexAL ALD system. The high-k deposition process includes initial surface passivation using 9 cycles of alternating N<sub>2</sub>-plasma and trimethylaluminum (TMAI) dosing (~1 nm AlO<sub>8</sub>N<sub>9</sub>)<sup>9,22</sup> followed by 40 cycles of H<sub>2</sub>O and tetrakis(ethylmethylamido)zirconium (TEMAZ) dosing (~2.5 nm ZrO<sub>2</sub>) at 300°C. <sup>23</sup> To further passivate surface dangling bonds, a 30 minute ALD in-situ H<sub>2</sub> anneal was performed at 350°C. Metal gate deposition at 300°C

utilizes a 35 cycles of TiN nucleation layer (~2 nm) first deposited using Tetrakis(dimethylamido)titanium (TDMAT) together with a N<sub>2</sub>- and H<sub>2</sub>-plasma (400W inductively coupled plasma (ICP) power). 500 cycles of ALD Ru (~30 nm) was then deposited using (ethylbenzene)(1,3-cyclohexadiene)ruthenium (EBCHDRu) and O<sub>2</sub> cycles at 300 °C. EBCHDRu is a zero-valent organometallic precursor (Hansol Chemical, Korea). In-situ post-metal annealing in H<sub>2</sub> ambient at 350 °C was employed for 30 minutes to recover plasma damage at the high-k/InP interface. The Ru metal gate patterns were dry etched using an O<sub>2</sub>-based ICP etch (catalyzed with a small of amount of Cl<sub>2</sub>).<sup>24</sup> The TiN and the high-k dielectric layers were etched via a 1-minute BHF dip. Source and drain metal contacts (Ti/Pd/Au) were deposited by lift-off. Devices were finally passivated using Al<sub>2</sub>O<sub>3</sub> (~3 nm) deposited by ALD.

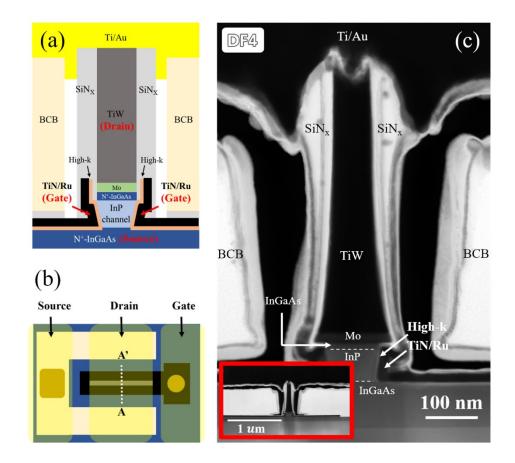

The vertical MOSFETs were fabricated in a top-down process. The epitaxial stack consisted of, from bottom to top, a Fedoped S.I. (100) InP substrate, a 90 nm thick Si-doped  $N^+$ -In<sub>0.53</sub>Ga<sub>0.47</sub>As (4×10<sup>19</sup> cm<sup>-3</sup>) source layer, 5 nm thick Si-doped  $N^+$ -InP  $(2\times10^{19} \text{ cm}^{-3})$  layer, a 50 nm thick Zn-doped P-InP  $(1\times10^{18} \text{ cm}^{-3})$  channel layer, a 5 nm thick Si-doped  $N^+$ -InP  $(2\times10^{19} \text{ cm}^{-3})$ <sup>3</sup>) drain layer, and a 10 nm thick Si-doped  $N^+$ -In<sub>0.53</sub>Ga<sub>0.47</sub>As (4×10<sup>19</sup> cm<sup>-3</sup>) contact layer. All layers were grown by MOCVD at 600°C. A refractory Mo/TiW (20/500 nm) drain metal contact was deposited by electron beam deposition and DC sputtering, respectively, and then patterned using EBL followed by ICP etching.<sup>25</sup> A 20 nm SiN<sub>x</sub> sidewall was formed by plasma-enhanced chemical vapor deposition (PECVD) followed by an anisotropic CF<sub>4</sub>-based plasma etch. The 10 nm InGaAs contact layer was wet etched in H<sub>3</sub>PO<sub>4</sub>: H<sub>2</sub>O<sub>2</sub>: H<sub>2</sub>O 1:1:25. A second 20 nm Si<sub>3</sub>N<sub>4</sub> sidewall was then formed. The InP drain and channel were wet etched in HCl:H<sub>3</sub>PO<sub>4</sub> 1:4. The vertical surface sidewalls of the p-type InP layer acted as the transistor channel. Prior to high-k deposition, 5 cycles of HCl-based digital etching were performed for native oxide removal on the channel surface. The high-k deposition, H<sub>2</sub> annealing and TiN deposition processes were identical to the fabrication of the planar MOSFET's detailed above. The ALD Ru deposition, on the other hand, had to be carried out at a lower temperature of 250°C to ensure conformal growth on the sidewalls of the vertical MOSFET structure (avoiding a small precursor decomposition on the structure at 300°C). 26,27 To avoid formation of surface RuO2 during this lower temperature Ru process, a layer which inhibits the growth of a metallic Ru layer, H<sub>2</sub> is added as a reducing co-reactant in the ALD growth cycle.<sup>28</sup> The same post-metal annealing and TiN/Ru patterning steps for planar MOSFETs were employed. Ti/Pd/Au source contact metal was evaporated and lifted off. Ti/Au metal posts were deposited on source and gate contacts for back-end wiring. A 30 nm PECVD SiN<sub>x</sub> passivation layer was deposited prior to planarization with spin-on dielectric benzocyclobutene (BCB). The BCB dielectric was baked at 250°C for 1 hour, and ashed back with a ICP CF<sub>4</sub>/O<sub>2</sub> plasma. The SiN<sub>x</sub> passivation layer was removed in a BHF dip to expose the TiW drain contact. Excess Ru/TiN/high-k stack that surrounded the TiW/Mo drain contact was wet etched using ruthenium etchant (Transcene RU-44) and BHF. A thick 60 nm SiN<sub>x</sub> sidewall spacer was formed by PECVD followed by CF<sub>4</sub>-based plasma etch to prevent drain-to-gate short. Finally, Ti/Au (15/10000 nm) metal pads were lifted off to finish the back-end wiring.

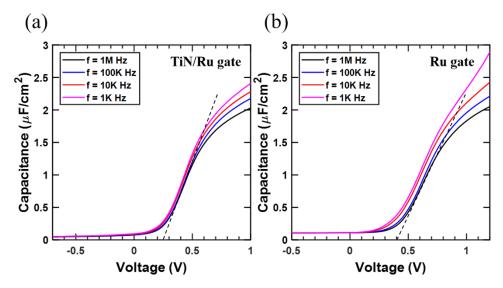

Non-uniform substrate color after Ru deposition on  $ZrO_2$  was sometimes observed, suggesting a less than ideal Ru nucleation on  $ZrO_2$ . By depositing a thin TiN layer (via ALD) prior to Ru growth, uniform nucleation on any arbitrary substrate can be realized. Fig. 1 shows the C-V characteristics of InP MOSCAPs with (a) TiN/Ru and (b) Ru gates measured from 1kHz to 1MHz. The threshold voltage of TiN/Ru gate MOSCAP is 0.25 V, which is lower than the 0.4 V measured for the Ru-only gate. The large apparent increase in capacitance in accumulation at low frequencies f is a measurement artifact due to gate leakage, as the conductivity dI/dV becomes comparable to  $2\pi fC$ , where C is the capacitance. The leakage current of the MOSCAPs is  $\sim 30 \text{ mA/cm}^2$  at  $V_g = 1 \text{ V}$  and is similar for both Ru and TiN/Ru gates. A larger frequency dispersion for Ru gate MOSCAP in depletion can be seen. In comparison, the TiN/Ru gate MOSCAP shows smaller frequency dispersion, suggesting a metal-semiconductor interface with low defect density. Furthermore, the C-V characteristic of the TiN/Ru gate MOSCAP is comparable with that using a thermally evaporated Ni/Au gate, which confirms a high quality high-k/InP interface and a low-damage gate metallization process. This suggests that the adding a thin TiN layer not only improves the nucleation of Ru, but also resolves the frequency dispersion in the case of Ru-only gates.

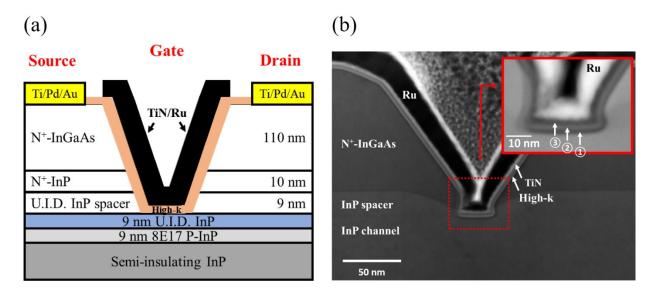

Fig. 2 shows the schematic planar MOSFET structure used in this study (a) and the TEM images of a  $L_g = 30$  nm MOSFET (b). The recess structure and U.I.D InP spacer are used to suppress band-to-band tunneling (BTBT) arising at the high-field region near the drain end of channel.<sup>29</sup> The regrowth facet with HSQ mask shows a ~30° incline at the channel after InP growth and a ~54° incline after InGaAs growth. The corresponding InP spacer thickness at the channel is approximately 5 nm. The inner highlight in Fig. 2(b) is high-angle annular dark-field imaging (HAADF) STEM image. The interfacial layers contain ~1/2.5/2 nm AlO<sub>x</sub>N<sub>y</sub>/ZrO<sub>2</sub>/TiN, as indicated by layer 1, 2 and 3, respectively. In addition, the thickness of Ru film in the channel is ~10 nm, which is much thinner than thickness in-field (~25 nm). This variability in thickness does not affect the DC performances of the planar MOSFETs, but could potentially increase the gate resistance or even result in gate open-circuits in more complex vertical transistor structures that require the gate metal to contacting the sidewall channel. Therefore, a more conformal Ru deposition is needed for vertical MOSFETs, and a process to improve Ru conformity will be discussed later.

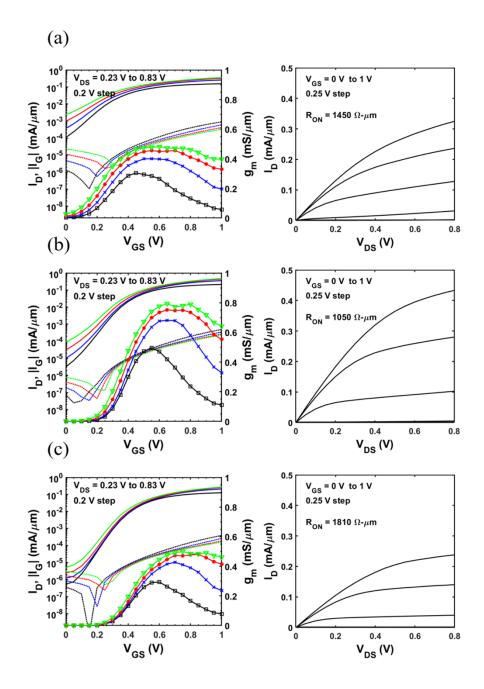

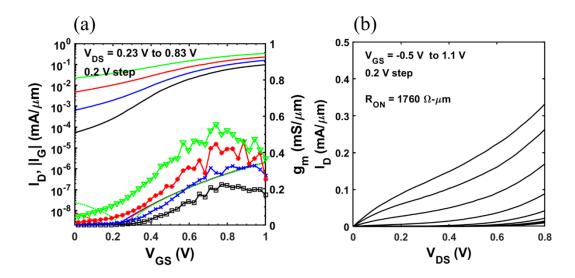

The gate length of fabricated planar MOSFETs ranges from 30 nm to 2  $\mu$ m. The transfer and output characteristics of TiN/Ru gate planar MOSFETs with  $L_g = 30$ , 80, 200 nm are shown in Fig. 3. The regrown N<sup>+</sup> S/D layer sheet resistance is ~14  $\Omega$ , while the S/D contact resistivity is 7  $\Omega$ - $\mu$ m<sup>2</sup>, as determined by transmission line method (TLM). At  $L_g > 200$  nm, a more than 5 orders of magnitude on/off ratio is achieved. The peak  $g_m$  of ~0.75 mS/ $\mu$ m is for a  $L_g = 80$  nm MOSFET at  $V_{DS} = 0.6$

V. This is the highest peak  $g_m$  reported for InP channel MOSFETs. Due to a comparably thick channel of ~18 nm, MOSFETs with  $L_g < 80$  nm suffer short-channel effects. At  $L_g = 30$  nm, the on/off ratio drops to of order 1000:1, and the peak  $g_m$  decreases. In addition, all the planar MOSFETs here reported have significant gate leakage ( $|I_G|$ ) of ~10<sup>-4</sup> mA per  $\mu$ m of gate width, as can been seen in the transfer curves. The high  $|I_G|$  arises from parasitic TiN/Ru present on the sidewalls of the N<sup>+</sup> S/D mesa. Given the large perimeter of the transistor mesa, the estimated parasitic area so covered is ~100:1 greater than the device active gate region. The gate leakage per total MOS junction area, gate and sidewall, in the planar MOSFETs is similar to that observed in the MOSCAPs.

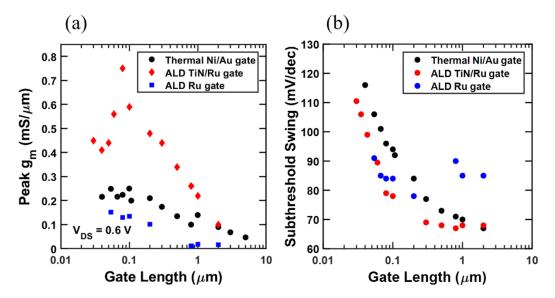

Fig. 4 summarizes (a) peak  $g_m$  vs  $L_g$  at  $V_{DS} = 0.6$  V and (b) S.S. vs  $L_g$  with ALD Ru gates, TiN/Ru gates (this work) and thermal evaporated Ni/Au gate MOSFETs.<sup>1</sup> Note that the channel thickness in this work is ~18 nm, which is ~4 nm thicker than for the Ni/Au gate MOSFETs plotted in Fig. 4. Transistors with ALD TiN/Ru gates had the highest peak  $g_m$  of ~0.75 mS/ $\mu$ m for a  $L_g = 80$  nm transistor. In comparison, Ru-only gates show lower peak  $g_m$ , which is consistent with the larger observed frequency dispersion in C-V characteristics as shown before. In addition, the Ru-only gate MOSFETs showed wide variations in characteristics between devices and low yield due to poor nucleation of Ru on the high-k gate dielectric. Correlating with the observed C-V dispersion of MOSCAPs using Ru-only gates, the SS of MOSFETs using Ru-only gates is >80 mV/dec. even at long gate lengths.

A record low SS, for an InP channel, of 68 mV/dec at  $V_{DS} = 0.1$  V for TiN/Ru gate MOSFETs is measured over 10 different > 800 nm- $L_g$  devices. This value is lower than the previously reported 70 mV/dec on thermal Ni/Au MOSFETs. From this, we calculate an  $D_{it}$  of ~1×10<sup>12</sup> cm<sup>-2</sup>eV<sup>-1</sup>, consistent with MOSCAP test structure results. Compared to the thermal Ni/Au gate, the ALD TiN/Ru gate exhibits a lower MOSCAP frequency dispersion under depletion, indicative of lower  $D_{it}$  near to band edge. This is consistent with the superior  $g_m$  and SS observed with MOSFETs using the ALD TiN/Ru gate.

As pointed out earlier, although ALD growth of Ru at 300°C yields a high conductivity metallic film, it is compromised by inadequate conformality on sidewalls due to a small amount of thermal decomposition of the precursor. <sup>26,27</sup> For improved step/sidewall coverage, an essential requirement for non-planar structures, deposition at 250°C is employed on vertical MOSFETs instead. Fig. 5 (a) and (b) show the cross-sectional and top-view of a vertical MOSFET structure. The TEM image, as shown in (c), is the cross-sectional cut along A and A' as indicated in Fig. 5 (b). The image shows the InP channel is covered by a uniform TiN/Ru film. The 250°C Ru film shows conformally underfilling of notches near to InP channel and almost constant thickness on the sidewalls and in the field, on top of N<sup>+</sup> InGaAs source. The TEM image shows an air gap between

the BCB planarization material and the Ti/Au pad metal; this may be due to BCB contraction during the relatively high temperature Ti/Au deposition.<sup>30</sup>

The  $I_D$ - $V_D$  and  $I_D$ - $V_G$  characteristics of vertical MOSFETs with TiN/Ru gate are shown in Fig 6 (a) and (b). As can be seen, strong short-channel characteristics are observed. The low aspect ratio between gate length and fin width (50:90 nm) results in poor gate electrostatics. Despite the higher bulk potential barrier in P-InP channel with doping concentration of  $1 \times 10^{18}$  cm<sup>-3</sup>, high leakage current density in the thick InP is present. To overcome this issue, a higher P channel doping or a higher aspect ratio between  $L_g$  and body thickness ( $t_{body}$ ) is needed. Nevertheless, peak  $g_m$  at  $V_{DS} = 0.6$  V of the vertical MOSFETs measures 0.42 mS/ $\mu$ m, comparable with the  $L_g = 50$  nm TiN/Ru gate planar MOSFET. This confirms ALD TiN/Ru/high-k gate's low surface trap density on non-planar InP device structures.

In summary, planar and vertical InP channel MOSFETs using ALD TiN/Ru gate are fabricated. The TiN/Ru gate exhibits better performance than Ru-only gates in MOSCAP C-V characteristics, and in the SS and  $g_m$  in planar MOSFETs. TiN/Ru gate also shows less frequency dispersion along with a record low average SS of 68 mV/dec in long gate length devices, indicating a high quality ZrO<sub>2</sub>/InP interface and a low-damage gate metallization process. By utilizing TiN/Ru gates in scaled planar MOSFETs, a record high ~0.75 mS/ $\mu$ m peak  $g_m$  for InP is observed at  $L_g = 80$  nm and  $V_{DS} = 0.6$  V. Vertical MOSFET utilizing TiN/Ru gates are also demonstrated. The vertical transistor shows a similar ~0.42 mS/ $\mu$ m peak  $g_m$  at  $V_{DS} = 0.6$  V at the same 80nm gate length as the planar MOSFET, which confirms the applicability of this gate metallization process in non-planar structures.

This research is funded by the National Science Foundation (NSF) (Grant No. 1640030) and by the Semiconductor Research Corporation (Grant No. 2016-EP-2694-A), and made use of shared facilities of the UCSB MRSEC (NSF DMR 1720256) and the UCSB Nanofabrication facility, an open access laboratory.

The data that support the findings of this study are available from the corresponding author upon reasonable request.

FIG. 1. The C-V characteristic of InP channel MOSCAPs with (a) TiN/Ru gate and (b) Ru gate. The large increase in capacitance in accumulation region at low frequencies is a measurement artifact due to gate leakage, arising when  $G/\omega$  becomes comparable to the capacitance. TiN/Ru gate shows much less frequency dispersion in depletion region, indicating a high quality high-k/InP interface and low damage gate metallization.

FIG. 2. (a) The cross-sectional planar MOSFET structure and (b) the STEM image of a  $L_g$  = 30 nm MOSFET with TiN/Ru gate. The inner plot in (b) is the HAADF-STEM image highlighting the structure at InP channel. Layer 1, 2, and 3 represent ~1 nm AlO<sub>x</sub>N<sub>y</sub>, ~2.5 nm ZrO<sub>2</sub> and ~2 nm TiN, respectively.

FIG. 3. Transfer (left) and output (right) characteristics of TiN/Ru gates planar MOSFETs with  $L_g = 30$  nm (a), 80 nm (b), 200 nm (c). In transfer characteristics, solid lines, dotted lines, and symbolic lines represent  $I_D$ ,  $|I_G|$ , and  $g_m$ , respectively.

FIG. 4. The comparison of peak  $g_m$  vs  $L_g$  (a) and the minimum SS vs  $L_g$  (b) for InP planar MOSFETs with thermal evaporated Ni/Au gates, <sup>1</sup> ALD TiN/Ru gates, and ALD Ru gates. The average minimum SS for 10 MOSFETs ( $L_g > 800$  nm) with TiN/Ru gates is 68 mv/dec, which is the record low SS for InP channel MOSFETs.

FIG. 5. The schematic (a) cross-sectional and (b) top view vertical MOSFET structure, and (c) the cross-sectional STEM image of the vertical MOSFET with TiN/Ru gate cutting along A and A', as indicated in (b). The P-InP channel length is 50 nm in this study, while the TiW/Mo drain metal stack is as thick as ~520 nm to facilitate contacting the drain. The inner plot in (c) is the image in a large field.

FIG. 6. The transfer (a) and output (b) characteristics for vertical MOSFETs with TiN/Ru gate. In transfer characteristic, solid lines, dotted lines, and symbolic lines represent  $I_D$ ,  $|I_G|$ , and  $g_m$ , respectively. Low ratio between gate length and fin width (50 nm: 90 nm) results in a poor gate control and shows a strong short channel behavior. The peak  $g_m$  at  $V_{DS}=0.6~{\rm V}$  is ~0.42 mS/ $\mu$ m, which is closed to planar MOSFET with  $L_g=50$  nm as shown in Fig. 4(a).

## **REFERENCES**

- <sup>1</sup> H.Y. Tseng, Y. Fang, S. Zhong, and M.J.W. Rodwell, in *Device Res. Conf.* (2019), pp. 183–184.

- <sup>2</sup> A. Tessmann, A. Leuther, F. Heinz, F. Bernhardt, L. John, H. Massler, L. Czornomaz, and T. Merkle, IEEE J. Solid-State Circuits **54**, 2411 (2019).

- <sup>3</sup> B. Markman, S.T.S. Brunelli, A. Goswami, M. Guidry, and M.J.W. Rodwell, J. Electron Devices Soc. 8, 930 (2020).

- <sup>4</sup> E. Memisevic, J. Svensson, M. Hellenbrand, E. Lind, and L.E. Wernersson, in *Tech. Dig. Int. Electron Devices Meet. IEDM* (2017), pp. 19.1.1–19.1.4.

- <sup>5</sup> C. Convertino, K.E. Moselund, C.B. Zota, Y. Baumgartner, P. Staudinger, M. Sousa, S. Mauthe, D. Caimi, L. Czornomaz, and A.M. Ionescu, in *Tech. Dig. Int. Electron Devices Meet. IEDM* (2019), pp. 2019–2022.

- <sup>6</sup> A. Alian, S. El Kazzi, A. Verhulst, A. Milenin, N. Pinna, T. Ivanov, D. Lin, D. Mocuta, and N. Collaert, in *Dig. Tech. Pap. Symp. VLSI Technol.* (2018), pp. 133–134.

- <sup>7</sup> C.Y. Chen, H.Y. Tseng, H. Ilatikhameneh, T.A. Ameen, G. Klimeck, M.J. Rodwell, and M. Povolotskyi, IEEE Trans. Electron Devices **68**, 3104 (2021).

- <sup>8</sup> S. Lee, V. Chobpattana, C.-Y. Huang, B.J. Thibeault, W. Mitchell, S. Stemmer, A.C. Gossard, and M.J.W. Rodwell, in *Dig. Tech. Pap. Symp. VLSI Technol.* (2014), pp. 1–2.

- <sup>9</sup> V. Chobpattana, E.M. Mates, J.Y. Zhang, and S. Stemmer, Appl. Phys. Lett. **104**, 182912 (2014).

- <sup>10</sup> O.-P. Kilpi, J. Wu, J. Svensson, E. Lind, and L.-E. Wernersson, in *Dig. Tech. Pap. Symp. VLSI Technol.* (2017), pp. 36–37.

- <sup>11</sup> D. Hisamoto, W. Lee, J. Kedzierski, H. Takeuchi, K. Asano, C. Kuo, E. Anderson, T. King, J. Bokor, and C. Hu, IEEE Trans. Electron Devices **47**, 2320 (2000).

- <sup>12</sup> K.H. Yeo, S.D. Suk, M. Li, Y.Y. Yeoh, K.H. Cho, K.H. Hong, S.K. Yun, M.S. Lee, N. Cho, K. Lee, D. Hwang, B. Park, D.W. Kim, D. Park, and B. Il Ryu, in *Tech. Dig. Int. Electron Devices Meet. IEDM* (2006).

- <sup>13</sup> J.J. Gu, X.W. Wang, H. Wu, J. Shao, A.T. Neal, M.J. Manfra, R.G. Gordon, and P.D. Ye, in *Tech. Dig. Int. Electron Devices Meet. IEDM* (2012), pp. 633–636.

- <sup>14</sup> S.N. Chopra, M.F.J. Vos, M.A. Verheijen, J.G. Ekerdt, W.M.M. Kessels, and A.J.M. Mackus, J. Vac. Sci. Technol. A **38**, 062402 (2020).

- <sup>15</sup> M. Zhou, T. Chen, J.J. Tan, G.P. Ru, Y.L. Jiang, R. Liu, and X.P. Qu, Chinese Phys. Lett. 24, 1400 (2007).

- <sup>16</sup> S.S. Yim, D.J. Lee, K.S. Kim, S.H. Kim, T.S. Yoon, and K.B. Kim, J. Appl. Phys. **103**, (2008).

- <sup>17</sup> J. Heo, S.Y. Lee, D. Eom, C.S. Hwang, and H.J. Kim, Electrochem. Solid-State Lett. 11, 3 (2008).

- <sup>18</sup> R.J. Martín-Palma and C.G. Pantano, Mater. Res. Express **6**, (2019).

- <sup>19</sup> M. Zhang, W. Chen, S.-J. Ding, X.-P. Wang, D.W. Zhang, and L.-K. Wang, J. Vac. Sci. Technol. A Vacuum, Surfaces, Film. **25**, 775 (2007).

- <sup>20</sup> J. Soethoudt, F. Grillo, E.A. Marques, J.R. van Ommen, Y. Tomczak, L. Nyns, S. Van Elshocht, and A. Delabie, Adv. Mater. Interfaces **5**, 1 (2018).

- <sup>21</sup> L.G. Wen, P. Roussel, O.V. Pedreira, B. Briggs, B. Groven, S. Dutta, M.I. Popovici, N. Heylen, I. Ciofi, K. Vanstreels, F.W. Østerberg, O. Hansen, D.H. Petersen, K. Opsomer, C. Detavernie, C.J. Wilson, S. Van Elshocht, K. Croes, J. Bömmels, Z. Tökei, and C. Adelmann, ACS Appl. Mater. Interfaces **8**, 26119 (2016).

- <sup>22</sup> V. Chobpattana, T.E. Mates, W.J. Mitchell, J.Y. Zhang, and S. Stemmer, J. Appl. Phys. 114, 0 (2013).

- <sup>23</sup> J. Wu, Y. Fang, B. Markman, H. Tseng, and M.J.W. Rodwell, **39**, 472 (2018).

- <sup>24</sup> W.J. Mitchell, B.J. Thibeault, D.D. John, and T.E. Reynolds, J. Vac. Sci. Technol. A 39, 043204 (2021).

- <sup>25</sup> Y. Fang, H. Tseng, and M.J.W. Rodwell, in *Device Res. Conf.* (2019), pp. 0–1.

- <sup>26</sup> S. Cwik, K.N. Woods, M.J. Saly, T.J. Knisley, and C.H. Winter, J. Vac. Sci. Technol. A 38, 012402 (2020).

- <sup>27</sup> S. Yeo, S.H. Choi, J.Y. Park, S.H. Kim, T. Cheon, B.Y. Lim, and S. Kim, Thin Solid Films **546**, 2 (2013).

- <sup>28</sup> J. Lu and J.W. Elam, Chem. Mater. **27**, 4950 (2015).

- <sup>29</sup> C.Y. Huang, S. Lee, V. Chobpattana, S. Stemmer, A.C. Gossard, B. Thibeault, W. Mitchell, and M. Rodwell, in *Tech. Dig. Int. Electron Devices Meet. IEDM* (2015), pp. 25.4.1–25.4.4.

- <sup>30</sup> S. Seok, IEEE Trans. Components, Packag. Manuf. Technol. 6, 1301 (2016).