Bikramjit Chatterjee<sup>®</sup>, Dong Ji<sup>®</sup>, *Member, IEEE*, Anchal Agarwal, Silvia H. Chan<sup>®</sup>, Srabanti Chowdhury<sup>®</sup>, *Senior Member, IEEE*, and Sukwon Choi<sup>®</sup>, *Member, IEEE*

Abstract—An electro-thermal co-design study has been performed on vertical GaN transistors (oxide, GaN interlayer based vertical trench MOSFETs; OG-FETs). Vertical (GaN-on-GaN) and quasi vertical (GaN-on-sapphire) devices were investigated. Vertical devices showed a 60% lower device peak temperature rise as compared to the quasivertical OG-FETs. Using electro-thermal device simulation, the internal electric field and heat generation distributions within the OG-FETs were analyzed. The temperature rise of a hexagonal honeycomb structured scaled array of OG-FETs was characterized using thermoreflectance thermal imaging and infrared thermography. A 3D thermal model was used to evaluate the impact of design variables including the number of cells, the pitch between individual cells, and the aspect ratio of the array configuration on the self-heating behavior of multi-cell arrays of OG-FETs.

*Index Terms*— Electrothermal effects, gallium nitride, power MOSFET, thermoreflectance imaging, thermal management of electronics.

#### I. INTRODUCTION

G ALLIUM nitride (GaN) is one of the most promising semiconductors for building high-frequency and high-power electronic devices due to its wide bandgap, high saturation velocity, large breakdown field and good bulk thermal conductivity [1], [2]. GaN power devices commercialized to date include lateral AlGaN/GaN high electron mobility transistors (HEMTs) and vertical Schottky barrier diodes [1] However, the lateral HEMT structures are limited to medium voltage (650-900V) power switching, and do not scale effectively to support higher voltages. In order to design a HEMT

Manuscript received January 30, 2021; revised March 2, 2021; accepted March 6, 2021. Date of publication March 10, 2021; date of current version April 26, 2021. This work was supported in part by the Air Force Office of Scientific Research (AFOSR) Young Investigator Program under Grant FA9550-17-1-0141, in part by NSF under Grant CBET-1934482, and in part by Advanced Research Projects Agency-Energy (ARPA-E) SWITCHES. The review of this letter was arranged by Editor R. Quay. (*Corresponding author: Sukwon Choi.*)

Bikramjit Chatterjee and Sukwon Choi are with the Department of Mechanical Engineering, The Pennsylvania State University, University Park, PA 16802 USA (e-mail: sukwon.choi@psu.edu).

Dong Ji is with the Department of Electrical Engineering, Stanford University, Stanford, CA 94305 USA, and also with Intel Corporation, Santa Clara, CA 95054 USA.

Anchal Agarwal is with the Department of Electrical and Computer Engineering, University of California, Santa Barbara, CA 93106 USA and also with Western Digital Corporation, San Jose, CA 95138 USA.

Silvia H. Chan is with the Department of Electrical and Computer Engineering, University of California, Santa Barbara, CA 93106 USA and also with SpaceX Corporation, Hawthorn, CA 90250 USA.

Srabanti Chowdhury is with the Department of Electrical Engineering, Stanford University, Stanford, CA 94305 USA.

Color versions of one or more figures in this letter are available at https://doi.org/10.1109/LED.2021.3065362.

Digital Object Identifier 10.1109/LED.2021.3065362

for larger breakdown voltages, the gate-to-drain spacing needs to be increased, resulting in a larger device footprint and a reduction in the effective current density per unit area, leading to increased chip size and cost. Furthermore, this negatively impacts the high-speed switching performance of the device due to the increased parasitic elements. In contrast, for vertical devices, the blocking voltage is enhanced by increasing the drift layer thickness, without compromise of the device footprint. Additional advantages for the vertical configuration includes larger threshold voltage, peak electric field buried in the GaN bulk, and the absence of current collapse. [3], [4]

Recent advancements in three-terminal GaN vertical devices include the development of the current aperture vertical electron transistor (CAVET) [5]–[9] and other forms of MOSFETs [10]–[12], including the oxide-GaN interlayerbased field effect transistor (OG-FET/OGFET) [9], [13]. While the CAVET is similar to a double-diffused metal oxide semiconductor, the OGFET is similar to a trench MOSFET that includes a GaN interlayer grown via metal organic chemical vapor deposition (MOCVD) to reduce the device ON-resistance. [3]

Work by Ji *et al.* [3] has shown the superior electrical performance and power handling capability of OGFETs fabricated on GaN substrates (vertical OGFET; V-OGFET) as well as sapphire substrates (quasi-vertical OGFET; QV-OGFET). While a breakdown voltage of 700 V was demonstrated, a current density of ~0.5 A was observed for scaled multi-cell arrays with an area of 400  $\mu$ m × 500  $\mu$ m. In this work, the thermal characteristics of single-cell and multi-cell arrays of both QV-OGFETs and V-OGFETs were investigated using high resolution optical thermography techniques and coupled electro-thermal modeling.

### II. DEVICE DESCRIPTION

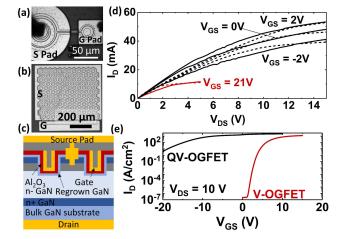

The V-OGFET and QV-OGFETs were fabricated atop a hydride vapor phase epitaxy (HVPE)-grown n+ GaN and sapphire substrates, respectively, using metal organic chemical vapor deposition (MOCVD). A MOCVD-regrown unintentionally doped GaN layer of 10 nm thickness serves as the channel in these devices. Details of the fabrication procedure and device design are in reference [3]. An optical image of a V-OGFET and its cross-section are shown in Figs. 1 (a) and (c), with Fig. 1 (b) showing the planar view of a scaled V-OGFET array. Fig. 1 (c) shows measured and simulated I-V characteristics of the V- and QV-OGFET. Transfer characteristics of the devices are shown in Fig. 1(e) [3].

# III. SINGLE CELL DEVICE CHARACTERIZATION

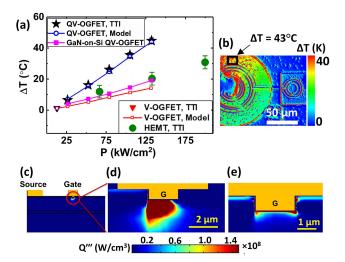

Fig. 2 (a) shows the temperature rise of these devices under varying power conditions as obtained from experimental and

0741-3106 © 2021 IEEE. Personal use is permitted, but republication/redistribution requires IEEE permission. See https://www.ieee.org/publications/rights/index.html for more information.

Fig. 1. Top-view of (a) single cell and (b) scaled array of V-OGFETs. (c) Cross-sectional schematic of a V-OGFET. For a similar QV-OGFET, the drain is located near the edge of the device die surface. (d) Output I-V characteristics from measurements (solid-lines) and electro-thermal simulation (dashed-lines). (e) Transfer characteristics for QV- and V-OGFETs. The black and red curves are for a QV-OGFET and a V-OGFET, respectively.

Fig. 2. (a) The temperature rise vs. areal power density of the QV- and V-OGFETs, and an AlGaN/GaN HEMT, obtained from TTI measurements. Also shown are simulation results for the OGFETs, including a GaN-on-Si QV-OGFET. (b) 2D temperature map of a QV-OGFET. (c) Cross-sectional view of the heat generation distribution (Q<sup>'''</sup>) within a V-OGFET. Zoomed in views of (d) a V-OGFET near the active region and (e) a QV-OGFET near the active region. The areal power densities for (a), (c) (d) and (e) are 132 kW/cm<sup>2</sup>.

simulation studies. Both the V- and the QV- OGFETs were characterized via thermoreflectance thermal imaging (TTI) and results were confirmed using infrared (IR) thermography, both of which are in-situ optical thermography techniques. While IR thermography works for high-emissivity surfaces and offers relatively low spatial resolution ( $\sim 3 \mu m$ ), TTI is particularly suitable for measuring metallization temperatures, with a higher spatial resolution ( $\sim 0.78 \mu m$  in this study). Details of the thermal characterization procedures can be found in [15].

Fig. 2 (b) shows the 2D temperature map of a QV-OGFET under a power dissipation level of  $P = 500 \text{ mW} (132 \text{ kW/cm}^2;$  areal power density based on the area enclosed by trench sidewalls) at  $V_{GS} = 0V$  and  $V_{DS} = 13.3V$ . The device temperature rise ( $\Delta T$ ) is represented by the average temperature

within the rectangular region of interest shown in Fig. 2 (b). For the V-OGFETs, the maximum power level during testing was limited to 50 mW (13.2 kW/cm<sup>2</sup>) due to the low current levels, resulting in a minimal  $\Delta T$ .

To compare the self-heating behavior of the V- and QV-OGFETs at higher power conditions, an electro-thermal model was built by coupling a 2D electrical model (Synopsys Sentaurus) with a 3D finite element thermal model (COMSOL Multiphysics). The electrical model accounts for temperature dependent parameters such as electron mobility, electronic bandgap, and thermal conductivity. Details of the coupled modeling procedure can be found in references [16], [17]. The thermal conductivity of the GaN substrate and various GaN layers (with different doping schemes/levels) were adopted from our previous work and a report by Song *et al.* [18] and Beechem *et al.* [19]. The electrical and thermal modeling outputs for both QV- and V-OGFETs were validated as illustrated in Fig. 1 (c) (I-V curves) and Fig. 2 (a) (device surface temperatures).

A comparison between the V- and QV-OGFETs and a typical GaN-on-Si AlGaN/GaN HEMT is shown in Fig. 2 (a). Also shown is the simulation result for a GaN-on-Si QV-OGFET with an identical device design as the GaN-on-Sapphire QV-OGFET. Details of the HEMT structure and thermal characterization results can be found in the authors' prior work [15]. The V-OGFET, GaN-on-Si QV-OGGET and the lateral HEMT exhibit a comparable  $\Delta T$ for similar areal power densities (i.e., heat flux conditions). However, the channel  $\Delta T$  the GaN-on-sapphire QV-OGFET was  $\sim 3 \times$  higher under identical power dissipation levels, as shown in Fig. 2 (a). This difference is mainly attributed to the poor thermal conductivity of the sapphire substrate ( $\kappa = 35-40$  W/mK at 300 K) as compared to bulk GaN ( $\kappa \sim 200$  W/mK at 300 K). [18]

Fig. 2 (b) shows a surface temperature map of an operational QV-OGFET under  $V_{GS} = 0V$ ,  $V_{DS} = 13.3V$ , P = 500 mW (132 kW/cm<sup>2</sup>). Hotter regions form near the gate ring, also confirmed via electro-thermal modeling. As shown in Figs. 2 (c)-(e), for both the V- and QV-OGFETs, the internal heat generation profile, Q''' (x,y) is mainly concentrated within the GaN interlayer. Here Q'''(x,y) is the distribution of volumetric heat generation (units: W/cm<sup>3</sup>) representative of the internal Joule heating. This concentrated pattern of Q''' is a result of the electron current density fields within these devices (not shown), that exhibit similar patterns as the Q". However, in case of a V-OGFET, a relatively large portion of Q''' occurs within the drift region underneath the trench, as compared to a QV-OGFET. The heat generation is more distributed in the vertical device since the current flows through the n+ GaN substrate. The differing Q<sup>'''</sup> profiles of each device configuration determine the distinct surface temperature patterns for the two types of OGFETs. It should be noted that Q''' (x,y) is also a function of the drift region resistance. With an order of magnitude reduction in the drift region doping density, the peak Q''' near the center of the trench can reduce by  $\sim 30\%$ .

To evaluate the fractional contributions of the device configuration and the substrate thermal conductivity to the higher peak temperatures observed in the QV-OGFET, simulation was performed to model a QV-OGFET employing a GaN substrate, at P = 500 mW (132 kW/cm<sup>2</sup>), identical to the case of Fig. 2(a). It was found that the QV-configuration (which determines the current and Q<sup>'''</sup> distributions) and the lower

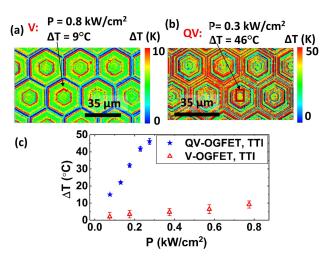

Fig. 3. Surface temperature maps of (a) V-OGFET and (b) QV-OGFET arrays. (c) Increase in  $\Delta T$  vs. power density for V- and QV-OGFETs.

$\kappa$  of sapphire contribute 13% and 87%, respectively, to the higher  $\Delta T$  observed in the QV-OGFET.

# IV. HIGH DENSITY CELL ARRAYS OF OGFETS

In order to overcome the relatively low current level of the single cell V-OGFETs, high density V-OGFET arrays with an active area as large as 0.4 mm  $\times$  0.5 mm have been demonstrated in the authors' previous work. [3] The surface  $\Delta T$  of these cell arrays were determined using the TTI technique, as shown in Fig. 3. Fig. 3 (a) shows a temperature map of a V-OGFET scaled array with a 12×12 honeycomb cell arrangement, which is dissipating 2 W of power (0.8 kW/cm<sup>2</sup>). A temperature map of a 42 × 12 QV-OGFET array is shown in Fig. 3 (b) under a power dissipation level of 0.3 kW/cm<sup>2</sup>. Similar to the case of single cell devices, the QV-OGFET cell array exhibits higher temperatures, as shown in Fig. 3 (c). The  $\Delta T$  is considerably higher than the V-OGFET arrays even under lower power density operation.

## V. THERMAL DESIGN OF THE MULTI-CELL ARRAYS

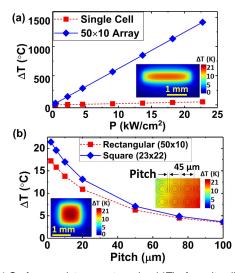

The cell arrays can be arranged with different aspect ratios and with different pitch between adjacent cells. These can lead to varying levels of device peak temperatures even under identical power density conditions, that will impact the device performance and reliability [20]. Thermal models were used to investigate the impact of these design variables. It was observed that the V-OGFET arrays would show  $\Delta T \sim 19^{\circ}$ C under  $\sim 1.2$  kW/cm<sup>2</sup> power density conditions (demonstrated in [3]). Results are summarized in Fig. 4 (a) and (b).

Fig. 4 (a) shows that the  $\Delta T$  for the center unit cell of a 50 × 10 scaled cell array can be more than ~30× hotter than a single cell OGFET dissipating an identical power per unit cell condition of 100 mW (4.6 kW/cm<sup>2</sup>). This reveals the amplified self-heating that individual cells will experience for scaled array configurations, as compared to single cell devices. The higher  $\Delta T$  for these scaled cell-arrays is attributed to the Neuman (adiabatic) thermal boundary condition formed between single cells at the planes of symmetry. In other words, the thermal cross-talk among individual cells impede the lateral (in-plane) heat diffusion towards the die periphery, thus increasing the device thermal resistance.

Fig. 4 (b) shows that by increasing the distance between two neighboring devices,  $\Delta T$  can be reduced by a large extent,

Fig. 4. (a) Surface peak temperature rise ( $\Delta$ T) of a unit cell device and a 50 × 10 cell array as a function of power dissipation. (b) The  $\Delta$ T of cell arrays with different aspect ratio and inter-cell pitch. The insets in (a) and (b) show thermal modeling results for 50 × 10 and 23 × 22 cell arrays, respectively, with a pitch of 2  $\mu$ m, operating under 6 mW/cell.

albeit at the cost of the device footprint. On the other hand, packing cells in a lower aspect ratio design is unfavorable in terms of thermal performance as a square-shaped scaled design of  $23 \times 22$  cell arrangement (504 cells) shows ~20% higher  $\Delta T$ , as compared to a rectangular-shaped 50 × 10 (500 cells) scaled cell array. These findings substantiate the importance of the cell packing arrangement on the overall device thermal resistance. The superiority of higher aspect ratio designs in terms of thermal performance has been reported for multi-finger GaN HEMTs. [21], [22]

To understand the thermal response of the OGFET arrays under transient conditions similar to power switching operation, thermal simulations were run at frequencies of 100 kHz and 1 MHz, [23] under an on-state power dissipation level of 100 W (~9.1 kW/cm<sup>2</sup>) and 10% duty cycle. Under such switching speeds, the QV- and V-OGFETs showed identical  $\Delta$ T. This is attributed to the limited extent of thermal diffusion of the generated heat from the active region so that the substrate thermal conductivity is rendered inconsequential. The resulting  $\Delta$ T was observed to be ~5% of that for DC operation, in case of the V-OGFET for a 1 MHz switching frequency. This suggests that self-heating would have less impact on the device performance and reliability under such operating conditions.

## VI. CONCLUSION

In this report, OGFETs have been characterized using TTI, an in-situ optical thermography technique. The peak  $\Delta T$  of a single-cell GaN-on-GaN V-OGFET was shown to be 68% lower than that for a GaN-on-sapphire QV-OGFET, due to the higher thermal conductivity of the GaN substrate and the difference in the current flow pattern. For both devices, majority of Joule-heating is concentrated near the trench and the GaN interlayer. A scaled QV-OGFET cell array was shown to experience a  $\sim 30 \times$  higher peak temperature than a single cell OGFET dissipating an identical power per unit cell (100 mW/cell). This is due to the thermal cross-talk between closely packed unit cells. By increasing the inter-cell pitch and the array aspect ratio, the peak temperature of OGFET cell arrays can be significantly reduced.

### REFERENCES

- C. Gupta, S. H. Chan, Y. Enatsu, A. Agarwal, S. Keller, and U. K. Mishra, "OG-FET: An *in-situ* oxide, GaN interlayer-based vertical trench MOSFET," *IEEE Electron Device Lett.*, vol. 37, no. 12, pp. 1601–1604, Dec. 2016, doi: 10.1109/LED.2016.2616508.

- [2] R. J. Trew, G. L. Bilbro, W. Kuang, Y. Liu, and H. Yin, "Microwave AlGaN/GaN HFETs," *IEEE Microw. Mag.*, vol. 6, no. 1, pp. 56–66, Mar. 2005, doi: 10.1109/MMW.2005.1417998.

- [3] D. Ji, C. Gupta, A. Agarwal, S. H. Chan, C. Lund, W. Li, S. Keller, U. K. Mishra, and S. Chowdhury, "Large-area *in-situ* oxide, GaN interlayer-based vertical trench MOSFET (OG-FET)," *IEEE Electron Device Lett.*, vol. 39, no. 5, pp. 711–714, May 2018, doi: 10.1109/LED.2018.2813312.

- [4] R. Vetury, N. Q. Zhang, S. Keller, and U. K. Mishra, "The impact of surface states on the DC and RF characteristics of AlGaN/GaN HFETs," *IEEE Trans. Electron Devices*, vol. 48, no. 3, pp. 560–566, Mar. 2001, doi: 10.1109/16.906451.

- [5] S. Chowdhury, M. H. Wong, B. L. Swenson, and U. K. Mishra, "CAVET on bulk GaN substrates achieved with MBE-regrown AlGaN/GaN layers to suppress dispersion," *IEEE Electron Device Lett.*, vol. 33, no. 1, pp. 41–43, Jan. 2012, doi: 10.1109/LED.2011.2173456.

- [6] S. Mandal, A. Agarwal, E. Ahmadi, K. M. Bhat, D. Ji, M. A. Laurent, S. Keller, and S. Chowdhury, "Dispersion free 450-V p GaNgated CAVETs with Mg-ion implanted blocking layer," *IEEE Electron Device Lett.*, vol. 38, no. 7, pp. 933–936, Jul. 2017, doi: 10.1109/LED.2017.2709940.

- [7] D. Ji, A. Agarwal, H. Li, W. Li, S. Keller, and S. Chowdhury, "880 V/2.7 mΩ·cm<sup>2</sup> MIS gate trench," *IEEE Electron Device Lett.*, vol. 39, no. 6, pp. 2018–2020, Jun. 2018.

- [8] H. Nie, Q. Diduck, B. Alvarez, A. P. Edwards, B. M. Kayes, M. Zhang, G. Ye, T. Prunty, D. Bour, and I. C. Kizilyalli, "1.5-kV and 2.2-mΩ-cm<sup>2</sup> vertical GAN transistors on bulk-GaN substrates," *IEEE Electron Device Lett.*, vol. 35, no. 9, pp. 939–941, Sep. 2014, doi: 10.1109/LED.2014.2339197.

- [9] M. Kanechika, M. Sugimoto, N. Soejima, H. Ueda, O. Ishiguro, M. Kodama, E. Hayashi, K. Itoh, T. Uesugi, and T. Kachi, "A vertical insulated gate AlGaN/GaN heterojunction field-effect transistor," *Jpn. J. Appl. Phys.*, vol. 46, no. 21, pp. L503–L505, 2007, doi: 10.1143/JJAP.46.L503.

- [10] T. Oka, Y. Ueno, T. Ina, and K. Hasegawa, "Vertical GaN-based trench metal oxide semiconductor field-effect transistors on a free-standing GaN substrate with blocking voltage of 1.6 kV," *Appl. Phys. Exp.*, vol. 7, no. 2, pp. 8–11, Jan. 2014, doi: 10.7567/APEX.7.021002.

- [11] D. Shibata, R. Kajitani, M. Ogawa, K. Tanaka, S. Tamura, and T. Hatsuda, "1.7 kV/1.0 mΩcm<sup>2</sup> normally-off vertical GaN transistoron GaN substrate with regrown p-GaN/AlGaN/GaN semipolar gate structure," in *IEDM Tech. Dig.*, Dec. 2016, pp. 248–251.

- [12] Y. Zhang, M. Sun, M. Pedra, Z. Liu, Y. Lin, X. Gao, K. Shepard, and T. Palacios, "1200 V GaN vertical fin power field-effect transistors," in *IEDM Tech. Dig.*, San Francisco, CA, USA, Dec. 2017, pp. 9.2.1–9.2.4, doi: 10.1109/IEDM.2017.8268357.

- [13] D. Ji, C. Gupta, S. H. Chan, A. Agarwal, W. Li, S. Keller, U. K. Mishra, and S. Chowdhury, "Demonstrating >1.4 kV OG-FET performance with a novel double field-plated geometry and the successful scaling of largearea devices," in *IEDM Tech. Dig.*, San Francisco, CA, USA, Dec. 2017, pp. 9.4.1–9.4.4, doi: 10.1109/IEDM.2017.8268359.

- [14] T. J. Flack, B. N. Pushpakaran, and S. B. Bayne, "GaN technology for power electronic applications: A review," *J. Electron. Mater.*, vol. 45, no. 6, pp. 2673–2682, Jun. 2016, doi: 10.1007/s11664-016-4435-3.

- [15] B. Chatterjee, D. Shoemaker, Y. Song, T. Shi, H.-L. Huang, D. Keum, A. Krishnan, B. M. Foley, I. Jovanovic, J. Hwang, H. Kim, and S. Choi, "Cumulative impacts of proton irradiation on the self-heating of AlGaN/GaN HEMTs," ACS Appl. Electron. Mater., vol. 2, no. 4, pp. 980–991, Apr. 2020, doi: 10.1021/acsaelm.0c00048.

- [16] B. Chatterjee, C. Dundar, T. E. Beechem, E. Heller, D. Kendig, H. Kim, N. Donmezer, and S. Choi, "Nanoscale electro-thermal interactions in AlGaN/GaN high electron mobility transistors," *J. Appl. Phys.*, vol. 127, no. 4, p. 44502, Jan. 2020, doi: 10.1063/1.5123726.

- [17] B. Chatterjee, Y. Song, J. S. Lundh, Y. Zhang, Z. Xia, Z. Islam, J. Leach, C. McGray, P. Ranga, S. Krishnamoorthy, A. Haque, S. Rajan, and S. Choi, "Electro-thermal co-design of β-(Al<sub>x</sub>Ga<sub>1-x</sub>)<sub>2</sub>O<sub>3</sub>/Ga<sub>2</sub>O<sub>3</sub> modulation doped field effect transistors," *Appl. Phys. Lett.*, vol. 117, no. 15, Oct. 2020, Art. no. 153501, doi: 10.1063/5.0021275.

- [18] Y. Song, J. S. Lundh, W. Wang, J. H. Leach, D. Eichfeld, A. Krishnan, C. Perez, D. Ji, T. Borman, K. Ferri, J.-P. Maria, S. Chowdhury, J.-H. Ryou, B. M. Foley, and S. Choi, "The doping dependence of the thermal conductivity of bulk gallium nitride substrates," *J. Electron. Packag.*, vol. 142, no. 4, pp. 1–10, Dec. 2020, doi: 10.1115/ 1.4047578.

- [19] T. E. Beechem, A. E. McDonald, E. J. Fuller, A. A. Talin, C. M. Rost, J.-P. Maria, J. T. Gaskins, P. E. Hopkins, and A. A. Allerman, "Size dictated thermal conductivity of GaN," *J. Appl. Phys.*, vol. 120, no. 9, Sep. 2016, Art. no. 095104, doi: 10.1063/1.4962010.

- [20] S. Choi, E. R. Heller, D. Dorsey, R. Vetury, and S. Graham, "The impact of bias conditions on self-heating in AlGaN/GaN HEMTs," *IEEE Trans. Electron Devices*, vol. 60, no. 1, pp. 159–162, Jan. 2013, doi: 10.1109/TED.2012.2224115.

- [21] A. Chvála, J. Marek, P. Príbytný, A. Šatka, S. Stoffels, N. Posthuma, S. Decoutere, and D. Donoval, "Analysis of multifinger power HEMTs supported by effective 3-D device electrothermal simulation," *Microelectron. Rel.*, vol. 78, pp. 148–155, Nov. 2017, doi: 10.1016/j.microrel.2017.08.012.

- [22] J.-H. Wang, X.-H. Wang, L. Pang, X.-J. Chen, and X.-Y. Liu, "Modeling, simulation and analysis of thermal resistance in multi-finger AlGaN/GaN HEMTs on SiC substrates," *Chin. Phys. Lett.*, vol. 29, no. 8, Aug. 2012, Art. no. 088502, doi: 10.1088/0256-307X/29/8/ 088502.

- [23] D. Ji, W. Li, and S. Chowdhury, "Switching performance analysis of GaN OG-FET using TCAD device-circuit-integrated model," in *Proc. IEEE 30th Int. Symp. Power Semiconductor Devices ICs (ISPSD)*, May 2018, pp. 208–211, doi: 10.1109/ISPSD.2018. 8393639.