# Diamond-Incorporated Flip-Chip Integration for Thermal Management of GaN and Ultra-Wide Bandgap RF Power Amplifiers

Daniel Shoemaker<sup>®</sup>, Mohamadali Malakoutian, *Member, IEEE*, Bikramjit Chatterjee<sup>®</sup>, Yiwen Song<sup>®</sup>, Samuel Kim<sup>®</sup>, Brian M. Foley, Samuel Graham<sup>®</sup>, *Senior Member, IEEE*, Christopher D. Nordquist<sup>®</sup>, *Senior Member, IEEE*, Srabanti Chowdhury<sup>®</sup>, *Senior Member, IEEE*, and Sukwon Choi<sup>®</sup>, *Member, IEEE*

Abstract—GaN radio frequency (RF) power amplifiers offer many benefits including high power density, reduced device footprint, high operating voltage, and excellent gain and power-added efficiency. Accordingly, these parts are enabling next-generation technologies such as fifth-generation (5G) base transceiver stations and defense/aerospace applications such as high-performance radar and communication systems. However, these benefits can be overshadowed by device overheating that compromises the performance and reliability. In response to this, researchers have focused on GaN-on-diamond integration during the past decade. However, manufacturability, scalability, and long-term reliability remain as critical challenges toward the commercialization of the novel device platform. In this work, a diamond-incorporated flip-chip integration scheme is proposed that takes advantage of existing semiconductor device processing and growth techniques. Using an experimentally validated GaN-on-SiC multifinger device model, the theoretical limit of the cooling effectiveness of the device-level thermal management solution has been evaluated. Simulation results show that by employing a  $\sim$ 2- $\mu$ m diamond passivation overlayer, gold thermal bumps, and a commercial polycrystalline carrier wafer, the power amplifier's dissipated heat can be effectively routed

Manuscript received January 30, 2021; revised May 7, 2021 and June 14, 2021; accepted June 15, 2021. Date of publication June 22, 2021; date of current version August 18, 2021. The work of Daniel Shoemaker, Bikramjit Chatterjee, Yiwen Song, Brian M. Foley, and Sukwon Choi was supported in part by NSF under Grant CBET-1934482 and in part by the Air Force Office of Scientific Research (AFOSR) Young Investigator Program under Grant FA9550-17-1-0141. Sandia National Laboratories is a multimission laboratory managed and operated by National Technology & Engineering Solutions of Sandia, LLC, a wholly owned subsidiary of Honeywell International, Inc., for the U.S. DOE's National Nuclear Security Administration under Contract DE-NA-0003525. Recommended for publication by Associate Editor M. Spector upon evaluation of reviewers' comments. (Corresponding author: Sukwon Choi.)

Daniel Shoemaker, Bikramjit Chatterjee, Yiwen Song, Brian M. Foley, and Sukwon Choi are with the Department of Mechanical Engineering, The Pennsylvania State University, University Park, PA 16802 USA (e-mail: sukwon.choi@psu.edu).

Mohamadali Malakoutian and Srabanti Chowdhury are with the Department of Electrical Engineering, Stanford University, Stanford, CA 94305 USA.

Samuel Kim and Samuel Graham are with The George W. Woodruff School of Mechanical Engineering, Georgia Institute of Technology, Atlanta, GA 30332 USA.

Christopher D. Nordquist is with the Sandia National Laboratories, Albuquerque, NM 87185 USA.

Color versions of one or more figures in this article are available at https://doi.org/10.1109/TCPMT.2021.3091555.

Digital Object Identifier 10.1109/TCPMT.2021.3091555

toward the package, which leads to a junction-to-package thermal resistance lower than GaN-on-diamond high electron mobility transistors (HEMTs). Furthermore, simulation results show that this approach is even more promising for lowering the device thermal resistance of emerging ultra-wide bandgap devices based on  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> and AlGaN, below that for today's state-of-the-art GaN-on-diamond HEMTs.

Index Terms—Aluminum gallium nitride, diamond passivation, flip-chip devices, gallium nitride, gallium oxide, radio frequency (RF), Raman scattering, thermal management of electronics, wide bandgap semiconductors.

## I. INTRODUCTION

THE GaN high electron mobility transistor (HEMT) architecture offers high voltage/current handling and high-frequency operation capabilities by taking advantage of the material's large critical breakdown field and the two-dimensional electron gas (2DEG) formed via polarization doping [1]. GaN radio frequency (RF) power amplifiers have become key components enabling fifth-generation (5G) cell towers, broadband satellites, high-performance military radar, and electronic warfare systems [2]–[5].

GaN HEMTs have demonstrated RF output power densities of 40 W/mm at S-band [6], 30 W/mm at X-band [7], and 8 W/mm at W-band [8]. However, heat accumulation caused by the extreme energy dissipation in the device channel degrades signal integrity and compromises the component lifetime [9]. Therefore, commercial AlGaN/GaN HEMTs employing silicon carbide (SiC) substrates are typically operated at reduced power levels of 5–8 W/mm to circumvent device self-heating issues.

In order to address the extreme operational heat flux of GaN HEMTs ( $q''>50~{\rm kW/cm^2}$ ) [9], device-level thermal management must precede the application of package- and/or system-level active cooling solutions [10]. For device-level cooling, the main focus has been to replace the SiC substrate of commercial GaN HEMTs with polycrystalline synthetic diamond [11]–[14]. GaN-on-diamond integration has been demonstrated through bonding the GaN epitaxy onto diamond [12], [15]–[19] and direct growth of diamond underneath the GaN buffer [20]–[22]. Enhanced RF performance of 11 W/mm

2156-3950 © 2021 IEEE. Personal use is permitted, but republication/redistribution requires IEEE permission. See https://www.ieee.org/publications/rights/index.html for more information.

output power density at a 40-V drain bias with 51% power-added efficiency (PAE) has been demonstrated [18]. However, the structural rigidity of the GaN/diamond interface under prolonged high power RF operation remains unanswered [23]. The additional fabrication steps associated with the integration process and the limited availability of large diameter of GaN-on-diamond wafers are other roadblocks to the entry into high-volume low-cost manufacturing [24]. Dielectric seeding/adhesive layers are necessary for the integration of GaN and diamond. Therefore, the thermal resistance of these layers must be precisely controlled, in order to maximize the benefit of the GaN-on-diamond technology.

As compared with bottom-side device-level cooling methods (i.e., diamond substrate integration) pursued to date, this work proposes a top-side cooling approach that leverages wellestablished flip-chip heterointegration processes [25]–[27], augmented by recent breakthroughs in diamond-on-GaN growth [28]–[30]. A 3-D finite element device thermal modeling was created for a commercial multifinger GaN-on-SiC HEMT, which was validated using micro-Raman thermometry. A 480-nm-thick polycrystalline diamond film was deposited on a GaN/sapphire template to measure its thermophysical properties to be used for subsequent modeling of diverse device configurations. Using the experimentally validated device model and the measured thermophysical properties of the diamond film, simulation was performed to quantify the theoretical limit of the cooling effectiveness of a diamondincorporated flip-chip integration scheme. Furthermore, this device-level thermal management solution was applied to emerging ultra-wide bandgap (UWBG) semiconductor device technologies [31] based on  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> and AlGaN, facing overheating as a bottleneck to their commercialization.

# II. SAMPLE DESCRIPTION AND EXPERIMENTS A. Device Thermal Characterization

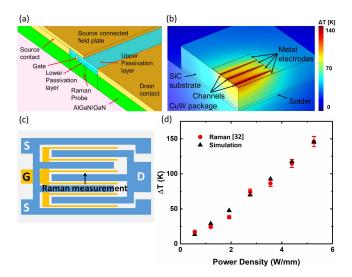

The channel temperature of a six-finger commercial GaN-on-SiC HEMT, mounted on a CuW package, was characterized using micro-Raman thermography [32]. This device had an identical epitaxial structure described in [33], and the only difference was the reduced number of gate fingers. Details of the Raman measurement setup can be found in [34] and [35]. The center point of the channel closest to the device center was measured at various power levels up to 11.69 W, which corresponds to a linear power density of 5.27 W/mm. The base temperature underneath the CuW package was maintained at 85 °C during the experiments. Measurement and device modeling results (to be discussed in Section III-A) are displayed in Fig. 1.

## B. Diamond Film Preparation and Thermal Characterization

In order to determine proper diamond thermophysical properties to be used in thermal models with diverse device configurations (to be discussed in Sections III-B and III-C), experiments were performed on a diamond film deposited on GaN. A 480-nm-thick polycrystalline diamond film was grown using a microwave plasma chemical vapor deposition (MPCVD) system (SDS 5000 Seki Diamond Systems) on a Si<sub>3</sub>N<sub>4</sub> (20 nm)/GaN (1.17  $\mu$ m)/sapphire (430  $\mu$ m) template.

Fig. 1. (a) Cross-sectional view of the channel region of the GaN-on-SiC HEMT model. (b) Quarter-thermal model of the six-finger GaN-on-SiC HEMT operated under a power density of 5.27 W/mm. (c) Planar device layout and measurement location for the Raman thermometry experiments. (d) Measured [32] and simulated channel temperature rise of the six-finger GaN-on-SiC HEMT.

The GaN layer was grown by metal organic chemical vapor deposition (MOCVD) on a sapphire substrate. Details of the growth process can be found in [29]. The optimized diamond growth process was shown not to negatively impact the device electrical characteristics [28]. The columnar grain structure of the diamond films (with increasing lateral grain size with film thickness) results in a highly anisotropic thermal conductivity (TC) where the in-plane TC ( $\kappa_r$ ) is lower than the cross-plane TC ( $\kappa_z$ ) [36]. The effective thermal boundary resistance (TBR) at the diamond/GaN interface includes contributions from the phonon mismatch between materials, the thermal resistance of the dielectric layer used for diamond seeding, and the defective nucleation/coalescence region [11], [37], [38].

Time-domain thermoreflectance (TDTR) and frequency-domain thermoreflectance (FDTR) measurements (previously used in [39]) were performed to determine  $\kappa_z$  and TBR, respectively, by taking advantage of the complementary sensitivities of the two techniques [40]. To minimize the number of fitting parameters during postprocessing, a diamond/GaN/sapphire material stack, GaN/sapphire template, and sapphire substrate were individually prepared and characterized. Au (90 nm)/Ti (7 nm) metal transducers were deposited on the samples and their thicknesses were confirmed by profilometry and cross-sectional scanning electron microscopy (SEM) measurements.

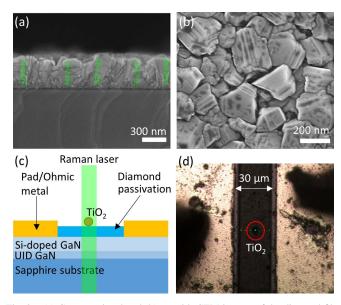

Using TDTR, the TCs of the sapphire substrate and GaN layer were determined to be 37.0  $\pm$  4.6 and 115.08  $\pm$  20.42 W/mK, respectively. These room temperature values are similar to those reported in [41] and [42]. The thickness variation of the diamond film [445–521 nm; Fig. 2(a)] and uncertainties associated with the thermal properties of the GaN/sapphire material stack resulted in a  $\kappa_z$  with a relatively large uncertainty (137.4  $\pm$  42.3 W/mK). It should be noted that  $\kappa_z$  represents the through-thickness average of the crossplane TC, while  $\kappa_z$  actually increases with the diamond thickness [43], [44].

Fig. 2. (a) Cross-sectional and (b) top-side SEM images of the diamond film deposited on a GaN/sapphire material stack. (c) Schematic and (d) optical image of the TLM structure used to estimate  $\kappa_r$  of the diamond layer.

Since both TDTR and FDTR methods did not have the measurement sensitivity to determine  $\kappa_r$ , transmission line measurement (TLM) devices (equivalent to ungated GaN HEMTs) with and without diamond passivation were fabricated. The base material stack consisted of 480-nm diamond/10-nm MOCVD  $SiN_x/320$ -nm Si-doped (1 × 10<sup>18</sup> cm<sup>-3</sup>) GaN/ 120-nm unintentionally doped (UID)  $GaN/430-\mu m$  sapphire substrate and Ti/Al/Ni/Au ohmic contacts, as shown in Fig. 2(c). The channel was 30  $\mu$ m long and 200  $\mu$ m wide. Under various power dissipation levels at room temperature, the GaN layer and diamond surface temperature at the center point of each device were measured, using standard [32] and nanoparticle-assisted Raman thermometry [35], [45]. A 3-D finite-element thermal model (COMSOL Multiphysics) was constructed with the mean value of the measured  $\kappa_z$  (137.4 W/mK) employed as a model input parameter. Temperature-dependent TCs for the GaN layers and the sapphire substrate were adopted from [41] and [42]. A constant temperature boundary condition of 25 °C was applied underneath the wafer die (which is consistent with the experimental setup) and a natural convection boundary condition (heat transfer coefficient, h = 5 W/mK) was applied to all other surfaces. A parametric sweep was performed to estimate  $\kappa_r$  (~95 W/mK), based on a diamond/GaN TBR of  $21.9 \pm 3.3 \text{ m}^2\text{K/GW}$ , which was determined from FDTR experiments, that also assumed the mean value of  $\kappa_7$ (137.4 W/mK). It should be noted that the TLM devices had to be operated up to 500 mW to clearly discern the subtle difference in the GaN channel and surface temperature of the TLM devices. At this power condition, the GaN channel (diamond surface) temperature rise for devices with and without the diamond capping layer was  $72.6 \pm 9.6 \text{ K} (84.4 \pm 1.8 \text{ K})$  and  $81.9 \pm 12.7 \text{ K}$  (87.9  $\pm 1.9 \text{ K}$ ), respectively. Despite the fact that this multimethod approach does not rigorously account for the temperature dependence of the diamond thermophysical properties, the derived  $\kappa_r$ ,  $\kappa_z$ , and TBR values (Table I) are

TABLE I

MEASURED/ESTIMATED DIAMOND THERMOPHYSICAL PROPERTIES

| Thermo-physical property                                              | Value (measurement technique)                            |

|-----------------------------------------------------------------------|----------------------------------------------------------|

| Diamond in-plane TC, $\kappa_r$<br>Diamond cross-plane TC, $\kappa_z$ | 95 W/mK (TLM, Raman, modeling)<br>137.4±42.3 W/mK (TDTR) |

| Diamond/GaN TBR                                                       | 21.9±3.3 m <sup>2</sup> K/GW (FDTR)                      |

reasonable when compared with previous reports in literature, also accounting for the relatively large average lateral grain size [ $\sim$ 344 nm; Fig. 2(b)] of the tested diamond films [36], [46] and the thickness of the SiN $_x$  (heretofore referred to simply as SiN) dielectric adhesion layer [37], [47]–[49].

## III. THERMAL MODELING

# A. Conventional Upright Configuration

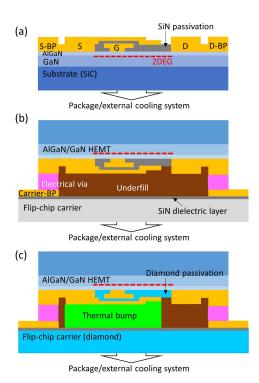

The 3-D finite-element thermal modeling of a six-finger GaN-on-SiC HEMT was performed using COMSOL Multiphysics. This device has an identical epitaxial structure described in [33], and the only difference is the reduced number of gate fingers. Taking advantage of the fourfold symmetry of the device, a quarter-model was built with an accurate solid geometry that would represent the real device [Fig. 1(b)]. Temperature-dependent TC of constituent materials for the HEMT structure (SiN passivation, AlGaN, GaN, and SiC substrate) and CuW package as well as the GaN/SiC TBR were adopted from [32], [33], and [39]. The die attach material (AuSn solder) TC was 57 W/mK (according to the vendor specifications) and the metal electrodes were assumed to be Au. Since the device was operated under fully open channel conditions ( $V_{GS} = 2.5 \text{ V}$ ), the Joule heating was assumed to occur uniformly across the channel [50]. A constant temperature boundary condition of 85 °C was applied underneath the CuW package (which is consistent with the experimental setup) and a natural convection boundary condition (h = 5 W/mK) was applied to all other surfaces. This conventional device configuration is illustrated in Fig. 3(a). The HEMT structure employs a source connected field plate (SCFP) with physical dimensions similar to that in [51] [Fig. 1(a)]. As shown in Fig. 1, the thermal response of the real device is successfully reproduced by the thermal model.

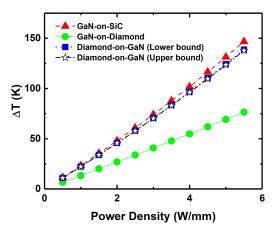

The SiC substrate of the simulated device was then replaced by polycrystalline diamond to form a GaN-on-diamond HEMT model. The temperature-dependent/anisotropic TC of the synthetic diamond substrate was adopted from [22]. The GaN/diamond substrate TBR was assumed to be the measured value in Table I (21.9 m²K/GW), which is similar to GaN/diamond effective TBRs reported in [52]. Fig. 4 shows the reduction in channel temperature by replacing the SiC substrate into diamond. The thermal resistance of this hypothetical GaN-on-diamond HEMT will serve as a benchmark to assess the cooling performance of the proposed diamond-incorporated flip-chip configuration [Fig. 3(c)].

#### B. Diamond Passivation

While most near-junction cooling efforts for GaN HEMTs have focused on GaN-on-diamond integration, a smaller

Fig. 3. (a) Conventional upright configuration. (b) Flip-chip integration of the GaN-on-SiC HEMT on a carrier wafer, without consideration of top-side heat extraction. (c) Thermally optimized diamond-incorporated flip-ship configuration. In (a) and (b), BP stands for bond pad.

Fig. 4. Channel temperature rise as a function of power density for GaN-on-SiC devices with and without diamond passivation, and a GaN-on-diamond HEMT

number of efforts have pursued device cooling through nanocrystalline diamond (NCD) coating on SiN-passivated GaN-on-SiC HEMTs [53]–[55]. While these studies demonstrate the resulting improvement in the device direct current (dc) and RF performance, the cooling effectiveness has not been accurately quantified.

The SiN passivation layer of the GaN-on-SiC HEMT model was replaced by a 980-nm-thick diamond passivation layer. While thicker diamond passivation layers will exhibit better cooling performance, the practical diamond thickness is less than  $\sim$ 2  $\mu$ m in order to prevent degradation of the 2DEG characteristics caused by undesired residual stress effects [28].

TABLE II

ASSUMED DIAMOND THERMOPHYSICAL PROPERTIES FOR CASE STUDIES

| Case  | Property                        | Value                    | References |

|-------|---------------------------------|--------------------------|------------|

|       | Thickness                       | 980 nm                   |            |

| Lower | $\kappa_{\rm r}$ (first 490 nm) | 46 W/mK                  | [36]       |

| bound | κ <sub>r</sub> (Second 490 nm)  | 77 W/mK                  | [36]       |

|       | $\kappa_z$ (first 490 nm)       | 89 W/mK                  | [36]       |

|       | κ <sub>z</sub> (Second 490 nm)  | 210 W/mK                 | [36]       |

|       | TBR                             | 24.3 m <sup>2</sup> K/GW |            |

|       | Thickness                       | 1960 nm                  |            |

| Upper | $\kappa_{\rm r}$ (first 490 nm) | 85 W/mK                  | [62]       |

| bound | κ <sub>r</sub> (Second 490 nm)  | 175 W/mK                 | [62]       |

|       | $\kappa_{\rm r}$ (third 980 nm) | 309 W/mK                 | [63]       |

|       | $\kappa_z$ (first 490 nm)       | 142 W/mK                 | [61]       |

|       | κ <sub>z</sub> (Second 490 nm)  | 310 W/mK                 | [61]       |

|       | $\kappa_z$ (third 980 nm)       | 510 W/mK                 | [63]       |

|       | TBR                             | 7.3 m <sup>2</sup> K/GW  |            |

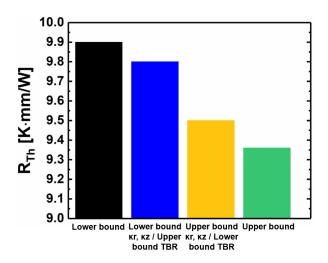

As shown in Fig. 1(a), the diamond passivation layer in the model was split into multiple domains to account for the increase in  $\kappa_r$  and  $\kappa_z$  with the diamond thickness [43], [44]. Two cases of diamond-passivated GaN-on-SiC HEMTs have been simulated, representing the lower bound and upper bound of diamond film thermophysical properties reported in literature (which represent two different diamond layer thicknesses as well as different diamond layer and interface quality).

For the lower bound case, the effective TBR between the 2DEG region (GaN surface) and the diamond passivation layer was assumed to be represented by an effective TBR that lumps the equivalent TBR arising from the 21-nm-thick AlGaN barrier ( $\kappa = 8.77 \text{ W/mK [39]}$ ) and the measured diamond/GaN TBR of 21.9 m<sup>2</sup>K/GW in Table I. This calculation results in an effective TBR of 24.3 m<sup>2</sup>K/GW. The diamond film thickness was assumed to be  $\sim 1~\mu m$  (980 nm). For the upper bound case, the thermal resistance between the GaN surface and the diamond passivation is represented by a situation where the thickness of the SiN diamond seeding layer is reduced from 20 nm (lower bound case) to 2 nm [28]. Based on the SiN TC of  $\sim 1.06$  W/mK [56], [57], an 18-nm reduction of the SiN thickness correlates to a reduction of the lumped/effective TBR by  $\sim 17 \text{ m}^2\text{K/GW}$ . Therefore, the upper bound effective TBR between the GaN surface and diamond passivation was set to be  $\sim 7.3 \text{ m}^2\text{K/GW}$ . The theoretical limit for the effective TBR between GaN and diamond was shown to be 3 m<sup>2</sup>K/GW, assuming no SiN seeding layer is implemented and only the diffusive mismatch between diamond and GaN contributes to the TBR [58], [59]. By adding the resistive contributions from the 21-nm AlGaN barrier ( $\sim$ 2.4 m<sup>2</sup>K/GW) and the 2-nm SiN seeding layer ( $\sim$ 1.9 m<sup>2</sup>K/GW) to this theoretical value, an identical effective TBR of  $\sim$ 7.3 m<sup>2</sup>K/GW is derived. These lower/upper bound case TBR values are listed in Table II. It should be noted that the diamond film thickness for this upper bound case was assumed to be  $\sim 2 \mu m$  (1960 nm) instead of the  $\sim 1 \ \mu m$  (980 nm) used for the lower bound. All of the assumptions used to derive the TBR values align with experimental findings reported in [19] and [60]. For instance, Yates et al. [60] show a diamond/GaN TBR of 9.5 m<sup>2</sup>K/GW for a sample with a 5-nm-thick SiN interlayer.

For the lower bound case, the  $\kappa_r$  and  $\kappa_z$  values for the bottom and top 490-nm domains of the diamond passivation layer [Fig. 1(a)] were based on top- and bottom-side TDTR measurements of a 1- $\mu$ m-thick diamond film reported in [36]. For the upper bound case, the  $\kappa_r$  and  $\kappa_z$  values for the bottom and middle 490-nm domains of the diamond passivation layer were chosen from [61] and [62]. For the top 980-nm domain,  $\kappa_{\rm r}$  and  $\kappa_{\rm z}$  were adopted from [63], within the error bar range of the measured values. These references were carefully chosen based on a comparison between the bottom-layer  $\kappa_r$  and  $\kappa_{7}$  values listed in Table II and those of the diamond film characterized in this work (Table I). It should be noted that the thickness of characterized film is comparable with the bottom-layer passivation layers in Table II. On the other hand, the lateral grain size of the diamond film grown in this work is larger than those in these references (see [36], [61], [62]). This aligns with the fact that  $\kappa_z$  of the characterized film lies between the lower and upper bound cases in Table II, while  $\kappa_r$  is larger than that of the upper bound case.

As shown in Fig. 4, the cooling benefit provided by diamond passivation is minute, regardless of adopting a higher quality diamond layer (upper bound case). This is because the diamond layer is exposed to a natural convection thermal boundary condition. The amount of heat spreading through this layer is much less than the heat dissipated through the substrate and package, i.e., the bottom side is the preferred pathway for heat flow due to the lower thermal resistance. Furthermore, it should be noted that the model assumes  $\kappa_r$  and  $\kappa_z$  of the diamond passivation layer are temperature invariant. For real devices, the cooling effectiveness of the diamond passivated configuration should be inferior to predictions shown in Fig. 4.

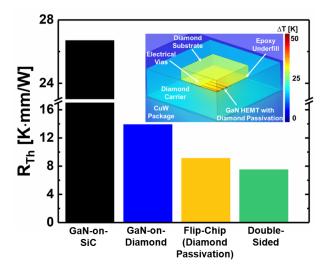

# C. Flip-Chip Integration

In the previously discussed conventional/upright device configuration, bond wires are used to interconnect the device to external circuitry. In contrast, in the flip-chip approach [64], the device is flipped over so that its bond pads connect with mirror-imaged matching pads on the carrier wafer using electrical vias [Fig. 3(b)]. However, an ordinary flip-chip configuration is inefficient in terms of heat extraction from the device, mainly because of the low TC of the epoxy underfill material ( $\kappa = 1.7$  W/mK; EPO-TEC 930-4 [65]). Recently, a thermally optimized flip-chip design locating thermal bump heat sinks between the device metal electrodes and the carrier wafer was shown to effectively lower the junction temperature of GaAs heterojunction bipolar transistors (HBTs) [66].

The key to accomplish high heat transfer performance from a flip-chip configuration is to maximize heat conduction from the heat source (for a GaN HEMT, the Joule heating region in the 2DEG) to the thermal bump, which in turn transfers heat to the carrier wafer. The proposed design scheme employs existing growth, processing, and packaging techniques: 1) a 980-nm diamond passivation layer [28] that promotes heat conduction from the 2DEG to the SCFP; 2) 2- $\mu$ m-tall Au thermal bumps [25]–[27] that transfer heat from the SCFP to the carrier wafer; and 3) a commercial polycrystalline diamond substrate [14], [43], [49] as the carrier wafer that

Fig. 5. Thermal optimization process of the flip-chip integration scheme.

spreads/dissipates the heat toward the CuW package. While the SCFP is grounded for most RF power amplifiers, the drain electrode experiences a large RF voltage swing. Therefore, we avoid the use of a thermal bump on the drain electrode that will result in added capacitance that may negatively impact the device RF performance. This diamond-incorporated flipchip configuration is displayed in Fig. 3(c). In principle, this top-side cooling approach locates the thermal solution in closer proximity to the heat source, as compared with the GaN-on-diamond bottom-side cooling method. In the model, the thickness of the bond pads and interconnects was 2  $\mu$ m. The carrier wafer length, width, and height were 1600, 1600, and 100  $\mu$ m, respectively. The 100-nm-thick SiN ( $\kappa = 4.5$  W/mK) was blanket deposited on the carrier wafer for electrical isolation.

## IV. RESULTS AND DISCUSSION

To compare the effectiveness of the flip-chip cooling method with the standard cooling methods, various flip-chip configurations were modeled for a GaN-on-SiC HEMT and the results are shown in Fig. 5. The first case was a standard flip-chip configuration with no thermal bumps, SiN passivation, SiC substrate, and an AlN carrier wafer. As expected, this configuration results in an inferior thermal performance as compared with the baseline GaN-on-SiC HEMT. The calculated junction-to-package thermal resistance (Rth) is  $\sim$ 31.1 Kmm/W, which means the channel temperature rise (with respect to the base plate temperature) will be 311 K at 10-W/mm operation. When replacing the AlN carrier wafer with a polycrystalline diamond carrier, the thermal resistance was reduced by 22% (Rth  $\sim$  24.15 Kmm/W). The implementation of thermal bumps is shown to be the most significant factor that further reduces the thermal resistance by 45.1% (Rth  $\sim$  13.25 Kmm/W), making this a more efficient cooling method than the baseline case (GaN-on-SiC HEMT with SiN passivation). However, it should be noted that the simulation results presume perfect bonding (without voids) among the Au bumps and the metallization structures. Finally, replacing the SiN passivation layer with diamond enables to further lower the thermal resistance below that for GaN-on-diamond devices. By implementing the "lower

Fig. 6. Reduction in device thermal resistance by improving thermophysical properties of the diamond passivation, for the thermally optimized flip-chip design. All *R*th values were calculated under a power density of 5.5 W/mm.

bound" diamond passivation as outlined in Table II, the resulting  $R_{Th}$  value reduces to ~9.87 Kmm/W, a further 25% reduction. For the GaN-on-diamond case listed in Fig. 5 (and subsequent Figs. 6–9), the GaN/diamond effective TBR is assumed to be 21.9 m<sup>2</sup>K/GW (from Table I; a value that is comparable with the current industry standard [67]) and the TC of the polycrystalline synthetic diamond substrate was adopted from [22] and [68].

One may speculate that ignoring any negative RF performance implications and adding a thermal bump between the drain electrode and diamond carrier wafer would result in a dramatic reduction in  $R_{\rm Th}$ . However, the resulting  $R_{\rm Th}$  reduction was found to be less than 0.4 Kmm/W ( $\sim$ 5%) from the diamond passivation-incorporated flip-chip design. Simulations show that most of the heat generated in the 2DEG conducts through the diamond passivation, SCFP and the thermal bump above it, and toward the diamond carrier wafer. This is the preferred pathway for heat dissipation being that the SCFP overhangs the majority of the channel, while the drain electrode does not. Not including a thermal bump on the drain is the preferred design anyway considering the RF performance and ease of fabrication.

Fig. 6 shows the effect of improving the thermophysical properties of the diamond passivation layer. The "Lower bound" case corresponds to the "Diamond Passivation" case represented in Fig. 5. In this model, the 980-nm diamond passivation is used with the TC and TBR values listed in Table II under "Lower bound." By applying the previously derived upper bound TBR limit of 7.3 m<sup>2</sup>K/GW (shown in Table II as the upper bound TBR) between the diamond passivation and the GaN,  $R_{\rm Th}$  is reduced by 0.5%. Now, if the 980-nm diamond passivation is replaced with a 1960-nm passivation layer with improved TC values outlined in Table II as "Upper bound" while using the lower bound TBR of 24.3 m<sup>2</sup>K/GW,  $R_{\rm Th}$  is reduced by 3.8% from the "Lower bound" case. This case is represented in Fig. 6 as "Upper bound  $\kappa_r$  and  $\kappa_z$ /Lower bound TBR." Finally, by employing the upper bound diamond passivation,  $R_{\text{Th}}$  is reduced by 5.2% from the "Lower bound"

Fig. 7. GaN HEMT ultimate device-level cooling limit (double-sided cooling; Inset: operation under a power density of 5.5 W/mm).

case. It should be noted that for real fabricated/integrated structures, the heat sinking performance of the thermal bumps can be inferior to the model predictions. This is due to the imperfect interfaces between the gold bumps, initially applied to both the device and carrier wafer metallization structures, that are eventually joined together via the flip-chip process [66]. Therefore, it is of critical importance to employ diamond layers with best thermophysical properties achievable (e.g., larger lateral grain size and lower dielectric seed layer thickness), within the growth regime (i.e., limitation in the layer thickness and film stress [28]) that prevents degradation of the intrinsic 2DEG electrical performance.

To push the limits of GaN HEMT cooling, the thermally optimized flip-chip design [shown in Fig. 3 (c)] was applied to a GaN-on-diamond device, from here on denoted as the "double-sided" cooling design. By combining both the enhanced top- and bottom-side cooling methods, a thermal resistance of 8.42 Kmm/W was achieved. This value corresponds to a 68% reduction in  $R_{\rm Th}$  compared with the conventional upright GaN-on-SiC baseline case and marks the ultimate limit for cooling the tested multifinger GaN HEMT that is achievable using diamond with state-of-the-art thermophysical standards ("upper bound" case in Table II). A comparison of this best-case scenario with the aforementioned baseline (GaN-on-SiC), GaN-on-diamond, and thermally optimized flip-chip cases can be found from Fig. 7.

# V. APPLICATION TO ULTRA-WIDE BANDGAP DEVICES

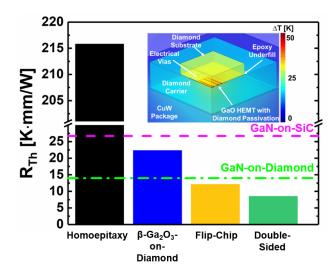

The future of RF and power switching lies with the incorporation of UWBG semiconductors such as AlGaN [69]–[71] and  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> [72] into the device design. The enhanced critical breakdown fields of these materials give promise to the development of next frontier devices with unmatched improvement in system-level size, weight, and power (SWaP) and efficiency [31].

While these UWBG materials offer substantial advantages in terms of potentially achievable electrical performance, their poor TCs [39], [73], [74] lead to greatly intensified device

Fig. 8.  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> device thermal management. A homoepitaxy baseline case,  $\beta$ -Ga<sub>2</sub>O<sub>3</sub>-on-diamond, diamond-incorporated flip-chip design, and a double-sided cooling approach are compared (Inset: double-sided cooling case under a power density of 5.5 W/mm).

self-heating. For AlGaN-channel HEMTs grown on a sapphire substrate [35], [39] and a homoepitaxial  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> modulationdoped field-effect transistor (MODFET) [65], the combined low TCs of the substrate and channel materials greatly reduce the ability for heat to dissipate through the bottom side of the device. Therefore, top-side cooling solutions that allow efficient heat extraction from the device heat generation region are pivotal to the realization of practical UWBG devices. By implementing the flip-chip design augmented by thermal bumps and diamond passivation layers, similar to the designs in Fig. 3(c), simulation results show that it is possible, in principle, to reduce the device thermal resistance to a value even lower than that of the conventional GaN-ondiamond case examined in Figs. 4 and 5. For both cases, the substrate thickness was assumed to be 100 µm and the AlGaN channel/buffer thickness is  $\sim 2 \mu m$ . It should be noted that the thickness of today's commercial  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> and sapphire substrates is on the order of 500–650  $\mu$ m. Also, it was shown in [75] that for bottom-side substrate integration schemes, reducing the thickness of the low TC  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> (and AlGaN) layers is the key to achieve high heat transfer performance; yet this is less of a concern for the flip-chip design. Details of the AlGaN-channel HEMT and  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> MODFET modeling procedure (thermal properties) can be found in [39] and [65]. In this work, both devices were assumed to have identical device layouts as the GaN-on-SiC six-finger HEMT studied so far.

Fig. 8 shows the comparison of the cooling effectiveness of a six-finger  $Ga_2O_3$  MODFET operated at a power density of 5.5 W/mm. The following four device configurations were studied: 1) homoepitaxy without additional thermal management; 2) integrating the  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> device with a diamond substrate; 3) flip-chipping a homoepitaxial device onto a diamond carrier while employing a diamond passivation layer; and 4) a  $\beta$ -Ga<sub>2</sub>O<sub>3</sub>-on-diamond MODFET using the diamond-incorporated flip-chip process (i.e., double-sided cooling).

Fig. 9. AlGaN-channel HEMT device-level thermal management. A baseline case where the AlGaN-channel HEMT is fabricated on a sapphire substrate, AlGaN-channel HEMT-on-diamond, diamond-incorporated flip-chip design, and a double-sided cooling approach are compared (Inset: double-sided cooling case under a power density of 5.5 W/mm).

For the typical homoepitaxial configuration with no flip-chipping, the poor TC and thus lack of an effective route to dissipate heat lead to  $R_{\rm Th}$  of ~216 Kmm/W, which is an order of magnitude higher than that for a typical GaN-on-SiC HEMT. However, if a diamond substrate is introduced, heat dissipation is far more efficient, and the resulting  $R_{\rm Th}$  is reduced to ~22.5 Kmm/W. Furthermore, the implementation of the top-side flip-chip cooling method with diamond passivation and thermal bumps [similar to that shown in Fig. 3(c)] further improves  $R_{\rm Th}$  to ~12.1 Kmm/W. Finally, by applying the double-sided cooling method to the Ga<sub>2</sub>O<sub>3</sub> device, it is possible to improve  $R_{\rm Th}$  to ~8.5 Kmm/W, which is lower than that of the GaN-on-diamond configuration.

Similarly, the effectiveness of the diamond substrate and flip-chip methods was studied for an AlGaN channel HEMT with Al concentrations of x = 0.7 and x = 0.85 for the channel and barrier layer, respectively, similar to the device described in [39] and [71]. For the baseline case [similar to Fig 3(a)] with the AlGaN-channel HEMT fabricated on a sapphire substrate,  $R_{\rm Th}$  is about three times higher (~75.7 Kmm/W) than GaN-on-SiC HEMTs. By replacing the sapphire substrate with diamond, R<sub>Th</sub> decreased to a level comparable with the GaN-on-SiC HEMT ( $R_{\rm Th} \sim 25.3$  Kmm/W). By applying the previously described diamond-incorporated flip-chip method (to an AlGaN-on-sapphire HEMT) as well as the double-sided cooling design,  $R_{Th}$  is further reduced to  $\sim$ 11 and  $\sim$ 8.7 Kmm/W, respectively. The diamond flip-chip cases again show that a thermal resistance lower than that of a GaN-on-diamond HEMT is possible to achieve.

# VI. CONCLUSION

In this work, the cooling effectiveness by applying diamond as a substrate, passivation layer, and carrier wafer for various device configurations was evaluated for GaN and UWBG multifinger lateral transistor structures. Due to the decent TC of GaN and SiC, simply adopting a diamond passivation

layer does not result in a significant reduction in the thermal resistance of conventional upright-positioned GaN-on-SiC HEMTs. However, flip-chipping a diamond-passivated GaN HEMT onto a diamond carrier while implementing thermal bumps into the device design significantly reduces the device thermal resistance, below that for current state-of-the-art GaNon-diamond HEMTs. In addition, this configuration can be applied to UWBG devices such as AlGaN-channel HEMTs and  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> MODFETs to reduce the thermal resistance of these devices within the range of current state-of-theart GaN-on-diamond RF power amplifiers. By implementing the double-sided cooling method, the GaN-on-diamond benchmark can be surpassed for both AlGaN and  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> devices, leading to the lowest possible thermal resistances currently achievable for these UWBG devices. In conclusion, the diamond-incorporated flip-chip integration scheme locates the heat extraction mechanism in proximity to (less than several tens of nanometers) the heat source of lateral transistors (that take advantage of a high electron mobility 2DEG, which is essential to build a high-frequency RF power amplifier). Therefore, an outstanding cooling performance can be achieved, regardless of the TC of the device base material system.

#### ACKNOWLEDGMENT

The views expressed in the article do not necessarily represent the views of the U.S. DOE or the United States Government.

# REFERENCES

- [1] R. J. Trew, G. L. Bilbro, W. Kuang, Y. Liu, and H. Yin, "Microwave AlGaN/GaN HFETs," *IEEE Microw. Mag.*, vol. 6, no. 1, pp. 56–66, Mar. 2005, doi: 10.1109/MMW.2005.1417998.

- [2] T. Kikkawa, K. Imanishi, M. Kanamura, and K. Joshin, "Recent progress of highly reliable GaN-HEMT for mass production," in *Proc. CS MANTECH Conf.*, 2006, pp. 171–174.

- [3] R. Ma, K. H. Teo, S. Shinjo, K. Yamanaka, and P. M. Asbeck, "A GaN PA for 4G LTE-advanced and 5G: Meeting the telecommunication needs of various vertical sectors including automobiles, robotics, health care, factory automation, agriculture, education, and more," *IEEE Microw. Mag.*, vol. 18, no. 7, pp. 77–85, Nov. 2017, doi: 10.1109/MMM.2017.2738498.

- [4] T. Kaneko, K. Shiikuma, and K. Kunihiro, "GaN HEMT high efficiency power amplifiers for 4G/5G mobile communication base stations," in Proc. Asia–Pacific Microw. Conf., 2014, pp. 994–997.

- [5] K. Yuk, G. R. Branner, and C. Cui, "Future directions for GaN in 5G and satellite communications," in *Proc. IEEE 60th Int. Midwest Symp. Circuits Syst. (MWSCAS)*, Aug. 2017, pp. 803–806, doi: 10.1109/MWSCAS.2017.8053045.

- [6] Y.-F. Wu, M. Moore, A. Saxler, T. Wisleder, and P. Parikh, "40-W/mm double field-plated GaN HEMTs," in *Proc. 64th Device Res. Conf.*, Jun. 2006, pp. 2005–2006, doi: 10.1109/DRC.2006.305162.

- [7] Y.-F. Wu et al., "30-W/mm GaN HEMTs by field plate optimization," IEEE Electron Device Lett., vol. 25, no. 3, pp. 117–119, Mar. 2004, doi: 10.1109/LED.2003.822667.

- [8] B. Romanczyk et al., "Demonstration of constant 8 W/mm power density at 10, 30, and 94 GHz in state-of-the-art millimeter-wave N-polar GaN MISHEMTs," *IEEE Trans. Electron Devices*, vol. 65, no. 1, pp. 45–50, Jan. 2018, doi: 10.1109/TED.2017.2770087.

- [9] A. Bar-Cohen, J. J. Maurer, and D. H. Altman, "Embedded cooling for wide bandgap power amplifiers: A review," *J. Electron. Packag.*, vol. 141, no. 4, Jul. 2019, doi: 10.1115/1.4043404.

- [10] X. Chen, F. N. Donmezer, S. Kumar, and S. Graham, "A numerical study on comparing the active and passive cooling of AlGaN/GaN HEMTs," *IEEE Trans. Electron Devices*, vol. 61, no. 12, pp. 4056–4061, Dec. 2014, doi: 10.1109/TED.2014.2360504.

- [11] A. Bar-Cohen, J. J. Maurer, and A. Sivananthan, "Near-junction microfluidic thermal management of RF power amplifiers," in *Proc. IEEE Int. Conf. Microw., Commun. Antennas Electron. Syst.*, Nov. 2015, pp. 2–8, doi: 10.1109/COMCAS.2015.7360498.

- [12] K. K. Chu et al., "High-performance GaN-on-diamond HEMTs fabricated by low-temperature device transfer process," in Proc. IEEE Compound Semicond. Integr. Circuit Symp. (CSICS), Oct. 2015, pp. 1–4, doi: 10.1109/CSICS.2015.7314511.

- [13] J. E. Graebner, S. Jin, G. W. Kammlott, J. A. Herb, and C. F. Gardinier, "Large anisotropic thermal conductivity in synthetic diamond films," *Nature*, vol. 359, no. 6394, pp. 401–403, Oct. 1992, doi: 10.1038/359401a0.

- [14] F. Ejeckam et al., "S2-t1: GaN-on-diamond: A brief history," in Proc. Lester Eastman Conf. High Perform. Devices (LEC), Aug. 2014, pp. 1–5, doi: 10.1109/LEC.2014.6951556.

- [15] P. C. Chao, K. Chu, and C. Creamer, "A new high power GaN-on-diamond HEMT with low-temperature bonded substrate technology," in *Proc. CS MANTECH Conf.*, 2013, pp. 179–182.

- [16] K. K. Chu et al., "S2-t4: Low-temperature substrate bonding technology for high power GaN-on-diamond HEMTs," in Proc. Lester Eastman Conf. High Perform. Devices (LEC), Aug. 2014, pp. 1–4, doi: 10.1109/LEC.2014.6951558.

- [17] K. K. Chu, T. Yurovchak, P. C. Chao, and C. T. Creamer, "Thermal modeling of high power GaN-on-Diamond HEMTs fabricated by low-temperature device transfer process," in *Proc. IEEE Compound Semiconductor Integr. Circuit Symp. (CSICS)*, Oct. 2013, pp. 1–4, doi: 10.1109/CSICS.2013.6659246.

- [18] P. C. Chao et al., "GaN-on-diamond HEMTs with 11 W/mm output power at 10 GHz," MRS Adv., vol. 1, no. 2, pp. 147–155, Mar. 2016, doi: 10.1557/adv.2016.176.

- [19] Z. Cheng, F. Mu, L. Yates, T. Suga, and S. Graham, "Interfacial thermal conductance across room-temperature-bonded GaN/diamond interfaces for GaN-on-diamond devices," ACS Appl. Mater. Interfaces, vol. 12, no. 7, pp. 8376–8384, Feb. 2020, doi: 10.1021/acsami. 9b16959.

- [20] D. H. Altman, A. Gupta, and M. Tyhach, "Development of a diamond microfluidics-based intra-chip cooling technology for GaN," in *Proc.* ASME, vol. 3, Jul. 2015, pp. V003T04A006-1–V003T04A006-7, doi: 10.1115/IPACK2015-48179.

- [21] M. Tyhach et al., "S2-t3: Next generation gallium nitride HEMTs enabled by diamond substrates," in Proc. Lester Eastman Conf. High Perform. Devices (LEC), Aug. 2014, pp. 1–4, doi: 10.1109/LEC.2014.6951557.

- [22] D. Altman et al., "Analysis and characterization of thermal transport in GaN HEMTs on diamond substrates," in Proc. 14th Intersociety Conf. Thermal Thermomechanical Phenomena Electron. Syst. (ITherm), May 2014, pp. 1199–1205, doi: 10.1109/ITHERM.2014.6892416.

- [23] D. Liu, S. Fabes, B.-S. Li, D. Francis, R. O. Ritchie, and M. Kuball, "Characterization of the interfacial toughness in a novel 'GaN-on-diamond' material for high-power RF devices," ACS Appl. Electron. Mater., vol. 1, no. 3, pp. 354–369, Mar. 2019, doi: 10.1021/acsaelm.8b00091.

- [24] D. Francis, F. Faili, D. Babić, F. Ejeckam, A. Nurmikko, and H. Maris, "Formation and characterization of 4-inch GaN-on-diamond substrates," *Diamond Rel. Mater.*, vol. 19, nos. 2–3, pp. 229–233, Feb. 2010, doi: 10.1016/j.diamond.2009.08.017.

- [25] S. Jangam and S. S. Iyer, "A signaling figure of merit (s-FoM) for advanced packaging," *IEEE Trans. Compon., Packag., Manuf. Technol.*, vol. 10, no. 10, pp. 1758–1761, Oct. 2020, doi: 10.1109/TCPMT.2020.3022760.

- [26] R. Mahajan et al., "Embedded multidie interconnect bridge—A localized, high-density multichip packaging interconnect," *IEEE Trans. Com*pon., Packag., Manuf. Technol., vol. 9, no. 10, pp. 1952–1962, Oct. 2019, doi: 10.1109/TCPMT.2019.2942708.

- [27] S. S. Iyer, S. Jangam, and B. Vaisband, "Silicon interconnect fabric: A versatile heterogeneous integration platform for AI systems," *IBM J. Res. Develop.*, vol. 63, no. 6, pp. 5:1–5:16, Nov. 2019, doi: 10.1147/JRD.2019.2940427.

- [28] M. Malakoutian, C. Ren, K. Woo, H. Li, and S. Chowdhury, "Development of polycrystalline diamond compatible with the latest N-polar GaN mm-wave technology," *Crystal Growth Des.*, vol. 21, no. 5, pp. 2624–2632, May 2021, doi: 10.1021/acs.cgd.0c01319.

- [29] M. A. Laurent, M. Malakoutian, and S. Chowdhury, "A study on the nucleation and MPCVD growth of thin, dense, and contiguous nanocrystalline diamond films on bare and Si3N4-coated N-polar GaN," Semicond. Sci. Technol., vol. 35, no. 1, p. 15003, 2019, doi: 10.1088/1361-6641/ab4f16.

- [30] M. Malakoutian, M. A. Laurent, and S. Chowdhury, "A study on the growth window of polycrystalline diamond on Si<sub>3</sub>N<sub>4</sub>-coated N-polar GaN," *Crystals*, vol. 9, no. 10, p. 498, Sep. 2019, doi: 10.3390/cryst9100498.

- [31] J. Y. Tsao et al., "Ultrawide-bandgap semiconductors: Research opportunities and challenges," Adv. Electron. Mater., vol. 4, no. 1, Dec. 2017, Art. no. 1600501, doi: 10.1002/aelm.201600501.

- [32] S. Choi, E. R. Heller, D. Dorsey, R. Vetury, and S. Graham, "Thermometry of AlGaN/GaN HEMTs using multispectral Raman features," *IEEE Trans. Electron Devices*, vol. 60, no. 6, pp. 1898–1904, Jun. 2013, doi: 10.1109/TED.2013.2255102.

- [33] R. Pearson, B. Chatterjee, S. Kim, S. Graham, A. Rattner, and S. Choi, "Guidelines for reduced-order thermal modeling of multifinger GaN HEMTs," *J. Electron. Packag.*, vol. 142, no. 2, Apr. 2020, doi: 10.1115/1.4046620.

- [34] J. S. Lundh et al., "Device-level multidimensional thermal dynamics with implications for current and future wide bandgap electronics," J. Electron. Packag., vol. 142, no. 3, May 2020, doi: 10.1115/1.4047100.

- [35] J. S. Lundh et al., "Multidimensional thermal analysis of an ultrawide bandgap AlGaN channel high electron mobility transistor," Appl. Phys. Lett., vol. 115, no. 15, Oct. 2019, Art. no. 153503, doi: 10.1063/1.5115013.

- [36] A. Sood *et al.*, "Anisotropic and inhomogeneous thermal conduction in suspended thin-film polycrystalline diamond," *J. Appl. Phys.*, vol. 119, no. 17, May 2016, Art. no. 175103, doi: 10.1063/1.4948335.

- [37] J. Cho, Y. Won, D. Francis, M. Asheghi, and K. E. Goodson, "Thermal interface resistance measurements for GaN-on-diamond composite substrates," in *Proc. IEEE Compound Semiconductor Integr. Circuit Symp.* (CSICS), Oct. 2014, pp. 1–4, doi: 10.1109/CSICS.2014.6978583.

- [38] Y. Won, J. Cho, D. Agonafer, M. Asheghi, and K. E. Goodson, "Cooling limits for GaN HEMT technology," in *IEEE Compound Semiconductor Integr. Circuit Symp. Tech. Dig. (CSIC)*, Oct. 2013, pp. 1–5, doi: 10.1109/CSICS.2013.6659222.

- [39] B. Chatterjee et al., "Interdependence of electronic and thermal transport in Al<sub>x</sub>Ga<sub>1-x</sub>N channel HEMTs," IEEE Electron Device Lett., vol. 41, no. 3, pp. 461–464, Mar. 2020, doi: 10.1109/LED.2020.2969515.

- [40] J. L. Braun and P. E. Hopkins, "Upper limit to the thermal penetration depth during modulated heating of multilayer thin films with pulsed and continuous wave lasers: A numerical study," *J. Appl. Phys.*, vol. 121, no. 17, May 2017, Art. no. 175107, doi: 10.1063/1.4982915.

- [41] A. M. Hofmeister, "Thermal diffusivity and thermal conductivity of single-crystal MgO and Al<sub>2</sub>O<sub>3</sub> and related compounds as a function of temperature," *Phys. Chem. Minerals*, vol. 41, no. 5, pp. 361–371, May 2014, doi: 10.1007/s00269-014-0655-3.

- [42] E. Ziade, J. Yang, G. Brummer, D. Nothern, T. Moustakas, and A. J. Schmidt, "Thickness dependent thermal conductivity of gallium nitride," *Appl. Phys. Lett.*, vol. 110, no. 3, p. 31903, Jan. 2017, doi: 10.1063/1.4974321.

- [43] J. Anaya et al., "Thermal conductivity of ultrathin nano-crystalline diamond films determined by Raman thermography assisted by silicon nanowires," Appl. Phys. Lett., vol. 106, no. 22, Jun. 2015, Art. no. 223101, doi: 10.1063/1.4922035.

- [44] M. Kuball et al., "Novel thermal management of GaN electronics: Diamond substrates," in Proc. ASME Interpack, vol. 3, Jul. 2015, Art. no. V003T08A001, doi: 10.1115/IPACK2015-48145.

- [45] J. Dallas et al., "Thermal characterization of GaN vertical p-i-n diodes," in Proc. 16th IEEE Intersociety Conf. Thermal Thermomechanical Phenomena Electron. Syst. (ITherm), May 2017, pp. 328–333, doi: 10.1109/ITHERM.2017.7992489.

- [46] J. Anaya et al., "Simultaneous determination of the lattice thermal conductivity and grain/grain thermal resistance in polycrystalline diamond," Acta Mater., vol. 139, pp. 215–225, Oct. 2017, doi: 10.1016/j.actamat.2017.08.007.

- [47] J. Cho, Z. Li, M. Asheghi, and K. E. Goodson, "Near-junction thermal management: Thermal conduction in gallium nitride composite substrates," *Annu. Rev. Heat Transf.*, vol. 18, pp. 1–65, Jan. 2014.

- [48] H. Sun et al., "Rapid characterization of GaN-on-diamond interfacial thermal resistance using contactless transient thermoreflectance," in Proc. CS MANTECH Conf., 2015, pp. 151–154.

- [49] H. Sun et al., "Temperature-dependent thermal resistance of GaN-on-diamond HEMT wafers," IEEE Electron Device Lett., vol. 37, no. 5, pp. 621–624, May 2016, doi: 10.1109/LED.2016.2537835.

- [50] S. Choi, E. R. Heller, D. Dorsey, R. Vetury, and S. Graham, "The impact of bias conditions on self-heating in AlGaN/GaN HEMTs," *IEEE Trans. Electron Devices*, vol. 60, no. 1, pp. 159–162, Jan. 2013, doi: 10.1109/TED.2012.2224115.

- [51] R. Therrien et al., "A 36 mm GaN-on-Si HFET producing 368 W at 60 V with 70% drain efficiency," in *IEDM Tech. Dig.*, Dec. 2005, pp. 568–571, doi: 10.1109/IEDM.2005.1609410.

- [52] Y. Won, J. Cho, D. Agonafer, M. Asheghi, and K. E. Goodson, "Fundamental cooling limits for high power density gallium nitride electronics," *IEEE Trans. Compon., Packag., Manuf. Technol.*, vol. 5, no. 6, pp. 737–744, Jun. 2015, doi: 10.1109/TCPMT.2015. 2433132.

- [53] T. J. Anderson *et al.*, "Nanocrystalline diamond for near junction heat spreading in GaN power HEMTs," in *Proc. IEEE Compound Semiconductor Integr. Circuit Symp. (CSIC)*, Oct. 2013, pp. 1–4, doi: 10.1109/CSICS.2013.6659241.

- [54] D. J. Meyer et al., "Large-signal RF performance of nanocrystalline diamond coated AlGaN/GaN high electron mobility transistors," *IEEE Electron Device Lett.*, vol. 35, no. 10, pp. 1013–1015, Oct. 2014, doi: 10.1109/LED.2014.2345631.

- [55] T. J. Anderson *et al.*, "Advances in diamond integration for thermal management in GaN power HEMTs," *ECS Trans.*, vol. 64, no. 7, pp. 185–190, Aug. 2014, doi: 10.1149/06407.0185ecst.

- [56] J. Cho, K. K. Chu, P. C. Chao, C. McGray, M. Asheghi, and K. E. Goodson, "Thermal conduction normal to thin silicon nitride films on diamond and GaN," in *Proc. Thermomech. Phenomena Electron. Syst. Intersoc. Conf.*, 2014, pp. 1186–1191, doi: 10.1109/ITHERM.2014.6892414.

- [57] H. Sun et al., "Reducing GaN-on-diamond interfacial thermal resistance for high power transistor applications," Appl. Phys. Lett., vol. 106, no. 11, Mar. 2015, Art. no. 111906, doi: 10.1063/1.4913430.

- [58] Y. Zhou et al., "Barrier-layer optimization for enhanced GaN-on-diamond device cooling," ACS Appl. Mater. Interfaces, vol. 9, no. 39, pp. 34416–34422, Oct. 2017, doi: 10.1021/acsami.7b08961.

- [59] D. Spiteri, J. Anaya, and M. Kuball, "The effects of grain size and grain boundary characteristics on the thermal conductivity of nanocrystalline diamond," *J. Appl. Phys.*, vol. 119, no. 8, Feb. 2016, Art. no. 085102, doi: 10.1063/1.4942522.

- [60] L. Yates et al., "Low thermal boundary resistance interfaces for GaN-on-diamond devices," ACS Appl. Mater. Interfaces, vol. 10, no. 28, pp. 24302–24309, Jul. 2018, doi: 10.1021/acsami.8b07014.

- [61] Y. Zhou et al., "Thermal characterization of polycrystalline diamond thin film heat spreaders grown on GaN HEMTs," Appl. Phys. Lett., vol. 111, no. 4, Jul. 2017, Art. no. 041901, doi: 10.1063/1.4995407.

- [62] J. Anaya et al., "Control of the in-plane thermal conductivity of ultra-thin nanocrystalline diamond films through the grain and grain boundary properties," Acta Mater., vol. 103, pp. 141–152, Jan. 2016, doi: 10.1016/j.actamat.2015.09.045.

- [63] E. O. Ziade, "Thermal transport in thin films and across interfaces," Ph.D. dissertation, Dept. Mech. Eng., Boston Univ., Boston, MA, USA, 2017.

- [64] E. M. Davis, W. E. Harding, R. S. Schwartz, and J. J. Corning, "Solid logic technology: Versatile, high-performance microelectronics," *IBM J. Res. Develop.*, vol. 8, no. 2, pp. 102–114, Apr. 1964, doi: 10.1147/rd.82.0102.

- [65] B. Chatterjee *et al.*, "Electro-thermal co-design of  $\beta$ -(Al<sub>x</sub>Ga<sub>1-x</sub>)<sub>2</sub>O<sub>3</sub>/Ga<sub>2</sub>O<sub>3</sub> modulation doped field effect transistors," *Appl. Phys. Lett.*, vol. 117, no. 15, Oct. 2020, Art. no. 153501, doi: 10.1063/5.0021275.

- [66] S. Choi et al., "Thermal design and characterization of heterogeneously integrated InGaP/GaAs HBTs," IEEE Trans. Compon., Packag., Manuf. Technol., vol. 6, no. 5, pp. 740–748, May 2016, doi: 10.1109/TCPMT.2016.2541615.

- [67] T. Gerrer et al., "Thermal design rules of AlGaN/GaN-based microwave transistors on diamond," *IEEE Trans. Electron Devices*, vol. 68, no. 4, pp. 1530–1536, Apr. 2021, doi: 10.1109/TED.2021.3061319.

- [68] H. Zhang and Z. Guo, "Thickness dependence and anisotropy of capped diamond thermal conductivity on cooling of pulse-operated GaN HEMTs," *IEEE Trans. Compon., Packag., Manuf. Technol.*, vol. 11, no. 2, pp. 233–240, Feb. 2021, doi: 10.1109/TCPMT.2021.3050976.

- [69] A. G. Baca et al., "An AlN/Al<sub>0.85</sub>Ga<sub>0.15</sub>N high electron mobility transistor," Appl. Phys. Lett., vol. 109, no. 3, Jul. 2016, Art. no. 033509, doi: 10.1063/1.4959179.

- [70] A. G. Baca et al., "High temperature operation of Al<sub>0.45</sub>Ga<sub>0.55</sub>N/Al<sub>0.30</sub>Ga<sub>0.70</sub>N high electron mobility transistors," ECS J. Solid State Sci. Technol., vol. 6, no. 11, pp. S3010–S3013, Aug. 2017, doi: 10.1149/2.0041711jss.

- [71] A. G. Baca et al., "Al<sub>0.85</sub>Ga<sub>0.15</sub>N/Al<sub>0.70</sub>Ga<sub>0.30</sub>N high electron mobility transistors with Schottky gates and large on/off current ratio over temperature," ECS J. Solid State Sci. Technol., vol. 6, no. 12, pp. Q161–Q165, Dec. 2017, doi: 10.1149/2.0231712jss.

- [72] M. Higashiwaki and G. H. Jessen, "Guest editorial: The dawn of gallium oxide microelectronics," *Appl. Phys. Lett.*, vol. 112, no. 6, p. 60401, Feb. 2018, doi: 10.1063/1.5017845.

- [73] P. Jiang, X. Qian, X. Li, and R. Yang, "Three-dimensional anisotropic thermal conductivity tensor of single crystalline β-Ga<sub>2</sub>O<sub>3</sub>," Appl. Phys. Lett., vol. 113, no. 23, Dec. 2018, Art. no. 232105, doi: 10.1063/1.5054573.

- [74] Z. Guo *et al.*, "Anisotropic thermal conductivity in single crystal  $\beta$ -gallium oxide," *Appl. Phys. Lett.*, vol. 106, no. 11, Mar. 2015, Art. no. 111909, doi: 10.1063/1.4916078.

- [75] B. Chatterjee, K. Zeng, C. D. Nordquist, U. Singisetti, and S. Choi, "Device-level thermal management of gallium oxide field-effect transistors," *IEEE Trans. Compon., Packag., Manuf. Technol.*, vol. 9, no. 12, pp. 2352–2365, Dec. 2019, doi: 10.1109/TCPMT.2019.2923356.

**Daniel Shoemaker** received the B.S. degree in mechanical engineering from The Pennsylvania State University, University Park, PA, USA, in 2020, where he is currently pursuing the Ph.D. degree in mechanical engineering, with a focus on the electrothermal analysis of wide and ultra-wide bandgap semiconductor devices.

**Mohamadali Malakoutian** (Member, IEEE) received the Ph.D. degree in electrical engineering from the University of California at Davis, Davis, CA, USA, in 2020.

He is currently a Post-Doctoral Fellow with Stanford University, Stanford, CA, USA, with a focus on high-power high-frequency transistors, all-diamond diodes, diamond integration for thermal management, and III–V wide bandgap semiconductors. His main research focuses are on the growth, fabrication, and characterization of diamond

integrated GaN high electron mobility transistors (HEMTs) for thermal management of mm-wave devices.

**Bikramjit Chatterjee** received the B.E. degree from Jadavpur University, Kolkata, India, in 2008, the M.Tech. degree from the IIT Kharagpur, Kharagpur, India, in 2010, and the Ph.D. degree in mechanical engineering from The Pennsylvania State University, University Park, PA, USA, in 2020.

He is currently a Post-Doctoral Fellow with the Georgia Institute of Technology, Atlanta, GA, USA. His current research interests include the thermal characterization, thermal management, and electrothermal co-design of wide and ultra-wide bandgap semiconductor devices.

**Yiwen Song** received the B.S. degree from The Pennsylvania State University, University Park, PA, USA, in 2019, where he is currently pursuing the Ph.D. degree in mechanical engineering.

His research focus is on the thermal characterization for novel ultra-wide bandgap and piezoelectric materials using laser-based optical pump-probe techniques.

**Samuel Kim** is currently pursuing the Ph.D. degree with the Georgia Institute of Technology, Atlanta, GA, USA.

His current research interest includes the thermal management of ultra-wide bandgap semiconductor power electronics.

**Brian M. Foley** received the B.S. and M.S. degrees from Worcester Polytechnic Institute, Worcester, MA, USA, in 2007 and 2008, respectively, and the Ph.D. degree in mechanical engineering from the University of Virginia, Charlottesville, VA, USA, in 2016.

From 2016 to 2018, he was a Post-Doctoral Researcher with the Georgia Institute of Technology, Atlanta, GA, USA. He is currently an Assistant Professor of mechanical engineering with The Pennsylvania State University, University Park, PA, USA.

His laboratory is specialized in the application and development of advanced optothermal characterization techniques for probing nanoscale thermal phenomena in novel material systems and device architectures.

Samuel Graham (Senior Member, IEEE) received the Ph.D. degree in mechanical engineering from the Georgia Institute of Technology, Atlanta, GA, USA, in 1999

From 1999 to 2003, he was a Technical Staff Senior Member with the Sandia National Laboratories, Livermore, CA, USA. He is currently a Professor and the Chair of The George W. Woodruff School of Mechanical Engineering, Georgia Institute of Technology. His current research interests include the thermal characterization and thermal reliability

of wide bandgap semiconductor devices for radio frequency (RF), power, and optoelectronic applications.

Christopher D. Nordquist (Senior Member, IEEE) received the B.S., M.S., and Ph.D. degrees in electrical engineering from The Pennsylvania State University, University Park, PA, USA, in 1997, 1998, and 2002, respectively.

At Penn State, he was an Undergraduate and a Graduate Research Assistant and NDSEG Fellow. Since 2002, he has been with the Sandia National Laboratories, Albuquerque, NM, USA, where he is currently a Technical Staff Distinguished Member of the RF Microsystems Department. His current

research interests and activities include the design, fabrication, integration, and application of emerging micromachined and solid-state radio frequency (RF) and microwave devices.

Dr. Nordquist is a Senior Member of the IEEE Electron Device and Microwave Theory and Techniques Societies.

**Srabanti Chowdhury** (Senior Member, IEEE) received the M.S. and Ph.D. degrees in electrical engineering from the University of California at Santa Barbara, Santa Barbara, CA, USA, in 2008 and 2010, respectively.

She is currently an Associate Professor of electrical engineering with Stanford University, Stanford, CA, USA, where she is also a Senior Fellow with the Precourt Institute for Energy. Her research focuses on wide bandgap and ultra-wide bandgap materials, and device engineering for energy efficient and

compact system architecture for power electronics and radio frequency (RF) applications. Besides gallium nitride, her group is exploring diamond for various active and passive (in particular, for thermal management) electronic applications.

Dr. Chowdhury is an IEEE Senior Member and Alfred P. Sloan Fellow in physics.

**Sukwon Choi** (Member, IEEE) received the B.S. and M.S. degrees from Hanyang University, Seoul, South Korea, in 2005 and 2007, respectively, and the Ph.D. degree in mechanical engineering from the Georgia Institute of Technology, Atlanta, GA, USA, in 2013.

From 2013 to 2015, he was a Post-Doctoral Appointee with the Sandia National Laboratories, Albuquerque, NM, USA. He is currently an Associate Professor of mechanical engineering with The Pennsylvania State University, University Park, PA,

USA. His current research interests include the thermal characterization and electrothermal co-design of ultra-wide bandgap semiconductor devices and piezoelectric microelectromechanical systems (MEMS).