# Thermal design of multi-fin Ga<sub>2</sub>O<sub>3</sub> vertical transistors

Cite as: Appl. Phys. Lett. **119**, 103502 (2021); https://doi.org/10.1063/5.0056557 Submitted: 11 May 2021 • Accepted: 19 August 2021 • Published Online: 07 September 2021

🗓 Bikramjit Chatterjee, 🗓 Wenshen Li, Kazuki Nomoto, et al.

#### ARTICLES YOU MAY BE INTERESTED IN

A review of Ga<sub>2</sub>O<sub>3</sub> materials, processing, and devices

Applied Physics Reviews 5, 011301 (2018); https://doi.org/10.1063/1.5006941

Thermal stability of epitaxial  $\alpha$ -Ga<sub>2</sub>O<sub>3</sub> and (Al,Ga)<sub>2</sub>O<sub>3</sub> layers on m-plane sapphire Applied Physics Letters 119, 062102 (2021); https://doi.org/10.1063/5.0064278

Ultrawide bandgap semiconductors

Applied Physics Letters 118, 200401 (2021); https://doi.org/10.1063/5.0055292

## Thermal design of multi-fin Ga<sub>2</sub>O<sub>3</sub> vertical transistors

Cite as: Appl. Phys. Lett. 119, 103502 (2021); doi: 10.1063/5.0056557 Submitted: 11 May 2021 · Accepted: 19 August 2021 · Published Online: 7 September 2021

Bikramjit Chatterjee, 1 (b) Wenshen Li, 2 (c) Kazuki Nomoto, 2 Huili Grace Xing, 2, 3, 4 (b) and Sukwon Choi 1, a) (b)

**AFFILIATIONS**

#### **ABSTRACT**

Ultra-wide bandgap  $\beta$ -gallium oxide (Ga<sub>2</sub>O<sub>3</sub>) vertical device technologies are of significant interest in the context of the development of next-generation kV-range power switching devices. In this work, thermal analysis of vertical fin channel-based metal-oxide-semiconductor field-effect transistors (or fin field-effect transistors-FinFETs) was performed using infrared thermal microscopy and coupled electrothermal modeling. FinFETs with different fin width and channel spacing were characterized to study the thermal design trade-off when attempting to minimize the footprint of multi-fin FinFET arrays. A  $50 \times 50 \ \mu\text{m}^2$  scaled FinFET cell array exhibited an  $\sim 23 \times$  higher temperature rise as compared to a 5-fin device. Devices with different orientations were fabricated and characterized. By rotating the fin channel aligned along the [010] direction by 90°, the channel temperature rise reduced by 30%, due to the anisotropy of the Ga<sub>2</sub>O<sub>3</sub> thermal conductivity ( $\kappa$ ). Electro-thermal modeling shows that a 20% reduction in the temperature rise is possible by fabricating devices on a (010)-oriented substrate as compared to the tested devices built on a (001) substrate. These results indicate the importance of the electro-thermal co-design process for Ga<sub>2</sub>O<sub>3</sub> vertical FinFET cell arrays.

Published under an exclusive license by AIP Publishing. https://doi.org/10.1063/5.0056557

In recent years,  $\beta$ -phase gallium oxide (Ga<sub>2</sub>O<sub>3</sub>) has emerged as a primary candidate to enable next-generation power electronic devices. The ultra-wide bandgap (4.6-4.9 eV)<sup>1,2</sup> of Ga<sub>2</sub>O<sub>3</sub> translates into a large critical electric field (~8 MV/cm) that is more than 2× higher than that of wide bandgap materials GaN and SiC.3 The potential performance gain by using Ga<sub>2</sub>O<sub>3</sub> in power switching applications is apparent from its Baliga's figure of merit (BFOM), which is higher than those of Si (3000 $\times$ ), SiC (10 $\times$ ), and GaN (4 $\times$ ). An advantage of Ga<sub>2</sub>O<sub>3</sub> over other ultra-wide bandgap (Al<sub>x</sub>Ga<sub>1-x</sub>N, diamond, etc.) and wide bandgap semiconductors (GaN, SiC) is that high-quality meltgrown substrates are commercially available.<sup>5-8</sup> However, one major roadblock toward the maturation of the Ga2O3 technology is device overheating, which is caused by the low anisotropic thermal conductivity ( $\kappa$ ) of the material (11–27 W/m K at 300 K). The emerging device technology will not be able to achieve the superior electrical performance suggested by the BFOM, unless this thermal challenge is overcome by using electro-thermal co-design techniques (i.e., by optimizing the device-layout design and employing thermal management solutions). 10

While significant advancements have been made in the development of  $Ga_2O_3$  lateral devices [e.g., modulation doped  $(Al_xGa_{1-x})_2O_3/$ Ga<sub>2</sub>O<sub>3</sub> heterostructures<sup>14</sup>], vertical devices are preferred for high power and high voltage applications. The vertical configuration allows for scaling the breakdown voltage by controlling the drift layer thickness without increasing the device footprint. Therefore, a higher current level can be achieved than lateral devices for a same chip area. In addition, the device characteristics are less impacted by the surface states. In 2016, a Ga<sub>2</sub>O<sub>3</sub> current aperture vertical electron transistor (CAVET) was demonstrated.<sup>15</sup> Early stage development of vertical metal-oxide-semiconductor field-effect transistors (MOSFETs) and FinFETs exhibiting relatively low breakdown voltages often without pinch-off characteristics has also been reported. 16,17 Recently, Hu et al. 18 demonstrated kV-range vertical Ga<sub>2</sub>O<sub>3</sub> transistors with normally off (E-mode) operation.<sup>19</sup> Among the vertical device architectures, the FinFET configuration provides several benefits, including stronger gate electrostatic control (by double-gating) and minimized resistance between the gate and source electrodes. The relatively low current density of individual devices can be overcome by the design of

$<sup>^1</sup>$ Department of Mechanical Engineering, The Pennsylvania State University, University Park, Pennsylvania 16802, USA

<sup>&</sup>lt;sup>2</sup>School of Electrical and Computer Engineering, Cornell University, Ithaca, New York 14853, USA

$<sup>^{3}</sup>$ Kavli Institute at Cornell for Nanoscale Science, Cornell University, Ithaca, New York 14853, USA

<sup>&</sup>lt;sup>4</sup>Department of Materials Science and Engineering, Cornell University, Ithaca, New York 14853, USA

<sup>&</sup>lt;sup>a)</sup>Author to whom correspondence should be addressed: sukwon.choi@psu.edu

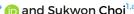

**FIG. 1.** (a) A single-fin FinFET with a fin width  $(W_{fin})$  of  $0.4~\mu m$  and fin length of  $50~\mu m$ . (b) A 5-fin FinFET with  $W_{fin}$  of  $4.4~\mu m$  and a fin spacing (S) of  $2~\mu m$ . (c) A  $50~\times~50~\mu m^2$  multi-fin transistor with  $W_{fin}=0.03~\mu m$  and  $S=2~\mu m$ . (e) The epitaxial structure of a multi-fin  $Ga_2O_3$  FinFET.

multi-fin FinFETs and the use of post-deposition annealing that improves the channel mobility. However, the thermal consequences of scaling multi-fin devices have not been experimentally studied. In this work, the self-heating behavior of FinFETs with different number of fins, fin design parameters, and device orientations was investigated. Optical thermography and electro-thermal device modeling were performed to study the impact of various design variables, including the chip area utilization (i.e., number of fins) and device/substrate orientation on the electrical and thermal performance.

An optical image of a single-fin transistor with a fin width (W<sub>fin</sub>) of  $0.4 \,\mu\text{m}$  is shown in Fig. 1(a). Figures 1(b) and 1(c) show a 5-fin device and a scaled multi-fin device with active area of  $50 \times 50 \,\mu\text{m}^2$ , respectively. A larger scaled device with an active area of  $430 \times 340 \,\mu\text{m}^2$ , W<sub>fin</sub> = 0.3  $\mu$ m and a fin spacing (S) of 2  $\mu$ m is shown in Fig. 1(d). The FinFETs were fabricated on a (001)-oriented n+ Ga<sub>2</sub>O<sub>3</sub> substrate with a 10 μm n-Ga<sub>2</sub>O<sub>3</sub> drift layer grown by halide vapor phase epitaxy [Fig. 1(e)]. For the devices shown here, the default fin length is along the [010] crystallographic direction, while the fin width is along the [100] direction. These lead to a [001]-like direction along the trench height (denoted henceforth as [001]\*), i.e., (100)-like trench sidewalls. The scaled multi-fin devices were fabricated by repeating the intermediate fin and trench structure. Details of the fabrication process can be found elsewhere. <sup>17,18,20,21</sup> The various types of devices studied in this work are summarized in Table I. For the  $50 \times 50 \,\mu\text{m}^2$  multi-fin devices, including that shown in Fig. 1(c), the number of fins was varied based on Wfin and S while the active area remains constant.

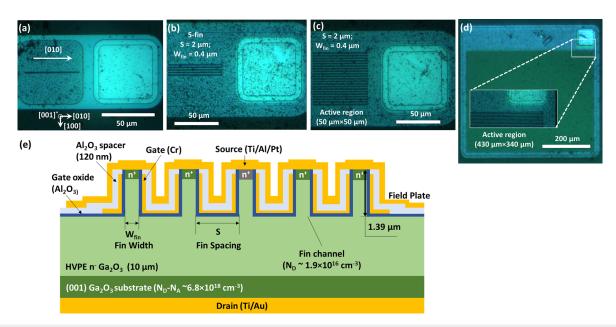

Current–voltage (I–V) characteristics of various single-fin devices are shown in Fig. 2(a) for  $W_{fin}$  of 0.3 and 0.4  $\mu m$ . The current is normalized with respect to the  $n^+$  doping area ( $W_{fin} \times 50 \ \mu m^2$ ). With an increase in  $W_{fin}$ , the resistance to the current flow from drain to source

reduces, leading to a higher current. However, as seen in Fig. 2(a), the calculated current density reduces with increased  $W_{\rm fin}$  due to the normalization scheme used. With an increase in  $W_{\rm fin}$ , the threshold voltage ( $V_{\rm th}$ ) shifts to the left as shown in Fig. 2(b). Figure 2(c) shows the I–V characteristics of a 5-fin FET with  $W_{\rm fin}=0.3\,\mu{\rm m}$  and S=3  $\mu{\rm m}$  obtained from measurements and coupled the electrothermal simulations.

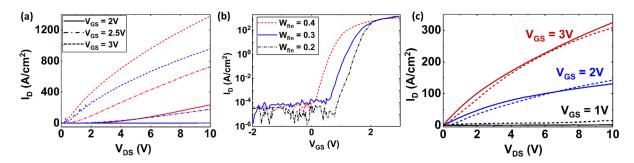

The surface temperature of the single- and multi-fin FinFETs was measured using a Quantum Focus medium wavelength infrared radiation (MWIR) Infrascope, which has also been used in our previous work on GaN p-i-n diodes and Ga $_2$ O $_3$  Schottky barrier diodes. A  $15\times$  objective was used for thermal imaging, and a pixel-by-pixel emissivity correction algorithm was used to increase the accuracy of the measurement. The diffraction limited spatial resolution was  $\sim\!2.8\,\mu\mathrm{m}$ . The typical size of a measured fin was  $\sim\!50\times1.5\,\mu\mathrm{m}^2$ . IR measurements were taken at a base temperature of 50 °C. The emissivity of the fin surface of a typical 5-fin device was  $\sim\!0.301\pm0.0034$ , which is sufficient for quantitative thermal imaging.  $^{19}$  Further details of the emissivity measurement can be found in the supplemental information. Figure 3(a) shows an IR thermal image of a 5-fin FinFET with

**TABLE I.** List of FinFET device types and the corresponding design parameters varied in this study.

| Device type                                | $W_{fin}$ variation ( $\mu$ m) | S variation (μm) |

|--------------------------------------------|--------------------------------|------------------|

| Single-fin                                 | 0.2;0.3;0.4                    | N.A.             |

| 5-fin                                      | 0.3;0.4                        | 1.2;2.0; 3.0;5.0 |

| Multi-fin $(50 \times 50 \mu\text{m}^2)$   | 0.3;0.4                        | 1.2;2.0;3.0;5.0  |

| Multi-fin $(430 \times 340 \mu\text{m}^2)$ | 0.3                            | 2.0              |

FIG. 2. (a) Electrical output characteristics of a single-fin FinFET with  $W_{\rm fin}$  of  $0.3~\mu m$  (red lines) and  $0.4~\mu m$  (blue lines). (b) Transfer characteristics of single-fin devices with  $W_{\rm fin}=0.2,~0.3,~and~0.4~\mu m$ , for  $V_{\rm DS}=10~V$ . (c) Output characteristics of 5-fin devices ( $W_{\rm fin}=0.3~\mu m$ ;  $S=3~\mu m$ ) obtained from measurement and simulation results. Solid lines are from measurements and dashed lines represent simulation results. Current density is calculated by normalizing to the  $n^+$  source area. 20

$W_{fin} = 0.4 \,\mu m$  and  $S = 3 \,\mu m$  [similar to the device structure in Fig. 1(b)] under  $V_{GS} = 3 \,V$  and a power dissipation level of 50 mW, which corresponds to an aerial power density of 7.1 kW/cm<sup>2</sup> (normalized with respect to the total area of the active region).

An electro-thermal FinFET model was constructed that couples a 2D technology computer aided design (TCAD) electrical model (Synopsys Sentaurus) with a 3D finite element thermal model (COMSOL Multiphysics). The motivation behind the coupled model lies in the importance of accurately capturing both the electronic transport processes that dictate the Joule heat generated in the devices, and the thermal transport processes across/through the 3D device structure that determines the internal temperature distribution. Details of this multi-physics modeling scheme can be found in our previous

work.  $^{13,24,25}$  In the electrical model, temperature dependent electronic properties available in the literature (electron mobility, bandgap energy, etc.) $^{20,26-28}$  were used as modeling inputs. The  $\rm Al_2O_3/Ga_2O_3$  interface trap density was adjusted to calibrate the simulated I-V characteristics. Temperature dependent thermal properties from the literature were used in the 3D thermal model.  $^{9,29-31}$  Further details of the electro-thermal model and the coupling method can be found in the supplementary material.

Electrical output characteristics obtained from the coupled electro-thermal simulation and experiments are in close agreement, as shown in Fig. 2(c). The Joule heat distribution in a 5-fin FinFET (W $_{\rm fin}=0.3~\mu{\rm m}$  and S=2  $\mu{\rm m}$ ) under a power density condition of  $10.5~{\rm kW/cm^2}$  and  $V_{\rm GS}=3~{\rm V}$  calculated by the electro-thermal model

FIG. 3. (a) Top-view infrared (IR) thermal image of a 5-fin device ( $W_{\text{fin}}=0.4~\mu\text{m};~S=3~\mu\text{m}$ ). (b) Joule heat distribution of a 5-fin device obtained from electro-thermal simulation. (c) Current density distribution in the 5-fin FinFET. (d) Electric field distribution across the 5-fin FinFET. All simulation results shown here were performed under  $P=50~\text{mW},~V_{\text{GS}}=3\text{V},~\text{with}~W_{\text{fin}}=0.3~\mu\text{m}~\text{and}~S=3~\mu\text{m}$ . (e) The surface temperature rise of single-fin ( $W_{\text{fin}}=0.4~\mu\text{m}$ ), 5-fin ( $W_{\text{fin}}=0.4~\mu\text{m};~S=5~\mu\text{m}$ ), and multi-fin devices with  $50~\times50~\mu\text{m}^2$  ( $W_{\text{fin}}=0.4~\mu\text{m};~S=5~\mu\text{m}$ ) and  $430~\times342~\mu\text{m}^2$  ( $W_{\text{fin}}=0.3~\mu\text{m};~S=2~\mu\text{m}$ ) device area, obtained from IR thermography. The power density for the single and 5-fin devices was calculated by normalizing the power with respect to the  $n^+$  source area. For the multi-fin devices, a total area of  $430~\times340~\text{and}~50~\times50~\mu\text{m}^2$  was used.

is shown in Fig. 3(b). The generated heat was observed to be concentrated near the bottom of the fin channels. The spatial distribution of Q'''(x,y) is determined by the distributions of the current density [Fig. 3(c)] and the electric field within the device active region [Fig. 3(d)].

Converting the current density (Fig. 2) into total current, the current flowing through devices with  $W_{fin}$  increases by  ${\sim}14{\times}$  when they are converted from a single-fin to a 5-fin device with  $S = 3 \mu m$ , and by  $37 \times$  for a  $50 \times 50 \,\mu\text{m}^2$  scaled device. However, the increase in current comes at the expense of a substantially increased thermal load. For example, Fig. 3(e) compares the IR-measured peak temperature rise  $(\Delta T)$  of single-fin device, 5-fin device, and multi-fin devices with active areas of  $50 \times 50$  and  $430 \times 342 \,\mu\text{m}^2$  for varying power dissipation levels. It is to be noted that  $\Delta T$  measured by IR thermography may underestimate the true peak temperature of the devices due to the limited spatial resolution of the technique. However, the 3D electrothermal model can be used to confirm the average surface temperature measured by IR and predict the device peak temperature rise. For the large-area scaled devices, the  $\Delta T$  is  $\sim 2 \times$  for the  $50 \times 50 \,\mu\text{m}^2$  active area device as compared to the 5-fin FinFET (active area of  $\sim$ 1100  $\mu$ m<sup>2</sup>). For scaled devices with an active area of 430  $\times$  342  $\mu$ m<sup>2</sup>, the  $\Delta T$  is  $\sim 40 \times$  as compared to the 5-fin FinFET. This aggravated self-heating effect is caused by the thermal crosstalk among adjacent fins, which impedes the heat flow away from the center of the device, owing to adiabatic boundary conditions forming at the planes of symmetry between the fins. This undesired effect significantly increases the peak temperature of multi-fin devices over single-fin devices under identical power density conditions.

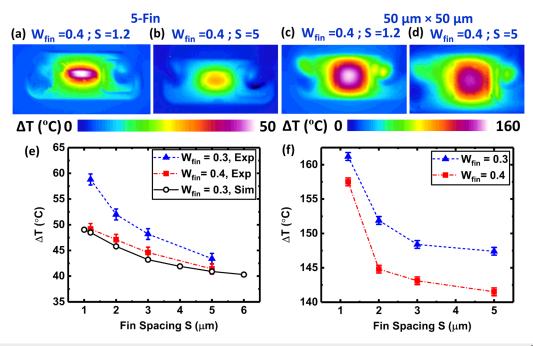

Effects of fin design variables (Wfin and S) on the device electrical performance have been discussed in our prior work.<sup>20</sup> While increasing W<sub>fin</sub> and S reduces the device on-resistance (R<sub>on</sub>), a larger fin area ratio (W<sub>fin</sub>/S) results in a lower specific on-resistance (R<sub>on-sp</sub>).<sup>20</sup> From a thermal perspective (Fig. 4), increasing S and  $W_{\rm fin}$  should reduce ΔT. Figures 4(a) and 4(b) show IR thermography images for 5-fin devices (W<sub>fin</sub> =  $0.4 \mu m$ ) with S of 1.2 (hotter) and 5  $\mu m$  (colder) for a power dissipation level of 50 mW, under  $V_{GS} = 3 \text{ V}$ . Figures 4(c) and 4(d) show IR thermography images for scaled devices with an active area of  $50 \times 50 \ \mu\text{m}^2$  ( $W_{\text{fin}} = 0.4 \ \mu\text{m}$ ) with S of 1.2 and 5  $\mu\text{m}$ . Figure 4(e) summarizes the measured  $\Delta T$  obtained from infrared thermal imaging for 5-fin devices. By increasing S from 1.2 to 5  $\mu$ m, the device thermal resistance (R<sub>th</sub>) of FinFETs with  $W_{fin} = 0.3$  and  $0.4 \,\mu m$ reduces by ~26% and 16%, respectively. For scaled devices with an active area of  $50 \times 50 \,\mu\text{m}^2$ , the effect of S (i.e., decrease in  $\Delta T$  with an increase in S) saturates faster than the 5-fin device case. For example, for the case of  $W_{fin} = 0.3 \,\mu m$ , there is 17% reduction in  $\Delta T$  for a 5-fin device as the fin spacing increases from 2 to  $5 \mu m$ , whereas for the  $50 \times 50 \,\mu\text{m}^2$  area device, the corresponding reduction in temperature is only  $\sim$ 3%. The 3D coupled electro-thermal model was used to calculate the  $\Delta T$  of 5-fin devices with intermediate values of S. As shown in Fig. 4(e), for the 5-fin FinFETs, the effect of increasing S diminishes rapidly for  $S \ge 4 \mu m$ , which corroborates with the experimental data discussed above.

Due to the strong anisotropy associated with a monoclinic crystal structure,  $^9$  the  $\kappa$  of  $\beta$ -phase  $Ga_2O_3$  can vary from  $\sim\!10.9$  W/m K in the [100] direction to  $\sim\!27$  W/m K in the [010] direction under 300 K temperature conditions.  $^{13}$  Consequently, the thermal performance of any

FIG. 4. Infrared (IR) thermal image of (a) 5-fin device with  $W_{\rm fin}=0.4~\mu\text{m}$ ,  $S=1.2~\mu\text{m}$ ; (b) 5-fin device with  $W_{\rm fin}=0.4~\mu\text{m}$ ,  $S=5.0~\mu\text{m}$ ; (c)  $50\times50~\mu\text{m}^2$  area device with  $W_{\rm fin}=0.4~\mu\text{m}$ ,  $S=5.0~\mu\text{m}$ . (e) Effect of fin spacing ( $S=1.2, 2.0, 3.0, \text{ and } 5.0~\mu\text{m}$ ) and fin width ( $W_{\rm fin}=0.3~\mu\text{m}$ ) and  $0.4~\mu\text{m}$ ) on device  $\Delta T$  from IR thermal imaging 5-fin FinFETs. Spatially averaged temperature rise determined from 3D electro-thermal simulation is also shown in the figure. (f) Variation of  $\Delta T$  for a  $50\times50~\mu\text{m}^2$  area devices with  $S=1.2, 2.0, 3.0, \text{ and } 5.0~\mu\text{m}$  and  $W_{\rm fin}=0.3~\mu\text{m}$  and  $W_{\rm fin}=0.3~\mu\text{m}$  acquired by IR thermal imaging. All results shown here were obtained at the power dissipation level of 50 mW and  $V_{\rm GS}=3~V$ .

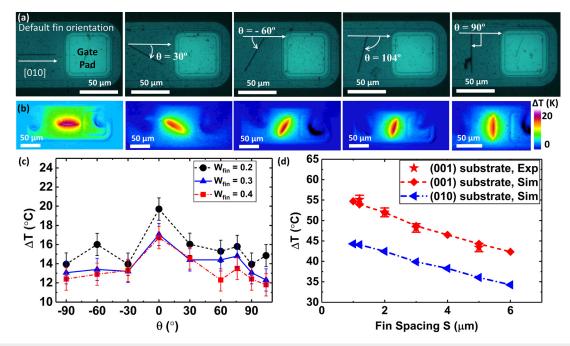

Ga<sub>2</sub>O<sub>3</sub> based electronic device is affected by the substrate orientation. The impact of crystal orientation on the heat dissipation and maximum forward current in Ga<sub>2</sub>O<sub>3</sub> vertical rectifiers has been recently reported by Xian et al. 32 To study the effect of the anisotropic  $\kappa$  and the orientation of the device layout on the FinFET thermal performance, single-fin devices were fabricated where the fin channels were rotated at different angles with respect to the baseline configuration. Figure 5(a) shows exemplar devices, and they were characterized using IR thermography [Fig. 5(b)]. Here,  $\theta$  denotes the angle between the direction along the fin channel length and [010] [Figs. 1(e) and 5(a)]. ΔT obtained from IR thermography for all the measured devices is summarized in Fig. 5(c).  $\Delta T$  in the FinFET devices was measured to be the lowest for the orientation with  $\theta = 90^{\circ}$ . There was a 30% reduction in  $\Delta T$  for the design with  $\theta = 90^{\circ}$  as compared to the baseline design of  $\theta = 0^{\circ}$ . This is because for  $\theta = 90^{\circ}$ , the fin width is along the [010] direction [ $\kappa$ (300 K) = 27 W/m K], thereby facilitating efficient heat transfer from the fin channels because of its higher  $\kappa$  as compared to the [100] orientation of the baseline case  $(\theta = 0^{\circ})$  [ $\kappa$ (300 K) = 10.9 W/m K]. 13 However, the change in the fin alignment impacts both V<sub>th</sub> and the saturated drain current (<sup>I</sup>D,Sat), as shown in our previous work.  $^{20}$  For the  $\theta \! = \! 90^{\circ}$  design, the  $V_{th}$  was observed to be the highest and I<sub>D,Sat</sub> was lowest among the tested devices with different fin orientation. The lowest V<sub>th</sub> and highest I<sub>D,Sat</sub> were observed for the device with  $\theta = 0^{\circ}$ .

Finally, the overall  $R_{th}$  of the device can be reduced by employing a substrate with a higher cross-plane  $\kappa$ .<sup>13</sup> The electro-thermal model was used to compare the  $\Delta T$  of the tested devices employing a (001)-oriented substrate as well as hypothetical devices fabricated on a

(010)-oriented substrate. The  $\Delta T$  measured via IR thermography and those predicted by the electro-thermal model show excellent agreement as shown in Fig. 5(d). This model was then used to predict the effect of substrate orientation on 5-fin FETs with various S values, as shown in the blue curve of Fig. 5(d). It should be noted that for all case studies involving different S, the R<sub>th</sub> of devices fabricated on a (010) substrate was lower than that for devices fabricated on a (001) substrate by 19% (for W<sub>fin</sub> = 0.3  $\mu$ m) and 25% (for W<sub>fin</sub> = 0.4  $\mu$ m, shown in the supplementary material).

An experimental study was performed on homoepitaxial Ga<sub>2</sub>O<sub>3</sub> FinFETs fabricated on a (001)-oriented substrate to identify key design parameters that impact the device thermal performance. For single-fin devices, increasing the fin width (Wfin) reduces the device Ron, which in turn negatively shifts the  $V_{th}$  and reduces the temperature rise ( $\Delta T$ ). While increasing the fin spacing (S) increases the device R<sub>on-sp</sub> and footprint, it reduces the  $\Delta T$ . For the 5-fin and the scaled multi-fin devices, it was found that increasing S results in a remarkable reduction in  $\Delta T$  (up to  $S = 3 \mu m$ ). As FinFETs are expanded to larger area scaled devices (50  $\times$  50, 430  $\times$  340  $\mu$ m<sup>2</sup>),  $\Delta$ T can increase by  $\sim$ 2 $\times$  and  $\sim$ 40×, respectively, as compared to 5-fin devices operating at an identical areal power density. To understand the effect of the anisotropic  $\kappa$ of Ga<sub>2</sub>O<sub>3</sub> on the self-heating behavior of FinFETs, devices with different fin channel orientations were fabricated and characterized via IR thermography. It was observed that for an orientation where the fin channel is rotated by 90° with respect to a baseline configuration (where the fin channel is oriented along the [010] orientation), the  $\Delta T$ reduces by  $\sim$ 30%. 3D electro-thermal simulation also showed that the device  $R_{th}$  can be reduced by  $\sim\!20\%$  if FinFETs are fabricated on a

**FIG. 5.** (a) Plan-view optical image of single-fin devices with  $\theta=0^\circ$ ,  $\theta=30^\circ$ ,  $\theta=-60^\circ$ , and  $\theta=90^\circ$ . (b) IR thermal image of each of these devices cooperating under a power dissipation level of 50 mW, V<sub>GS</sub> = 5 V. (c) Summary of the effect of device orientation for single-fin FETs for various W<sub>fin</sub> FinFETs on a 001-oriented substrate. IR measurements were done under a power dissipation level of 50 mW and V<sub>GS</sub> = 5 V. (d) Effect of substrate orientation on device  $\Delta$ T demonstrated by electro-thermal modeling of 5-fin FinFETs, with varying S, for W<sub>fin</sub> = 0.3 μm and a fin orientation of  $\theta=0^\circ$ . All simulations were performed at a power dissipation level of 50 mW for V<sub>GS</sub> = 3 V. IR thermography results are shown for the baseline configuration of the (001) substrate.

(010)-oriented  $Ga_2O_3$  substrate instead of a (001) substrate on which test structures were built. Along with the thermally aware device layout design, device-level thermal management solutions will be necessary to further reduce  $R_{th}$  to a manageable level. For vertically configured devices, top-side cooling solutions, such as flip-chip integration on a high thermal conductivity carrier wafer, will be preferred over bottom-side heat extraction methods, such as integration with a high  $\kappa$  substrate.  $^{10,11,13,33,34}$

See the supplementary material for more detailed discussions on the electro-thermal modeling, infrared thermography experiments, and the substrate orientation effect on the device self-heating for  $W_{\rm fin} = 0.4 \ \mu \rm m$ .

Funding for this work was provided by the AFOSR Young Investigator Program (Grant No. FA9550-17-1-0141, Program Officers: Dr. Brett Pokines and Dr. Michael Kendra, also monitored by Dr. Kenneth Goretta) and NSF (CBET-1934482, Program Director: Dr. Ying Sun). All the device fabrication work was supported by the AFOSR/Cornell Center of Excellence (Grant No. FA9550-18-1-0529, Program Officer: Dr. Ali Sayir) and AFOSR Grant No. FA9550-20-1-0148 (Program Officer: Dr. Kenneth Goretta), using CNF and CCMR Shared Facilities sponsored by the NSF NNCI program (No. ECCS-1542081), MRSEC program (No. DMR-1719875), and MRI (No. DMR-1338010).

#### **DATA AVAILABILITY**

The data that support the findings of this study are available from the corresponding author upon reasonable request.

### REFERENCES

- <sup>1</sup>H. H. Tippins, Phys. Rev. **140**, A316 (1965).

- <sup>2</sup>M. Orita, H. Ohta, M. Hirano, and H. Hosono, Appl. Phys. Lett. 77, 4166 (2000).

- <sup>3</sup>K. D. Chabak, D. E. Walker, A. J. Green, A. Crespo, M. Lindquist, K. Leedy, S. Tetlak, R. Gilbert, N. A. Moser, and G. Jessen, in 2018 IEEE MTT-S International Microwave Workshop Series on Advanced Materials and Processes for RF THz Applications IMWS-AMP 2018 (IEEE, 2018), pp. 1–3.

- <sup>4</sup>M. Baldini, Z. Galazka, and G. Wagner, Mater. Sci. Semicond. Process. 78, 132 (2018).

- <sup>5</sup>Y. Tomm, P. Reiche, D. Klimm, and T. Fukuda, J. Cryst. Growth **220**, 510 (2000).

- <sup>6</sup>Z. Galazka, K. Irmscher, R. Uecker, R. Bertram, M. Pietsch, A. Kwasniewski, M. Naumann, T. Schulz, R. Schewski, D. Klimm, and M. Bickermann, J. Cryst. Growth 404, 184 (2014).

- <sup>7</sup>E. G. Villora, K. Shimamura, Y. Yoshikawa, K. Aoki, and N. Ichinose, J. Cryst. Growth 270, 420 (2004).

- <sup>8</sup>H. Aida, K. Nishiguchi, H. Takeda, N. Aota, K. Sunakawa, and Y. Yaguchi, Jpn. J. Appl. Phys., Part 1 47, 8506 (2008).

- <sup>9</sup>Z. Guo, A. Verma, X. Wu, F. Sun, A. Hickman, T. Masui, A. Kuramata, M. Higashiwaki, D. Jena, and T. Luo, Appl. Phys. Lett. 106, 111909 (2015).

- <sup>10</sup>B. Chatterjee, K. Zeng, C. D. Nordquist, U. Singisetti, and S. Choi, IEEE Trans. Compon., Packag, Manuf. Technol. 9, 2352 (2019).

- <sup>11</sup>R. H. Montgomery, Y. Zhang, C. Yuan, S. Kim, J. Shi, T. Itoh, A. Mauze, S. Kumar, J. Speck, and S. Graham, J. Appl. Phys. **129**, 085301 (2021).

- <sup>12</sup>B. Chatterjee, D. Ji, A. Agarwal, S. H. Chan, S. Chowdhury, and S. Choi, IEEE Electron Device Lett. 42, 723 (2021).

- <sup>13</sup>B. Chatterjee, Y. Song, J. S. Lundh, Y. Zhang, Z. Xia, Z. Islam, J. Leach, C. McGray, P. Ranga, S. Krishnamoorthy, A. Haque, S. Rajan, and S. Choi, Appl. Phys. Lett. 117, 153501 (2020).

- <sup>14</sup>Y. Zhang, A. Neal, Z. Xia, C. Joishi, J. M. Johnson, Y. Zheng, S. Bajaj, M. Brenner, D. Dorsey, K. Chabak, G. Jessen, J. Hwang, S. Mou, J. P. Heremans, and S. Rajan, Appl. Phys. Lett. 112, 173502 (2018).

- <sup>15</sup>M. H. Wong, K. Goto, A. Kuramata, S. Yamakoshi, H. Murakami, Y. Kumagai, and M. Higashiwaki, in 2017 75th Annual Device Research Conference (IEEE, 2017), pp. 1–2.

- <sup>16</sup>K. Sasaki, Q. T. Thieu, D. Wakimoto, Y. Koishikawa, A. Kuramata, and S. Yamakoshi, Appl. Phys. Express 10, 124201 (2017).

- <sup>17</sup>Z. Hu, K. Nomoto, W. Li, L. J. Zhang, J. Shin, N. Tanen, T. Nakamura, D. Jena, and H. G. Xing, in 2017 75th Annual Device Research Conference (IEEE, 2017), pp. 1–2.

- pp. 1–2.

18Z. Hu, K. Nomoto, W. Li, R. Jinno, T. Nakamura, D. Jena, and H. Xing, in Proceedings of International Symposium on Power Semiconductor Devices ICs (IEEE, 2019), p. 483.

- <sup>19</sup>Z. Hu, K. Nomoto, W. Li, Z. Zhang, N. Tanen, Q. T. Thieu, K. Sasaki, A. Kuramata, T. Nakamura, D. Jena, and H. G. Xing, Appl. Phys. Lett. 113, 122103 (2018).

- <sup>20</sup>W. Li, K. Nomoto, Z. Hu, T. Nakamura, D. Jena, and H. G. Xing, in International Electron Devices Meeting (IEDM), Technical Digest (IEEE, 2019), p. 270.

- <sup>22</sup>J. Dallas, G. Pavlidis, B. Chatterjee, J. S. Lundh, M. Ji, J. Kim, T. Kao, T. Detchprohm, R. D. Dupuis, S. Shen, S. Graham, and S. Choi, Appl. Phys. Lett. 112, 073503 (2018).

- 23B. Chatterjee, A. Jayawardena, E. Heller, D. W. Snyder, S. Dhar, and S. Choi, Rev. Sci. Instrum. 89, 114903 (2018).

- <sup>24</sup>B. Chatterjee, C. Dundar, T. E. Beechem, E. Heller, D. Kendig, H. Kim, N. Donmezer, and S. Choi, J. Appl. Phys. 127, 044502 (2020).

- <sup>25</sup>B. Chatterjee, J. S. Lundh, J. Dallas, H. Kim, and S. Choi, in *Proceedings of the 16th Intersociety Conference on Thermal and Thermomechanical Phenomena in Electronic Systems (ITherm 2017)* (IEEE, 2017), pp. 1247–1252.

- <sup>26</sup>Z. Xia, H. Xue, C. Joishi, J. McGlone, N. K. Kalarickal, S. H. Sohel, M. Brenner, A. Arehart, S. Ringel, S. Lodha, W. Lu, and S. Rajan, IEEE Electron Device Lett. 40, 1052 (2019).

- <sup>27</sup>Y. Zhang, C. Joishi, Z. Xia, M. Brenner, S. Lodha, and S. Rajan, Appl. Phys. Lett. 112, 233503 (2018).

- <sup>28</sup>S. Krishnamoorthy, Z. Xia, C. Joishi, Y. Zhang, J. McGlone, J. Johnson, M. Brenner, A. R. Arehart, J. Hwang, S. Lodha, and S. Rajan, Appl. Phys. Lett. 111, 023502 (2017).

- <sup>29</sup>M. Higashiwaki, K. Sasaki, H. Murakami, Y. Kumagai, A. Koukitu, A. Kuramata, T. Masui, and S. Yamakoshi, Semicond. Sci. Technol. 31, 034001 (2016).

- <sup>30</sup>M. Slomski, N. Blumenschein, P. P. Paskov, J. F. Muth, and T. Paskova, J. Appl. Phys. **121**, 235104 (2017).

- <sup>31</sup>P. Jiang, X. Qian, X. Li, and R. Yang, Appl. Phys. Lett. **113**, 232105 (2018).

- <sup>32</sup>M. Xian, C. Fares, F. Ren, Z. Islam, A. Haque, M. Tadjer, and S. J. Pearton, ECS J. Solid State Sci. Technol. 9, 035007 (2020).

- <sup>33</sup>S. Kim, Y. Zhang, C. Yuan, R. Montgomery, A. Mauze, J. Shi, E. Farzana, J. S. Speck, and S. Graham, IEEE Trans. Components, Packag. Manuf. Technol. 11, 1171 (2021).

- <sup>34</sup>C. Yuan, Y. Zhang, R. Montgomery, S. Kim, J. Shi, A. Mauze, T. Itoh, J. S. Speck, and S. Graham, J. Appl. Phys. **127**, 154502 (2020).