# The effectiveness of heat extraction by the drain metal contact of β-Ga<sub>2</sub>O<sub>3</sub> MOSFETs

Samuel H. Kim<sup>1</sup>, Daniel Shoemaker<sup>2</sup>, Bikramjit Chatterjee<sup>2</sup>, Kelson D. Chabak<sup>3</sup>, Andrew J. Green<sup>3</sup>, Kyle J.

Liddy<sup>3</sup>, Gregg H. Jessen<sup>3</sup>, Samuel Graham<sup>1</sup>, and Sukwon Choi<sup>2,\*</sup> <sup>1</sup>Georgia Institute of Technology, Atlanta, GA 30332 <sup>2</sup>The Pennsylvania State University, University Park, PA 16802

<sup>3</sup>Air Force Research Laboratory, Dayton, OH 45433

\*Email: sukwon.choi@psu.edu

Abstract — Beta-phase gallium oxide ( $\beta$ -Ga<sub>2</sub>O<sub>3</sub>) has garnered considerable attention for power devices due to (i) its large critical electric field strength and (ii) the availability of low cost/high quality melt-grown substrates, both of which are advantages over silicon carbide (SiC) and gallium nitride (GaN). However, because of the low thermal conductivity of β-Ga<sub>2</sub>O<sub>3</sub>, thermal management strategies at the device-level are required to achieve high-power operation. In this work, electrically identical MOSFETs (fixed current channel length) with varying spacings between the gate electrode and drain metal contact (thus, thermally different) have been fabricated, to study the effectiveness of heat extraction by the drain metal electrode. Results show that the topside features of lateral β-Ga<sub>2</sub>O<sub>3</sub> MOSFETs are important in both electrical and thermal design perspectives.

Keywords—Electro-thermal modeling, gallium oxide (Ga2O3), infrared thermal microscopy, MOSFET, Raman spectroscopy, selfheating, thermal management

# I. INTRODUCTION

$\beta$ -type gallium oxide ( $\beta$ -Ga<sub>2</sub>O<sub>3</sub>) is an ultra-wide bandgap (UWBG) semiconductor material known for its outstanding material properties that enables the realization of next generation power electronic devices. The large bandgap energy (4.6 eV -4.9 eV) and high breakdown electric field (8 MV/cm) lead to an outstanding Baliga's figure of merit (BFOM), which renders the material ideal for high-voltage/power switching devices as shown in Table 1 [1]–[4]. Among several polytypes of the Ga<sub>2</sub>O<sub>3</sub> materials system, the  $\beta$ -phase exhibits superior thermal and chemical stability. Recent work has demonstrated the development of depletion mode lateral metal-oxidesemiconductor field-effect transistors (MOSFETs), with high critical field strength (3.8 MV/cm [5]), high current density (600 mA/mm [6]), and high breakdown voltage (2.32 kV [7]).

However, there are two main shortcomings of β-Ga<sub>2</sub>O<sub>3</sub> devices that are often pointed out in discussions about the material's power device potential. First,  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> MOSFETs exhibit a high source access resistance (R<sub>S</sub>), reflected by a sheet resistance ( $R_{SH}$ ) in the k $\Omega$ /sq range, between the ungated region between source and gate [8]. This relatively high R<sub>S</sub> negatively impacts the device transconductance and drain-current density. Second,  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> possesses a very poor thermal conductivity compared to other wide band gap materials (e.g., GaN and SiC)

as shown in Table 1, and therefore,  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> MOSFETs suffer from device self-heating under nominal operating conditions [9]–[11]. Experimental studies show that the thermal conductivity of  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> is highly anisotropic, where values along different crystallographic directions of [010], [001], and [100] orientations fall in the range of 11 - 26 W/m-K at room temperature [12]. This range of thermal conductivities is an order of magnitude lower than those for SiC and GaN.

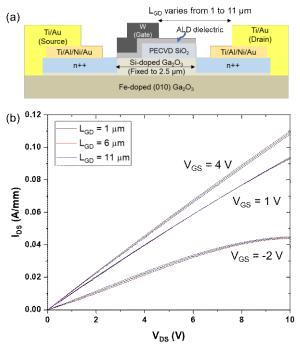

This work aims to address the critical thermal issues associated with  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> electronics. To study the effectiveness of heat extraction from the device active region by the drain metal contact, three sets of MOSFETs [8] were fabricated. The devices had an identical effective current channel length of 2.5 μm (i.e., the drain/source Si-implanted ohmic regions are 2.5 μm apart from each other as shown in Fig. 1 (a)); however, with the drain metal contact located 1, 6, and 11 µm away from the gate electrode (L<sub>GD</sub> in Fig. 1 (a)). In other words, we fabricated electrically identical, but thermally distinct MOSFETs, in terms of the distance between the gate edge and the heat-sinking drain metal electrode. This set of experiments will help to elucidate how contact metallization helps in the heat dissipation of devices made from  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> where challenges arise from device electrical and thermal resistances.

Table 1. Electronic and thermal properties of semiconductor materials.

| Material<br>Property                        | Si  | 4H-SiC | GaN | Ga <sub>2</sub> O <sub>3</sub>   |

|---------------------------------------------|-----|--------|-----|----------------------------------|

| Bandgap (eV)                                | 1.1 | 3.25   | 3.4 | 4.6 - 4.9                        |

| Breakdown field<br>(MV/cm)                  | 0.3 | 2.5    | 3.3 | 8                                |

| Normalized<br>BFOM                          | 1   | 320    | 860 | 1100 -<br>3250                   |

| Thermal<br>conductivity at<br>300 K (W/m-K) | 150 | 370    | 210 | 26 [010]<br>14 [001]<br>11 [100] |

### II. DEVICE DESCRIPTION

The device sample was prepared with a single 65 nm thick Si-doped β-Ga<sub>2</sub>O<sub>3</sub> homoepitaxial channel layer grown by metal organic vapor phase epitaxy (MOVPE) directly on a semiinsulating (010) Fe-doped substrate. The device fabrication process began by depositing 200 nm of SiO<sub>2</sub> by plasmaenhanced chemical vapor deposition to serve as the gate dielectric as well as an implant cap. Next, a tungsten (W) refractory metal layer was sputtered and patterned with a chromium (Cr) hard mask to define a 2.5 µm W/Cr gate electrode with SF<sub>6</sub> reactive ion etch (RIE) chemistry. A refractory metal gate is crucial to the self-aligned process because an Au-based gate metal stack would not survive at the required implant activation temperature of greater than 900 °C. Si-implant regions were then patterned with the source-side of the W/Cr gate ( $L_G = 0.5 \mu m$ ) exposed to eliminate the gatesource region ( $L_{GS} = 0 \mu m$ ), while the gate–drain distance ( $L_{GD}$ = 1, 6, 11 µm) remained. A shallow Si-implant profile was designed with 10 and 35 keV energies with a total dose of 1×10<sup>15</sup> ions cm<sup>-2</sup> to achieve a target doping concentration of  $1 \times 10^{20}$ cm<sup>-3</sup>. Activation of the Si-implant was achieved using a 900°C rapid thermal annealing process for 2 minutes in a nitrogen ambient. Following activation, Ti/Al/Ni/Au ohmic contacts were evaporated and annealed at 470°C for 1 min in a N<sub>2</sub> ambient after removing the implant cap with RIE. Electrical isolation was achieved with inductively coupled plasma/reactive ion etching. Fig. 1 (a) shows the device cross section schematic. Since the current channel length of all three devices are identical to 2.5 µm, the IV-characteristics are similar for these electrically identical but thermally distinct devices as shown in Fig. 1 (b).

Fig. 1 (a) Schematic of the metal-oxide-semiconductor field-effect transistors (MOSFETs). While effective current channel length is fixed at 2.5  $\mu$ m, L<sub>GD</sub> varies between 1 and 11  $\mu$ m. (b) I<sub>DS</sub>-V<sub>DS</sub> characteristics for V<sub>GS</sub> = -2, 1, 4 V, where the channel is fully opened at V<sub>GS</sub> = 4V.

# III. EXPERIMENTAL AND MODELING DETAILS

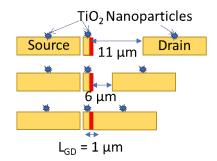

To qualitatively study the effectiveness of heat extraction by the drain metal contact, infrared (IR) thermal microscopy measurements were performed using a medium wavelength IR (MWIR) QFI InfraScope with a 15× MWIR objective on the three sets of devices operated under diverse power dissipation levels. The major advantage of IR thermography is the prompt measurement capabilities offering 2D temperature mapping of the entire field of view. However, the quality of the emissivity calibration and the lateral signal averaging due to the limited spatial resolution ( $\sim 3 \mu m$ ) restrict this technique to be useful only in a qualitative manner. To probe the channel surface temperatures in a quantitative manner, nanoparticle-assisted Raman thermometry was utilized [13], [14]. Nanoparticleassisted Raman thermometry was accomplished using a Horiba LabRAM HR Evolution spectrometer with 532 nm excitation. Measurements were performed in a 180° backscattering configuration with a long working distance 50× objective (NA = 0.45), where the spatial resolution is determined by the size of the sub-micrometer nanoparticles. To reduce the systematic error resulting from sources such as room temperature fluctuations, a reference mercury emission line at ~546 nm was used [15]. Anatase (TiO<sub>2</sub>) nanoparticles (99.98% purity) were selected due to high measurement sensitivity and excellent consistency among Raman temperature coefficients [13]. For the electrically identical, but thermally distinct MOSFETs, the temperature of the metal electrodes was measured to compare their self-heating behavior. Fig. 2 shows a schematic of the measurement locations for the three tested MOSFETs. All three devices share an identical heat generation profile (red region in Fig. 2), but the drain metal electrode is displaced at different distances from the heat source (or gate electrode). The nanoparticle temperature sensors were deposited on the drain and source metal electrodes as well as on the gate near the gate metal electrode on the drain side. The temperatures of these locations were then measured using Raman thermometry.

In order to validate and further understand the trends observed in the experiments, a 3D coupled electro-thermal model was constructed. This modeling scheme involves the creation of a technology computer aided design (TCAD) electrical model via Synopsys Sentaurus using the device geometries and electrical characteristics outlined in Fig. 1, and coupling it with a 3D finite element thermal model using COMSOL Multiphysics, as demonstrated in [13], [16], [17]. Furthermore, the temperature dependence as well as the anisotropy of the thermal conductivity of  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> [18] was reflected into the device model. The simulated surface temperatures were compared with the experimental results from nanoparticle-assisted Raman thermometry.

Fig. 2 Schematic of TiO<sub>2</sub> nanoparticles deposited on MOSFETs with three different gate-to-drain spacings ( $L_{GD}$ ). Since the distance between the Si-implanted ohmic regions are identical for all three MOSFETs, the heat generation profile (red rectangular in the image) is identical for the three transistors.

# IV. RESULTS AND DISCUSSION

Fig. 3 (a) shows qualitative IR thermal images of the three MOSFETs with different L<sub>GD</sub>. The temperature measurements were performed under a fully-open channel condition ( $V_{GS} = 4$ V) to avoid any bias dependency [19], and the power dissipation level was fixed at 0.8 W/mm. For the MOSFET with  $L_{GD} = 1$  $\mu$ m (left image from Fig. 3 (a)), since the drain metal electrode is closest to the channel (where the heat generation occurs as depicted in Fig. 2), the heat is more effectively transferred/spread out to the drain metal electrode, compared to the transistors with longer  $L_{GD}$ . However, for the  $L_{GD} = 6$  and 11 µm MOSFETs (middle and right image of Fig. 3 (a)), as the drain metal electrodes are located farther away from the heat generation region, the heat must primarily dissipate through the  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> layer and the source contacts. Therefore, more intense device self-heating occurs in these devices as compared to the MOSFET with  $L_{GD} = 1 \ \mu m$ . This effect results in a larger channel temperature rise as the drain contact moves further away from the heat generation region. Fig. 3 (b) shows the quantitative temperature rise of electrodes measured by nanoparticle-assisted Raman thermometry, along with simulation results. Since TiO<sub>2</sub> nanoparticles were deposited by drop-casting, not all of the measured nanoparticles were located on the center of the metal electrode as shown in Fig. 2. In addition, since the length of the gate is 0.5 µm, numerous nanoparticles were covering both the gate metal and the channel. Therefore, less than 5% disagreement between experiments and simulations can be caused by the uncontrollable deposition of the nanoparticles. The uncertainties were less than 1 °C for all Raman thermometry measurements.

Fig. 3 (a) Infrared thermography of three MOSFETs. (left:  $L_{GD} = 1 \ \mu m$ , middle:  $L_{GD} = 6 \ \mu m$ , right:  $L_{GD} = 11 \ \mu m$ ) (b) Temperature rise from Raman thermometry and 3-D fully coupled electro-thermal simulation. Temperature of the middle of the drain and source ohmic contact were measured.

Results in Fig. 3 (b) show that even though all three transistors exhibit identical heat generation profiles, the temperatures of the gate metal electrodes are different by a large

extent. The temperature rise of the gate electrode is the lowest for the device with the drain electrode closest to the gate ( $L_{GD}$  =  $1 \mu m$ ). However, the drain temperature is highest for this device because the heat more effectively spreads towards the drain metal contact. This trend observed in the Raman measurement results agree well with IR thermal images in that the drain ohmic contact of the transistor with  $L_{GD} = 1 \ \mu m$  facilitates dissipation of the thermal energy and reduces the temperature of the device channel region and gate electrode. There is negligible difference in the source electrode temperature, while there is  $\sim 35\%$ increase in the gate temperature rise when the drain metal electrode is located 10  $\mu$ m further away from the gate (L<sub>GD</sub> = 11 µm). The temperature rise of the drain ohmic contact of the transistor with  $L_{GD} = 1 \,\mu m$  is 52 °C, while that of the device with  $L_{GD} = 11 \ \mu m$  is 70 °C. When  $L_{GD} = 6 \ \mu m$ , the gate temperature rise increases by ~15% as compared to the case of  $L_{GD} = 1 \ \mu m$ . The temperature rise of the drain electrode of the  $L_{GD} = 1 \ \mu m$ MOSFET is ~10% higher compared to that of the  $L_{GD} = 6 \ \mu m$ MOSFET, and ~20% higher compared to that of the MOSFET with  $L_{GD} = 11 \ \mu m$ . These results show that metallic ohmic contact pads have a significant impact on the thermal performance of lateral transistor devices based on β-Ga<sub>2</sub>O<sub>3</sub>.

## V. CONCLUSION

In this study, electrically identical, but thermally different MOSFETs were fabricated to study the effectiveness of the heat extraction by the drain metal contact. It was proven that simply changing the distance between the drain ohmic contact pad and the heat generation region significantly impacts the device thermal performance, because of the low thermal conductivity of the base material. When the drain metal electrode is shifted by 10  $\mu$ m away from the gate electrode (L<sub>GD</sub> = 11  $\mu$ m), a ~35% increase in the gate temperature rise occurs as compared to a case of L<sub>GD</sub> = 1  $\mu$ m. For the case of L<sub>GD</sub> = 6  $\mu$ m, the gate temperature rise increases by about 15%, as compared to the baseline case of L<sub>GD</sub> = 1  $\mu$ m. These results demonstrate the design trade-off when optimizing both the device breakdown voltage and thermal performance of homoepitaxial lateral transistors based on  $\beta$ -Ga<sub>2</sub>O<sub>3</sub>.

#### ACKNOWLEDGMENT

This work was supported by the AFOSR Young Investigator Program (Grant No. FA9550-17-1-0141, Program Officers: Dr. Brett Pokines and Dr. Michael Kendra, also monitored by Dr. Kenneth Goretta) and the National Science Foundation under Grant No. CBET-1934482. This work was also supported by AFRL through KBR Wyle (Grant No. FA8075-14-D-0025)

# REFERENCES

- J. Y. Tsao et al., "Ultrawide-Bandgap Semiconductors: Research Opportunities and Challenges," Adv. Electron. Mater., vol. 4, no. 1, pp. 1–49, 2018.

- [2] M. Higashiwaki, K. Sasaki, A. Kuramata, T. Masui, and S. Yamakoshi, "Development of gallium oxide power devices," *Phys. Status Solidi Appl. Mater. Sci.*,

vol. 211, no. 1, pp. 21-26, 2014.

- [3] S. J. Pearton, F. Ren, M. Tadjer, and J. Kim, "Perspective: Ga2O3 for ultra-high power rectifiers and MOSFETS," J. Appl. Phys., vol. 124, no. 22, 2018.

- [4] M. Higashiwaki, H. Murakami, and Y. Kumagai, "State-of-the-art technologies of gallium oxide power devices Current status of Ga 2 O 3 power devices," J. Phys. D Appl. Phys. Masataka Higashiwaki al J. Phys. D Appl. Phys, vol. 50, 2017.

- [5] A. J. Green *et al.*, "3.8-MV/cm Breakdown Strength of MOVPE-Grown Sn-Doped β-Ga2O3 MOSFETs," *IEEE Electron Device Lett.*, vol. 37, no. 7, pp. 902–905, 2016.

- [6] H. Zhou, M. Si, S. Alghamdi, G. Qiu, L. Yang, and P. D. Ye, "High-Performance Depletion/Enhancement-ode \beta -Ga2O3 on Insulator (GOOI) Field-Effect Transistors with Record Drain Currents of 600/450 mA/mm," *IEEE Electron Device Lett.*, vol. 38, no. 1, pp. 103–106, 2017.

- [7] J. K. Mun, K. Cho, W. Chang, H.-W. Jung, and J. Do, "Editors' Choice—2.32 kV Breakdown Voltage Lateral β-Ga 2 O 3 MOSFETs with Source-Connected Field Plate," *ECS J. Solid State Sci. Technol.*, vol. 8, no. 7, pp. Q3079–Q3082, 2019.

- [8] K. J. Liddy *et al.*, "Thin channel β-Ga2O3 MOSFETs with self-aligned refractory metal gates," *Appl. Phys. Express*, vol. 12, no. 12, pp. 0–4, 2019.

- [9] J. S. Lundh *et al.*, "Device-Level Multidimensional Thermal Dynamics With Implications for Current and Future Wide Bandgap Electronics," *J. Electron. Packag.*, vol. 142, no. 3, May 2020.

- [10] B. Chatterjee *et al.*, "Electro-thermal co-design of β-(AlxGa1-x)2O3/Ga2O3 modulation doped field effect transistors," *Appl. Phys. Lett.*, vol. 117, no. 15, 2020.

- [11] B. Chatterjee, A. Jayawardena, E. Heller, D. W.

Snyder, S. Dhar, and S. Choi, "Thermal characterization of gallium oxide Schottky barrier diodes," *Rev. Sci. Instrum.*, vol. 89, no. 11, 2018.

- [12] M. Higashiwaki *et al.*, "Anisotropic thermal conductivity in single crystal β-gallium oxide," *Appl. Phys. Lett.*, vol. 106, no. 11, p. 111909, 2015.

- [13] J. Dallas *et al.*, "Thermal characterization of gallium nitride p-i-n diodes," *Appl. Phys. Lett.*, vol. 112, no. 7, 2018.

- [14] S. Choi, E. Heller, D. Dorsey, R. Vetury, and S. Graham, "The impact of mechanical stress on the degradation of AlGaN/GaN high electron mobility transistors," *J. Appl. Phys.*, vol. 114, no. 16, p. 164501, 2013.

- [15] J. S. Lundh *et al.*, "Multidimensional thermal analysis of an ultrawide bandgap AlGaN channel high electron mobility transistor," *Appl. Phys. Lett.*, vol. 115, no. 15, 2019.

- [16] B. Chatterjee, J. S. Lundh, J. Dallas, H. Kim, and S. Choi, "Electro-thermal reliability study of GaN high electron mobility transistors," *Proc. 16th Intersoc. Conf. Therm. Thermomechanical Phenom. Electron. Syst. ITherm 2017*, pp. 1247–1252, 2017.

- [17] B. Chatterjee *et al.*, "Nanoscale electro-thermal interactions in AlGaN/GaN high electron mobility transistors," *J. Appl. Phys.*, vol. 127, no. 4, 2020.

- [18] P. Jiang, X. Qian, X. Li, and R. Yang, "Threedimensional anisotropic thermal conductivity tensor of single crystalline β-Ga2O3," *Appl. Phys. Lett.*, vol. 113, no. 23, pp. 8–13, 2018.

- [19] S. Choi, E. R. Heller, D. Dorsey, R. Vetury, and S. Graham, "The impact of bias conditions on self-heating in AlGaN/GaN HEMTs," *IEEE Trans. Electron Devices*, vol. 60, no. 1, pp. 159–162, 2013.