# Signal Integrity Design Methodology for Package in Co-packaged Optics Based on Figure of Merit as Channel Operating Margin

Bo Pu

DeTooLIC Technology Co., Ltd

Ningbo, Zhejiang, China

bobpu@ieee.org

ORCID: 0000-0001-7084-2439

Jiayi He Cisco Systems, Inc. San Jose, CA, USA jiayihe@cisco.com Aaron Harmon

EMC Laboratory

Missouri University of Science and

Technology

Rolla, MO, USA

afhpq4@mst.edu

Yuandong Guo

EMC Laboratory

Missouri University of Science and

Technology

Rolla, MO, USA

ydggdd@mst.edu

Yuanzhuo Liu

EMC Laboratory

Missouri University of Science and

Technology

Rolla, MO, USA

liuyuanz@mst.edu

Qiangming Cai

(Corresponding Author)

Southwest University of Science and

Technology

Mianyang, Sichuan, China

qmcai@swust.edu.cn

Abstract— Optical engines co-packaged with switching Application-Specific Integrated Circuit (ASIC) can offer a solution for advancement in bandwidth requirement and are potentially the ultimate direction for the long-touted "optical integration" era. This paper proposes a novel signal integrity (SI) design methodology for package of co-packaged optics (CPO) by using channel operating margin (COM) as a figure of merit (FOM) for the first time. The conventional design method of SI based on individual criteria, such as masks for loss, crosstalk, jitter, eye width/height, impedance, etc., are no longer able to be satisfied at the same time for current high-speed signals up to 50Gbps and even over 100Gbps. COM, combining most of the individual criteria into a single value of signal to noise ratio, provides the possibility to estimate the quality of the channel and achieve a balance between performance and design complexity in the early design stage. In this work, a design methodology in a format of a visible map using the most two significant factors, loss, and crosstalk, to satisfy the required COM is discussed in detail. With this novel methodology, one can predict the SI performance of a package in the early design stage when the real layout has not generated yet for full-wave simulation and can avoid the costly iteration in the conventional design concept.

Keywords—channel operating margin (COM), co-packaged optics (CPO), design methodology, ethernet, figure of merit, high speed, insertion loss, integrated crosstalk noise (ICN), package design, signal integrity

### I. INTRODUCTION

Electronic packaging plays a significant role in electronic systems. Packaging not only provides a robust cover to ensure the reliability of integrated circuits (ICs) but also acts as a bridge between the silicon chip and the external printed circuit board (PCB). Further, the performance of the package greatly impacts the working capability of the whole electronic system. With the emergence of ever-increasing data rates and system density comes the need for higher bandwidth and lower latency signaling pathways i.e., data link. Examples of such links are communication between processors in a high-performance computer (HPC), and networks in a data center.

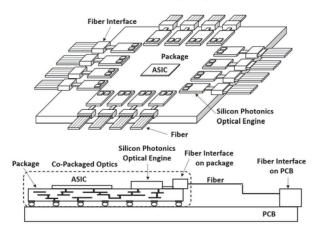

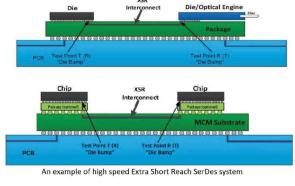

Fig. 1. An architecture of co-packaged optics and its implementation for Extra Short Reach (XSR) in Ethernet.

One signaling pathway that can address this need is copackaged optics (CPO).

CPO have been the focus of active research to overcome the bottleneck in ultra-high bandwidth and speed. CPO integrate optics and electronics to mitigate the thermal and power inefficiencies inherent in more conventional approaches to high-speed optoelectronics. This co-packaging of the silicon and optical connections allow for much shorter and higher density electrical lines than on-board optical modules [1]. An example of this co-packaging for the extra short reach (XSR) protocol is shown in Fig. 1. For CPO, the losses and crosstalk that happen in the package are as important as the losses and crosstalk that happen in the external channel [2]. Due to this, it is important to design a package/channel interface that meets the required signal integrity (SI) specification if one is to guarantee a high speed, low error rate transmission [3]. However, this is easier said than done as SI analysis for multichip packages can be quite complex. To address this complexity, design flows have been developed to help package designers better meet the SI requirements.

In [4] a design flow for System in Package (SiP) tracks that address those SI requirements from the beginning was presented. Further, systematic design flows that address concerns such as power integrity (PI) and electromagnetic immunity of components in the package along with SI were presented in [5]-[10]. Notably, these design flows only focus on the package and as data rates increase, designing packages that meet the SI and PI requirements along with other components is becoming a more serious challenge [11]-[13]. The design flow outlined in [14] adopts an advanced collaborative design for the die, package, and pin map to meet the SI requirements.

For data rates beyond the current state of the art, it may not be possible to generate a system design cost-effectively using fixed design margins. To this extent, a balanced strategy to determine the design margins for chip, package and the channel is attracting attention. This balanced strategy brings flexibility into the design of high-speed interconnects, and might consider a design path by using artificial intelligence. These machine-learning-based methods have been discussed in [15] and [16]. A prerequisite for these approaches, however, is a large number of training data sets and well trained neural network. This prerequisite makes these approaches ill-suited for the early stage of new design. Therefore, a forward predictable, minimally iterative, signal integrity design methodology is needed in the early stage of CPO and similar high-speed packages development.

To the best of our knowledge, the proposed design method based on figure of merit (FOM) as channel operating margin (COM) is the first SI design method for cpo, and it offers a straight forward and cost reduced approach. The novelty of this design flow is that the SI performance as COM value can be predicted directly with a given design margin such as loss and crosstalk, and does not require an iterative approach. Section II demonstrates the concept of COM in detail. The proposed design method is compared to the conventional method in Section III. In section IV a 112G XSR SerDes package with CPO is used to describe and validate the proposed method in detail. In section V a conclusion is ultimately achieved.

## II. CONCEPTION OF CHANNEL OPERATING MARGIN

COM was introduced as a FOM to evaluate the performance of signal propagation on a trace [17] and is defined by IEEE Std 802.3bjTM-2014 as normative means to judge the performance of a passive high-speed electrical channel [18]. COM is proposed to determine if the quality of the channel satisfies the SI requirement of the compliant transceiver. A ratio of the available signal amplitude  $A_8$  to the statistical noise amplitude  $A_n$  is described by COM as in (1).

$$COM = 20 \times \log_{10} \left( \frac{A_s}{A_n} \right) \tag{1}$$

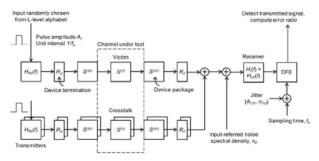

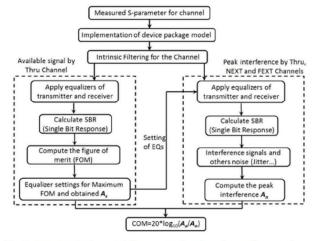

A flow chart for the derivation of COM that considers the characteristics of the Transmitter (Tx), Receiver (Rx), and the channel is described in detail [18] and depicted in Fig. 2. Calculation of COM starts with the characteristics of a channel. In this work scattering parameters (S-parameters) are defined to represent the channel characteristics. A detailed procedure for the computation of COM is listed in the following steps and Fig. 3.

Fig. 2. A flow chart to demonstrate the derivation of COM [17].

Fig. 3. A summarized computation process for channel operating margin.

Step 1: Extraction of the transfer function for the channel (S-parameter from Tx to Rx).

Step 2: To obtain the single-bit response for the transfer function by conversion from frequency to time domain.

Step 3: Optimize signal to noise ratio (SNR) as FOM determines best equalization settings and obtain the amplitude of the available signal as (2). Those factors at denominator are root mean square (RMS) noise of Tx, ISI, jitter converted voltage, coding voltage, and Rx, sesquentially.

$$FOM = 10 \times \log_{10} \left( \frac{A_s^2}{\sigma_{TX}^2 + \sigma_{ISI}^2 + \sigma_J^2 + \sigma_{XT}^2 + \sigma_N^2} \right)$$

(2)

Step 4: Implementing the channel interference, jitter, and other noise to get the amplitude of the statistical noise.

Step 5: COM is achieved as a SNR by (1).

Overall, COM is a convenient metric for channel design. COM provides a single-valued FOM to judge channel quality as opposed to more traditional metrics that are based on a wide range of specifications such as jitter, eye height and width, etc [19], [20]. Further COM can be calculated using a non-iterative approach thereby reducing the time and number of iterations needed for evaluation.

#### III. PROPOSED PACKAGE DESIGN METHODOLOGY

### A. Conventional Way of Package Design

The package of a device is where communication between the silicon and external devices takes place. Thusly, the performance of the package affects the performance of the device. For traditional package design, a diverse set of criteria

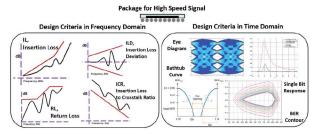

Fig. 4. Criteria of package design in frequency and time domains.

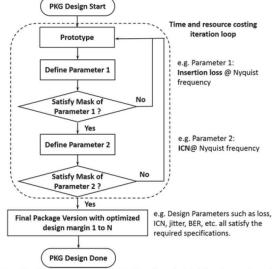

Fig. 5. Traditional package design flow based on trial and error iterations.

are used to evaluate the operating performance of a designed package. These specifications namely are insertion/return loss, insertion loss deviation, the insertion loss to crosstalk ratio in the frequency domain, the eye diagram, jitter, single-bit response, bathtub curve, and the bit error rate (BER) contour in the time domain as shown in Fig. 4.

The traditional design flow of the package follows an iterative trial and error approach to arrive at the pre-defined margins and final optimized goal [21]. The procedure is typically to design the prototype and then evaluate if the first design parameter, usually the loss, meets the defined margin. If it does, then move to the next step to check other design parameters such as crosstalk or one of the other above listed parameters. This method is shown in Fig. 5. The disadvantage of this traditional approach is that it requires a re-design when the package fails to meet a specification. This requirement to redesign once a singular metric is not met dramatically increases the turn-around time and cost of a project. In short, the more iterations needed the higher the turn-around time and cost associated with the design.

Moreover, unlike the traditional process of a package design, where a diverse set of specifications is met via iteration, the use of COM as a FOM makes it possible to establish a function, where the various design masks are used as the input data sets and COM is the output result. Designing a package using this COM as FOM method as opposed to the traditional method allows package designers to obtain the balance between design complexity and signal propagation performance.

For packages working at a relatively low data rate, where the issues of loss and crosstalk are not as serious, empirical guides on package design work well, and whole defined masks can easily be satisfied. However, the speed of current integrated circuits, for example, serial and parallel interfaces, can reach upwards of tens of gigabits per second (Gbps), and sometimes be above 100 Gbps. For these devices, it is not easy to satisfy all the criteria mentioned above. Further, efforts to satisfy these requirements using the traditional design approach typically result in excessive cost in both time and resources and still may result in an inefficient design. Moving forward a balanced design method that weighs both performance and design costs should be considered.

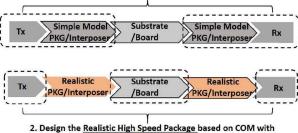

# B. Proposed Novel Design Methodology for Package Based on Channel Operating Margin

To design a COM based-on package the designer must first obtain the reference channel. The channel is considered as all interconnects and interfaces from the ball of the transmitter's package to the ball of the receiver's package, refer to as ball-to-ball. Such interconnects and interfaces could be the MCM substrate, PCB traces, connectors, and or cables. An example channel is shown in the upper of Fig. 6.

The reference ball-to-ball channel obtained must have a COM greater than or equal to 3 dB with pre-defined SerDes circuits and a standard package definition per IEEE 802.3. In particular, the pre-defined SerDes circuits include transmitter and receivers, and their characteristics such as differential peak voltage, modulation, jitter, functions of equalizers (FFE, CTLE and DFE) are built into the algorithm of COM caculation. The standardized channel indicates the ball to ball signal propagation trace, which should satisfy the 3dB COM requirement with pre-defined on-chip circuits and package in IEEE 802.3. It varies with protocol and here is based on XSR.

1. Obtain the Reference Channel Satisfying COM ≥ 3 dB from Vendor or generate reference channel based on Simple Tx/Rx and Package Models

Defined in IEEE 802.3

Pre-defined Tx/Rx and Reference Channel

Fig. 6. A flow to design the package based on COM for high speed extra short reach (XSR) SerDes system as shown in the upper part of figure [2].

If a reference ball-to-ball channel is not obtainable one can be generated based upon the pre-defined Tx/Rx models and the standard package model defined in IEEE specification. The target package, which is used for a realistic scenario, is designed following the 2<sup>nd</sup> step of flow in Fig. 6 based on the reference channel and a criterion of a 3 dB COM value. Since the reference channel is derived in a condition when the COM equals 3 dB, per the pre-defined Tx/Rx and package, the designed package should have a similar or better performance than this pre-defined package.

After a reference channel is obtained the appropriate mask ranges must be defined. While there are many parameters used to quantify the performance of signal propagation in a channel, insertion loss and ICN are the most dominant two factors. Due to this these parameters will be the primary focus for this work, however, this method is not limited to only these design parameters.

Insertion loss is widely understood by hardware engineers in regard to high-speed signal transmission while ICN is a relatively new factor. A channel's ICN has been widely used as an alternative to the insertion crosstalk ratio (ICR) for channel crosstalk evaluation in the IEEE 802.3ba standard [22]. The ICN represents the crosstalk as a weighted sum of crosstalk noise in the frequency domain with respect to the power spectrum of the signal being transferred [23]. The total ICN can be calculated using the near-end and far-end ICN as shown in (3).

$$\sigma_{x} = \sqrt{\sigma_{nx}^{2} + \sigma_{fx}^{2}} \tag{3}$$

The near-end or far-end ICN can be derived by the multidisturber near and far-end crosstalk loss MDNEXT/MDFEXT and weight function W for near or far end crosstalk as in (4) and (5). In (5) T is the aggressors 20% to 80% rise and fall time and  $f_r$  is the receivers -3 dB bandwidth.

$$\sigma_{(n/f)x} = \left(2\sum_{n} W_{(n/f)t}(f_n)10^{-MD(N/F)EXT_{loss}(f_n)/10}\right)^{1/2} (4)$$

$$W_{(n/f)t}(f) = A_{(n/f)t}^{2} \left( \Delta f / f_{b} \right) \operatorname{sinc}^{2} \left( f / f_{b} \right)$$

$$\cdot \left[ \frac{1}{1 + \left( f T_{(n/f)r} / 0.2365 \right)^{4}} \right] \left[ \frac{1}{1 + \left( f / f_{r} \right)^{8}} \right]^{(5)}$$

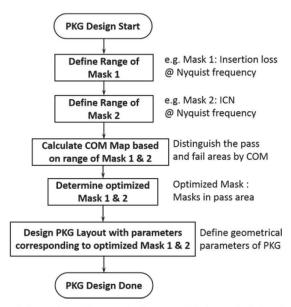

After the design mask ranges are defined the design guide map must be created. This may seem complicated while this map creation is rather straightforward as illustrated in Fig. 7. The design space is an *N*+1 dimensional structure consists of all *N* design masks and the COM result. As noted above these design masks can be based upon many parameters such as insertion loss, ICN, jitter, etc. The parameters for each of these masks are input into the COM function and the output COM is recorded. This is performed for all values in the predefined mask ranges. The resultant of this calculation is a set of COM values referenced to the *N*-dimensional design space.

With this resultant, it is easy to find the regions of each singular input design mask where the COM is greater than or equal to 3 dB. These regions are the optimized mask regions. Finally, the traditional package design can be performed using these optimized mask regions.

Fig. 7. A straight working flow for the proposed design method of package.

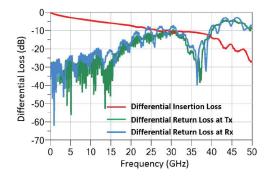

Fig. 8. Differential insertion and return loss of reference channel from the ball of the package at Tx to the ball of the package at Rx. (Sdd21=10.19dB@26.5625GHz)

After the design guide is created, straight forward design method is used for mask values that fall in this pass area. All values that are not in the pass areas must be disregarded by the design method. By only using mask values that satisfy the masks in the pass area the designer can avoid the high cost of trial and error iteration.

#### IV. CASE STUDY AND VALIDATION OF PROPOSED METHOD

# A. Demonstration of Proposed Method In a Case Study

A reference channel for XSR interconnects is provided by the IEEE 802.3 task force working group and is used to establish the whole signal propagation trace. The differential insertion, and return losses at ball side of Tx/Rx package for this reference channel are shown in Fig. 8. At the Nyquist frequency of a 112Gbps PAM4 signal, 26.5625GHz, the losses are -10.19dB, -11.85dB, and -8.759dB for above mentioned losses respectively from Fig. 8.

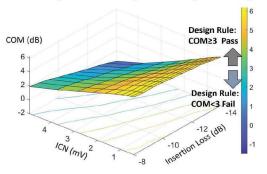

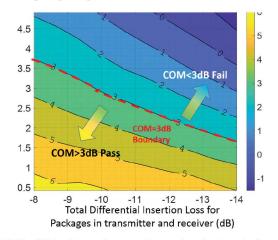

The possible range of differential insertion loss for each package implemented in the 112G PAM4 signal propagation is defined as 10 values from -7dB to -4dB. The total ICN to represent the levels of crosstalk varies from 0.4mV to 5mV as well in an array of 10 numbers, which are close to the predicted trend by the IEEE 802.3 working group. Corresponding results of COM are ultimately calculated, and then the COM map is expressed as a 3D surface as illustrated

in Fig. 9, and a contour type as shown in Fig. 10 to observe the relationship between the COM and the corresponding values of loss and crosstalk. The range to pass or fail with the required design criterion, where COM equals 3dB, is obvious in the map derived by using the proposed design methodology. Related insertion loss and crosstalk levels are easily seen as well. This map provides a clear direction and straight forward approaches to appropriately determine the loss and crosstalk margins in the early stage when there is no layout or schematic for performance extraction.

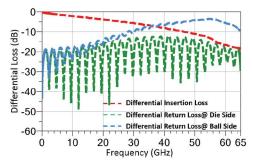

#### B. Validation by Realistic Package

A validation case based on the realistic package model from the IEEE 802.3 working group to investigate the accuracy of the proposed design method for the package will be discussed in this sub-section. The differential insertion loss and return loss at both the die and ball sides are shown in Fig. 11. At the Nyquist frequency of a 112Gbps PAM4 signal defined by IEEE specification, 26.5625GHz, the differential insertion loss is indicated to be -4.98dB. The S-parameters representing the loss and crosstalk for the real package that this validations reference channel is based upon were used to calculate the real values of COM. The corresponding insertion loss and ICN for the calculation are -9.96dB and 2.86mV.

From these values, a real-world COM of 2.91 with corresponding 11.030mV of EH (eye height), 10.440dB of VEC (normalized vertical eye opening) and 13.116 dB of ERL (effective return loss) were calculated. Main values are summarized in TABLE I. Here the EH is less than the minimum required EH as 15mV, an enhancement of EH is required in the optimization stage for final system margin.

Fig. 9. The COM guide map in a type of 3D surface based on insertion loss and ICN for package design.

Fig. 10. The COM guide map in a type of contour based on insertion loss and ICN for package design.

TABLE I. CHARACTERISTICS AND COM VALUE OF PACKAGE IMPLEMENTED FOR VALIDATION

| Nyquist Frequency for 112G (GHz)        | 26.5625     |

|-----------------------------------------|-------------|

| ICN (mV)                                | 2.86        |

| Total Insertion Loss (dB)               | 20.76       |

| Total PKG insertion Loss (dB)           | 9.96        |

| COM from Real Package Model (dB)        | 2.91        |

| COM Predicted by Method in Fig. 10 (dB) | 3.00 ~ 3.05 |

| Maximum Error Rate                      | 4.81%       |

Fig. 11. Differential insertion and return loss of realistic package from IEEE 802.3 working group. (<u>Sdd21=-4.98dB@26.5625GHz</u>)

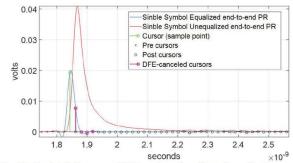

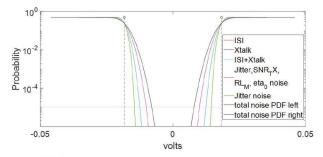

Fig. 12. Single Bit Response (SBR) to show the effect of equalization.

Fig. 13. The bathtub figure to distinguish the noises clearly.

Single bit response and bathtub to demonstrate the effect of equalization and noises are also illustrated in Fig. 12 and Fig. 13, respectively.

The crossing point of the insertion loss and ICN values indicated a predicted COM between 3.00 and 3.05. The real world calculated values is 2.91 resulting in a less than a 5% error rate between the predicted and calculated COM for the realistic package. More importantly, this proposed method only requires the level of loss and crosstalk at the Nyquist frequency. The proposed method does not require an existing layout, schematic, or S-parameter model. This method is completely different from the traditional method of package design, and offers a fast but accurate guide for package design

in the early stage of development. At the same time, the predicted value is an underestimation. When compared to the COM calculated for the real package response, the 5% error could be caused by the impedance mismatching, random jitter, and other interference which are not able to be estimated without a final design. Therefore, in the real design, we can add a margin of 10% to the COM predicted by the design guide map to compensate for the potential degradation of the COM from those additional factors. In general, the proposed method can be used not only for CPO, where the value of COM is predefined for XSR interconnects but also can be extended to other high-speed interconnects with a defined FOM.

#### V. CONCLUSION

In this paper, a novel SI design methodology is proposed for package design in co-packaged optics. The method is based on channel operating margin, as a figure of merit, and considers various criteria. An demonstration of the method is given using the two most dominant package performance design parameters, insertion loss, and integrated crosstalk noise. The relationship between these dominant parameters and the corresponding COM values was established via a 3D or contour map for an easy determination. To validate the proposed method a example for a 112Gbps PAM4 signal reference channel was presented and compared to a realistic package presented by IEEE 802.3 working group. Less than a 5% maximum error rate was observed between the values predicted by the proposed model and the actual values calculated for the real package. Ultimately a margin of 10% to compensate unpredictable factors in early design stage was suggested in the proposed methodology. Especially, there is no requirement for the layout, schematic or S-parameter while only need the level of loss and crosstalk at the Nyquist frequency to estimate the design margin of package. Different from traditional method of package design, the proposed one obviously can offer a fast but accurate guide in the early design stage of development where these data set may not be available. Finally, the proposed method for co-packaged optics, where the value of COM is predefined for XSR interconnects, can also be extended to other channel design once a figure of merit like COM can be defined.

#### REFERENCES

- Y. Taira, "Technology for Optical Co-Packaging," 2020 Pan Pacific Microelectronics Symposium (Pan Pacific), HI, USA, 2020, pp. 1-6

- [2] IEEE Std 802.3ck-2018 IEEE Standard for 100 Gb/s, 200 Gb/s, and 400 Gb/s Electrical Interfaces Task Force.

- [3] Y. Liu et al., "S-Parameter De-Embedding Error Estimation Based on the Statistical Circuit Models of Fixtures," in IEEE Transactions on Electromagnetic Compatibility, vol. 62, no. 4, pp. 1459-1467, Aug. 2020, doi: 10.1109/TEMC.2020.2992553.

- [4] P. Pulici et al., "Signal Integrity Flow for System-in-Package and Package-on-Package Devices," in Proceedings of the IEEE, vol. 97, no. 1, pp. 84-95, Jan. 2009.

- [5] H. Chuang et al., "Signal/power integrity design strategy for low-cost package of high-speed memory I/O interfaces," 2009 IEEE Electrical Design of Advanced Packaging & Systems Symposium (EDAPS), Shatin, Hong Kong, 2009.

- [6] B. Pu, J. Fan and W. Nah, "Immunity Enhancement of the Power Distribution Network in Integrated Circuits With Coplanar Meander Lines in Package," in IEEE Transactions on Electromagnetic Compatibility, vol. 62, no. 5, pp. 2238-2246, Oct. 2020.

- [7] E. Li et al., "Progress Review of Electromagnetic Compatibility Analysis Technologies for Packages, Printed Circuit Boards, and Novel Interconnects," in *IEEE Transactions on Electromagnetic Compatibility*, vol. 52, no. 2, pp. 248-265, May 2010.

- [8] T. Wu, H. Chuang and T. Wang, "Overview of Power Integrity Solutions on Package and PCB: Decoupling and EBG Isolation," in IEEE Transactions on Electromagnetic Compatibility, vol. 52, no. 2, pp. 346-356, May 2010.

- J. Kim et al., "Chip-Package Hierarchical Power Distribution Network Modeling and Analysis Based on a Segmentation Method," in *IEEE Transactions on Advanced Packaging*, vol. 33, no. 3, pp. 647-659, Aug. 2010

- [10] T. Sudo, H. Sasaki, N. Masuda and J. L. Drewniak, "Electromagnetic interference (EMI) of system-on-package (SOP)", *IEEE Trans. Adv. Packag.*, vol. 27, no. 2, pp. 304-314, May 2004.

- [11] H. Liu, Q. Ding and J. Jiang, "112G PAM4/56G NRZ Interconnect Design for High Channel Count Packages," 2018 IEEE 27th Conference on Electrical Performance of Electronic Packaging and Systems (EPEPS), San Jose, CA, 2018.

- [12] X. C. Wei, E. P. Li, E. X. Liu and R. Vahldieck, "Efficient Simulation of Power Distribution Network by Using Integral-Equation and Modal-Decoupling Technology," in *IEEE Transactions on Microwave Theory* and Techniques, vol. 56, no. 10, pp. 2277-2285, Oct. 2008

- [13] E. Liu, X. Wei, Z. Z. Oo, E. Li and L. Li, "Modeling of Advanced Multilayered Packages with Multiple Vias and Finite Ground Planes," 2007 IEEE Electrical Performance of Electronic Packaging, Atlanta, GA, USA, 2007, pp. 275-278

- [14] L. Bai, H. He, F. Liu, J. Li, Y. Jia and H. Yang, "The Collaborative Design for the Package of High - speed Interface Chip," 2020 21st International Conference on Electronic Packaging Technology (ICEPT), Guangzhou, China, 2020.

- [15] T. Suwa and H. Hadim, "Multidisciplinary Electronic Package Design and Optimization Methodology Based on Genetic Algorithm," in IEEE Transactions on Advanced Packaging, vol. 30, no. 3, pp. 402-410, Aug. 2007.

- [16] M. Swaminathan, H. M. Torun, H. Yu, J. A. Hejase and W. D. Becker, "Demystifying Machine Learning for Signal and Power Integrity Problems in Packaging," in IEEE Transactions on Components, Packaging and Manufacturing Technology, vol. 10, no. 8, pp. 1276-1295, Aug. 2020

- [17] R. Mellitz, A. Ran, M. P. Li, and V. Ragavassamy, "Channel Operating Margin (COM): Evolution of Channel Specifications for 25 Gbps and Beyond", *DesignCon* 2013, Santa Clara, CA, 2013.

- [18] IEEE Std 802.3bj-2014 IEEE Standard for Ethernet Amendment 2: Physical Layer Specifications and Management Parameters for 100 Gb/s Operation Over Backplanes and Copper Cables.

- [19] B. Pu, R. W. Yoo, J. Park, J. S. Pak and S. Moon, "Fast Hierarchical Optimization Method for High Speed. Channel Design Using Channel Operating Margin (COM)", *DesignCon 2018*, Santa Clara, CA, USA, Jan. 30-Feb.1, 2018.

- [20] F. de Paulis, T. Wang-Lee, R. Mellitz, M. Resso, R. Rabinovich and O. J. Danzy, "Backplane Channel Design Exploration at 112 Gbps Using Channel Operating Margin (COM)," 2020 IEEE International Symposium on Electromagnetic Compatibility & Signal/Power Integrity (EMCSI), Reno, NV, USA, 2020, pp. 158-163.

- [21] B. Pu, K. Kim and W. Nah, "Package design methodology in consideration with signal integrity, power integrity and electromagnetic immunity," 2014 XXXIth URSI General Assembly and Scientific Symposium (URSI GASS), Beijing, 2014, pp. 1-4.

- [22] Adam Healey, "Noise considerations for 40/100GBase-CR4/10", IEEE 802.3ba Task Force Meeting, July, 2009.

- [23] B. Chen et al., "Differential Integrated Crosstalk Noise (ICN) Mitigation in the Pin Field Area of SerDes Channel," 2018 IEEE Symposium on Electromagnetic Compatibility, Signal Integrity and Power Integrity (EMC, SI & PI), Long Beach, CA, 2018, pp. 533-537.