# Stochastic Power Loss Analysis of Differential Power Processing

Ping Wang, *Student Member, IEEE*, Robert C. N. Pilawa-Podgurski, *Member, IEEE*, Philip T. Krein, *Fellow, IEEE* and Minjie Chen, *Senior Member, IEEE*

Abstract—This paper presents stochastic power loss analysis for differential power processing (DPP). A stochastic model is developed to analyze power loss scaling in a DPP system based on probability distributions of loads or sources. Scaling factors are introduced to describe how losses change with DPP system size and load or source power variance. Expected power losses of representative DPP topologies are analyzed and compared to losses of a conventional dc-dc converter with the same total switch die area and magnetic volume. The results quantify performance trends of DPP architectures. Models and scaling factors are verified with SPICE simulations and experimental results. The analytical framework, scaling factors, and quantitative models provide useful guidelines for designing large-scale DPP systems. This paper is accompanied by a video file demonstrating the modeling procedures and the experimental setup.

*Index Terms*—Differential power processing (DPP), stochastic models, battery management systems, photovoltaic systems, data center power management, dc-dc converters, series modules

#### I. Introduction

THE emerging differential power processing (DPP) concept offers important advantages in systems with load or source modules connected in series. DPP converters process a small fraction of total power to reduce overall conversion stress and enhance system efficiency and functionality. This paper, extended from [1], presents a systematic way to analyze power flows and losses in general DPP architectures. For the first time, a stochastic model is developed for quantitative evaluation based on the statistics of load or source power. The analysis models power loss scaling and loss distribution within a DPP system. It reveals how DPP benefits scale with system size and the degree of module power mismatch, offering design insights.

DPP architectures follow from battery active equalization circuits, including switched-inductor (buck-boost) types [2], [3], switched-capacitor types [4], [5], and ac-link or dc-link fully-coupled types based on flyback [6]–[8], forward [9], half-bridge [10], and dual-active-bridge (DAB) converters [11],

- P. Wang and M. Chen are with the Department of Electrical and Computer Engineering and Andlinger Center for Energy and the Environment at Princeton University, Princeton, NJ 08540, USA.

- R. C. N. Pilawa-Podgurski is with the Department of Electrical Engineering and Computer Sciences, University of California Berkeley, Berkeley, CA 94720, USA.

- P. T. Krein is with the Department of Electrical and Computer Engineering, University of Illinois at Urbana-Champaign, Urbana, IL 61801, USA.

- This paper is an extension of a prior conference paper, "Performance Limits of Differential Power Processing" in *Proc. IEEE COMPEL* 2020 [1].

This work was jointly supported by the DOE ARPA-E CIRCUITS program (DE-AR0000906), the NSF CAREER award (#1847365), the Princeton E-ffiliates Program, and the Grainger Center for Electric Machinery and Electromechanics at the University of Illinois.

[12]. Similar topologies were later applied to photovoltaic (PV) systems to manage mismatch among series PV cells [13], [14]. Control strategies and architectures have been proposed to achieve PV maximum power point tracking (MPPT) [15]–[21]. DPP architectures have also been implemented in emerging dc systems such as data center servers [22], [23] and multiprocessor systems [24]–[26].

Power flows in DPP systems are usually dynamic and unpredictable [27]. Power distribution and mismatch among series voltage domains are influenced by factors that include aging, manufacturing variation, temperature differences [4], illuminance variation [28], [29], and random task requests for data center servers [22]. Potentially, each module power is a random process. Previous work to analyze how power loss and power ratings of DPP converters change with statistical variance has been based on numerical simulations or data-driven methods [30]–[32]. An analytical method to evaluate performance with large-scale stochastic loads or sources is needed and is the main focus here.

In this paper, DPP topologies are grouped into two primary categories: fully coupled DPP and ladder DPP. We perform a systematic analysis of power flow for each, and develop a stochastic model to predict conduction loss and its distribution. The purpose of the stochastic model is not to predict all losses in DPP systems, but rather to understand how performance scales with system dimension and load or source power variance. The model provides guidance on topology selection and design optimization. Instead of estimating loss for a specific case, the model is an ensemble evaluation for stochastic power distributions (e.g., Gaussian, Poisson, Bernoulli, etc.). A scaling factor,  $S(\bullet)$ , is introduced to describe how loss changes with system size or module power variance. Representative DPP topologies are analyzed and compared to a reference N:1DAB converter [33], [34], given the same total switch die area and magnetic core size. The models are validated with SPICE simulations and with experiments designed to test loss scaling.

In the remainder of this article, Section II introduces stochastic modeling for the primary DPP categories and develops loss scaling factors. Section III demonstrates typical circuit implementations and derives output resistance for loss analysis. Section IV compares various DPP topologies against the reference  $N{:}1$  DAB converter, derives performance trends, and verifies these with SPICE simulations. Section V generalizes the model to include module power correlation. Section VI validates the model with experimental results. Section VII concludes this paper. Extended derivations for the models, and an application case study on a DPP-powered data storage

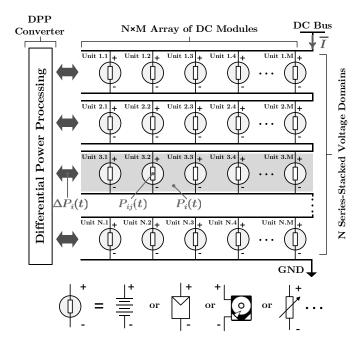

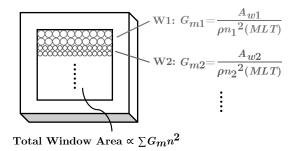

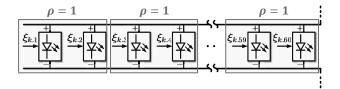

Fig. 1. An  $N \times M$  DPP system with N series-stacked voltage domains, each comprising M load or source modules.  $P_{ij}(t)$  and  $P_i(t)$  are the power of one dc module and of one voltage domain, respectively;  $\Delta P_i(t)$  is the power mismatch for one voltage domain.

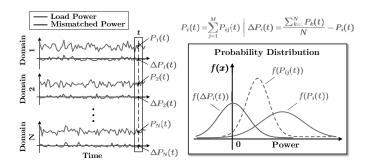

Fig. 2. Load power and mismatched power of each voltage domain is a random process with a probability distribution (Gaussian distributions are shown here as an example).

server, are provided in the Appendix.

#### II. STOCHASTIC MODEL FOR DPP LOSS

Fig. 1 shows a general DPP system. An  $N \times M$  array of load or source modules is configured in N series-stacked voltage domains. Each domain comprises M modules connected in parallel. Analysis in this paper is based on modular loads, and analysis for modular sources is the same. Denote the power consumption of the  $j^{th}$  load in the  $i^{th}$  voltage domain as  $P_{ij}(t)$ . The total *domain power* consumed within the  $i^{th}$  voltage domain is

$$P_i(t) = P_{i1}(t) + P_{i2}(t) + \dots + P_{iM}(t).$$

(1)

DPP converters deliver power mismatch  $\Delta P_i(t)$  among series voltage domains. In practical applications, the power distribution can be complicated, with unpredictable patterns or correlations. In this paper, each individual load power  $P_{ij}(t)$ , domain power  $P_i(t)$ , and mismatched power  $\Delta P_i(t)$

2

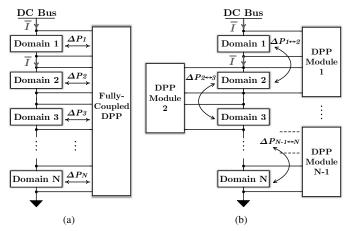

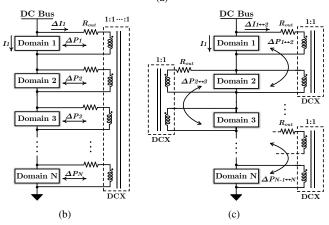

Fig. 3. Typical DPP architectures: (a) fully-coupled DPP; (b) ladder DPP.

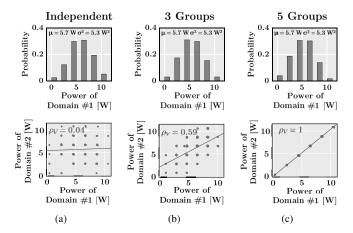

is modeled as a random process as indicated in Fig. 2. Their values at any time instant t are random variables with certain probability distributions. We first analyze the case when all module powers are statistically independent with identical distributions (i.i.d.), and later extend the analysis to cases with correlation. In the case with i.i.d. loads, individual load power mean values  $\mathbb{E}[P_{ij}(t)]$  and variances  $\mathrm{Var}[P_{ij}(t)]$  are identical and are denoted as  $\mu_0$  and  $\sigma_0^2$ . Each domain has the same voltage, denoted as  $V_0$ . A more general case allows unbalanced voltages (as when each domain has its own power droop characteristic), but matched domain voltages are explored here for clarity. The analytical framework in this paper can be applied to DPP systems with more complicated patterns such as unmatched load power expectations across voltage domains.

#### A. Fully Coupled DPP and Ladder DPP

The two primary DPP categories are shown in Fig. 3. Fig. 3a depicts the architecture of a fully-coupled DPP converter, in which all voltage domains are coupled by the DPP circuitry. A typical fully-coupled DPP circuit functions as a multiport dc-dc converter [13], with a direct power flow path between any two domains. Due to the series architecture, the same bus current  $\overline{I}(t) = \sum_{k=1}^{N} P_k(t)/NV_0$  flows through each voltage domain plus its corresponded DPP port. The instantaneous differential power processed for the  $i^{th}$  voltage domain is

$$\Delta P_i(t) = \overline{I}(t)V_0 - P_i(t) = \overline{P}(t) - P_i(t). \tag{2}$$

Here,  $\overline{P}(t) = \sum_{k=1}^{N} P_k(t)/N$  is the arithmetic average of the N domain powers. Eq. (2) indicates that in a fully-coupled DPP converter, the differential power processed at the  $i^{th}$  port is the power mismatch between the average domain power  $\overline{P}(t)$  and the  $i^{th}$  domain power  $P_i(t)$ . With i.i.d. loads, the power rating of each port in a fully-coupled DPP is the same.

Fig. 3b shows the architecture of a domain-to-domain or ladder DPP system, in which multiple standalone dc-dc converters (termed *DPP submodules*) link neighboring voltage domains. The differential power processed for one voltage domain is related to multiple DPP submodules,

$$P_i(t) + \Delta P_{i \leftrightarrow i+1}(t) - \Delta P_{i-1 \leftrightarrow i}(t) = \overline{I}(t)V_0 = \overline{P}(t), \quad (3)$$

where  $\Delta P_{i\leftrightarrow i+1}(t)$  is the differential power that the  $i^{th}$  submodule delivers from the  $i^{th}$  domain to the  $(i+1)^{th}$  domain  $(\Delta P_{i\leftrightarrow i+1}(t) = 0$ , if i = 0 or N). Reorganizing (3),

$$\Delta P_{i \leftrightarrow i+1}(t) = \sum_{k=1}^{i} (\overline{P}(t) - P_k(t)) = \sum_{k=1}^{i} \Delta P_k(t)$$

$$= i \times \overline{P}(t) - \sum_{k=1}^{i} P_k(t).$$

(4)

In a ladder DPP converter, there is no direct power path between non-neighboring voltage domains. Differential power must go through multiple submodules to manage non-neighboring domains, potentially resulting in differential power accumulation. As indicated in (4), the  $i^{th}$  submodule needs to process the accumulated mismatched power of first i voltage domains, i.e.,  $\sum_{k=1}^{i} \Delta P_k(t)$ . This will cause additional power to be processed in a ladder DPP system compared to a fully-coupled DPP system. It also leads to varied power ratings among submodules in a ladder DPP converter.

In some DPP architectures, the power flow may be impacted by the control methods [35], [36]. Modeling the power loss of these architectures is beyond the scope of this paper, but the stochastic analytical framework developed here can be extended to cover these cases.

#### B. Stochastic Loss Model and Scaling Factor

In Fig. 1, parameters N, M, and  $\sigma_0^2$  impact the differential power processed by DPP converters. Here, we develop a stochastic model with i.i.d. loads to quantify the impact. Scale-dependent loss (i.e., loss that scales with system size or load power variance) is derived based on processed differential power. Losses that are expected to be approximately scale independent, such as control power and losses linked to switching frequency, are not included in the model but are explored during experiments to test scaling validity. The expected value of scale-dependent power loss is used to describe the average loss of a DPP system. For comparison, a stochastic loss model is derived for a conventional N:1 DAB converter delivering the same total load power  $\sum_{i=1}^{N} P_i(t)$ , and this is used as a reference case. Detailed derivations of the expected scale-dependent power loss are provided in Appendix I.

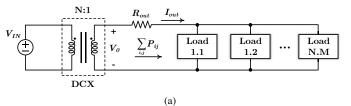

Fig. 4 shows equivalent circuit models of the reference converter and of the two typical DPP architectures. Conduction loss dominates scale-dependent losses, and is captured by aggregating internal losses into an effective output resistance,  $R_{out}$ , for each module or circuit. Switching loss, core loss, control power, and other nonideal effects can be added, typically as polynominal functions of the processed power, to enhance accuracy, but the modeling procedure for any of these follows from that presented below.

1. Conventional reference N:1 DAB: A stochastic loss model for a conventional N:1 DAB converter outputting  $V_0$  is derived here as a comparative reference or baseline. This converter can be modeled as an N:1 transformer with an output resistance  $R_{out}$  [37], as shown in Fig. 4a. All loads are

Fig. 4. Equivalent circuit model for loss analysis of: (a) conventional N:1 dc-dc converter based on a DAB; (b) fully-coupled DPP; (c) ladder DPP.

connected in parallel at the output. The loss in this converter when processing full power is

$$\mathbb{E}[P_{loss}(t)] = \mathbb{E}[R_{out}I_{out}^2(t)] = \frac{R_{out}}{V_0^2} \mathbb{E}\left[\left(\sum_{i=1}^N P_i(t)\right)^2\right]$$

$$= \left(MN\sigma_0^2 + M^2N^2\mu_0^2\right) \times \frac{R_{out}}{V_0^2} \Rightarrow \underbrace{\mathcal{S}(M^2N^2\mu_0^2)}_{scaling\ factor}.$$

(5)

Detailed derivations are provided in Appendix I. We use symbol  $S(\bullet)$  to represent a performance scaling factor that describes how power loss changes with system size or load power variance. As indicated by (5), loss in the reference converter depends on average load power as well as on load variance, and scales quadratically with the total average load power  $MN\mu_0$  unless the variance  $\sigma_0^2$  is extremely high.

2. Fully-Coupled DPP Converter: As illustrated in Fig. 4a, a fully-coupled DPP topology can be modeled as an N-port network coupled with an N-winding transformer with uniform turns ratios. Each port has an effective output resistance  $R_{out}$ , matched for this analysis. The  $i^{th}$  port processes  $\Delta P_i(t)$ , so the instantaneous loss and expected loss at the  $i^{th}$  port are

$$P_{loss.i}(t) = \Delta I_i(t)^2 R_{out} = \left(\frac{\Delta P_i(t)}{V_0}\right)^2 R_{out}$$

$$= R_{out} \left(\frac{\overline{P}(t) - P_i(t)}{V_0}\right)^2, \tag{6}$$

$$\mathbb{E}[P_{loss.i}(t)] = \frac{R_{out}}{V_0^2} \times \frac{M(N-1)}{N} \sigma_0^2. \tag{7}$$

Here,  $\Delta I_i(t)$  is the current flowing through  $R_{out}$  at each port and is also the mismatch between the average current and domain load current:  $\Delta I_i(t) = \overline{I}(t) - I_i(t)$ . Notice that

|                   | Expected Power Loss of the $i^{th}$ DPP Port/Submodule     | Expected Total Power Loss                                                | Scaling Factor                |  |  |  |

|-------------------|------------------------------------------------------------|--------------------------------------------------------------------------|-------------------------------|--|--|--|

| N:1 DAB Converter | N/A                                                        | $\left(MN\sigma_0^2 + M^2N^2\mu_0^2\right) \times \frac{R_{out}}{V_0^2}$ | $\mathcal{S}(M^2N^2\mu_0^2)$  |  |  |  |

| Fully-Coupled DPP | $\frac{M(N-1)}{N}\sigma_0^2 \times \frac{R_{out}}{V_0^2}$  | $M(N-1)\sigma_0^2 \times \frac{R_{out}}{V_0^2}$                          | $\mathcal{S}(MN\sigma_0^2)$   |  |  |  |

| Ladder DPP        | $\frac{M(N-i)i}{N}\sigma_0^2 \times \frac{R_{out}}{V_0^2}$ | $\frac{M(N-1)(N+1)}{6}\sigma_0^2 \times \frac{R_{out}}{V_0^2}$           | $\mathcal{S}(MN^2\sigma_0^2)$ |  |  |  |

TABLE I STOCHASTIC POWER LOSS MODELS OF N:1 DAB CONVERTER AND TWO GENERAL DPP ARCHITECTURES ( $M \geq 1, N \geq 2$ )

$\mathbb{E}[P_{loss.i}(t)]$  is proportional to  $\sigma_0^2$  because  $P_{loss.i}(t)$  depends on  $\Delta I_i^2(t)$ . Each port has the same expected loss, and the total is

$$\mathbb{E}[P_{loss}(t)] = \sum_{i=1}^{N} \mathbb{E}[P_{loss.i}(t)]$$

$$= M(N-1)\sigma_0^2 \times \frac{R_{out}}{V_0^2} \Rightarrow \underbrace{\mathcal{S}(MN\sigma_0^2)}_{scaling\ factor}.$$

(8)

The loss scaling in (8) is linear in N, M, and  $\sigma_0^2$  but independent of the average load power  $\mu_0$ .

3. Ladder DPP Converter: In a ladder DPP topology, each submodule can be modeled as a 1:1 transformer with output resistance  $R_{out}$ , as illustrated in Fig. 4b. The  $i^{th}$  submodule is processing  $\Delta P_{i\leftrightarrow i+1}(t)$ , so the instantaneous and expected loss of the  $i^{th}$  submodule are

$$P_{loss.i}(t) = \Delta I_{i \leftrightarrow i+1}(t)^2 R_{out} = \left(\frac{\Delta P_{i \leftrightarrow i+1}(t)}{V_0}\right)^2 R_{out}$$

$$= R_{out} \left(\frac{i \times \overline{P}(t) - \sum_{k=1}^{i} P_k(t)}{V_0}\right)^2,$$

$$\mathbb{E}[P_{loss.i}(t)] = \frac{R_{out}}{V_c^2} \times \frac{M(N-i)i}{N} \sigma_0^2.$$

(10)

Here,  $\Delta I_{i \leftrightarrow i+1}(t)$  is the effective current that flows through  $R_{out}$  at each submodule and is equal to the accumulated mismatched current of the top i voltage domains:  $\Delta I_{i \leftrightarrow i+1}(t) = \sum_{k=1}^i \Delta P_k(t)/V_0 = \sum_{k=1}^i \Delta I_k(t)$ . Expected loss varies among submodules, and the total expected loss is

$$\mathbb{E}[P_{loss}(t)] = \sum_{i=1}^{N-1} \mathbb{E}[P_{loss.i}(t)]$$

$$= \frac{M(N-1)(N+1)}{6} \sigma_0^2 \times \frac{R_{out}}{V_0^2} \Rightarrow \underbrace{\mathcal{S}(MN^2\sigma_0^2)}_{scaling\ factor}.$$

(11)

The loss scales linearly with M and  $\sigma_0^2$ , and quadratically with N. Compared to a fully-coupled DPP converter, a ladder DPP converter has a higher scaling factor with N since differential power accumulates along the series stack. Notice that the total loss is still independent of the average load power  $\mu_0$ .

Table I summarizes the expected power loss and scaling factors of the three architectures. For DPP solutions, the expected loss scales linearly with variance  $\sigma_0^2$  but is independent of average load power  $\mu_0$ . This is consistent with the

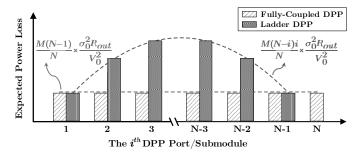

Fig. 5. Expected power loss of the  $i^{th}$  port or submodule in a fully-coupled DPP converter and a ladder DPP converter with N series voltage domains.

fundamental benefit: loss in a DPP system is determined by power differences, expected to be only a fraction of total load power. If the individual load powers match, a DPP system has no conduction loss.

Fig. 5 plots the expected loss distribution in a fully-coupled DPP converter and a ladder DPP converter. In a fully-coupled DPP, the expected loss is uniformly distributed among different ports, whereas in a ladder DPP, submodules closer to center of the series stack tend to process more power and generate more loss.

## III. OUTPUT RESISTANCE ANALYSIS FOR VARIOUS DPP TOPOLOGIES

In a DPP architecture, the switch count and magnetic component count track the number of voltage domains N. A reasonable approach is to compare alternatives given the same total semiconductor switch size and magnetic component volume. In this section, DPP topologies are explored this way. Their output resistance  $R_{out}$  is analyzed and compared with that of the reference converter under the following constraints:

- 1) Identical Total Semiconductor Die Area: For switches, semiconductor die area scales linearly with the  $G_{sw}V_{sw}^k$  product [38], [39].  $G_{sw}$  is switch conductance;  $V_{sw}$  is switch blocking voltage; and coefficient k, typically 2, depends on material and process. The total semiconductor die area is represented as the sum  $\sum G_{sw}V_{sw}^2$  for all switches, constrained to be identical for topologies compared here and normalized to  $G_{SW}V_0^2$ .

- Identical Total Volume of Magnetic Components: In this paper, total volume of magnetic components is evaluated using core window area, which in turn tracks core cross

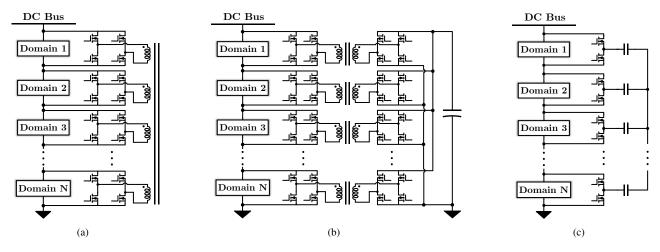

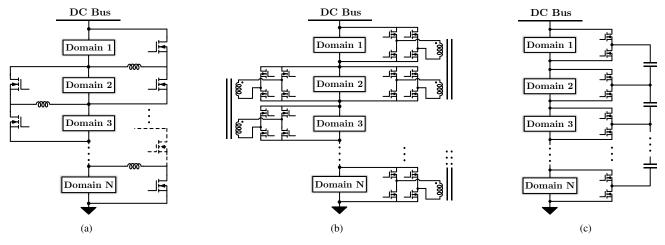

Fig. 6. Fully-coupled DPP topologies: (a) ac fully-coupled DPP [12], [22]; (b) dc fully-coupled DPP [11], [23]; (c) Dickson-SC DPP [5].

Fig. 7. Ladder DPP topologies: (a) ladder DPP with buck-boost cells [2], [17], [19], [25], [27], [30]–[32]; (b) ladder DPP with DAB cells; (c) ladder-SC DPP [4]–[6], [16], [24].

Fig. 8. Magnetic core window area distribution and winding conductance. Total core window area is proportional to  $\sum G_m n^2$ .  $A_w$  represents the distributed window area for each winding, n is the effective number of turns in each winding,  $\rho$  is the winding resistivity, and MLT is the mean length per turn, set to be identical for all windings.

sectional area. As illustrated in Fig. 8, the window area of each winding is proportional to  $G_m n^2$  (each winding is assigned the same fill factor).  $G_m$  is the winding conductance and n is the number of series turns. Here n is determined by flux limits on volts per turn. Volts per turn values are scaled to  $V_0$ . The total window area is the sum  $\sum G_m n^2$  over all windings, constrained to be identical for topologies

compared here and normalized to  $G_M$ . Switched-capacitor topologies do not require magnetics.

To model the output resistance  $R_{out}$  in Fig. 4,  $R_{ds(on)}$  of each switch and winding dc resistance are lumped together and constrained as above.

Figs. 6 and 7 exhibit several typical circuit implementations of fully-coupled DPP architectures and ladder DPP architectures, respectively. An energy buffering capacitor can be added in parallel to each voltage domain for stable voltage. Table II compares these topologies to the reference converter, in terms of normalized quantities. In Table II, the root-mean-square (RMS) current in each component is calculated based on the output current ( $I_{out}$ ) or the effective differential current ( $\Delta I_i$  or  $\Delta I_{i \leftrightarrow i+1}$ ) as defined in Fig. 4. For the reference DAB converter, the semiconductor die area  $G_{SW}V_0^2$  and winding window area  $G_M$  are equally distributed between the primary and secondary sides; for DPP converters, they are equally distributed among DPP ports or submodules.

To model  $R_{out}$  of magnetic-based topologies (reference converter, Figs. 6a-6b, and Figs. 7a-7b), the component RMS current is calculated with the following approximations: (1) trapezoidal current waveforms in topologies with active bridges (reference converter, Figs. 6a-6b, and Fig. 7b) are

|                          |                           |                      |                 | nductor Switch    | hes                   | Transformer/Inductor Windings                       |                  |                    |                       |                                    |                                                |  |

|--------------------------|---------------------------|----------------------|-----------------|-------------------|-----------------------|-----------------------------------------------------|------------------|--------------------|-----------------------|------------------------------------|------------------------------------------------|--|

|                          | Topologies                |                      | Switch<br>Count | Voltage<br>Rating | $R_{ds(on)}$          | RMS <sup>a</sup><br>Current                         | Winding<br>Count | Turns <sup>b</sup> | Winding<br>Resistance | RMS <sup>c</sup><br>Current        | Output Resistance $R_{out}$                    |  |

| N:1 Converter            | DAB                       | Primary <sup>d</sup> | 4               | $NV_0$            | $\frac{8N^2}{G_{SW}}$ | $\frac{\sqrt{2}}{2N}I_{out}$                        | 1                | N                  | $\frac{2N^2}{G_M}$    | $\frac{I_{out}}{N}$                | $-\frac{32}{G_{SW}}+\frac{4}{G_M}$             |  |

| (Conventional Reference) | DAB                       | Secondarye           | 4               | $V_0$             | $\frac{8}{G_{SW}}$    | $\frac{\sqrt{2}}{2}I_{out}$                         | 1                | 1                  | $\frac{2}{G_M}$       | $I_{out}$                          | $\overline{G_{SW}}^{+}\overline{G_{M}}$        |  |

|                          | Ac-Coupled                |                      | 4N              | $V_0$             | $\frac{4N}{G_{SW}}$   | $\frac{\sqrt{2}}{2}\Delta I_i$                      | N                | 1                  | $\frac{N}{G_M}$       | $\Delta I_i$                       | $\frac{8N}{G_{SW}} + \frac{N}{G_M}$            |  |

| Fully-Coupled DPP        | Dc-Coupled                |                      | 8 <i>N</i>      | $V_0$             | $\frac{8N}{G_{SW}}$   | $\frac{\sqrt{2}}{2}\Delta I_i$                      | 2N               | 1                  | $\frac{2N}{G_M}$      | $\Delta I_i$                       | $\frac{32N}{G_{SW}} + \frac{4N}{G_M}$          |  |

|                          | SC-b                      | ased (FSL)           | 2N              | $V_0$             | $\frac{2N}{G_{SW}}$   | $\sqrt{2}\Delta I_i$                                | N/A              | N/A                | N/A                   | N/A                                | $\frac{8N}{G_{SW}}$                            |  |

| Ladder DPP               | Buck-Boost-cell  DAB-cell |                      | 2N-2            | $2V_0$            | $\frac{8N-8}{G_{SW}}$ | $\sqrt{2}\Delta I_{i\leftrightarrow i+1}$           | N-1              | 2                  | $\frac{4N-4}{G_M}$    | $2\Delta I_{i\leftrightarrow i+1}$ | $\frac{32N - 32}{G_{SW}} + \frac{4N - 4}{G_M}$ |  |

|                          |                           |                      | 8N-8            | $V_0$             | $\frac{8N-8}{G_{SW}}$ | $\frac{\sqrt{2}}{2}\Delta I_{i\leftrightarrow i+1}$ | 2N-2             | 1                  | $\frac{2N-2}{G_M}$    | $\Delta I_{i \leftrightarrow i+1}$ | $\frac{32N - 32}{G_{SW}} + \frac{4N - 4}{G_M}$ |  |

TABLE II COMPARISON BETWEEN THE REFERENCE CONVERTER AND DIFFERENT DPP TOPOLOGIES  $(N \geq 2)$

treated as square waves; (2) the inductor current in the DPP topology with buck-boost cells (Fig. 7a) has low ripple. Based on switch  $R_{ds(on)}$ , winding dc resistance, and RMS current, effective output resistance  $R_{out}$  of the magnetic-based topologies can be obtained.

Fig. 6a shows an ac fully-coupled DPP converter with full bridge coupling to a multiwinding transformer. This converter comprises 4N switches, each blocking  $V_0$ , and N windings. Volts-per-turn values are scaled to  $V_0$ , so each winding contains one turn per unit. The resistances of each switch and each winding are  $\frac{4N}{G_{SW}}$  and  $\frac{N}{G_M}$ . The RMS currents in each switch and transformer winding at the  $i^{th}$  port are  $\frac{\sqrt{2}}{2}\Delta I_i$  and  $\Delta I_i$ , respectively, so the conduction loss at the  $i^{th}$  port is

$$P_{loss.i} = \left(\frac{\sqrt{2}}{2}\Delta I_i\right)^2 \frac{4N}{G_{SW}} \times 4 + \Delta I_i^2 \frac{N}{G_M}$$

$$= \Delta I_i^2 R_{out}.$$

(12)

This indicates that the output resistance of each port is  $\frac{8N}{G_{SW}} + \frac{N}{G_M}$ . Results for  $R_{out}$  of other magnetic-based DPP topologies and the reference converter can be modeled similarly and are summarized in Table II.

To model  $R_{out}$  of switched-capacitor (SC) DPP topologies (Figs. 6c and 7c), power loss should be analyzed at both the slow switching limit (SSL) and fast switching limit (FSL) [38]. Fig. 6c shows a Dickson-SC DPP converter in which all voltage domains are coupled through capacitors. Since charge can be transferred through the capacitors between any two voltage domains within one switching cycle, there is a direct power flow path between arbitrary voltage domains, and the circuit functions like a fully-coupled DPP topology. Fig. 7c shows a ladder-SC DPP in which neighboring voltage domains are linked by one capacitor. Charge can transfer only between

$\mbox{TABLE III} \\ R_{out} \mbox{ Modeling of SC DPP Topologies at SSL } (N \geq 2)$

| Topologies     | Capacitor<br>Count | Charge <sup>a</sup><br>Transfer                   | Output Resistance Rout (@ SSL) |  |  |  |

|----------------|--------------------|---------------------------------------------------|--------------------------------|--|--|--|

| Dickson-SC DPP | N                  | $\frac{\Delta I_i}{f_{sw}}$                       | $\frac{1}{Cf_{sw}}$ (Fig. 4a)  |  |  |  |

| Ladder-SC DPP  | N-1                | $\frac{\Delta I_{i \leftrightarrow i+1}}{f_{sw}}$ | $\frac{1}{Cf_{sw}}$ (Fig. 4b)  |  |  |  |

<sup>&</sup>lt;sup>a</sup> This column lists the charge transfer per half switching cycle of the  $i^{th}$  capacitor (from top to bottom) in a SC DPP.

two neighboring voltage domains in each switching cycle, so this functions like a ladder-DPP topology.

At the SSL, power loss of a SC converter is dominated by capacitor charge sharing loss. Table III summarizes charge transfer of each capacitor and  $R_{out}$  at the SSL for a Dickson-SC DPP and ladder-SC DPP. Denote the capacitance as C and the switching frequency as  $f_{sw}$ . The energy buffering capacitor at each voltage domain should be large, with a stable voltage, so its charge sharing loss is neglected. In the Dickson-SC DPP, charge transfer of the  $i^{th}$  capacitor is  $\Delta I_i/f_{sw}$  per half switching cycle, so the charge sharing loss at the  $i^{th}$  port is

$$P_{loss.i} = \frac{\Delta Q_i^2}{C} f_{sw} = \frac{(\Delta I_i / f_{sw})^2}{C} f_{sw} = \Delta I_i^2 R_{out}.$$

(13)

Accordingly,  $R_{out}$  of the Dickson-SC DPP as defined in Fig. 4a is  $\frac{1}{Cf_{sw}}$ . In the ladder-SC DPP, charge transfer of the  $i^{th}$  capacitor that links the  $i^{th}$  and  $(i+1)^{th}$  voltage domains is  $\sum_{k=1}^{i} \Delta I_k/f_{sw} = \Delta I_{i \leftrightarrow i+1}/f_{sw}$  per half switching cycle. Similarly,  $R_{out}$  of the ladder-SC DPP as defined in Fig. 4b is also  $\frac{1}{Cf_{sw}}$ . Although ladder-SC topologies have the same  $R_{out}$ , they generate higher power loss due to differential power accumulation, especially if the voltage domain is close to the

a,c These two columns list RMS current in each component. For the reference converter, they list the RMS current in each component on the primary side or the secondary side; for DPP topologies, they list the RMS current in the i<sup>th</sup> port or submodule.

b This column lists the number of turns per winding, normalized to a volts-per-turn value of V<sub>0</sub>.

de These two rows show primary side and secondary side information of the reference converter. Semiconductor die area  $G_{SW}V_0^2$  and winding window area  $G_M$  are allocated equally across the primary and secondary sides.

stack center or if N is large. Note that SC capacitor sizing also relates to capacitor utilization and voltage ratings, which is outside the scope of this work. Detailed comparison of various SC topologies and their passive component utilization and sizing can be found in [40].

At the FSL, capacitor charge sharing loss of a SC DPP is negligible. Conduction loss dominates. All capacitors act as fixed voltage sources. In this case, both the Dickson-SC DPP and the ladder-SC DPP function like fully-coupled DPP circuits and are equivalent. Each switch at the  $i^{th}$  domain conducts  $2\Delta I_i$  for half a switching cycle, and corresponded  $R_{out}$  values are listed in Table III. For a unified comparison, internal capacitor power loss is not included here, and SC DPP topologies are compared with the reference converter as fully-coupled circuits based on conduction loss at the FSL.

As listed in Table II,  $R_{out}$  of a dc fully-coupled DPP is four times of that in an ac fully-coupled DPP due to doubling of switch and winding counts and doubling of "dc-ac-dc" differential power conversion stages [22]. At the FSL, the two SC DPP topologies have the same conduction loss as that of an ac fully-coupled DPP without considering winding loss. Although a SC topology has no winding loss, the capacitor charge sharing loss is non-negligible if the capacitors are not large enough or if the switching frequency is not high enough.

Table II also indicates that with a fixed total switch die area and a fixed total magnetic volume, output resistance of DPP topologies increases linearly with the number of voltage domains due to the linear growth of component count, whereas  $R_{out}$  of the reference converter is fixed.

## IV. DPP SCALING AND PERFORMANCE TRENDS

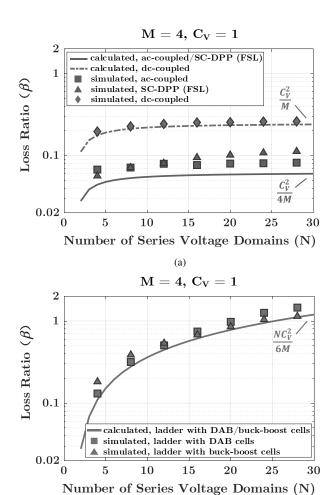

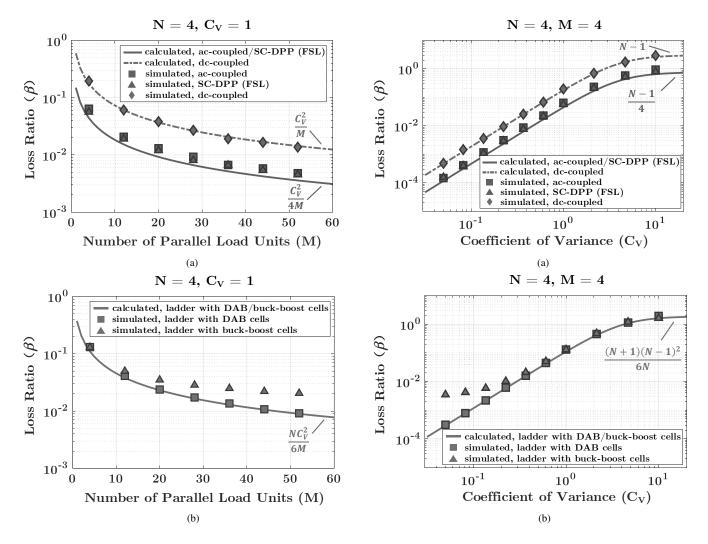

This section explores DPP performance trends as the system size or power variance scales up. In DPP systems, the processed differential power increases as load power variance increases, and advantages in terms of output resistance diminish when N scales up, as shown in Table II. To evaluate trends, a comparative expected loss ratio  $\beta = \frac{\mathbb{E}[P_{loss,DPP}]}{\mathbb{E}[P_{loss,ref}]}$  can be used as a performance metric. The coefficient of variance  $C_V = \frac{\sigma_0}{\mu_0}$  is used to represent the normalized variance of  $P_{ij}(t)$ . Values of  $\beta$  for a variety of topologies have been calculated based on the analysis. Lower values are better, and DPP advantages disappear if  $\beta > 1$ . The calculated  $\beta$  values and their asymptotic limits as M, N, and  $C_V$  scale up are plotted in Figs. 9-11.

Calculated results have been compared to Monte Carlo simulations in SPICE, in which a random sequence is generated for each load power. In simulations, the domain voltage  $V_0$  is 5 V, and the domain power is mostly below 10 W. For a given M, N, and  $C_V$ , each simulation was run 10,000 times to obtain an average power loss. For each case, simulated  $\beta$  was obtained as the ratio of the simulated average DPP loss to the calculated loss of the reference converter delivering the same total power. Switch  $R_{ds(on)}$  and winding resistance in each topology are set based on Table II. Since the Dickson-SC DPP and the ladder-SC DPP are equivalent with fast switching, the simulation uses a ladder-SC DPP at the FSL. When comparing SC DPP circuits to the reference converter, winding conduction loss has been excluded.

Fig. 9. Calculated and simulated loss ratio  $\beta$  as a function of N in: (a) fully-coupled DPP converters; (b) ladder DPP converters.

Figs. 9-11 compare calculated and simulated  $\beta$  values for various DPP topologies as functions of load array dimensions N and M, and coefficient of variance  $C_V$ . Considering the scaling of  $R_{out}$ , when N increases, the expected loss of fully-coupled DPP topologies increases as  $N^2$ , the same growth rate as for the reference converter. The expected power loss of ladder DPP topologies grows as  $N^3$ . Therefore, as N scales up,  $\beta$  of fully-coupled DPP topologies converges to an upper limit, but  $\beta$  of ladder DPP topologies keeps increasing, as shown in Fig. 9. The figure suggests that ladder DPP circuits lose their advantages for  $N \geq 25$ , given M = 4 and  $C_V = 1$ .

When the number of parallel load units M increases, the expected loss in both fully-coupled DPP and ladder DPP circuits increases as M, while the expected loss in the reference converter tracks  $M^2$ . Thus, the loss ratio  $\beta$  decreases for both fully-coupled DPP and ladder DPP circuits with increasing M, as shown in Fig. 10. As M increases, power consumption of each voltage domain becomes relatively more balanced since multiple random loads with the same probability distribution in parallel will narrow the domain population variance. The asymptotic limits are  $\beta \to \frac{C_V^2}{4M}$  for an ac-coupled or a SC DPP (FSL),  $\beta \to \frac{C_V^2}{M}$  for a dc-coupled DPP, and  $\beta \to \frac{NC_V^2}{6M}$  for a

Fig. 10. Calculated and simulated loss ratio  $\beta$  as a function of the number of the parallel loads M in (a) fully-coupled and (b) ladder DPP converters.

Fig. 11. Calculated and simulated loss ratio  $\beta$  as a function of coefficient of variance  $C_V$  in (a) fully-coupled and (b) ladder DPP converters.

ladder DPP with DAB or buck-boost cells.

Fig. 11 shows log-log plots of  $\beta$  for various DPP topologies as a function of  $C_V$ . As  $C_V$  increases, power variation among voltage domains increases, so the DPP converters need to process more power. Thus,  $\beta$  increases with  $C_V$  for all DPP topologies, but it converges to an upper limit. This is because the power loss of the reference converter, as in (5), is ultimately dominated by  $MN\sigma_0^2$  when  $C_V$  (i.e.,  $\frac{\sigma_0}{\mu_0}$ ) increases, the same rate of increase with  $C_V$  as for DPP topologies. Asymptotic upper limits of  $\beta$  for ac-coupled or SC DPP (FSL), dc-coupled DPP, and ladder DPP with DAB or buck-boost cells are  $\frac{N-1}{4}$ , N-1, and  $\frac{(N+1)(N-1)^2}{6N}$ , respectively.

In Figs. 9 – 11, calculated ratios match simulated ones well, validating the stochastic model. Mismatches are caused by active bridge trapezoidal current waveforms (Figs. 6a-6b, Fig. 7b), inductor current ripple in buck-boost cells (Fig. 7a), and capacitor charge sharing loss in SC converters (Fig. 6c, Fig. 7c). For larger M or smaller  $C_V$ , the average differential power processed by each buck-boost cell is reduced. In this case, inductor ripple current becomes comparable to average current, yielding increased mismatch between calculated and

simulated results for ladder DPP with buck-boost cells, as shown in Figs. 10b and 11b.

Figs. 9 – 11, together with Tables I – III, provide useful design insights for DPP architectures. For example, the asymptotic upper limit of  $\beta$  in an ac-coupled DPP topology is  $\frac{C_V^2}{4M}$  as N increases. When  $M=4, N\geq 2$ , and  $C_V=1$ , the loss ratio of an ac-coupled DPP converter is below 0.0625, indicating at least 16x loss reduction compared to the reference converter. A dc-coupled DPP converter can offer at least 4x reduction under the same conditions. If  $M > C_V^2$ , then  $\beta$  of fully-coupled DPP converters will be always less than 1, indicating that a fullycoupled DPP solution will be more efficient than the reference converter for arbitrary N. For a ladder DPP converter,  $\beta$  will be larger than 1 if N exceeds  $\frac{6M}{C_V^2}$ , indicating that a ladder DPP converter will lose advantages if N is large. It should be pointed out, however, that ladder DPP circuits are attractive if load variance is limited. A  $C_V$  value of 0.1, for instance, supports a large value of N before  $\beta$  exceeds unity. Figs. 9 – 11 and Tables I and II reveal that ac-coupled DPP solutions stand out from others explored here, although SC solutions are equally good if the FSL applies.

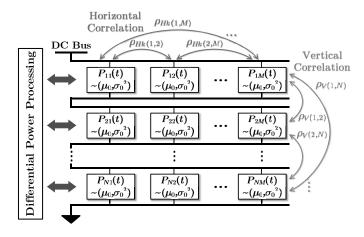

Fig. 12. Two types of load correlation in an  $N \times M$  DPP system: (1) vertical correlation across different voltage domains is denoted in green; (2) horizontal correlation between loads within one voltage domain is denoted in blue.

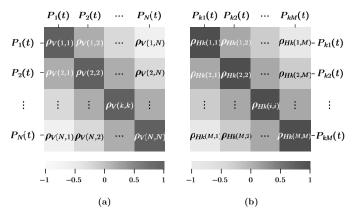

Fig. 13. (a) Vertical correlation matrix  $\rho_{\pmb{V}}$ :  $\rho_{V}(i,j)$  is the correlation coefficient between the  $i^{th}$  and  $j^{th}$  domain power,  $P_i(t)$  and  $P_j(t)$ ; (b) Horizontal correlation matrix  $\rho_{Hk}$ :  $\rho_{Hk}(i,j)$  is the correlation coefficient between the  $i^{th}$  and  $j^{th}$  load power in the  $k^{th}$  domain,  $P_{ki}(t)$  and  $P_{kj}(t)$ .

## V. DPP PERFORMANCE WITH LOAD CORRELATION

Load (or source) power correlation is common in DPP applications, such as when managing partial shading in a solar panel array, thermal hot spots in a series battery pack, or task distribution algorithms for a hard-disk storage cluster. In this section, the i.i.d. condition is relaxed to generalize the stochastic loss analysis. Each load power  $P_{ij}(t)$  is given the same distribution but the values are not independent. Detailed derivations are provided in Appendix I.

As shown in Fig. 12, load correlation can happen between loads across different voltage domains (vertical correlation) or between loads within one voltage domain (horizontal correlation). These can be described using correlation matrices as in Fig. 13. Fig. 13a is the vertical correlation matrix  $\rho_V$ , in which each entry  $\rho_V(i,j)$  represents the correlation coefficient between the  $i^{th}$  domain power  $P_i(t)$  and  $j^{th}$  domain power  $P_j(t)$ . Fig. 13b shows the horizontal correlation matrix  $\rho_{Hk}$  of the  $k^{th}$  voltage domain, in which  $\rho_{Hk}(i,j)$  is the correlation coefficient of the  $i^{th}$  load power  $P_{ki}(t)$  and  $j^{th}$  load power  $P_{kj}(t)$  within the  $k^{th}$  domain. These are Pearson's correlation coefficients [41]:  $\rho_{X,Y} = {}^{\text{Cov}[X,Y]}/\sqrt{\text{Var}[X]\text{Var}[Y]} \in [-1,1]$ .

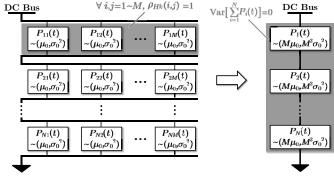

Fig. 14. Power loss of a fully-coupled DPP converter reaches its maximum with worst case load correlation, where  $\rho_{Hk}(i,j)=1$  for all loads within a voltage domain, and  $\operatorname{Var}\left[\sum_{k=1}^{N}P_{k}(t)\right]=0$ .

The expected power loss of a fully-coupled DPP converter when considering load correlation is

$$\mathbb{E}[P_{loss}(t)] = \frac{R_{out}}{NV_0^2} \left( \underbrace{(N-1)\sum_{k=1}^N \text{Var}[P_k(t)]}_{\boxed{1}} - 2\sum_{1 \le i < j \le N} \text{Cov}[P_i(t), P_j(t)] \right). \tag{14}$$

In part  $\widehat{1}$  of (14), the variance of each domain power,  $Var[P_k(t)]$ , can be expanded as

$$\operatorname{Var}[P_{k}(t)] = \sum_{i=1}^{M} \operatorname{Var}[P_{ki}(t)] + 2 \sum_{1 \leq i < j \leq M} \operatorname{Cov}[P_{ki}(t), P_{kj}(t)]$$

$$= \left(M + 2 \sum_{1 \leq i < j \leq M} \rho_{Hk}(i, j)\right) \underbrace{\operatorname{Var}[P_{ij}(t)]}_{=\sigma_{0}^{2}}.$$

(15)

In part ②, the covariance between arbitrary two domain powers,  $Cov[P_i(t), P_j(t)]$ , can be expressed as

$$Cov[P_i(t), P_j(t)] = \rho_V(i, j) \sqrt{Var[P_i(t)] Var[P_j(t)]}. \quad (16)$$

Eqs. (14) - (16) indicate that positive vertical correlation  $\rho_V(i,j)>0$  reduces the total expected power loss, whereas positive horizontal correlation  $\rho_{Hk}(i,j)>0$  increases the total expected power loss.

The worst-case horizontal load correlation is to have  $\rho_{Hk}(i,j)=1$  for two arbitrary loads within the  $k^{th}$  voltage domain, i.e., two arbitrary loads are linearly related and change exactly in the same direction. In this case, the  $k^{th}$  domain power variance reaches a maximum of  $\mathrm{Var}[P_k(t)]=M^2\sigma_0^2$ , and that domain can be treated as a single load.

The worst-case vertical correlation can be analyzed by

reorganizing (14) as

$$\mathbb{E}[P_{loss}(t)] = \frac{R_{out}}{V_0^2} \left( \sum_{k=1}^N \text{Var}[P_k(t)] - \frac{\text{Var}\left[\sum_{k=1}^N P_k(t)\right]}{N} \right).$$

(17)

The worst-case vertical correlation is when  $\operatorname{Var}\left[\sum_{k=1}^{N}P_{k}(t)\right]=0$ , i.e., the total power across all voltage domains is constant.

With both worst-case horizontal and vertical correlation, an  $N\times M$  DPP system becomes equivalent to a system in which each voltage domain contains a single load with mean power  $M\mu_0$  and power variance  $M^2\sigma_0^2$ , and the system load power  $\sum_{k=1}^N P_k(t)$  is constant, as depicted in Fig. 14. In this case, the expected loss of a fully-coupled DPP converter is

$$\mathbb{E}[P_{loss}(t)] = M^2 N \sigma_0^2 \times \frac{R_{out}}{V_0^2} \Rightarrow \underbrace{\mathcal{S}(M^2 N \sigma_0^2)}_{scaling\ factor}.$$

(18)

Worst-case horizontal correlation results in the expected loss scaling quadratically with M. Worst-case vertical correlation increases the domain scaling rate from N-1 to N. Based on (18), comparing an ac-coupled DPP to the reference converter under worst-case load correlation, the upper limit of  $\beta$  is  $\frac{C_V^2}{4}$ . In practice,  $C_V$  is usually less than one, and an ac-coupled DPP converter can reduce the expected loss by at least a factor of four even with arbitrary load correlation. When  $C_V$  is lower, the benefits are substantial.

## VI. EXPERIMENTAL VERIFICATION

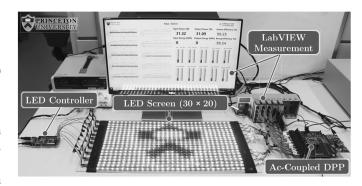

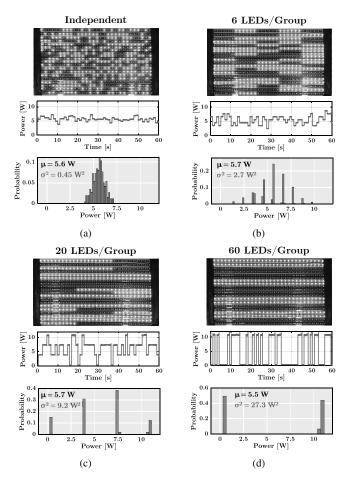

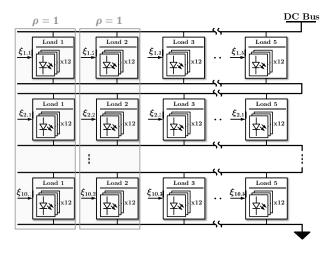

To validate the stochastic model, a  $30\times20$  LED array was built and tested as a large-scale DPP system with probabilistic load distribution. Random load tasks (independent or correlated) were set up and assigned to the LED array, which is supported by an ac fully-coupled DPP converter. Measured average DPP power loss was compared to the expected conduction power loss predicted by the model to validate scaling factors. The analytical framework developed in this paper is applicable to a range of DPP applications. An extended application study and model verification on a data storage server powered by DPP are provided in Appendix II.

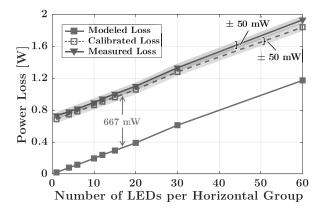

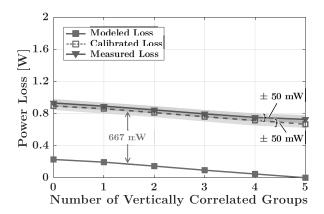

Recall that the stochastic model captures conduction losses, expected to dominate scale-dependent DPP system losses. Switching loss, core loss, and control and auxiliary losses could be weakly load dependent, so the key validation challenge is to determine whether total losses measured in experiments show the same scaling effects as conduction losses in the model.

## A. Experimental Setup

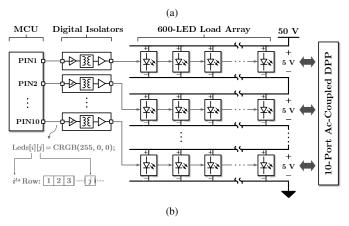

Fig. 15 shows an overview of the test bench. The  $30\times20$  LEDs were divided into ten voltage domains, connected in series to a 50 V dc bus. Each voltage domain supplied 5 V to 60 LEDs, and the full load power of the 600-LED screen is 108 W. Differential power of the ten domains was processed by a ten-port ac-coupled DPP circuit [22]. All 60 LEDs in

Fig. 15. (a) Experimental test bench with a  $30\times20$  LED array. (b) Power and signal configuration. 600 LEDs are divided into 10 series-stacked voltage domains and supported by a 10-port ac-coupled DPP converter. Each LED is individually addressable from the MCU controller.

each voltage domain were controlled by a serial signal path connected to a digital pin on the microcontroller (Arduino Mega) through a digital isolator (ADuM1200). Each LED was controlled individually by the microcontroller (MCU). A LabVIEW measurement system (cDAQ-9178 & NI9221 & NI9227) monitored and recorded total input power, load power of each voltage domain, and average power loss of the DPP system, in real time.

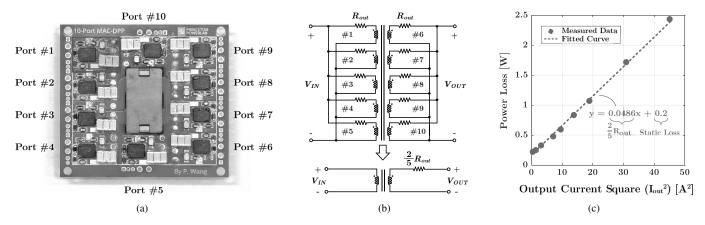

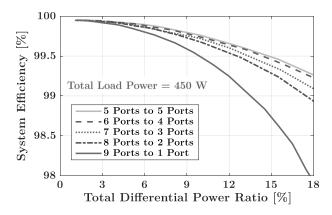

Fig. 16a shows the DPP prototype. A ten-winding printed-circuit-board (PCB) transformer in the center is surrounded by ten half-bridge ports. Each port couples one voltage domain to the transformer, and has the same  $R_{out}$  as that of a full-bridge implementation given the same switch die area and magnetic size. The prototype measures 4 cm  $\times$  3.5 cm  $\times$  0.76 cm, switches at 100 kHz, and supports up to 450 W system power with a power density of 700 W/in<sup>3</sup>. Key component values are listed in Table IV. System efficiency when supporting 450 W load for various operating conditions is plotted in Fig. 17. More details about the prototype can be found in [22].

$R_{out}$  of each port was measured with a five-port-to-five-port power delivery test in which five ports are connected in parallel as the input and five other ports are in parallel as the output. Fig. 16b depicts the equivalent circuit of this test. In this case, the DPP prototype is equivalent to a dc-dc converter with an output resistance of  $\frac{2}{5}R_{out}$ . The measured power loss versus  $I_{out}^2$  is plotted in Fig. 16c. Measured data are fitted with a line. The slope is the output resistance  $\frac{2}{5}R_{out}$  and the

Fig. 16. (a) Prototype of a 10-port ac-coupled DPP. (b) Equivalent circuits of the ac-coupled DPP prototype when delivering power from 5 ports to 5 ports  $(V_{IN} = V_{OUT} = 5 \text{ V})$ . (c) Measured power loss versus the square of output current for 5-port-to-5-port power delivery. This measurement is performed on common ground without sampling resistors, etc., so the 485 mW control and auxiliary losses are not captured in static loss here.

Fig. 17. System efficiency versus total processed differential power ratio (i.e.,  $\frac{\Sigma |\Delta P_i|}{\text{Total System Power}}$ ) when supporting 450 W load (i.e., rated system power of the DPP prototype) in various differential power delivery scenarios (e.g., 9 Ports to 1 Port indicates the differential power is delivered from 9 voltage domains to 1 domain). The 485 mW control and auxiliary losses are not included in the system losses here.

Fig. 18. Estimated magnetic core loss and switching loss as a function of the switching frequency.

intercept comprises switching loss and magnetic core loss. The  $R_{out}$  value is estimated as  $0.12~\Omega$ .

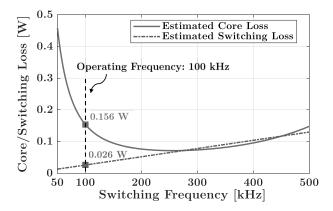

Fig. 18 shows estimated core loss and switching loss as a function of switching frequency. When switching at 100 kHz, the estimated core loss is 156 mW, the switching loss is

TABLE IV

KEY COMPONENT VALUES OF THE AC-COUPLED DPP PROTOTYPE

| Half-Bridge | Transformer | External Series  | Blocking                        |  |  |

|-------------|-------------|------------------|---------------------------------|--|--|

| Switch      | Core        | Inductor         | Capacitor                       |  |  |

| TI - DrMOS  | Ferroxcube  | Coilcraft        | Murata X5R $100 \mu F \times 3$ |  |  |

| CSD95377Q4M | ELP18-3C95  | SLC7649S, 100 nH |                                 |  |  |

26 mW and the sum is 182 mW. The current meter (NI-9227) was calibrated with an Agilent 34401A digital multimeter. Its tolerance is  $\pm 1$  mA on a 5 A scale, translating into 50 mW of power measurement tolerance on the full 50 V stack, or 5 mW for each 5 V port. Control and auxiliary losses (including level shifters, resistive dividers, etc.) were measured with inactive switches, and totalled  $485\pm50$  mW. Gate drives were powered from a separate source (which also powers the microcontroller and other auxiliary circuits). Thus, estimated loss above and beyond conduction loss totals  $667\pm50$  mW.

This difference is observed in all measurements. As will be noted below, it is load independent and has minimal impact on scaling. Since the paper is not seeking to design an extreme-performance DPP implementation and it is vital to have extensive real-time measurements, control overhead power is not optimized in the design and might be higher than in a commercial implementation. An alternative way to verify the loss analysis is to develop a thermal model for the system and use thermal images and colorimetric methods to differentiate the static loss and loss scaling.

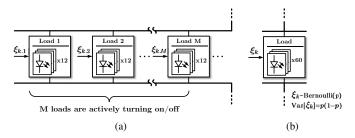

In the random load experiment, power to each LED is controlled by a random variable  $\xi$  that follows a Bernoulli distribution, Bernoulli(p). Here, p is the probability of turning on the LED. The load power of each LED therefore follows  $P_{ij} = \xi P_{on}$ , where  $P_{on} = 0.18$  W is the power consumption of one LED at full brightness, and the value of  $\xi \in \{0,1\}$  is updated once per second. By changing the turn-on probability p, the number of active loads per voltage domain M, and the vertical and horizontal load correlations, various random load tasks can be set up on the LED screen.

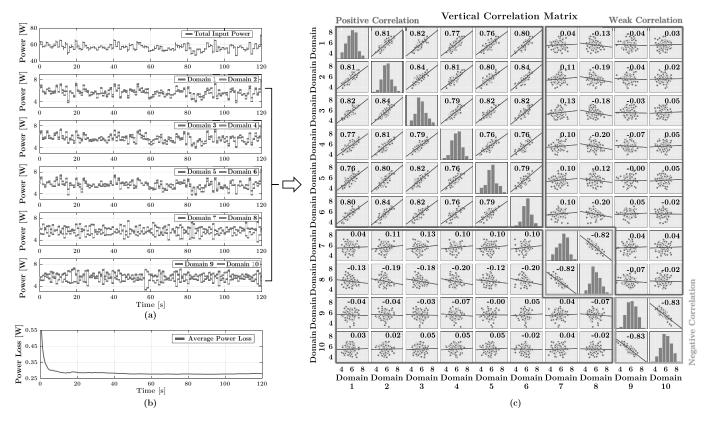

Fig. 19 illustrates the method for comparing measured average power loss to expected power loss from the stochastic model. Fig. 19a shows the instantaneous input system power

Fig. 19. (a) Measured total input power and each domain power in LabVIEW. (b) Measured average power loss of the DPP system in LabVIEW. (c) Vertical correlation matrix based on sampled data (2 min) of each domain power. Diagonal histograms plot the distribution of each domain power. Non-diagonal scatter plots depict power correlation between each pair of domains and the correlation coefficients.

and domain power measured by LabVIEW when performing a particular random load task. Measured average power loss over time is displayed in Fig. 19b. For each random load task in the experiments, the full system is operated long enough for measured average power loss to converge (typically 10 min).

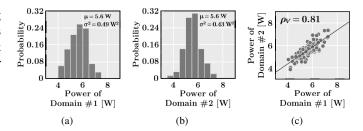

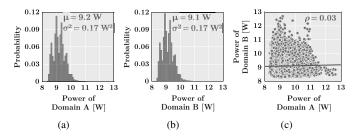

The expected power loss is obtained from statistics of the sampled domain power waveforms. As shown in Fig. 19c, measured power waveforms of all voltage domains are sampled every second for two minutes and plotted in the vertical correlation matrix. Fig. 20 zooms in on three example diagonal and non-diagonal entries in Fig. 19c. The diagonal entries (such as Fig. 20a and Fig. 20b) are histograms of domain powers  $P_1(t)$  through  $P_{10}(t)$ . The variance of each domain power,  $Var[P_k(t)]$  in part (1) of (14), can be obtained from the histograms. Horizontal correlation within a voltage domain is also reflected in the probability distribution of each diagonal histogram. The non-diagonal scatter plots (such as Fig. 20c) describe vertical correlation coefficients between any two domain powers. For scatter plots in Fig. 19c, red boxes show positive correlation, blue boxes show negative correlation, and green boxes show weak correlation.  $Cov[P_i(t), P_i(t)]$  in part (2) can be obtained from correlation coefficients of nondiagonal scatter plots. The statistical information provided in Fig. 19c can be used in the model to predict the expected power loss of a DPP system.

Fig. 20. Example zooms from Fig. 19c: (a) diagonal histogram of domain #1; (b) diagonal histogram of domain #2; (c) non-diagonal scatter plot of domain #1 power and domain #2 power.

Fig. 21. Experimental setup to validate the model as: (a) M increases; (b)  $\sigma_0^2$  increases.

## B. Power Loss Scaling with M and $\sigma_0^2$

To validate stochastic model scaling with M and  $\sigma_0^2$ , we perform two experiments as shown in Fig. 21. Vertical correlation is not considered in this subsection.

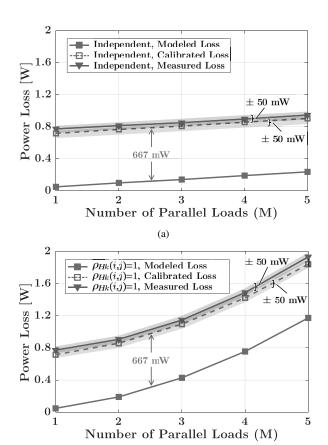

Fig. 22. Comparison between expected power loss and measured average loss as M increases in the case of: (a) independent load; (b) worst-case horizontal load correlation. The calibrated loss is the sum of modeled loss and estimated 667 mW overhead.

(b)

Fig. 23. Comparison between expected power loss and measured average loss when  $\sigma_0^2$  increases. The calibrated loss is the sum of modeled loss and the estimated 667 mW overhead.

In the M scaling experiment (Fig. 21a), sets of 12 LEDs in each voltage domain are bundled as one load and controlled by one random variable. The turn-on probability of each load is fixed at 0.5. By controlling the number of active loads (non-active loads are kept off), M can be adjusted from 1 to 5. Fig. 22 compares measured average loss and expected loss with and without horizontal correlation as M increases. The figure shows the conduction loss from the model, the

Fig. 24. Experimental setup for horizontal correlation. Here each horizontally correlated group contains two correlated LEDs with  $\rho=1$ .

model loss plus the estimated 667 mW overhead (shown as *calibrated loss*), and the total measured loss. The results confirm that average power loss of this ac-coupled DPP circuit scales linearly with M when loads are independent, but scales quadratically with M with worst-case horizontal correlation, as predicted by (8) and (18). The tracking match is as tight as the power measurement tolerance supports, with error bounds ( $\pm 50$  mW) highlighted.

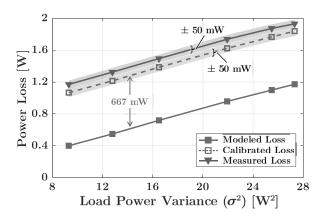

To test  $\sigma_0^2$  scaling, all 60 LEDs in each voltage domain are bundled as one load as shown in Fig. 21b, and the load power variance is adjusted by changing the turn-on probability p. Fig. 23 compares the measured average loss and expected loss as a function of  $\sigma_0^2$ . The figure shows the conduction loss from the model, the calibrated loss with added 667 mW overhead, and the measured total loss. The average loss of this ac-coupled DPP circuit increases linearly with load variance  $\sigma_0^2$ , consistent with the scaling factor in (8). The tracking match is as tight as power measurement tolerance supports.

### C. Impact of Load Correlation

Fig. 24 shows the setup to test horizontal correlation. In the experiment, each LED is controlled individually with p=0.5. Positive horizontal correlation is created by dividing 60 LEDs in a voltage domain equally into horizontally correlated groups in which  $\rho=1$  for LEDs within a group. Fig. 24 shows an example in which each horizontal group contains two LEDs. By increasing the number of LEDs in a horizontal group, a stronger positive horizontal correlation is created.

Figs. 25 and 26 show experimental results for horizontal correlation. Fig. 25 shows four cases of horizontal correlation as LEDs of each voltage domain shift from independent to fully correlated. The number of correlated LEDs per group increases from zero (i.e., independent), to six LEDs, 20 LEDs, and then 60 LEDs per group. When all LEDs are independent, the domain power consumption has a single smooth peak in histogram that follows a binomial distribution, and variance is small. When LEDs are horizontally correlated and the number of LEDs per correlated group increases, multiple split peaks appear in the histogram, with a higher power variance, as indicated by the power waveforms and probability histograms of domain #1. Fig. 26 compares the measured average loss to the expected loss and the calibrated loss with 667 mW overhead as the number of LEDs per horizontal group increases. The tracking match to the model is as tight as the power measurement tolerance supports. Figs. 25 and 26 confirm that positive horizontal correlation increases power

Fig. 25. LED screen pattern, power waveform and the probability histogram of domain #1 when 60 LEDs of each voltage domain are: (a) independent; (b) horizontally grouped with 6 LEDs/group; (c) horizontally grouped with 20 LEDs/group; (d) horizontally grouped with 60 LEDs/group.

Fig. 26. Comparison between expected power loss and measured average loss as the number of LEDs per horizontal group increases. A larger number of LEDs per group represents a stronger positive horizontal correlation. The calibrated loss is the sum of modeled loss and estimated 667 mW overhead.

variance, and thus the system needs to process more power and generates more loss. More positive horizontal correlation leads to higher DPP system loss, consistent with conclusions in Section V.

To test vertical load correlation, sets of 12 LEDs in a voltage domain are bundled as one load and controlled with p = 0.5.

Fig. 27. Experimental setup for vertical load correlation. Here is an example in which two vertically correlated groups are set up. In each vertical correlated group,  $\rho = 1$  for any two loads within the group.

Fig. 28. Power distribution histogram of domain #1 and power correlation graph between domains #1 and #2 when the number of vertically correlated groups is (a) zero (independent), (b) three, (c) five (fully-correlated).

Each domain contains five loads in total. As shown in Fig. 27, vertical correlation is created by grouping one load from each voltage domain, with  $\rho=1$  for loads within a vertical group. Fig. 27 demonstrates an example with two vertically correlated groups. By increasing the number of correlated groups, stronger positive vertical correlation can be generated. In this case, loads in each domain are controlled by five independent random variables, i.e., loads are vertically correlated but horizontally independent. Therefore, the distribution and variance of each domain power (part ① of (14)) remain unchanged. DPP power loss variation in this experiment is only related to vertical load correlation (part ② of (14)).

Figs. 28 and 29 show experimental results for vertical correlation. Fig. 28 plots the power distribution histogram of domain #1 and power correlation between domains #1 and #2. As the number of vertically correlated groups increases, positive load correlation across voltage domains becomes stronger and  $\rho_V$  increases from 0 to 1. During this process, the power distribution histogram of each voltage domain changes little, as expected. The measured average loss, calibrated loss with

Fig. 29. Comparison between expected power loss and measured average loss as the number of vertically correlated groups increases. A larger number of correlated groups represents a stronger positive vertical correlation. The calibrated loss is the sum of modeled loss and estimated 667 mW overhead.

667 mW overhead, and expected loss are compared in Fig. 29. The average loss of a fully-coupled DPP system decreases when  $\rho_V$  increases, validating the conclusions in Section V. Again, the tracking match is as tight as the power measurement tolerance supports, and error bounds are highlighted.

#### VII. CONCLUSION

This paper explores scaling of DPP systems by means of stochastic models. An analytical framework is developed to estimate average power loss of a DPP topology under probabilistic load distributions. Scaling factors are introduced to describe how power loss scales as the dimension (N, M), average load power  $(\mu_0)$ , and load power variance  $(\sigma_0^2)$  of a modular load array change. The scaling characteristics of general DPP topologies were analyzed and compared, providing useful design guidelines for selecting DPP topologies. The analytical framework was verified by SPICE simulations and experimental results. The results show that many DPP topologies reduce power loss substantially even with power coefficients of variance as high as 1, with greater benefits as variance decreases. The results also indicate that in a DPP system with relatively balanced load, power loss caused by differential power processing will be low. Switching loss, core loss, and other static losses may be significant. The analytical framework, scaling factors, and stochastic models provide useful guidelines for designing large-scale DPP systems.

## APPENDIX I

## DERIVATIONS OF THE EXPECTED POWER LOSS

This appendix derives expected power loss for the stochastic model under conditions of independent loads and of correlated loads. Definitions and constraints are the same as those introduced in Sections II and V.

## A. Expected Power Loss with Independent Load

In Section II, the stochastic model is developed based on independent and identically distributed (i.i.d.) individual load powers  $P_{ij}(t)$ . With this condition, the domain powers  $P_i(t)$  are also i.i.d..

For the conventional reference converter, loss is related to total load power, and the expected value in (5) can be derived as

$$\mathbb{E}[P_{loss}(t)] = \frac{R_{out}}{V_0^2} \mathbb{E}\left[\left(\sum_{i=1}^N P_i(t)\right)^2\right]$$

$$= \frac{R_{out}}{V_0^2} \left\{\sum_{i=1}^N \mathbb{E}[P_i^2(t)] + 2\sum_{1 \le i < j \le N} \mathbb{E}[P_i(t)P_j(t)]\right\}$$

$$\stackrel{\text{(i)}}{=} \frac{R_{out}}{V_0^2} \left(N\mathbb{E}[P_i^2(t)] + N(N-1)\mathbb{E}^2[P_i(t)]\right). \tag{19}$$

Here, line (i) follows because  $P_i$  values are i.i.d.. Therefore,  $\mathbb{E}[P_i(t)]$  and  $\mathbb{E}[P_i^2(t)]$  are identical for i=1,...,N, and  $\mathbb{E}[P_i(t)P_j(t)] = \mathbb{E}^2[P_i(t)]$  for any  $i \neq j$ . Considering  $P_i(t) = P_{i1}(t) + ... + P_{iM}(t)$ , where  $P_{i1}(t),...,P_{iM}(t)$  are also i.i.d.,  $\mathbb{E}[P_i^2(t)]$  and  $\mathbb{E}^2[P_i(t)]$  in (19) can be expanded to

$$\mathbb{E}[P_i^2(t)] = M\mathbb{E}[P_{ij}^2(t)] + M(M-1)\mathbb{E}^2[P_{ij}(t)],$$

$$\mathbb{E}^2[P_i(t)] = (M\mathbb{E}[P_{ij}(t)])^2 = M^2\mathbb{E}^2[P_{ij}(t)].$$

(20)

Substituting (20) into (19), the expected power loss is

$$\mathbb{E}[P_{loss}(t)] = \frac{R_{out}}{V_0^2} \left\{ MN \left( \mathbb{E}[P_{ij}^2(t)] - \mathbb{E}^2[P_{ij}(t)] \right) + M^2 N^2 \mathbb{E}^2[P_{ij}(t)] \right\}$$

$$\stackrel{(i)}{=} \frac{R_{out}}{V_0^2} \left( MN \underbrace{\text{Var}[P_{ij}(t)]}_{=\sigma_2^2} + M^2 N^2 \underbrace{\mathbb{E}^2[P_{ij}(t)]}_{\mu_2^2} \right). \tag{21}$$

Line (i) is based on  $Var[X] = \mathbb{E}[X^2] - \mathbb{E}^2[X]$ .

To calculate expected loss of DPP converters,  $P_i'(t) = P_i(t) - \mathbb{E}[P_i(t)]$  is defined to subtract out the mean value  $M\mu_0$  of  $P_i(t)$ , so that  $E[P_i'(t)] = 0$ . The i.i.d. property still holds for  $P_i'(t)$ . For a fully-coupled DPP with this loading condition, instantaneous power loss at each port has the same probability distribution. The expected power loss at the  $i^{th}$  port can be derived from (6) as

$$\mathbb{E}[P_{loss.i}(t)] \stackrel{\text{(i)}}{=} \frac{R_{out}}{V_0^2} \mathbb{E}\left[\left(\frac{\sum_{k=1}^N P_k'(t)}{N} - P_i'(t)\right)^2\right]$$

$$= \frac{R_{out}}{V_0^2} \mathbb{E}\left[\left(\sum_{k \neq i} \frac{1}{N} P_k'(t) + \frac{1-N}{N} P_i'(t)\right)^2\right]$$

$$\stackrel{\text{(ii)}}{=} \frac{R_{out}}{V_0^2} \left\{\sum_{k \neq i} \frac{1}{N^2} \mathbb{E}[P_k'^2(t)] + \frac{(1-N)^2}{N^2} \mathbb{E}[P_i'^2(t)]\right\}$$

$$\stackrel{\text{(iii)}}{=} \frac{R_{out}}{V_0^2} \frac{N-1}{N} \mathbb{E}[P_i'^2(t)]$$

$$\stackrel{\text{(iv)}}{=} \frac{R_{out}}{V_0^2} \frac{N-1}{N} \left(\mathbb{E}[P_i^2(t)] - \mathbb{E}^2[P_i(t)]\right)$$

$$= \frac{R_{out}}{V_0^2} \frac{N-1}{N} \text{Var}[P_i(t)]$$

$$\stackrel{\text{(v)}}{=} \frac{R_{out}}{V_0^2} \frac{M(N-1)}{N} \underbrace{\text{Var}[P_{ij}(t)]}_{-\sigma^2}.$$

(22)

Here, lines (i) and (iv) change the variables between  $P_i(t)$  and  $P_i^{'}(t)$ ; (ii) follows because  $P_1^{'}(t),...,P_N^{'}(t)$  are independent with zero mean, and hence  $\mathbb{E}[P_i^{'}(t)P_j^{'}(t)]=0$  for any  $i\neq j$ ; (iii) follows because  $P_i^{'}(t)$  values are identically distributed, and hence  $\mathbb{E}[P_i^{'2}(t)]$  is the same for all i; (v) follows because all  $P_{ij}(t)$  values are i.i.d., and hence  $\mathrm{Var}[P_i(t)]=\mathrm{Var}[P_{i1}(t)+...+P_{iM}(t)]=M\mathrm{Var}[P_{ij}(t)].$

In a ladder DPP, power loss varies among submodules. Similar to (22), the expected power loss at the  $i^{th}$  submodule can be calculated from (9) as

$$\mathbb{E}[P_{loss.i}(t)] = \frac{R_{out}}{V_0^2} \mathbb{E}\left[\left(i\overline{P}'(t) - \sum_{k=1}^{i} P_k'(t)\right)^2\right] \\

= \frac{R_{out}}{V_0^2} \mathbb{E}\left[\left(\sum_{k=1}^{i} \left(\frac{i}{N} - 1\right) P_k'(t) + \sum_{k=i+1}^{N} \frac{i}{N} P_k'(t)\right)^2\right] \\

= \frac{R_{out}}{V_0^2} \left\{\sum_{k=1}^{i} \left(\frac{i}{N} - 1\right)^2 \mathbb{E}[P_k'^2(t)] + \sum_{k=i+1}^{N} \frac{i^2}{N^2} \mathbb{E}[P_k'^2(t)]\right\} \\

= \frac{R_{out}}{V_0^2} \frac{(N-i)i}{N} \mathbb{E}[P_k'^2(t)] \\

= \frac{R_{out}}{V_0^2} \frac{M(N-i)i}{N} \underbrace{\operatorname{Var}[P_{ij}(t)]}_{-\sigma^2}.$$

(23)

## B. Expected Power Loss with Correlated Load

In Section V, load correlation is considered to generalize the stochastic loss model. The i.i.d. condition is relaxed so that each load power has identical probability distribution but is not necessarily independent. In this case,  $\mathbb{E}[P_{ij}(t)]$  and  $\mathrm{Var}[P_{ij}(t)]$  are still identical for each load;  $\mathbb{E}[P_i(t)] = M\mu_0$  is identical for each domain, but  $\mathrm{Var}[P_i(t)] = M\sigma_0^2 + 2\sum_{k\neq l} \mathrm{Cov}[P_{ik}(t), P_{il}(t)]$  might vary among domains due to load correlation. In this case, expected total power loss of a fully-coupled DPP in (14) can be derived as

$$\mathbb{E}[P_{loss}(t)] = \frac{R_{out}}{V_0^2} \mathbb{E} \left[ \sum_{k=1}^{N} \left( \overline{P}(t) - P_k(t) \right)^2 \right] \\

= \frac{R_{out}}{V_0^2} \mathbb{E} \left[ \frac{1}{N} \left( (N-1) \sum_{k=1}^{N} P_k^2(t) - 2 \sum_{1 \le i < j \le N} P_i(t) P_j(t) \right) \right] \\

= \frac{R_{out}}{NV_0^2} \left\{ (N-1) \sum_{k=1}^{N} \mathbb{E}[P_k^2(t)] - 2 \sum_{1 \le i < j \le N} \mathbb{E}[P_i(t) P_j(t)] \right\} \\

\stackrel{\text{(i)}}{=} \frac{R_{out}}{NV_0^2} \left\{ (N-1) \sum_{k=1}^{N} \left( \mathbb{E}[P_k^2(t)] - \mathbb{E}^2[P_k(t)] \right) - 2 \sum_{1 \le i < j \le N} \text{Cov}[P_i(t), P_j(t)] \right\} \\

= \frac{R_{out}}{NV_0^2} \left\{ (N-1) \sum_{k=1}^{N} \text{Var}[P_k(t)] - 2 \sum_{1 \le i < j \le N} \text{Cov}[P_i(t), P_j(t)] \right\}. (24)$$

Fig. 30. Power consumption waveforms of two example voltage domains when the data storage server is running a random read/write program.

Fig. 31. Probability distribution and correlation of the two example domain powers: (a) power distribution histogram of domain A; (b) power distribution of domain B; (c) correlation plot of domain A power and domain B power.

Line (i) follows because  $\mathbb{E}[P_i(t)P_j(t)] = \mathbb{E}[P_i(t)] \times \mathbb{E}[P_j(t)] + \text{Cov}[P_i(t), P_j(t)]$ , and  $\mathbb{E}[P_i(t)]$  are identical for i = 1, ..., N. Eq. (17) can be obtained by rearranging (24) as

$$\mathbb{E}[P_{loss}(t)] = \frac{R_{out}}{NV_0^2} \left\{ N \sum_{k=1}^N \text{Var}[P_k(t)] - \left( \sum_{k=1}^N \text{Var}[P_k(t)] + 2 \sum_{1 \le i < j \le N} \text{Cov}[P_i(t), P_j(t)] \right) \right\}$$

$$\stackrel{\text{(i)}}{=} \frac{R_{out}}{V_0^2} \left\{ \sum_{k=1}^N \text{Var}[P_k(t)] - \frac{\text{Var}\left[\sum_{k=1}^N P_k(t)\right]}{N} \right\}. \tag{25}$$

Here, (i) holds because  $\operatorname{Var}[X_1 + X_2... + X_N] = \sum_{k=1}^N \operatorname{Var}[X_k] + 2\sum_{k \neq l} \operatorname{Cov}[X_k, X_l].$

## APPENDIX II APPLICATION STUDY AND MODEL VERIFICATION ON A DATA STORAGE SERVER

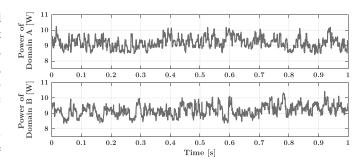

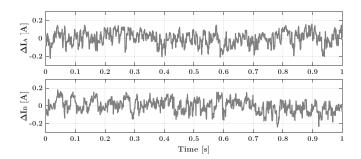

To further verify the model in a practical application, we recorded the power profiles of a data storage server (in [22]) and applied them to a SPICE simulation (PLECS v4.5). The data storage server contains ten series voltage domains. Each domain supplies 5 V to multiple parallel hard disk drives (HDDs). A random read/write program was running on the server. Fig. 30 shows power waveforms of two example voltage domains. Probability distributions of the two domain powers and their correlation are plotted in Fig. 31. Fig. 31 indicates that the measured ten domain powers are i.i.d.. Differential current waveforms of the two example voltage domains are plotted in Fig. 32.

In the SPICE simulation, a DPP system with ten series domains was built and supported by an ac fully-coupled DPP

| _ | Domain              | #1   | #2   | #3   | #4   | #5   | #6   | #7   | #8   | #9   | #10  | Simulated<br>Domain<br>Average | Simulated<br>Total<br>System | Modeled<br>Total<br>System |

|---|---------------------|------|------|------|------|------|------|------|------|------|------|--------------------------------|------------------------------|----------------------------|

| _ | Average Power [W]   | 9.10 | 9.17 | 9.13 | 9.21 | 9.19 | 9.12 | 9.10 | 9.17 | 9.19 | 9.19 | 9.16                           | 91.6                         | 91.6                       |

|   | DPP Power Loss [mW] | 2 73 | 2.62 | 2.51 | 2.52 | 2 67 | 2.66 | 2.68 | 2 53 | 2 46 | 2.70 | 2.61                           | 26.1                         | 24.5                       |

TABLE V AVERAGE POWER CONSUMPTION AND DPP POWER LOSS OF EACH VOLTAGE DOMAIN AND OF THE TOTAL SYSTEM

<sup>&</sup>lt;sup>†</sup> The system operated for 60 seconds. Conduction losses are considered. Switching loss, core loss, control, and other auxiliary losses are not included.

Fig. 32. Differential current ( $\Delta I_i$ ) of the two example voltage domains.

converter (Fig. 6a). Here, each domain contains one random load with the recorded domain power profile, so in this system  $N=10, M=1, V_0=5$  V,  $\mu_0=9.2$  W, and  $\sigma_0^2=0.17$  W<sup>2</sup>. For the DPP converter, each switch  $R_{ds(on)}$  is set as  $0.1~\Omega$  and each winding resistance is set as  $0.2~\Omega$ , yielding  $R_{out}=0.4~\Omega$ . Table V lists the average power consumption and DPP power loss of each voltage domain and of the total system. It also compares the modeled system power loss (based on (8)) to the simulated system loss (24.5 mW) is within 6% of the simulated system loss (26.1 mW), validating the stochastic loss model.

#### REFERENCES

- P. Wang, R. C. N. Pilawa-Podgurski, P. T. Krein and M. Chen, "Performance Limits of Differential Power Processing," *Proc. IEEE Workshop Control Model. Power Electron.*, Aalborg, Denmark, 2020, pp. 1-8.

- [2] G. L. Brainard, "Non-dissipative Battery Charger Equalizer," U.S. Patent 5479083, Dec. 26, 1995.

- [3] Y. S. Lee and M. W. Cheng, "Intelligent Control Battery Equalization for Series Connected Lithium-ion Battery Strings," *IEEE Trans. Ind. Electron.*, vol. 52, no. 5, pp. 1297-1307, Oct. 2005.

- [4] C. Pascual and P. T. Krein, "Switched Capacitor System for Automatic Series Battery Equalization," in *Proc. IEEE Appl. Power Electron. Conf. Expo.*, 1997, pp. 848-854.

- [5] Y. Ye, K. W. E. Cheng, Y. C. Fong, X. Xue and J. Lin, "Topology, Modeling, and Design of Switched-Capacitor-based Cell Balancing Systems and Their Balancing Exploration," *IEEE Trans. Power Electron.*, vol. 32, no. 6, pp. 4444-4454, June 2017.

- [6] H. Schmidt and C. Siedle, "The Charge Equalizer-A New System to Extend Battery Lifetime in Photovoltaic Systems, UPS and Electric Vehicles," Proc. IEEE Int. Telecom. Energy Conf., 1993, pp. 146-151.

- [7] S. T. Hung, D. C. Hopkins and C. R. Mosling, "Extension of Battery Life via Charge Equalization Control," *IEEE Trans. Ind. Electron.*, vol. 40, no. 1, pp. 96-104, Feb. 1993.

- [8] A. M. Imtiaz and F. H. Khan, "Time Shared Flyback Converter' based Regenerative Cell Balancing Technique for Series Connected Li-Ion Battery Strings," *IEEE Trans. Power Electron.*, vol. 28, no. 12, pp. 5960-5975, Dec. 2013.

- [9] N. H. Kutkut, D. M. Divan and D. W. Novotny, "Charge Equalization for Series Connected Battery Strings," *IEEE Trans. Ind. Appl.*, vol. 31, no. 3, pp. 562-568, May-June 1995.

- [10] S. K. Dam and V. John, "A Modular Fast Cell-to-Cell Battery Voltage Equalizer," *IEEE Trans. Power Electron.*, vol. 35, no. 9, pp. 9443-9461, Sept. 2020.

- [11] M. Evzelman, M. M. Ur Rehman, K. Hathaway, R. Zane, D. Costinett and D. Maksimovic, "Active Balancing System for Electric Vehicles with Incorporated Low-Voltage Bus," *IEEE Trans. Power Electron.*, vol. 31, no. 11, pp. 7887-7895, Nov. 2016.

- [12] M. Liu, Y. Chen, Y. Elasser and M. Chen, "Dual Frequency Hierarchical Modular Multilayer Battery Balancer Architecture," *IEEE Trans. Power Electron.*, vol. 36, no. 3, pp. 3099-3110, March 2021.

- [13] T. Shimizu, M. Hirakata, T. Kamezawa and H. Watanabe, "Generation Control Circuit for Photovoltaic Modules," *IEEE Trans. Power Electron.*, vol. 16, no. 3, pp. 293-300, May 2001.

- [14] G. R. Walker and J. C. Pierce, "Photovoltaic DC-DC Module Integrated Converter for Novel Cascaded and Bypass Grid Connection Topologies - Design and Optimization," in *Proc. IEEE Power Electron. Spec. Conf.*, 2006, pp. 1-7.

- [15] C. Olalla, D. Clement, M. Rodriguez and D. Maksimovic, "Architectures and Control of Submodule Integrated DC-DC Converters for Photovoltaic Applications," *IEEE Trans. Power Electron.*, vol. 28, no. 6, pp. 2980-2997, June 2013.

- [16] J. T. Stauth, M. D. Seeman, and K. Kesarwani, "Resonant Switched-Capacitor Converters for Sub-Module Distributed Photovoltaic Power Management," *IEEE Trans. Power Electron.*, vol. 28, no. 3, pp. 1189–1198, March 2013.

- [17] S. Qin, S. T. Cady, A. D. Domínguez-García and R. C. N. Pilawa-Podgurski, "A Distributed Approach to Maximum Power Point Tracking for Photovoltaic Submodule Differential Power Processing," *IEEE Trans. Power Electron.*, vol. 30, no. 4, pp. 2024-2040, April 2015.

- [18] A. H. Chang, A. Avestruz and S. B. Leeb, "Capacitor-Less Photovoltaic Cell-Level Power Balancing using Diffusion Charge Redistribution," *IEEE Trans. Power Electron.*, vol. 30, no. 2, pp. 537-546, Feb. 2015.

- [19] C. Liu, D. Li, Y. Zheng and B. Lehman, "Modular Differential Power Processing (mDPP)," in *Proc. IEEE Workshop Control Model. Power Electron.*, 2017, pp. 1-7.

- [20] Y. Jeon, H. Lee, K. A. Kim and J. Park, "Least Power Point Tracking Method for Photovoltaic Differential Power Processing Systems," *IEEE Trans. Power Electron.*, vol. 32, no. 3, pp. 1941-1951, March 2017.

- [21] H. Jeong, S. Park, J. Jung, T. Kim, A. -R. Kim and K. A. Kim, "Segmented Differential Power Processing Converter Unit and Control Algorithm for Photovoltaic Systems," *IEEE Trans. Power Electron.*.

- [22] P. Wang, Y. Chen, J. Yuan, R. C. N. Pilawa-Podgurski and M. Chen, "Differential Power Processing for Ultra-Efficient Data Storage," *IEEE Trans. Power Electron.*, vol. 36, no. 4, pp. 4269-4286, April 2021.

- [23] E. Candan, P. S. Shenoy and R. C. N. Pilawa-Podgurski, "A Series-Stacked Power Delivery Architecture with Isolated Differential Power Conversion for Data Centers," *IEEE Trans. Power Electron.*, vol. 31, no. 5, pp. 3690-3703, May 2016.

- [24] A. Stillwell and R. C. N. Pilawa-Podgurski, "A Resonant Switched-Capacitor Converter with GaN Transistors for Series-Stacked Processors with 99.8% Power Delivery Efficiency," in *Proc. IEEE Energy Convers. Cong. Expo.*, 2015, pp. 563–570.

- [25] P. S. Shenoy and P. T. Krein, "Differential Power Processing for DC Systems," *IEEE Trans. Power Electron.*, vol. 28, no. 4, pp. 1795-1806, April 2013.

- [26] P. T. Krein, R. H. Campbell, N. R. Shanbhag, "System and method for improving power conversion for advanced electronic circuits," U.S. Patent 9116692, August 25, 2015.

- [27] M. Kasper, D. Bortis, and J. W. Kolar, "Unified Power Flow Analysis of String Current Diverters," *Electr. Eng.*, vol. 100, no. 3, pp. 2085-2094, Sep. 2018.

- [28] Y. Cao, J. A. Magerko, T. Navidi and P. T. Krein, "Power Electronics Implementation of Dynamic Thermal Inertia to Offset Stochastic Solar

- Resources in Low-Energy Buildings," *IEEE Trans. Emerg. Sel. Topics Power Electron.*, vol. 4, no. 4, pp. 1430-1441, Dec. 2016.

- [29] P. T. Krein and J. A. Galtieri, "Active Management of Photovoltaic System Variability with Power Electronics," *IEEE Trans. Emerg. Sel. Topics Power Electron.*.

- [30] K. A. Kim, P. S. Shenoy and P. T. Krein, "Converter Rating Analysis for Photovoltaic Differential Power Processing Systems," *IEEE Trans. Power Electron.*, vol. 30, no. 4, pp. 1987-1997, April 2015.

- [31] P. S. Shenoy, K. A. Kim, B. B. Johnson and P. T. Krein, "Differential Power Processing for Increased Energy Production and Reliability of Photovoltaic Systems," *IEEE Trans. Power Electron.*, vol. 28, no. 6, pp. 2968-2979, June 2013.