# A Low-Power Front-End with Compressive sensing Circuit for Neural Signal Acquisition Designed in 180 nm CMOS Process

Karthik Kakaraparty, Nishat Tasneem, and Ifana Mahbub Department of Electrical Engineering University of North Texas Denton, USA Karthik.Kakaraparthy@gmail.com

Abstract-Multi-channel data acquisition of bio-signals is a promising technology that is being used in many fields these days. Compressed sensing (CS) is an innovative approach of signal processing that facilitates sub-Nyquist processing of bio-signals such as an electrocardiogram (ECG) and electroencephalogram (EEG). This strategy can be used to lower the data rate to realize ultra low power performance, As the count of recording channels increase, data volume is increased resulting in impermissible transmitting power. In this paper, the implementation of a CMOS based front-end design for CS using standard 180 nm technology is presented. A novel pseudo-random sequence generator is proposed, which consists of two different types of D flip-flops that are used for obtaining a completely random sequence. The power consumed by the bio-signal amplifier block is 277  $\mu W$ . The SAR-ADC block that is designed to digitize the amplified signal consumes 2.35  $\mu W$  of power and the power consumption value of pseudo-random bit sequence generator (PRBS) is 546  $\mu W$ . The low power consumption per channel confirms the importance of the proposed approach for multiple channel high-density neural interfaces.

*Index Terms*—Compressive sensing, Pseudo random sequence generator, LFSR, Pseudo Random sampling, Sub-Nyquist Sampling.

## I. INTRODUCTION

Compressive sensing (CS) as the name suggests, is an approach of the acquisition of the data itself that is implemented in an efficient and compressive way. The signals can be interpreted sparsely or in a compressible way, Based on signals that are sparsed, The compressed sensing method lets us sample the Signals at a much lower rate than that of the conventional sampling rate that is suggested by the Nyquist sampling theory [1].

CS lets the original signal to be faithfully reconstructed back from the pseudo-randomly sampled signal which needs far fewer data bits when compared to the signal sampled using the conventional Nyquist sampling approach. In the applications specifically in domains where there are high data rates and low-power constraints CS can play important role in performing the tasks efficiently. For example, in the medical imaging domain, the speed or the data rate is the highest priority. In the circuit implementation of the data compression of the physiological signals such as EEG, ECG [2], low power

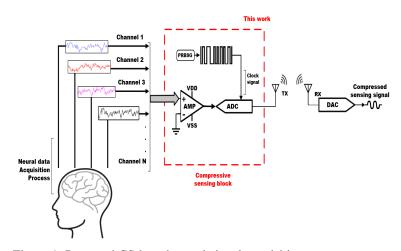

Figure 1: Proposed CS-based neural signal acquisition system.

consumption is considered as the highest priority. While other strong survey articles are available in CS literature [3], [4]. CS strategy is used in many biomedical applications such as signal processing of bio-signals, efficient neural signal acquisition, genomic sensing, and bacterial composition reconstruction. Here, in this paper, the application of neural signal acquisition based on CS is emphasized.

## II. COMPRESSED SENSING METHODOLOGY

# A. Primary objective

The chief objective of our work is to implement a CMOS based circuit which can compressively acquire the EEG/ ECG data without actually losing the essence of the original data. This CS strategy results in the reduced amount of data needed for transmission and thus results in reduction in the power required for data transmission.

#### B. Conventional CS Methodologies

The method of detection of spikes based on the threshold values [5] is commonly used for compression of data of biosignals based on activity parameters. It transmits the spikeactivity signal segments while omitting the segments of signal that wont involve any essential spike activity. The threshold crossing detection method is the most common spike detection method. However, this approach retains the spike's shape While discarding the inter-spike signal, which involves undetected spikes and other significant neural voltage variations. As the research scholars are interested in the analysis of the entire neural signal, this compression approach can not be used.

The nearly lossless alternative of the wavelet transform based compression approach which involves the off-chip transmission of only the important coefficients values of wavelet after the signals are converted into their wavelet representations using an on-chip circuit. Wavelet transform systems allow for impressive compression rates, thus ensuring excellent efficiency for the signal reconstruction [6]. However, in terms of the power and area consumption, wavelet transformation based on the ASIC implementation is insignificant as it involves the digital filter implementation and memories that are on-chip running at faster rate than the Nyquist sampling rate.

The conventional multi-channel compressive sensing (MCS) architecture has many problems, For Instance, the need for analog to digital converter (ADC) with high resolution. [7] Improving the conventional MCS architecture, there is another architecture consisting of a block of multiple inputs with single output compressive sensing (MISOCS) which utilises the methodology to embed data present in all channels into each sample of the compressed signal. [8].

Proceeding further in improving this CS system architecture, there is another methodology that involves implementing an optimized neural signal recording system for wireless compressed sensing [9], [10]. The system benefits from both integrated circuits which are custom and compatible wireless solutions. An wireless system-on-chip (SoC) which is implantable and an external relay which is wireless based are involved in their proposed system. Another approach in implementing the CS is involved in the design of a system-onchip (SoC) CS current sensor using bipolar 0.16  $\mu m$  CMOS-DMOS technology. For the data rate reduction, two current sensing cores which are broadband, each constitutes of a 9bit ADC and Hall-effect probe are integrated together monolithically with a multiple mode digital compressive sensing encoder (DCSE) [8], [11].

# III. DESIGN ARCHITECTURE

Even though all the previously proposed methodologies are achieving the improvement in the compressed sensing performance [12], however low power consumption criteria have been compromised to significant level. Thus, we have proposed a simple and novel CS system design block giving the highest priority to the low power consumption criteria. To address the problem of high power consumption in a multichannel neural data acquisition system, a new CS system is proposed. In this proposed design, unlike the conventional CS strategy [13] where the input analog signal is multiplied with a random sequence using a Gilbert multiplier which alone consumes 10 mW power with a supply of 1.8 V, we have proposed a new strategy, that is to use this random sequence

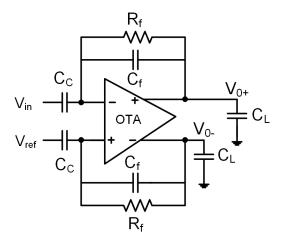

Figure 2: Schematic of the closed-loop amplifier.

as a clock to the ADC block and feed the analog neural data signal as input directly to the ADC. The proposed approach is also presented in Fig.1, the entire proposed CS system consumes the total power of  $825.35 \ \mu m$  which is significantly less amount when compared to the power consumed by Gilbert multiplier [14] alone in the conventional methodology. The individual sub-blocks that are involved in the proposed CS system are discussed in the upcoming sub-sections III-A, III-B, III-C respectively.

### A. Neural amplifier

This paper presents a fully-differential neural amplifier with a capacitive-resistive feedback network [15]. A folded-cascode (FC) architecture is used as the operational transconductance amplifier (OTA) [16]. The FC-OTA which achieves wider swing in the signal along with high gain is presented in this paper. The complete amplifier schematic with the closed-loop is presented in Fig.2. The reference input of the amplifier uses the reference neural electrode data. Two DC-blocking

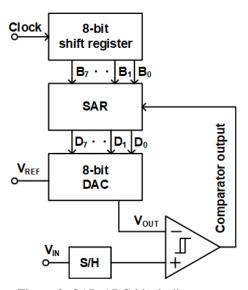

Figure 3: SAR-ADC block diagram.

capacitors are connected to each of the inputs to block the DC component from the inputs. This amplifier design gives enhanced performance in terms of gain-bandwidth (GBW). The neural amplifier achieves a gain of 50.3 dB within the neural signal bandwidth of 0.1 Hz - 5 kHz.

# B. ADC

To digitize the amplified version of input neural data from the designed amplifier, a successive approximation register analog-to-digital converter (SAR-ADC) is designed in the 180 nm CMOS process [16]. The block diagram of the SAR-ADC is shown in Fig.3. It consists of the 8-bit shift register, SAR logic block, DAC (digital-to-analog converter), and a dynamic comparator. This SAR-ADC has a sampling rate ranging from 10 to 40 kHz and consumes a 277  $\mu W$  of power.

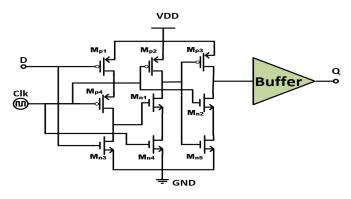

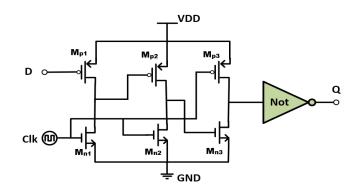

# C. Pseudo random bit sequence (PRBS) generator block

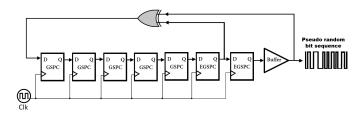

Even before designing the PRBS block, we ask ourselves the following questions: Can we generate a long random bit sequence without compromising the low power criteria? Can this random bit sequence be generated using fewer components when compared to conventional methods that involve complex design blocks? [17] The conventional way to implement the pseudo-random bit sequence (PRBS) generator is to use 14 Dflip flops, 2 xors, and one Mux [18]. As this method involves more number of register blocks (D-flip flops) resulting in a significant increase in power consumption, we have proposed a simple PRBS block through efficient usage of components. The Proposed pseudo-random bit sequence topology consists of two different types of D-flip flops which are responsible to attain a high data rate simultaneously satisfying the lowpower and low area constraints. Two extended genuinely single-phase clock (E-GSPC) logic dependent D-flip flops are used to shorten the critical path delay and thus boost the data rate. The power consumption value of pseudo-random bit sequence generator (PRBS) is 546  $\mu W$  at 1.8-V VDD including the clock buffer. The E-GSPC, GSPC D-flip flops along with an XOR and buffer constitutes to form the proposed PRBS generator block. An XOR gate is used to maintain the randomness of the generated bit sequence and a feedback loop is used for the repetition of the random signal sequence. Unlike the conventional methods where 14 D-flip flops, 2 XOR's, and one Mux are used to generate random bit sequence [18], this proposed PRBS block is simply built with just 7 D-flip flops, XOR, and a buffer. There is a possibility of dynamic flip flops losing their states when the PRBS block is made to run with a slow sequence rate. So, while designing the PRBS block we made sure that there is no loss of the state in D-flip flops.

# **IV. SIMULATION RESULTS**

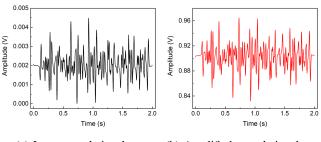

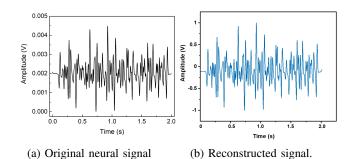

A previously recorded neural signal as shown in Fig.10a, whose maximum amplitude is 4 mV is imported in the Cadence Virtuoso Custom IC design tool to be used as an input to the amplifier. The resultant amplified version of the neural signal has its peak amplitude as 0.96 V. The mid-band gain of the designed amplifier is 50.3 dB.

Figure 4: Pseudo random bit sequence block.

Figure 5: Schematic of Genuinely Single-phased clock dependent D-flip flop.

Figure 6: Schematic of Extended Genuinely Single-phased clock dependent D-flip flop.

(a) Input neural signal(b) Amplified neural signalFigure 7: Simulation results of the proposed neural amplifier

Figure 9: Output of the PRBS block.

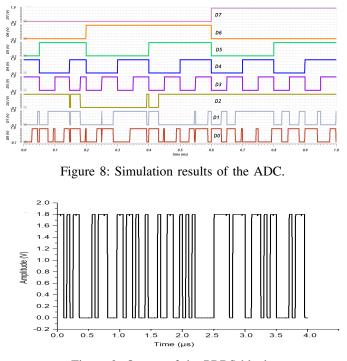

In this paper, we have considered collecting neural data from the 32 channels, each sampled at 20 KS/s with an 8bit SAR-ADC, making the total data rate of  $32 \times 20$  K×8. The analog neural data from one channel among the 32 channels is considered and its equivalent digitized version with the 8-bit resolution is presented in Fig.8.

The amplitude of this PRBS is 1.8 V. A transient run for 4  $\mu$ sec time-frame is done and the output of the proposed pseudorandom bit sequence generator is shown in Fig.9. To verify the quality of reconstruction of the original signal from the compressively sensed signal, the digitized output data is given as an input to Ideal ADC and the corresponding reconstructed signal is presented in Fig. 10b.

The output of SAR-ADC is reconstructed using an Ideal DAC (digital to analog converter) in LabVIEW (Laboratory Virtual Instrument Engineering Workbench) software and the resultant output is presented in Fig. 10b.

# V. CONCLUSION

This paper proposes the design of a novel compressed sensing system which is implemented using 180 nm CMOS technology. The highest priority is given to the low power consumption of the proposed novel CS system design. The proposed CS-based neural acquisition system needs 825.35  $\mu W$  of power, the performance and power consumption results show the significance of the proposed approach.

## ACKNOWLEDGMENT

The Work which we have presented in this paper is supported by the National Science Foundation (NSF) under Grant Number ECCS 1943990.

Figure 10: Comparision between original and reconstructed signal.

| TT 1 1 T | a • •       |           | •      | 1     |

|----------|-------------|-----------|--------|-------|

| Table 1  | Comparision | among pre | 2VIOUS | works |

|          |             |           |        |       |

|                         | Comparision of works |                   |              |

|-------------------------|----------------------|-------------------|--------------|

| Parameters              | Tsung [19]           | O.U Khan [20]     | This Work    |

| CMOS Technology         | 180nm                | 180nm             | 180nm        |

| Signal type             | ECG                  | Sinusoidal signal | Neural       |

| Compression methodology | Algorithm based      | CS                | CS           |

| No. of channels         | 2                    | NA                | 32           |

| Sampling rate           | 90 MHz               | 1.2 GHz           | 10 to 40 kHz |

| Power consumption       | 6.7 mW               | 11.2 mW           | 825.35 µW    |

#### REFERENCES

- E. Crespo Marques, N. Maciel, L. Naviner, H. Cai, and J. Yang, "A review of sparse recovery algorithms," *IEEE Access*, vol. 7, pp. 1300– 1322, 2019.

- [2] H. Kuo, Y. Lin, and A. Wu, "Compressive sensing based ecg monitoring with effective af detection," in 2017 IEEE International Conference on Acoustics, Speech and Signal Processing (ICASSP), 2017, pp. 1008– 1012.

- [3] K. V. Siddamal, S. P. Bhat, and V. S. Saroja, "A survey on compressive sensing," in 2015 2nd International Conference on Electronics and Communication Systems (ICECS), 2015, pp. 639–643.

- [4] M. Rani, S. B. Dhok, and R. B. Deshmukh, "A systematic review of compressive sensing: Concepts, implementations and applications," *IEEE Access*, vol. 6, pp. 4875–4894, 2018.

- [5] A. Sarje and P. Abshire, "Low power cmos circuit for spike detection," in SENSORS, 2011 IEEE, 2011, pp. 928–931.

- [6] P. Turcza, "A wavelet-based compression for neural recording system," in 2016 International Conference on Signals and Electronic Systems (ICSES), 2016, pp. 33–36.

- [7] R. Ranjandish and A. Schmid, "A sub- µW /channel, 16-channel seizure detection and signal acquisition soc based on multichannel compressive sensing," *IEEE Transactions on Circuits and Systems II: Express Briefs*, vol. 65, no. 10, pp. 1400–1404, 2018.

- [8] D. Bellasi, M. Crescentini, D. Cristaudo, A. Romani, M. Tartagni, and L. Benini, "A broadband multi-mode compressive sensing current sensor soc in 0.16 μ m cmos," *IEEE Transactions on Circuits and Systems I: Regular Papers*, vol. 66, no. 1, pp. 105–118, 2019.

- [9] J. Zhang, Y. Suo, S. Mitra, S. Chin, S. Hsiao, R. F. Yazicioglu, T. D. Tran, and R. Etienne-Cummings, "An efficient and compact compressed sensing microsystem for implantable neural recordings," *IEEE Transactions on Biomedical Circuits and Systems*, vol. 8, no. 4, pp. 485–496, 2014.

- [10] M. Shoaran, M. H. Kamal, C. Pollo, P. Vandergheynst, and A. Schmid, "Compact low-power cortical recording architecture for compressive multichannel data acquisition," *IEEE Transactions on Biomedical Circuits and Systems*, vol. 8, no. 6, pp. 857–870, 2014.

- [11] X. Liu, M. Zhang, T. Xiong, A. G. Richardson, T. H. Lucas, P. S. Chin, R. Etienne-Cummings, T. D. Tran, and J. Van der Spiegel, "A fully integrated wireless compressed sensing neural signal acquisition system for chronic recording and brain machine interface," *IEEE Transactions* on Biomedical Circuits and Systems, vol. 10, no. 4, pp. 874–883, 2016.

- [12] J. Zhang, T. Xiong, S. Mitra, Y. Suo, T. D. Tran, R. Firat Yazicioglu, and R. Etienne-Cummings, "Live demonstration: A closed loop compressive sensing neural recording system," in 2014 IEEE Biomedical Circuits and Systems Conference (BioCAS) Proceedings, 2014, pp. 170–170.

- [13] H. Nouasria and M. Et-Tolba, "New sensing approach for compressive sensing using sparsity domain," in 2018 19th IEEE Mediterranean Electrotechnical Conference (MELECON), 2018, pp. 20–24.

- [14] H. Ghayvat, L. Bandil, S. C. Mukhopadhyay, and R. Gupta, "A 2.4ghz cmos gilbert mixer in 180nm technology," in 2015 Fifth International Conference on Communication Systems and Network Technologies, 2015, pp. 781–785.

- [15] N. T. Tasneem and I. Mahbub, "Design of a 52.5 db neural amplifier with noise-power trade-off," in 2019 IEEE 62nd International Midwest Symposium on Circuits and Systems (MWSCAS). IEEE, 2019, pp. 921– 924.

- [16] N. T. Tasneem, D. K. Biswas, P. R. Adhikari, R. Reid, and I. Mahbub, "Design of a reverse-electrowetting transducer based wireless selfpowered motion sensor," in 2020 IEEE International Symposium on Circuits and Systems (ISCAS). IEEE, 2020, pp. 1–5.

- [17] C. Wu, J. Jou, H. Ting, S. Chu, and B. Liu, "Multi-channel multi-gigabit prbs generator with a built-in clock in 0.18-m cmos technology," in 2017 International SoC Design Conference (ISOCC), 2017, pp. 276–277.

- [18] F. Weiss, H. Wohlmuth, D. Kehrer, and A. L. Scholtz, "A 24-gb/s 27 - 1 pseudo random bit sequence generator ic in 0.13 m bulk cmos," in 2006 Proceedings of the 32nd European Solid-State Circuits Conference, 2006, pp. 468–471.

- [19] T. Tsai, M. A. Hussain, and P. Hao, "Vlsi implementation of ecg compression algorithm using golomb rice coding," in 2018 IEEE International Conference on Consumer Electronics-Taiwan (ICCE-TW), 2018, pp. 1–2.

- [20] O. U. Khan and D. D. Wentzloff, "1.2 gs/s hadamard transform frontend for compressive sensing in 65nm cmos," in 2013 IEEE Radio and Wireless Symposium, 2013, pp. 181–183.