# A Wireless Power Transfer based Gate Driver Design for Medium Voltage SiC MOSFETs

Yuqi Wei University of Arkansas Department of Electrical Engineering Fayetteville, Arkansas, United States yuqiwei@uark.edu

Venkata Samhitha Machireddy University of Arkansas Department of Electrical Engineering Fayetteville, Arkansas, United States Liyang Du University of Arkansas Department of Electrical Engineering Fayetteville, Arkansas, United States

Alan Mantooth

University of Arkansas

Faculty of Department of Electrical

Engineering

Fayetteville, Arkansas, United States

Xia Du University of Arkansas Department of Electrical Engineering Fayetteville, Arkansas, United States

Abstract—Wide band gap (WBG) devices have been widely adopted in numerous industrial applications. In medium voltage applications, multi-level converters are necessary to reduce the voltage stress on power devices, which increases the system control complexity and reduces power density and reliability. High voltage silicon carbide (SiC) MOSFET enables the medium voltage applications with less voltage level, simple control strategy and high power density. Nevertheless, great challenges have been posed on the gate driver design for high voltage SiC MOSFET. Wireless power transfer (WPT) can achieve power conversion with large airgap, which can satisfy the system isolation requirement. Thus, in this article, a WPT based gate driver is designed for the medium voltage SiC MOSFET. The coil is optimized by considering voltage isolation, coupling capacitance, size, and efficiency. Experimental prototype was built and tested to validate the effectiveness of the proposed WPT based gate driver.

Keywords—Silicon carbide (SiC) MOSFET, medium voltage, gate driver, wireless power transfer (WPT)

# I. INTRODUCTION

High power and medium voltage (MV) applications are increasingly important. To achieve the required voltage blocking capability, multiple power devices in series connection is necessary. However, the voltage sharing among these power devices cannot be ensured [1, 2]. High voltage silicon carbide (SiC) metal–oxide–semiconductor field-effect transistor (MOSFET) can effectively avoid the series connection and enable the application of the simple converter topology in these MV applications. In particular, 10 kV SiC MOSFET has been characterized and adopted in MV applications by several research groups [3]-[5].

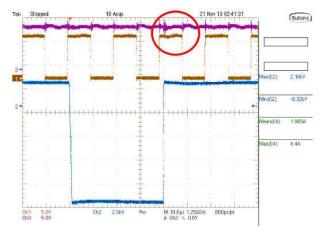

The dv/dt of the 10 kV SiC MOSFET can reach up to 110 kV/µs [6]. Such high dv/dt may flow through the coupling capacitance of the gate driver isolation transformer and generate noise current to cause malfunction of the control circuit as demonstrated in Fig. 1 [6]. Therefore, a careful design of the gate driver isolation transformer with extreme low coupling capacitance between primary side and secondary side is desired.

Fig. 1. Waveforms of the common-mode voltage and its influence on the signals on the primary side of the isolation stage. (Ch1: A PWM input of the H-bridge IC on primary side of the isolation stage; Ch2: Common-mode voltage; Ch3: Vcc of the H-bridge IC) [6].

High voltage isolation (>20 kV) is also required for the 10 kV SiC MOSFET gate driver design. To achieve high voltage isolation, the existing methods have been categorized into the following four groups: 1) voltage transformer [6]-[11]; 2) current transformer [12]-[15]; 3) power over fiber [16]; 4) wireless power transfer [17]-[21].

For the voltage transformer, large size transformer core is required to satisfy the creepage and clearance requirements, which increases the volume and weight of gate driver. On the other hand, due to the high coupling between primary side and secondary side, high efficiency operation can be achieved.

The current transformer solution can satisfy the system requirement with less number of turns and lower coupling capacitance when compared with voltage transformer based solution. Another main advantage of current transformer based solution is that it can be simply used to drive multiple power modules. The primary winding is shared among all different channels. However, a large transformer core is still required. The coupling between primary side and secondary side is reduced when compared with the voltage transformer.

Although the optical fiber can achieve extreme low (theoretical zero) coupling capacitance, this solution is expensive and the reported power is only 0.5 W, which may not provide sufficient driving capability for 10 kV SiC MOSFET with multiple dies in parallel [16].

Wireless power transfer (WPT) is also a promising technology for 10 kV SiC MOSFET application. The high voltage isolation requirement can be easily achieved by adjusting the airgap of primary coil and secondary coil, and the coupling capacitance between two coils can be reduced by optimal deign. Moreover, multiple-output can be easily achieved by using WPT technology as demonstrated in [19] and [21]. Although the system efficiency is not very good when compared with other solutions due to the low coupling between primary and secondary, the power loss is acceptable for 10 kV SiC MOSFET applications, where the system power is in the range MW. In [17], an asymmetric primary coil and secondary coil structure is designed to reduce the coupling capacitance. The system coupling capacitance is selected as optimization objective and the parametric sweep method with the aid of ANSYS simulation model is adopted to achieve the coil design. Additional non-isolated regulators are required to obtain the desired gate voltages for turn-on and turn-off.

In this article, a WPT based gate driver is designed for medium voltage applications with low coupling capacitance and high voltage isolation capability. Symmetric coil structure design is adopted to reduce the system complexity and cost. The selected compensation topology can achieve fixed voltage output with constant switching frequency operation, which helps reduce the adoption of the nonisolated regulator for the turn-on gate voltage. The turn-off gate voltage can be generated from a non-isolated regulator. The finite element analysis (FEA) based simulations are performed to achieve the optimal design of the coil by considering various factors into consideration, like voltage gain, efficiency, and coupling capacitance. The overall gate driver structure and implementations are discussed. Finally, experimental results for the developed gate driver are presented under different scenarios.

# II. SYSTEM DESIGN AND OPTIMIZATION

In this section the system structure and optimal design procedures are discussed.

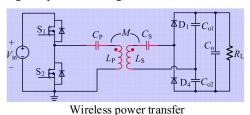

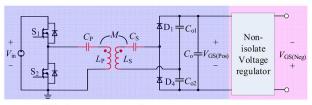

In this work, the inductive power transfer with primary series compensated and secondary series compensated structure as shown in Fig. 2 is selected. For medium voltage gate driver application, the major design objective is to minimize the coupling capacitance between primary side and secondary side. Thus, closed-loop control is not preferred due to the high voltage isolation requirement and introduced extra coupling capacitance. As discussed in [22], the selected circuit topology in Fig. 2 has one operating point, where the converter voltage gain is independent of the load. This operating point can be used to achieve open-loop operation of the converter. Another feature of the selected topology is simplicity, where only two capacitors are used to compensate the voltage drop on the leakage inductors.

Fig. 2. Circuit diagram of the primary side series compensated and secondary side series compensated inductor power transfer.

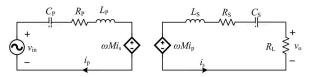

The circuit equivalent diagram for the system can be derived as shown in Fig. 3 [22].

Fig. 3. Equivalent circuit diagram.

According to Fig. 3, the voltage transfer ratio or voltage gain can be derived as follows

$$G = \frac{v_{\text{out}}}{v_{\text{in}}} = \frac{\omega M}{Z_{\text{P}} Z_{\text{S}} + \omega^2 M^2} R_{\text{L}}$$

(1)

where  $Z_P$  and  $Z_S$  are the primary and secondary impedance, respectively.  $\omega$  is the angular switching frequency. M is the mutual inductance of the primary side and secondary side coils. There exists an operating switching that ensures that the voltage transfer ratio is independent of the load [22], which is desired for the 10 kV gate driver application with simple circuit and high reliability. Meanwhile, feedback control would increase coupling capacitance between the primary side and secondary side. Therefore, in this research, the converter switching frequency is designed at this switching frequency point as shown in Eq. (2) to achieve constant voltage transfer ratio.

$$\omega = \sqrt{\frac{\omega_p^2 + \omega_s^2 + \Delta}{2(1 - k^2)}} \tag{2}$$

where  $\omega_p$  and  $\omega_s$  are the primary side and secondary side angular resonant frequency. Due to the symmetric structure of primary side and secondary side,  $\omega_p=\omega_s$  on be obtained. k is the coupling coefficient between primary and secondary. The expression for  $\Delta$  is shown in Eq. (3).

$$\Delta = \sqrt{(\omega_p^2 + \omega_s^2)^2 - 4(1 - k^2)\omega_p^2\omega_s^2}$$

(3)

The system loss is mainly caused the parasitic resistors. Then, the primary side and secondary side efficiencies can be expressed as:

$$\eta_{P} = \frac{\frac{\omega^{2} k^{2} L_{P} L_{S} (R_{S} + R_{L})}{(R_{S} + R_{L})^{2} + X_{S}}}{R_{P} + \frac{\omega^{2} k^{2} L_{P} L_{S} (R_{S} + R_{L})}{(R_{S} + R_{L})^{2} + X_{S}}}$$

(4)

$$X_{\rm S} = \omega L_{\rm S} - \frac{1}{\omega C_{\rm S}} \tag{5}$$

$$\eta_{S} = \frac{R_{L}}{R_{S} + R_{L}} \tag{6}$$

$$\eta = \eta_P \times \eta_S \tag{7}$$

where  $R_P$  and  $R_S$  re the primary and secondary resistances.

The main trade-offs for the coil design are voltage isolation, size, and system efficiency. With the aid of the ANSYS software, the coil parameters can be optimized.

The coupling capacitance of the coils can be modelled by using the paralleling copper plate.

$$C_{\text{couple}} = \frac{\mathcal{E}_0 \mathcal{E}_{\text{r}} A}{d}$$

(8)

where  $\mathscr{E}$ r is the relative permittivity of the insulation material. In this case, air is used as the insulation material and  $\mathscr{E}$ r=1 can be obtained. A is the overlapping area between the primary side and secondary side coils. d is the distance between two coils.

The estimated isolation capability of the system can be obtained by using Eq. (9) [23].

$$V_{\text{breakdown}} = \kappa t$$

(9)

where  $\kappa$  is the dielectric strength of the insulation material and t is the thickness. In this case, the thickness equal to the distance between two coils.

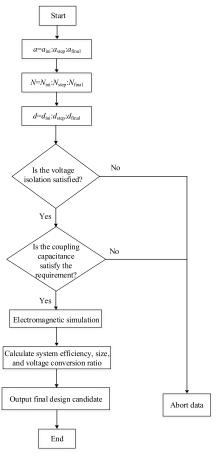

From the theoretical analysis, we can conclude that: 1) Large distance is preferred to achieve high voltage isolation and low coupling capacitance; 2) small distance is preferred to achieve high coupling and high efficiency operation; 3) small overlapping area is preferred for low coupling capacitance; 4) large overlapping area is preferred for high coupling. Design flow chart as shown in Fig. 4 is adopted to achieve the optimal design of the coils. In the design, the coil inner radius a, the number of turns N, and the coil distance d are selected as design variables. The copper width, pitch, and system operating frequency are predefined.

Fig. 4. Design flow chart for the coil.

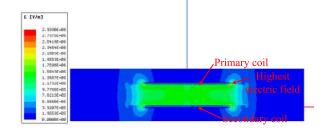

Fig. 5 shows the electric filed simulation result. It can be seen that the maximum electric filed occurs inside the PCB

coils, the FR4 epoxy material has large electric strength (20 MV/m). To reduce the coupling capacitance and common mode (CM) noise current, an EMI shielding layer is added to provide conduction path for CM current.

Fig. 5. Electric field simulation result.

The measurement results for the coil are summarized in Table I. The system switching frequency is designed at 2.5 MHz to achieve high efficiency conversion. Fig. 6 shows the measurement result of the coupling capacitance, a low coupling capacitance around 2 pF is achieved with an airgap of 15 mm.

TABLE I. MEASUREMENT RESULTS FOR THE DESIGNED COIL

| <i>a</i> =1 mm, <i>N</i> =24, <i>t</i> =15 mm |        |

|-----------------------------------------------|--------|

| $L_P/\mu H$                                   | 11.98  |

| C <sub>P</sub> /pF                            | 450    |

| $R_P/\Omega$                                  | 3.3887 |

| L <sub>s</sub> /μH                            | 11.98  |

| C <sub>S</sub> /pF                            | 3.388  |

| Mutual inductance/μH                          | 2.05   |

| Coupling coefficient k                        | 0.1767 |

| Coupling capacitance/pF                       | 2.0327 |

Fig. 6. Coupling capacitance measurement result with impedance analyzer.

# III. EXPERIMENT RESULTS AND DISCUSSIONS

Fig. 7 shows the overall gate driver power supply structure. The positive gate voltage is provided by the wireless power transfer and the negative voltage is generated through a non-isolated regulator. The secondary side PWM side is transmitted through optical fiber to achieve high voltage isolation and good EMI performance. The linear regulator VX7805-1000 from CUI Inc is selected, which has the following characteristics: 1) wide input voltage range: 8 V-26 V; 2) the maximum power is around 2.5 W. The gallium nitride (GaN) half-bridge driver (LMG5200) is used as the primary half-bridge inverter, which is capable of up to 10 MHz operation.

Wireless power transfer

Fig. 7. The proposed medium voltage gate driver power supply structure.

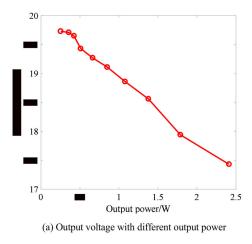

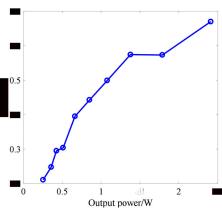

Fig. 8 shows the wireless power transfer system output voltage and efficiency with different output power. The output voltage variation with output power is small (the largest variation is around 2.34 V), which makes open-loop operation of the power supply feasible and the maximum efficiency around 70% can be achieved for the system.

(b) Converter efficiency with different output power

Fig. 8. WPT system efficiency and output voltage with different output power.

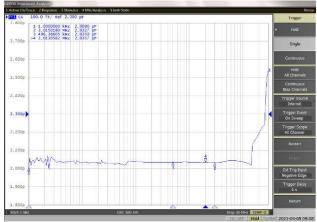

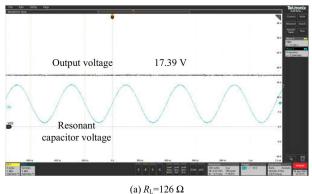

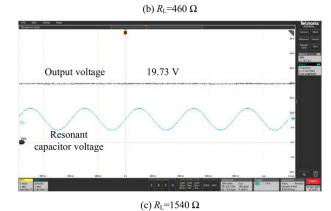

Fig. 9 shows the system output voltage experiment waveforms, where the system operating frequency is 2.5 MHz. The output voltage varies from 17.39 V to 19.73 V even with a large variation of load resistance. Therefore, open loop operation of the designed circuit is feasible.

Output voltage 19.27 V

Fig. 9. Output voltage experiment waveforms under different load conditions.

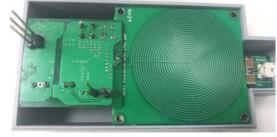

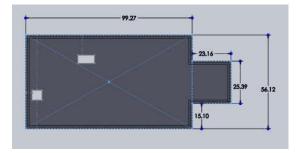

A 3D printed box as shown in Fig. 10 is designed to encapsulate the inductive power transfer based high voltage isolated power supply. The dimensions of the designed high voltage isolated power supply is shown in Fig. 10(c).

(a) 3D printed box for power supply with top side open

(b) 3D printed box for power supply with top side closed

(c) Dimensions in mm for the designed 3D printed box

Fig. 10. 3D printed box for the designed inductive power transfer based power supply for medium voltage gate driver.

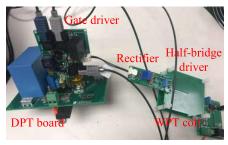

To further validate the effectiveness of the WPT based medium voltage gate driver, a double pulse test (DPT) platform as shown in Fig. 11 is built. 1200 V/40 A SiC MOSFET SCT2080KE from ROHM is selected as device under test (DPT) to validate the operation of the designed gate driver.

Fig. 11. Picture of the DPT test setup and designed  $\ensuremath{\mathsf{wpt}}$  based gate driver.

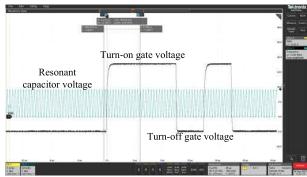

Fig. 12 shows the gate driver output experiment waveform. The turn-on gate voltage is around 18 V, while the turn-off gate voltage is around -5 V, which can be used to drive medium voltage SiC MOSFET.

Fig. 12. Gate driver experiment waveform.

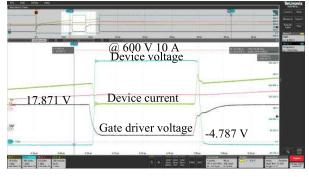

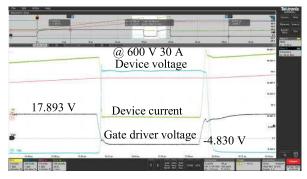

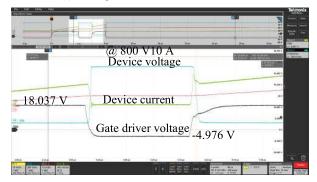

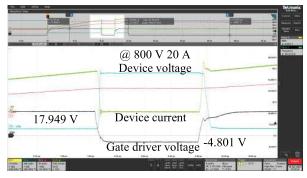

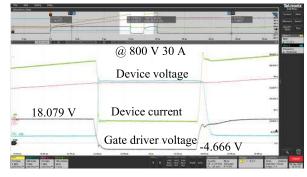

Fig. 13 shows the experiment waveforms under different conditions. It can be seen even with open loop operation, the

gate voltage is almost constant at 18 V with small variations, which proves that the proposed gate driver can be designed with open loop to simplify the circuit and reduce the coupling capacitance caused by the feedback control.

(a) DPT experiment waveform at 600 V and 10 A

(b) DPT experiment waveform at 600 V and 30 A

(c) DPT experiment waveform at  $800\ V$  and  $10\ A$

(d) DPT experiment waveform at 800 V and 20 A

(e) DPT experiment waveform at 800 V and 30 A

Fig. 13. Experiment waveforms under different operating conditions.

Isolation test for the designed power supply is performed by applying constant dc voltage on the primary side and secondary side. The system setup is shown in Fig. 14. The high voltage dc power supply FC30P4 with 30 kV maximum output from glassman is used to apply 20 kV voltage difference on the primary side and secondary side. As can be seen from Fig. 14, no leakage current can be observed during the test, which lasts for 10 minutes.

Fig. 14. Isolation test by applying constant dc voltage.

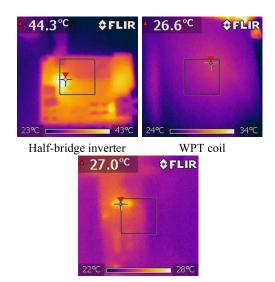

Fig. 15 shows the thermal performance of the designed gate driver at rated output power (2.5 W). The hottest part is the gallium nitride (GaN) half-bridge driver (LMG5200of the primary inverter, which is around 44 °C, which is far below than the maximum junction temperature 125 °C. Based on the characteristic of 10 kV power module (multiple dies in parallel operation), a higher power capability can be achieved with the proposed design.

Voltage doubler rectifier

Fig. 15. Thermal performance of the WPT coil based power supply.

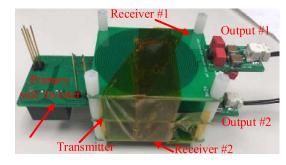

The designed power supply can also be modified to have two-output isolated voltages as shown in Fig. 16, which can be used to drive a half-bridge power module. The primary side inverter and coil are shared, which can reduce the number of components and power supply system size. Due to the large distance between two receivers, the coupling and corresponding influence between them is negligible.

Fig. 16. Designed high voltage insulated power supply with two output channels.

# IV. CONCLUSION

In this article, a WPT based gate driver for 10 kV SiC MOSFET application is presented. For 10 kV gate driver application, the isolation and coupling capacitance are the most important requirements. By operating the WPT system at a specific constant frequency, the system output voltage is independent of the load, which can be used for the gate driver power supply design with reduced complexity and coupling capacitance. Preliminary experiment results are presented to validate the effectiveness of the developed WPT based gate driver. The isolation test demonstrates the high voltage isolation characteristic of the designed power supply. Medium voltage test is the focus of future work.

# ACKNOWLEDGEMENT

This work was supported by the U.S. National Science Foundation (NSF) within the Industry/University Cooperative Research Center (I/UCRC) on Grid Connected

Advanced Power Electronic Systems (GRAPES) under Grant No. IIP-1939144.

### REFERENCES

- [1] J. Zhang, S. Shao, Y. Li, J. Zhang and K. Sheng, "A Voltage Balancing Method for Series-Connected Power Devices in an LLC Resonant Converter," IEEE Transactions on Power Electronics, vol. 36, no. 4, pp. 3628-3632, Apr. 2021.

- [2] F. Zhang, Y. Ren, X. Yang, W. Chen and L. Wang, "A Novel Active Voltage Clamping Circuit Topology for Series-Connection of SiC-MOSFETs," IEEE Transactions on Power Electronics, vol. 36, no. 4, pp. 3655-3660, April 2021.

- [3] D. Rothmund, D. Bortis and J. W. Kolar, "Highly compact isolated gate driver with ultrafast overcurrent protection for 10 kV SiC MOSFETs," CPSS Transactions on Power Electronics and Applications, vol. 3, no. 4, pp. 278-291, Dec. 2018.

- [4] C. DiMarino, I. Cvetkovic, Z. Shen, R. Burgos and D. Boroyevich, "10 kV, 120 a SiC MOSFET modules for a power electronics building block (PEBB)," 2014 IEEE Workshop on Wide Bandgap Power Devices and Applications, 2014, pp. 55-58.

- [5] S. Ji et al., "Short circuit characterization of 3rd generation 10 kV SiC MOSFET," 2018 IEEE Applied Power Electronics Conference and Exposition (APEC), 2018, pp. 2775-2779.

- [6] A. Kadavelugu and S. Bhattacharya, "Design considerations and development of gate driver for 15 kV SiC IGBT," 2014 IEEE Applied Power Electronics Conference and Exposition -APEC 2014, 2014, pp. 1494-1501.

- [7] K. Mainali, S. Madhusoodhanan, A. Tripathi, K. Vechalapu, A. De and S. Bhattacharya, "Design and evaluation of isolated gate driver power supply for medium voltage converter applications," 2016 IEEE Applied Power Electronics Conference and Exposition (APEC), Long Beach, CA, 2016, pp. 1632-1639.

- [8] J. Kim, H. Kim, Y. Cho and J. Kim, "Highly isolated power supply design for gate drivers of the solid state transformer," 2017 Asian Conference on Energy, Power and Transportation Electrification (ACEPT), 2017, pp. 1-5.

- [9] D. N. Dalal et al., "Gate driver with high common mode rejection and self turn-on mitigation for a 10 kV SiC MOSFET enabled MV converter," 2017 19th European Conference on Power Electronics and Applications (EPE'17 ECCE Europe), 2017, pp. P.1-P.10.

- [10] A. Anurag, S. Acharya, Y. Prabowo, G. Gohil and S. Bhattacharya, "Design Considerations and Development of an Innovative Gate Driver for Medium-Voltage Power Devices With High dv/dt," IEEE Transactions on Power Electronics, vol. 34, no. 6, pp. 5256-5267, June 2019.

- [11] L. Zhang et al., "Design Considerations for High-Voltage Insulated Gate Drive Power Supply for 10-kV SiC MOSFET Applied in Medium-Voltage Converter," IEEE Transactions on Industrial Electronics, vol. 68, no. 7, pp. 5712-5724, July 2021.

- [12] J. Hu, J. Wang, R. Burgos, B. Wen and D. Boroyevich, "High-Density Current-Transformer-Based Gate-Drive Power Supply With Reinforced Isolation for 10-kV SiC MOSFET

- Modules," IEEE Journal of Emerging and Selected Topics in Power Electronics, vol. 8, no. 3, pp. 2217-2226, Sept. 2020.

- [13]J. Gottschlich, M. Schäfer, M. Neubert and R. W. De Doncker, "A galvanically isolated gate driver with low coupling capacitance for medium voltage SiC MOSFETs," 2016 18th European Conference on Power Electronics and Applications (EPE'16 ECCE Europe), 2016, pp. 1-8.

- [14] L. Zhang, S. Sen and A. Q. Huang, "7.2-kV/60-A Austin SuperMOS: An Intelligent Medium-Voltage SiC Power Switch," IEEE Journal of Emerging and Selected Topics in Power Electronics, vol. 8, no. 1, pp. 6-15, March 2020.

- [15] S. Sen, L. Zhang, X. Feng and A. Q. Huang, "High Isolation Auxiliary Power Supply for Medium-Voltage Power Electronics Building Block," 2020 IEEE Applied Power Electronics Conference and Exposition (APEC), 2020, pp. 2249-2253

- [16] X. Zhang et al., "A Gate Drive With Power Over Fiber-Based Isolated Power Supply and Comprehensive Protection Functions for 15-kV SiC MOSFET," IEEE Journal of Emerging and Selected Topics in Power Electronics, vol. 4, no. 3, pp. 946-955, Sept. 2016.

- [17] V. -T. Nguyen, V. U. Pawaskar and G. Gohil, "Isolated Gate Driver for Medium-Voltage SiC Power Devices Using High-Frequency Wireless Power Transfer for a Small Coupling Capacitance," IEEE Transactions on Industrial Electronics, vol. 68, no. 11, pp. 10992-11001, Nov. 2021.

- [18] K. Kusaka, K. Orikawa, J. Itoh, K. Morita and K. Hirao, "Isolation system with wireless power transfer for multiple gate driver supplies of a medium voltage inverter," 2014 International Power Electronics Conference (IPEC-Hiroshima 2014 - ECCE ASIA), Hiroshima, 2014, pp. 191-198.

- [19] V. T. Nguyen and G. Gohil, "Dual-Output Isolated Gate Driver Power Supply for Medium Voltage Converters using High Frequency Wireless Power Transfer," 2020 IEEE Applied Power Electronics Conference and Exposition (APEC), 2020, pp. 1821-1828.

- [20] C. Marxgut, J. Biela, J. W. Kolar, R. Steiner and P. K. Steimer, "DC-DC converter for gate power supplies with an optimal air transformer," 2010 Twenty-Fifth Annual IEEE Applied Power Electronics Conference and Exposition (APEC), 2010, pp. 1865-1870.

- [21] K. Kusaka, K. Orikawa, J. Itoh, K. Morita and K. Hirao, "Isolation system with wireless power transfer for multiple gate driver supplies of a medium voltage inverter," 2014 International Power Electronics Conference (IPEC-Hiroshima 2014 - ECCE ASIA), 2014, pp. 191-198.

- [22] W. Zhang, S. Wong, C. K. Tse and Q. Chen, "Analysis and Comparison of Secondary Series- and Parallel-Compensated Inductive Power Transfer Systems Operating for Optimal Efficiency and Load-Independent Voltage-Transfer Ratio," IEEE Transactions on Power Electronics, vol. 29, no. 6, pp. 2979-2990, June 2014.

- [23] A. Anurag, S. Acharya, N. Kolli and S. Bhattacharya, "Gate Drivers for Medium-Voltage SiC Devices," IEEE Journal of Emerging and Selected Topics in Industrial Electronics, vol. 2, no. 1, pp. 1-12, Jan. 2021.