# A 4-Element 500MHz 40mW 6-bit ADC enabled Time-Domain Spatial Signal Processor

Erfan Ghaderi, *Student Member, IEEE*, and Subhanshu Gupta, *Senior Member, IEEE*

**Abstract**—Next-generation wireless communication requires phased-array systems with large modulated bandwidths and high energy-efficiency ensuring Gb/s data communication. Conventional phase-shifter-based arrays result in frequency-dependent processing and therefore beam-squinting in an array. This work demonstrates a 4-element 500 MHz modulated bandwidth true-time-delay-based ADC-enabled spatial signal processor (SSP) with frequency-uniform beam-forming, wideband beam-nulling, and multiple independent interference filtering using Kronecker decomposition. This processor can augment conventional phased-array RF front-ends to implement a complete antenna-to-digital solution. The proposed baseband delay-compensating solution in the SSP uses scalable time-domain circuits comprising of time-interleaved voltage-to-time converters followed by asynchronous 6-bit pipeline time-to-digital converters and consumes only 40 mW with a total area of 0.31 mm<sup>2</sup> in 65nm CMOS technology.

**Index Terms**—Kroenecker decomposition, spatial signal processor, time-domain processing, true-time-delay.

## I. INTRODUCTION

Spatial signal processing in multi-antenna receivers offers not only higher received power and signal-to-noise ratio (SNR) because of higher number of reception antennas but also enables spatial diversity and simultaneous communication with multiple devices. For the past several years, there have been many works on integrated multi-antenna receivers. Approximating the time-delay with a phase shift element is the basis of large portion of these works [1]–[8]. However, the frequency-dependent approximation of true-time-delay (TTD) with a phase-shift element results in beam-squinting in the angular domain [9] and limited fractional bandwidth (BW) in the frequency domain [10]. Using TTD with the SSP results in frequency-uniform processing, which translates to beam-squinting free beamforming. The beam-squint issue has its parallel in beam-nulling arrays handling wide modulated bandwidths. State-of-the-art phase-shifter-based arrays targeting beam-nulling [1], [4], [11]–[15] have limited rejection capability towards wideband interference because the array gain variation at different frequency components makes it hard to steer a deep null towards interference. For multi-antenna receivers, it results in interference leakage and significantly higher dynamic range requirements for the baseband (BB) and the ADC [16].

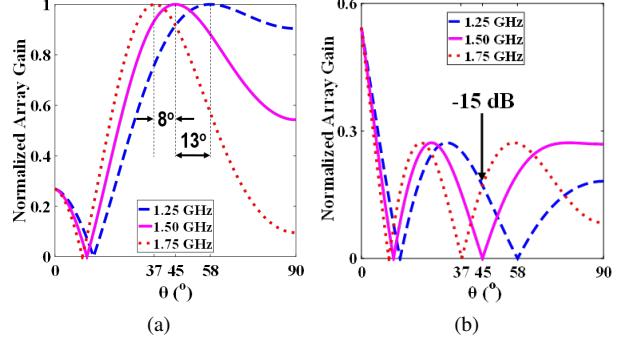

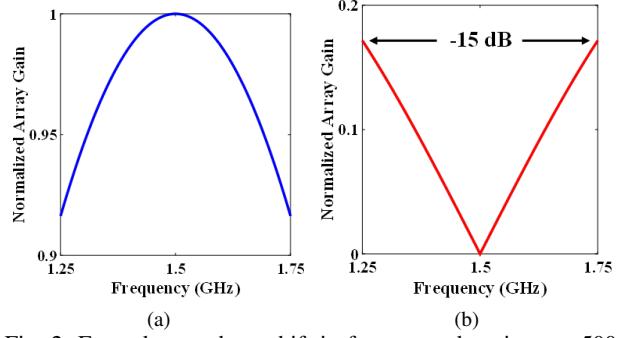

To emphasize the importance of the need for TTD SSP, a case study on the errors caused by phase-shift approximation in a linear array is presented. Assuming a 4-element array with 500 MHz modulated bandwidth and 1.5 GHz center frequency, Fig. 1(a) shows that approximating TTD with a phase shifter results in  $-8^\circ$  and  $+13^\circ$  error in the angular domain (assuming

This work has been partially supported by NSF CAREER Award (#1944688) and NSF Award 1705026. Erfan Ghaderi and Subhanshu Gupta are with the School of Electrical Engr. and Comp. Science, Washington State University, Pullman, WA 99163 USA (e-mail: sgupta@eecs.wsu.edu).

Fig. 1: Error due to phase-shift in angular domain over 500 MHz BW for (a) beam-forming, and (b) beam-nulling.

Fig. 2: Error due to phase-shift in frequency domain over 500 MHz BW for (a) beam-forming, and (b) beam-nulling.

angle of arrival (AoA) of  $45^\circ$  at the bandedge). These errors are what are known as beam squinting in a beamformer. Also for beam-nulling, these errors result in limiting the filtering to only 15 dB, at the bandedge. This can be observed in Fig. 1(b). The beam squinting error further depends on the AoA. When the AoA increases, the beam-squinting gets worse. For high angles close to  $\pm 60^\circ$ , the error at the band edges is as high as  $28^\circ$ . This results in non-alignment with the transmitter and consequently loss in the intended AoA.

Similarly in the frequency domain, phase shifting results in frequency-dependent beamforming, which acts like a bandpass filter (Fig. 2(a)) and affects the desired signal quality. Also for the beam-nulling case, this approximation limits the rejection performance that in this case is only 15 dB at the band edges (Fig. 2(b)). This problem gets significantly more severe for larger arrays.

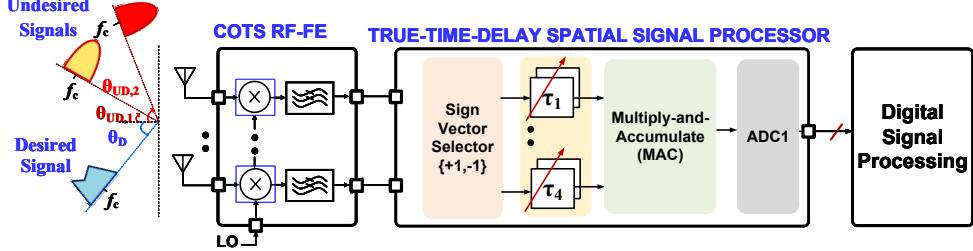

TTD SSP can also be implemented in the digital domain, after digitizing all the channels [9]. This implementation gives complete access to the received signals at the cost of power hungry ADCs. In contrast to prior approaches, our recent work [17] demonstrated a TTD SSP in the BB time-domain prior to the ADC. In [17] and as shown in Fig. 3, we relaxed the data conversion resolution and hence power consumption requirement by filtering the high power wideband blocker prior to the conversion; and the TTD elements range and resolution

Fig. 3: Proposed baseband (BB) delay-compensating TTD SSP. Only one beam is implemented.

requirements by implementing the TTD in the baseband clock path [18], and all with digital-friendly time-based circuits and systems. This work significantly expands on the circuits and systems proposed in [17] with the following distinct contributions:

- 1) Analysis of multiple independent interference cancellation in phased arrays using the properties of Kroenecker decomposition,

- 2) Detailed circuit design of the SSP comprising voltage-to-time converter (VTC), time-to-digital converter (TDC), and time amplifier (TA) considering noise and linearity metrics, and

- 3) Expanded measurement methodology detailing the test setup and single-tone and wideband measurements for the SSP including the time-based ADC.

The rest of the paper is organized as follows. Section II briefs SSP techniques in linear arrays for beam-forming, beam-nulling, and independent cancellation of multiple interferences. Proposed system design and circuit implementation details are presented in Section III combining discrete-time delay compensation with time-based ADCs. Section IV presents the measurement results for different SSP modes followed by conclusions in Section V.

## II. SPATIAL SIGNAL PROCESSING (SSP) IN LINEAR ARRAYS

Considering an  $N$ -element uniformly-spaced linear array with half-wavelength spacing, the time delay between any two consecutive antennas can be represented as [19]:

$$\tau = \frac{d \cdot \sin(\theta)}{c} = \frac{\sin(\theta)}{2 \cdot f_c} \Big|_{d=\lambda_c/2} \quad (1)$$

where  $\lambda_c$  and  $f_c$  are the received signal's wavelength and center frequency, respectively. These time delays between the received signals can be expressed in the frequency domain as an array vector,  $\mathbf{V}(j\omega)$ , representing the antenna signals as a frequency domain vector:

$$\mathbf{S}(j\omega) = L(j\omega) \cdot [1 \ e^{-j\omega\tau} \ \dots \ e^{-j\omega(N-1)\tau}]' \cdot \mathbf{X}(j\omega) \quad (2)$$

$$= L(j\omega) \cdot \mathbf{V}(j\omega) \cdot \mathbf{X}(j\omega)$$

where  $\mathbf{S}(j\omega)$  is the received signals vector, scalar  $L(j\omega)$  captures the path loss, and scalar  $\mathbf{X}(j\omega)$  is the transmitted signal. In the following sub-sections, we will take advantage of this vector representation in the frequency domain to perform different spatial signal processing functions, including beam-forming, beam-nulling, and independent cancellation of multiple interferences.

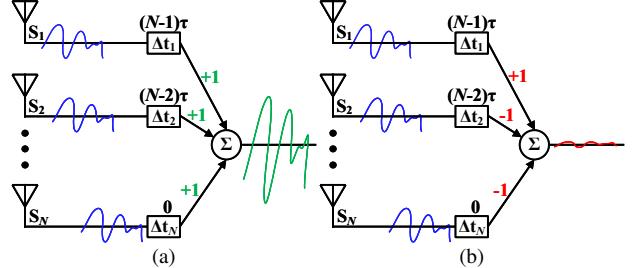

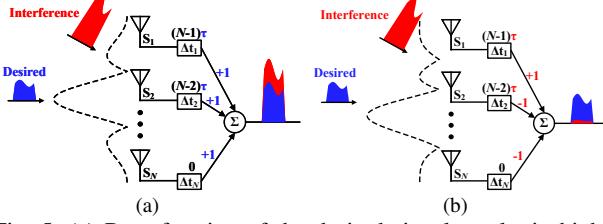

Fig. 4: TTD arrays for (a) beam-forming, and (b) beam-nulling.

### A. Beam-forming

The time delayed received signals at the antennas can be time-aligned first and then constructively combined to increase the power of the intended signal [10], [20]–[23]. This constructive addition is called beamforming as shown in Fig. 4(a), and it can be also expressed in the frequency domain through the following vector expression:

$$\begin{aligned} \mathbf{Y}(j\omega) &= [e^{-j\omega(N-1)\tau} \ e^{-j\omega(N-2)\tau} \ \dots \ 1]' \cdot \mathbf{S}(j\omega) \\ &= N \cdot e^{-j\omega(N-1)\tau} \cdot \mathbf{X}(j\omega) \end{aligned} \quad (3)$$

where  $\mathbf{Y}(j\omega)$  is the beamforming output. As seen in (3), the amplitude of  $\mathbf{Y}$  is higher than  $\mathbf{X}$  amplitude by a factor of  $N$ . This results in an improvement of  $N$  in the Signal to Noise Ratio (SNR) as the signal power is increased by  $N^2$  and the noise power is amplified only by factor of  $N$ .

The relation between the angle with the maximized received power and the implemented inter-element delay ( $\tau$ ) can be extracted from (1) and written as:

$$\theta = \sin^{-1}(2f_c \cdot \tau) \quad (4)$$

Any deviation in the implemented inter-element time delay from the delay caused by the intended AoA results in drop in the beamforming gain. One form of deviation is the phase-shift approximation that neglects the frequency-dependency of the  $\theta$  and causes non-uniform beamforming gain.

### B. Beam-nulling

Opposite to the beamforming, the received signals can be time-aligned and then destructively combined [18]. This destructive combination cancels the received signal and is called beam-nulling as shown in Fig. 4(b). Similar to the beamforming case, beam-nulling can also be modeled in frequency domain through vector representation:

$$\mathbf{Z}(j\omega) = [e^{-j\omega(N-1)\tau} \ -e^{-j\omega(N-2)\tau} \ \dots \ -1]' \cdot \mathbf{S}(j\omega) = 0 \quad (5)$$

Fig. 5: (a) Beamforming of the desired signal results in high interference power at the output, and (b) beam-nulling the interference guarantees the immunity at the cost of lower desired gain.

The output of the beam-nulling system,  $Z(j\omega)$  is equal to zero and the signal is nulled. In this spatial signal processing function, the undesired in-band interference can be filtered based on its AoA. To control the direction of the null,  $\tau$  can be easily varied filtering the undesired signal from any direction.

Note that in the beamforming case, there is a desired signal in which the receiver steers toward its direction and suppresses other directions. If there is a high-power interference located in non-zero points of the beamforming gain (at the worst case, one of the side-lobes), the interference is not filtered enough and can potentially block the communication with the desired transmitter as shown in Fig. 5(a). To solve this issue, the receiver can change to the beam-nulling mode to filter the high-power interference and receive the desired signal as shown in Fig. 5(b). Note that the desired signal is affected by the beam-nulling conversion gain, depending on both the desired and undesired AoA. As mentioned earlier, the destructive combination (which half of the channels being subtracted from the other half) in the beam-nulling implementation is chosen to maximize the desired signal gain. A limitation of the beam-nulling technique at BB is that the BB TTD implementation comes with the linearity overhead on the RF front-end (RFFE), as the strong undesired signals must be down-converted without affecting the weak desired signal SNR.

### C. Multiple independent interference filtering

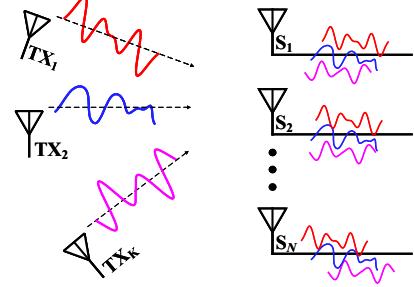

In the previous sub-section, a mathematical solution for filtering an interference with a specific AoA was presented. Even though that solution can offer multiple combinations for the interference cancellation, all the combinations null the same interference. This limitation makes a simultaneous multiple independent interference cancellation solution attractive. In this sub-section a generalized approach to cancel multiple interferences in an  $N$ -element receiver is presented (Fig. 6), where,  $K_{max} = \log_2(N)$  with  $K_{max}$  being the maximum number of transmitters.

Each transmitted signal is received at the receiver with its own unique array vector  $(V_1(j\omega), \dots, V_i(j\omega), \dots, V_K(j\omega))$  where  $i = 1 \dots K$  and  $K \leq K_{max}$ . The constant  $\tau$  makes the array vector entries to form a geometric sequence with scale factor of 1 and common ratio of  $e^{-j\omega\tau}$ . This property offers a unique decomposition of the array vector through Kronecker product of  $K_{max}$  sub-vectors [24] as follows:

$$V_i(j\omega) = [1 \ e^{-j\omega\tau_i} \ \dots \ e^{-j\omega(N-1)\tau_i}]' \\ = [1 \ e^{-j\omega\tau_i}]' \bigotimes [1 \ e^{-j\omega 2\tau_i}]' \dots \bigotimes [1 \ e^{-j\omega(N/2)\tau_i}]' \quad (6)$$

Fig. 6: TTD array cancelling multiple independent interferences.

where  $i$  is the array index,  $N = 2^{K_{max}}$ , and  $\bigotimes$  denotes the left Kronecker product. In this operation, the entire first matrix is multiplied by each entry of the second matrix. Because any array vector  $V_i(j\omega)$  can be decomposed into  $K_{max}$   $2 \times 1$  sub-vectors, there will be  $K_{max}$   $1 \times 2$  unique vectors that each null one of the decomposed  $2 \times 1$  sub-vectors. The Kronecker product of any  $1 \times (N/2)$  random vectors with the  $K_{max}$   $1 \times 2$  vectors can null the entire decomposed array vector. For example, the  $1 \times 2$  vector that can null the first sub-vector of the first transmitter array in (6) is:

$$[e^{-j\omega\tau_1} \ -1] \bigotimes A(j\omega) [1 \ e^{-j\omega\tau_1} \ \dots \ e^{-j\omega(N-1)\tau_1}]' \\ = [e^{-j\omega\tau_1} \ -1] [1 \ e^{-j\omega\tau_1}]' \bigotimes \widehat{A(j\omega)} \\ = 0 \bigotimes \widehat{A(j\omega)} = 0 \quad (7)$$

where  $\widehat{A(j\omega)}$  is a new random vector and does not affect the outcome of the nulling. Similarly, the  $1 \times 2$  vector that can null the decomposed sub-vector of the second transmitter array can be expressed as:

$$[e^{-j\omega 2\tau_1} \ -1] \bigotimes B(j\omega) [1 \ e^{-j\omega\tau_1} \ \dots \ e^{-j\omega(N-1)\tau_1}]' \\ = [e^{-j\omega 2\tau_1} \ -1] [1 \ e^{-j\omega 2\tau_1}]' \bigotimes \widehat{B(j\omega)} \\ = 0 \bigotimes \widehat{B(j\omega)} = 0 \quad (8)$$

where  $\widehat{B(j\omega)}$  is a new random vector and do not affect the outcome of the nulling.

The final cancellation vector in this instance ( $F_1(j\omega)$ ) for the  $K = K_{max}$  scenario can be written as:

$$F_1(j\omega) = [e^{-j\omega\tau_1} \ -1] \bigotimes [e^{-j\omega 2\tau_2} \ -1] \bigotimes \dots \\ [e^{-j\omega(N/2)\tau_{K_{max}}} \ -1] \quad (9)$$

The subscript in  $F_1(j\omega)$  shows the first possible solution, as there are  $K_{max}$  possible unique solutions depending on which order is chosen to null the sub-vectors (or which transmitter is called  $TX_1$ ,  $TX_2$ , and so on). For the specific implementation with 4-elements, two independent interferences can be cancelled ( $K_{max} = \log_2 4 = 2$ ). The two possible solutions to cancel the interferences in this 4-element receiver are as follows:

$$F_1(j\omega) = [e^{-j\omega\tau_1} \ -1] \bigotimes [e^{-j\omega 2\tau_2} \ -1] \\ = [e^{-j\omega(\tau_1+2\tau_2)} \ -e^{-j\omega(2\tau_2)} \ -e^{-j\omega\tau_1} \ 1] \quad (10)$$

$$F_2(j\omega) = [e^{-j\omega\tau_2} \ -1] \bigotimes [e^{-j\omega 2\tau_1} \ -1] \\ = [e^{-j\omega(2\tau_1+\tau_2)} \ -e^{-j\omega(2\tau_1)} \ -e^{-j\omega\tau_2} \ 1] \quad (11)$$

Fig. 7: Block diagram of the proposed 4-element BB time-domain SSP with ADC.

Note that the outcome of (9) is a non-uniform delay implementation, in contrast with the constant inter-element delay implementation for the beamforming and beam-nulling cases. The beam-nulling and multiple independent interference cancellation performance can be further improved by implementing a real-time adaptive TTD control (for example, in [25]). In this delay optimization, the algorithm will find the best delay values to maximize the interference cancellation and hence the system SNR in contrast with a unique one-to-one mapping between the TTD element delay and the interference locations.

### III. SSP SYSTEM DESIGN & CIRCUIT IMPLEMENTATION

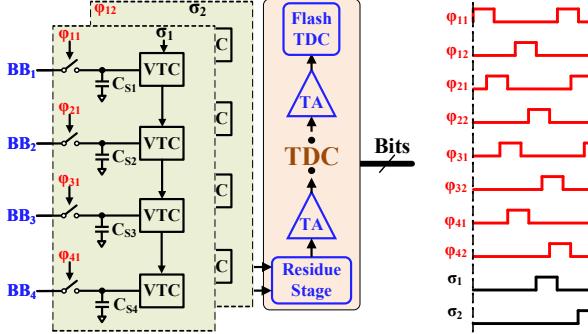

In Fig. 7, the system-level diagram of the designed 4-element baseband discrete-time time-domain SSP is presented. The proposed SSP is demonstrated with 500 MHz modulated-bandwidth, sampling rate of 1 GS/s, and 1 ns delay compensation range through 2-level of time-interleaving, capable of beamforming, beam-nulling, and 2-independent interference cancellation modes. Similar to the charge-domain implementation in [10], the TTD elements are implemented through the baseband delay compensation technique in the BB, accompanied by the LO phase-shifters. However, unlike the closed-loop OTA-based charge-domain implementation in [10], the signal combination in the time-domain does not impose any extra bandwidth requirements. The TTD element in this design is implemented in the clock path through a voltage-controlled delay line. This design's amplitude response purely depends on the capacitor and DC current mismatch and the delay value does not affect the amplitude. In terms of amplitude correction/calibration, future research can implement a reconfigurable switched capacitor network instead of one single sampling capacitor or controlling the discharging current (of the voltage-to-time converter) similar to a current-starving Digital to Analog Converter (DAC).

The proposed time-domain SSP is capable of three different processing modes. In Mode 1, the processor is in the beam-forming mode and all the BB signals are added constructively after time-alignment through the delay compensating technique in the VTC sampling phase. By changing the processor sign vectors and time-aligning the interferences, half of the received signals are subtracted from the other half resulting in beam-nulling in Mode 2. And finally in the Mode 3, by taking advantage of the Kronecker decomposition of the array vectors,  $\log_2(N)$  independent interferences can be filtered. The

Fig. 8: Schematic of the differential VTC [17].

TTD elements in Mode 3 are not uniformly spaced (required inter-element delay is not constant for each pair of consecutive elements) and are calculated after Kronecker decomposition. The sign vector and the required TTD elements for the 4-element RX in Mode 3 can be found through (10) or (11).

In this implementation, the signal combination is performed in the time-domain, where the first sampled BB input is converted to a time-domain pulse by the first VTC. By applying the output of the first VTC to the second one, the time-domain information of the second input, which is the time-domain representation of the second sampled value, is added (or subtracted) to the first one. This delayed version of CLK is then applied to the second VTC to generate a new delay proportional to the second sampled voltage. In other words, the sampled voltage of the first two inputs are combined and converted to a delay between the CLK and the output pulse of the second VTC. By continuing this trend for the remaining VTCs, all the input signals are added in the time domain at the output of the last VTC. The time-domain output of the last VTC, which contains all the sampled input information, is then digitized through an asynchronous pipeline TDC for further digital processing. At each stage of the TDC, two raw bits are extracted and a residue value is generated and amplified by a TA, for the following stages. At the end, all the bits extracted from different stages are combined in a specific timely manner to reconstruct the complete digital data. For TA calibration across the PVT variations, the particle swarm optimization (PSO) is used. The delay compensation values are generated through a tunable delay-line explained later. Also, a 6-bit TDC is implemented to digitize the time-domain information for further processing. The TA linearity is enhanced by combining two different TAs with different input-output characteristic. The detailed implementation of each sub-blocks are presented next.

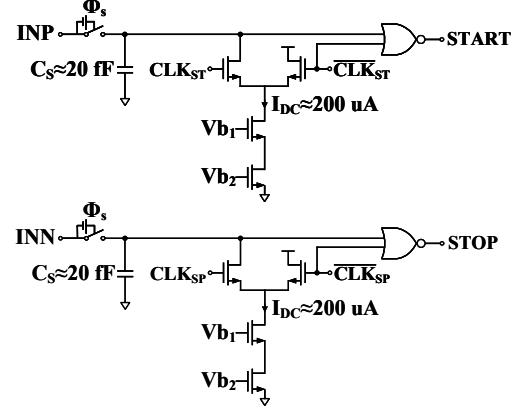

#### A. Discrete-time VTC

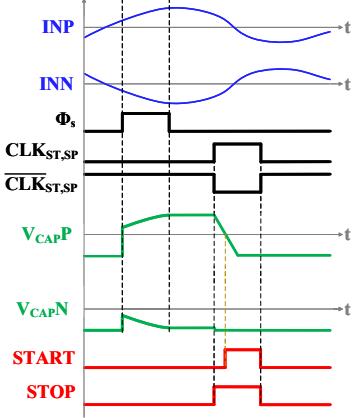

A single-ended implementation of the VTC is shown in Fig. 8. In this VTC, the differential input continuous-time voltages (INP/INN) are sampled on the sampling capacitors ( $C_S \approx 20 fF$ ) while the output pulses (START/STOP) are low. When the reference phases ( $CLK_{ST}/CLK_{SP}$ ) rise, the capacitors are disconnected from the inputs and begin to discharge by the constant current  $I_{DC} (= 200 \mu A)$ . Based on

Fig. 9: An example of differential VTC operation.

the sampled values on the capacitors, there will be  $T_{OUT}$  amount of time delay between the times that capacitors voltages cross the comparator reference voltage on each side. The comparator outputs (START/STOP) are triggered and rise when the crossing happens. This way, the continuous-time input voltage is first sampled and is then converted to a delay between START and STOP. The input-output characteristic of the VTC can be expressed as [26]:

$$T_{OUT}[k] = \frac{C_s}{I_{DC}} V_{IN}[kT_S] \quad (12)$$

From (12), the conversion gain of this VTC is equal to  $C_s/I_{DC} = 100\text{ps/V}$ . The bootstrapped switch enhances the linearity and allows up to  $1_{VPP,\text{diff}}$  input voltage range while sampling at 1 GS/s. In the two time-interleaved VTCs corresponding to the first channel, the VTC reference clocks are connected to  $\sigma_1$  and  $\sigma_2$  respectively, and for the rest of the VTCs, they are connected to the previous VTC output pulses for signal combination.

The high power interference signal in the cascaded VTCs cause the largest nonlinearities in the first stage (i.e., in the pair of VTCs connected to the first input) and this stage dominates the overall linearity as its nonlinearities propagate through the entire chain and will be present at the final time-domain value (i.e., the output of the last VTC). Any non-idealities in the first VTC can potentially get amplified by the following stages and reduce the overall performance. In this design, we have used the same VTCs for all the stages and tried to optimize the overall voltage to time conversion, and not the individual stages.

An example of the VTC operation with non-overlapping sampling and reference phases is shown in Fig. 9. In the sampling phase, both the capacitors track the input voltage, while both the outputs are zero. By turning off the sampling switches, the capacitors hold the sampled value, while the outputs are still low. When the reference phase arrives, if the sampled value on the capacitor ( $V_{CAPP}$  or  $V_{CAPN}$ ) is less than the NOR gate threshold voltage the corresponding output, STOP (corresponding to  $V_{CAPN}$ ), in this example, rises while the other output remains low.  $V_{CAPP}$  begins to discharge by the constant current source and the moment  $V_{CAPP}$  reaches the NOR gate threshold voltage the corresponding output,

START, rises. Thus, the continuous-time input voltages are sampled and then converted to two pulses that the delay between them is proportional to the difference between the sampled values. The falling edge of the reference clocks synchronizes the output falling edges. Thus the delay between the rising events are only of interest.

### B. Asynchronous pipeline time-to-digital converter

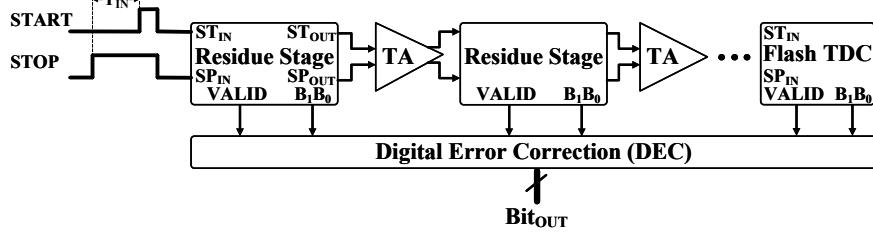

To quantize the time-domain spatially processed output of the VTCs, an asynchronous pipeline TDC, with four residue stages, 4 TAs each with a gain of two, and a 2-bit flash TDC is implemented as shown in Fig. 10. The input time-domain pulses are first applied to the first residue stage, where two raw bits with Most Significant Bit (MSB) value are extracted and a residue value is generated. The residue value is first amplified through a TA and then applied to the second residue stage. This trend continues until the the fourth (last) residue stage where the output residue value is amplified and then quantized through the 2-bit flash TDC. Besides the bits and the residue value, at each stage an asynchronous pulse (VALID) is generated for proper timing of the raw bits combination in the Digital Error Correction (DEC) block.

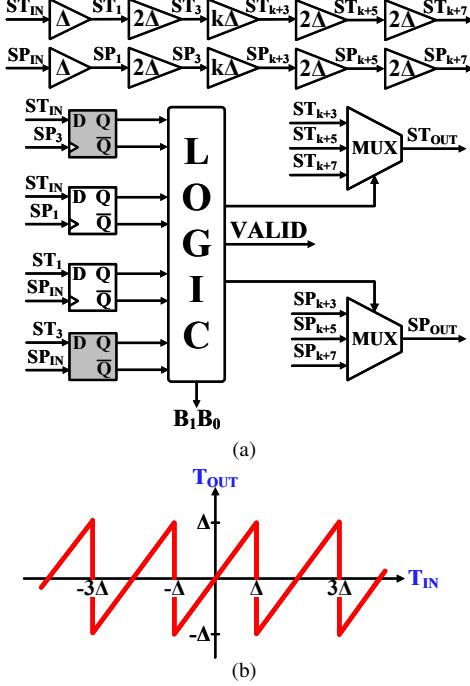

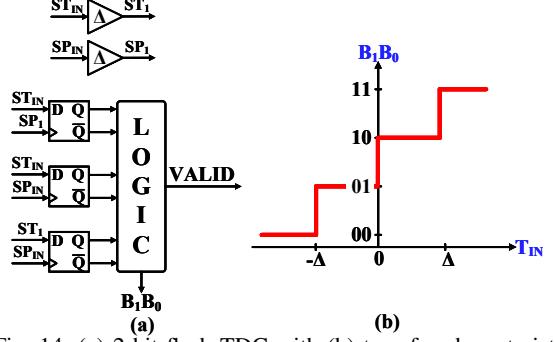

The residue generation is implemented by a 1.5-bit residue stage, shown in Fig. 11(a). In this implementation, the operation region is detected by comparing the different delayed versions of the input pulses ( $ST_{IN}$  and  $SP_{IN}$ ) through a time-domain comparator, which is an arbiter that detects early or late arrival of one input compared to the other one. The delayed version of the input pulses are generated through a delay-line with an inter-stage delay of  $\Delta = 40\text{ps}$ . Based on the arbiter outputs, the LOGIC unit determines the operation region and generates the raw bits. After the region detection and the bit extraction, the LOGIC also generates the asynchronous VALID pulse as the operation validation. The VALID pulse is the outcome of the case that all the arbiters have settled to their final result. The residue generation, which basically is the controlled shift in the input time value ( $T_{IN}$ ), is performed by selecting the different delayed version of input pulses as the output ( $ST_{OUT}$  and  $SP_{OUT}$ ). Compared to the conventional pipeline residue stage, two extra time comparators (highlighted in gray) are added to limit the output residue value range. The input-output characteristic of the designed 1.5-bit residue stage with the extra time comparators is shown in Fig. 11(b). By removing the extra comparators, the output residue range can get as high as  $\pm 3\Delta$  and this directly affects the TA linearity. Because the TA linearity is the main bottleneck in this design, adding two extra time comparators is well justified with minimal power penalty. The output residue value then is amplified by a factor of two and applied to the following residue stage.

As the output range of the first residue stage is  $\pm\Delta$ , the second residue stage input range is limited to  $\pm 2\Delta$ , and hence the extra comparators will not be needed in the second residue stage. This range limitation applies to the third and fourth residue stages as well. Therefore, two extra time comparators are only needed in the first residue stage.

As mentioned earlier, the TA linearity determines the overall TDC linearity and consequently its signal-to-noise-distortion-

Fig. 10: Block diagram of the proposed asynchronous pipeline TDC.

Fig. 11: (a) Proposed 1.5-bit residue stage, and (b) transfer characteristics of residue stage.

Fig. 12: Block diagram of companding-expanding TA.

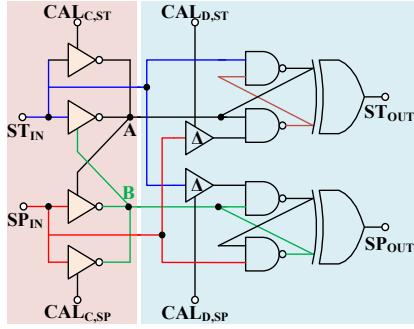

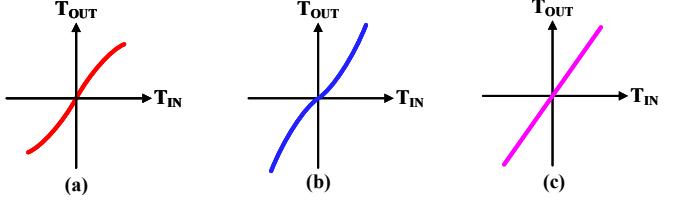

ratio (SNDR). To enhance the TA linearity, two TAs with different input-output characteristic are combined. The block diagram of the combined TA with gain of two, is shown in Fig. 12. In this implementation, two sub-TAs (blue and red parts of the Fig. 12) are combined to increase the overall time amplification linearity. The companding sub-TA [27] is based on multi-path discharging shown in Fig. 13(a). In this technique, both the inputs are inverted through two inversion paths, where one of the paths is enabled by the inverted version of the other input. For instance in Fig. 12, inverted version of  $ST_{IN}$  (node A) enables or disables one of the discharging paths of the other input ( $SP_{IN}$ ) and consequently varies the delay from  $SP_{IN}$  to node B. This variation in the discharging power

Fig. 13: Transfer characteristic of: (a) companding sub-TA; (b) expanding sub-TA; (c) proposed combined TA.

Fig. 14: (a) 2-bit flash TDC with (b) transfer characteristic.

results in time amplification with gain of approximately two. This approximation is mostly valid for small values of input but for larger input values the gain begins to drop. On the other hand, the metastability-based expanding sub-TA that is implemented through cross-coupled NAND gates [28], results in an expanding characteristic, as shown in Fig. 13(b). By combining these two different characteristics, the TA linearity is enhanced as shown in Fig. 13(c) and consequently the TDC SNDR is improved. For both the sub-TAs, calibration nodes are included to maintain the required SNDR with the PVT variations. The PSO is used to calibrate the TA. This optimization is explained with the presented measurement results in the next section.

The 2-bit flash TDC block diagram and input-output characteristic is shown in Fig. 14. Similar to the residue stage, the output bits of the flash TDC are found through comparing different delayed versions of the input pulses. The pipeline nature of the implemented TDC requires a careful bit combination, performed in a timely manner. The found raw bits of the residue stages of the flash TDC are stored in D flip-flops clocked with the VALID pulse from each stage. After time-alignment of the raw bits, they are added with one bit redundancy to ensure the proper pipeline quantization, similar to the conventional pipeline voltage-domain ADCs.

#### IV. TEST SETUP AND MEASUREMENT RESULTS

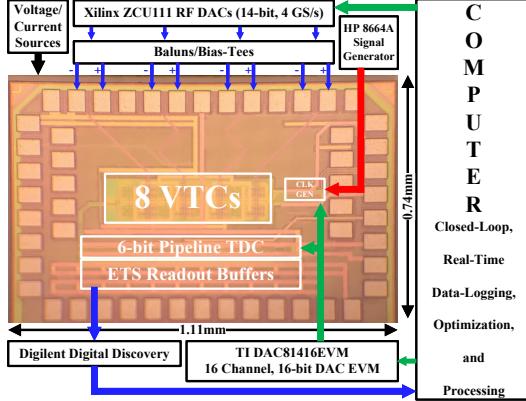

The presented BB TTD SSP is fabricated in a 65-nm TSMC process as a proof-of-concept. The die micrograph and the test

Fig. 15: Die micrograph and the test setup used for the TTD SSP.

Fig. 16: TDC SNDR of each particle plotted vs. the iteration index.

setup for the SSP are shown in Fig. 15. The chip occupies  $0.82\text{mm}^2$  area with only  $0.31\text{mm}^2$  active core area. To validate the prototype, various measurements have been performed using a Quad-Flat No Leads (QFN) packaging. All the input signals are MATLAB generated and then uploaded to a Xilinx ZCU111 Evaluation Board. The signals are applied to the device under test (DUT) after DC biasing using bias-tees. The reference 1 GHz clock is provided off-chip from an HP8664A signal generator. Through this reference clock, the required time-interleaved phases for sampling are generated on-chip. The implemented inter-element delays are controlled externally through a 16-bit Texas Instruments (TI) digital-to-analog converter (DAC) Evaluation Module (DAC81416EVM). The TI DAC is also used to tune the TA calibration nodes. Finally, the output digital data is read at a lower speed (40 MHz clock rate,  $25\times$  lower than the ADC operation speed) through a Digilent Digital Discovery board. To reconstruct the original data from the low-speed read-out, an Equivalent Time Sampling (ETS) technique has been used followed by post-processing in MATLAB. The ETS read-out technique is commonly used in digital sampling oscilloscopes, where the input data is sampled at a lower rate, stored in the memory and displayed later after the original data reconstruction [29].

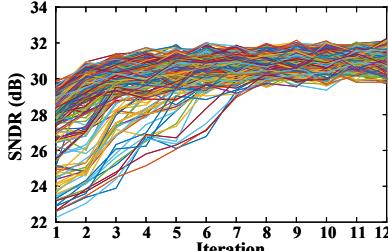

Each channel's input-to-output characteristic is measured by applying a constant amplitude signal to each input (one at a time) and observing the digital output amplitude. The gain mismatch between the channels is initially calibrated by equalizing each input amplitude. After the channel mismatch calibration, the TDC and specifically the TAs are calibrated through PSO in closed-loop. The PSO is performed one time before the normal operation of the chip. In the PSO, 400 particles are used representing 400 possible solutions for the TA calibration node voltage values. A single-tone input is applied to the chip and the TDC SNDR is measured and stored

Fig. 17: TDC linearity enhancement through the PSO.

Fig. 18: Measured single-tone test results in beamforming mode: (a) conversion gain vs. input signal frequency; and (b) beam patterns for the three different AoAs.

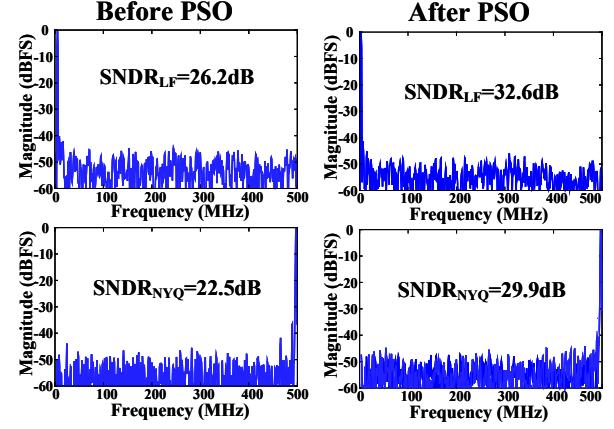

for all the 400 possible solutions. Based on the outcome SNDR of each of the 400 particles for one iteration, the location of the particles that result in lower SNDR values are changed towards the particles with higher corresponding SNDR values in the next iteration. This trend is continued for 12 iterations until the all the particles are close enough to the maximum possible value for the SNDR of the TDC. The SNDR value of all the particles versus the optimization iteration is plotted in Fig. 16, where after each iteration the particles are getting closer and closer to the maximum possible SNDR. The SNDR enhancement through the PSO can be seen in Fig. 17, where for both cases of low frequency and Nyquist input SNDR increase by more than 6.4 dB through this optimization.

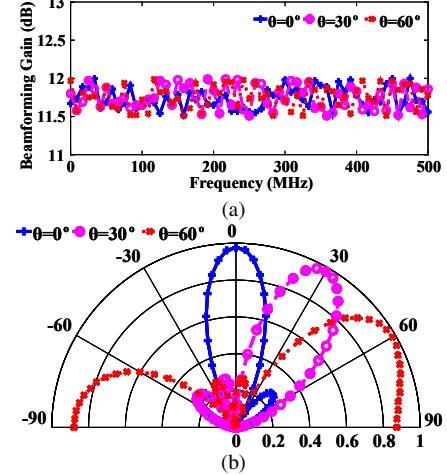

The implemented SSP has been tested for the three processing modes and various types of input, including single-tone, wideband, and modulated signals. We have assumed that the RF-FE is operating at 1.5GHz center frequency, with antenna spacing of  $\lambda/2$  (10 cm), and  $\pm 90^\circ$  angle coverages. These numbers result in a maximum inter-element delay of 1ns/3 and the overall delay range of 1ns. In Fig. 18(a), the measurement result of the chip in the beamforming mode and for a swept single-tone input signal is presented. For three cases of desired AoA ( $0^\circ$ ,  $30^\circ$ , and  $60^\circ$ ), frequency-independent beamforming gain of close to 12 dB is measured across the 500 MHz bandwidth. The jitter in the sampling phases and limited TDC

Fig. 19: Measured result of the single-tone test in the beam-nulling mode: (a) conversion gain vs. input signal frequency; and (b) cancellation for three AoAs.

Fig. 20: Measured single-tone test in Mode 3: (a) average cancellation vs. frequency; and (b) the angular response for two pairs of interference AoA.

resolution are the main reasons for the small variation in the beamforming gain. For the three cases of AoA, the beamforming beam patterns of the processor are presented in Fig. 18(b). The frequency-independent beamforming conversion gain and the beam-squinting free beam patterns show the TTD-based operation of the SSP.

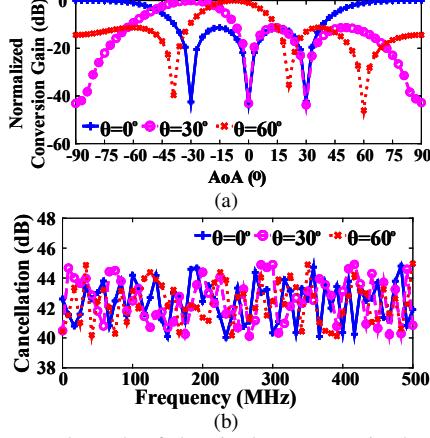

The same single-tone test is performed for the beam-nulling conversion gain versus the input signal frequency and the beam-nulling pattern of the TTD SSP for three different interference AoAs are presented in Fig. 19(a) and Fig. 19(b), respectively. More than 40 dB interference cancellation is observed for the time-domain SSP across the entire bandwidth, in the beam-nulling mode. Also, deep angular nulls are generated in the beam pattern, providing high performance beam-nulling.

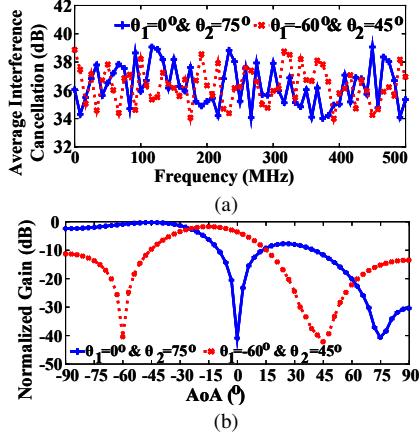

The time-domain design is also validated for the 2-independent interference cancellation, where two undesired input signals with different AoA are applied to the chip and the processor filters both the undesired signals. In Fig. 20(a), the average cancellation of the undesired signals is plotted versus their single-tone frequencies, for two different pairs of interference AoA. On average, more than 34 dB cancellation is measured in Mode 3, proving high-performance capability of the implemented design. The angular domain response of

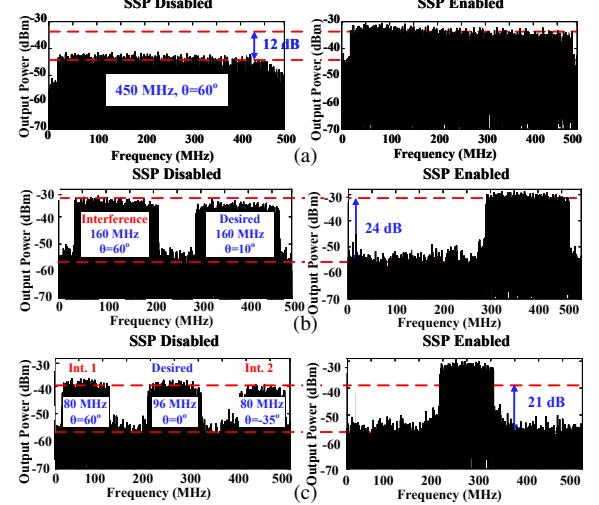

Fig. 21: Measured performance with wideband signals in: (a) beamforming mode; (b) beam-nulling mode; and (c) 2-independent interference cancellation mode.

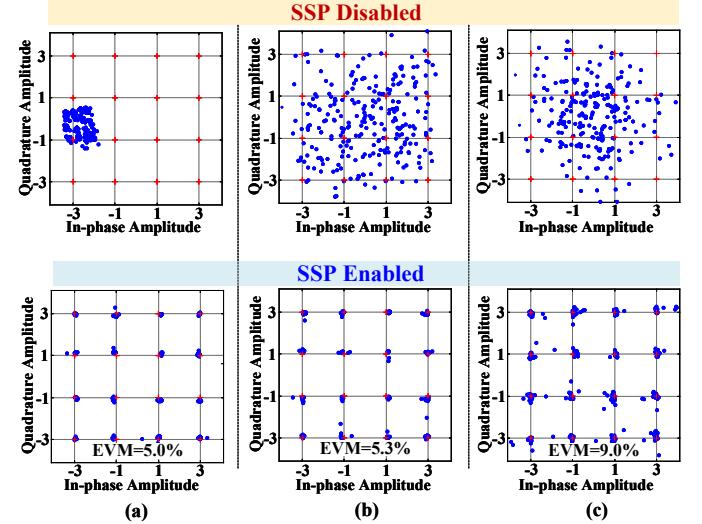

Fig. 22: Measured constellation and EVM of the modulated signal in the: (a) beamforming mode; (b) beam-nulling mode; and (c) 2-independent interference cancellation mode.

the processor for the two different pairs of AoA is plotted in Fig. 20(b), where two independent nulls are generated in both the pairs. In both the cases, two deep nulls are generated in both the interferences AoA.

The chip is also tested with wideband input signals, in all the processing modes. The wideband input measurement results are shown in Fig. 21(a). In the beamforming mode, frequency-independent roughly 12 dB beamforming gain is observed for a 450 MHz wideband input with  $\text{AoA} = 60^\circ$ . The wide bandwidth in Fig. 21(a) results in TDC performance limitation that folds the distortion components in the desired signal. This problem can be avoided by increasing the TDC operating bandwidth or improving the oversampling ratio in the TDC to avoid noise/distortion folding. In the second mode, two 160 MHz input signals from two different directions are applied to the processor. In this mode, the in-band interference with  $\text{AoA} = 60^\circ$  is filtered by 24 dB, while the desired signal with  $\text{AoA} = 10^\circ$  is preserved Fig. 21(b). Finally, in the third mode, the 96 MHz desired signal with  $\text{AoA} = 0^\circ$  is preserved, while

|                                               |                        | [1]<br>JSSC 2017                   | [4]<br>JSSC 2019                     | [9]<br>JSSC 2019                | [18]<br>TMTT20                                  | This Work                                          |

|-----------------------------------------------|------------------------|------------------------------------|--------------------------------------|---------------------------------|-------------------------------------------------|----------------------------------------------------|

| <b>Architecture</b>                           |                        | Phased-shift array                 | Phased-shift array                   | Digital TTD array               | TTD array                                       | TTD array                                          |

| <b>Implementation</b>                         |                        | RF + BB                            | mmWave + BB                          | RF + BB + DIG                   | BB                                              | BB                                                 |

| # Elements                                    |                        | 4 inputs / 4 outputs               | 4 inputs / 4 outputs                 | 16 inputs / 16 output (4 beams) | 4 inputs / 3 outputs                            | 4 inputs / 1 output                                |

| <b>Functionality</b>                          |                        | Arbitrary Spatial Filtering        | Beamformer + Multi-Blocker Rejection | Beamformer + ADC                | <b>SpICa</b>                                    | Beamformer + Multi-Blocker Rejection + ADC         |

| <b>Domain</b>                                 |                        | Voltage                            | Voltage                              | Voltage                         | Charge                                          | Time                                               |

| <b>Technology</b>                             |                        | 65nm CMOS                          | 45nm SOI                             | 40nm CMOS                       | 65nm CMOS                                       | 65nm CMOS                                          |

| Supply (V)                                    |                        | 1.2                                | NR                                   | NR                              | 1.0                                             | 1.0                                                |

| # Elements (N)                                |                        | 4                                  | 4                                    | 16                              | 4                                               | 4                                                  |

| Rejection (dB)                                | Single-Tone            | 51-56                              | 50-62                                | 47                              | 46-51                                           | 40-46                                              |

|                                               | Modulated BW           | NR                                 | 28.5 <sup>1</sup>                    | NA                              | >35                                             | 24                                                 |

| Rejection Mod. BW (MHz)                       |                        | CW                                 | 500 <sup>2</sup>                     | NA                              | 100                                             | 500                                                |

| Beamforming Mod. BW (MHz)                     |                        | NR                                 | 500 <sup>2</sup>                     | 100                             | -                                               | 500                                                |

| TTD Range (ns)                                |                        | NA                                 | NA                                   | 7.5                             | 15                                              | 1                                                  |

| Operational Frequency Range (GHz)             |                        | 0.1-3.1                            | 27-41                                | 0.95-1.05                       | 0-0.1                                           | 1.25-1.75                                          |

| Fractional BW (Mod. BW /RF Carrier Frequency) |                        | NR                                 | 1.8% (0.5GHz/28GHz)                  | 10.0% (0.1GHz/1GHz)             | 100.0% (0.1GHz/0.1GHz) <sup>3</sup>             | 33.3% (0.5GHz/1.5GHz) <sup>3</sup>                 |

| Linearity                                     | P <sub>1dB</sub> (dBm) | NR                                 | -27.3 (Canc. OFF)                    | NR                              | 4.7 <sup>4,5</sup>                              | -0.5 (Canc. OFF) <sup>4,5</sup>                    |

|                                               | IP3 (dBm)              | -296. <sup>7</sup>                 | -15 <sup>7,8</sup>                   | NR                              | 10.6 <sup>4,5</sup>                             | 7.9 <sup>4,5</sup>                                 |

| Noise Performance                             |                        | 3.4-5.8 dB<br>Noise Figure         | 4.3-6.3 dB<br>Noise Figure           | 60 dB<br>SNDR                   | 330 $\mu$ V <sub>rms</sub><br>(Output-referred) | 32.6 dB<br>SNDR                                    |

| Power (mW)                                    |                        | 116-147 <sup>9</sup>               | 280-340 <sup>9</sup>                 | 453                             | 52                                              | 25 (8 VTCs)<br>12 (TDC)<br>3 (Clock)<br>40 (Total) |

| Area (mm <sup>2</sup> )                       |                        | 2.25 <sup>9</sup><br>1.44 (active) | 23.4 <sup>9</sup>                    | 4.42<br>0.29 (active)           | 0.9                                             | 0.82<br>0.31 (active)                              |

NR: Not reported; NA: Not applicable; <sup>1</sup>SINR in presence of two 256-QAM 100M Sym/s blockers; <sup>2</sup>Raw bandwidth calculated for 3Gb/s 64QAM; <sup>3</sup>Assuming RF front-end at carrier frequency of  $(N-1)/2 \times$  TTD Range; <sup>4</sup>1-element; <sup>5</sup>BB RX only; <sup>6</sup>Receiving angle; <sup>7</sup>IIP3=OIP3+Conversion Gain; <sup>8</sup>Calculated for receiving angle when signal-to-blocker incidence difference is 90°; <sup>9</sup>RF included, NO ADC.

two independent 80 MHz wideband in-band interferences are filtered by more than 21 dB, as shown in Fig. 21(c). In this measurement, one interference is arriving from -35° and the other from 60°.

The performance of the time-domain SSP is also measured for wide modulated-bandwidth signals, in all the three processing modes. In all the three modes, the desired 16-QAM 250 Mb/s signal is applied with one or two interferences. In the beamforming mode, a 12 dB stronger single-tone interference is added to the desired signal and placed in a null AoA of the beamforming pattern. The constellation of the desired signal, before and after enabling the spatial signal processing, at the output of the chip is shown in Fig. 22(a). After beamforming, 5% EVM is calculated for the desired signal. In Fig. 22(b), the constellation of the same desired signal is plotted in presence of a 12 dB stronger 160 MHz wideband interference, before and after enabling the beam-nulling. In this mode, 5.3% EVM is calculated. In the third processing mode, two 80 MHz wideband interferences, each 6 dB stronger than the desired signal power, are added to the desired signal. In this mode, 9.0% EVM is calculated and the constellation of the desired signal is shown in Fig. 22(c). The

modulated signals performance in all the processing modes proves the applicability of the proposed SSP for high-speed wireless links.

The 4-element BB discrete-time SSP consumes 40 mW power (25 mW for the signal combination through the time-interleaved VTCs, 12 mW for TDC quantization, and 3 mW for sample phase generation using controlled delay-lines). The input 1dB compression point (P<sub>1dB</sub>) of this SSP is -0.5 dBm from the desired signal perspective and its IIP3 is 7.9 dBm. In Table I, the BB time-domain SSP is compared with the state-of-the-art. The implemented delay range of 1 ns allows the RF-FE to work at center frequencies as low as 1.5 GHz, resulting in >33% fractional bandwidth for this design.

## V. CONCLUSIONS

This work presents a baseband discrete-time time-domain SSP that presents a time-based system-level design approach for wideband beam-forming, beam-nulling, and independent filtering of multiple interferences. The time-domain design offers TTD-based processing, that results in high fractional bandwidth capability. This design is also the only solution with multiple interference cancellation and embedded ADC. Time amplification linearity enhancement was presented

through combining different time amplifier structures. The time-domain processor chip was fabricated and its functionality was proven through various measurements. Wideband frequency-independent baseband spatial processing, in the beamforming, beam-nulling, and 2-independent interference cancellation modes was validated by applying swept single-tone, wideband, and modulated signals to the chip. At the end, the measurement results of the fabricated chip was compared with the state-of-the-art.

## VI. ACKNOWLEDGEMENTS

The authors are thankful to Profs. Deukhyoun Heo and Sudip Shekhar for useful discussions on this work. The authors also thank Chase Puglisi and Shrestha Bansal for their help with sampling switch layout and the particle-swarm optimization respectively.

## REFERENCES

- [1] L. Zhang and H. Krishnaswamy, "Arbitrary analog/RF spatial filtering for digital MIMO receiver arrays," *IEEE Journal of Solid-State Circuits*, vol. 52, no. 12, pp. 3392–3404, 2017.

- [2] R. Garg, G. Sharma, A. Binaie, S. Jain, S. Ahasan, A. Dascurcu, H. Krishnaswamy, and A. Natarajan, "4.3 a 28GHz 4-element mimo beam-space array in 65nm CMOS with simultaneous spatial filtering and single-wire frequency-domain multiplexing," in *2020 IEEE International Solid- State Circuits Conference - (ISSCC)*, 2020, pp. 80–82.

- [3] M. Huang, T. Chi, S. Li, T. Huang, and H. Wang, "A 24.5–43.5-GHz ultra-compact CMOS receiver front end with calibration-free instantaneous full-band image rejection for multiband 5G Massive MIMO," *IEEE Journal of Solid-State Circuits*, vol. 55, no. 5, pp. 1177–1186, 2020.

- [4] M. Huang and H. Wang, "A mm-wave wideband MIMO RX with instinctual array-based blocker/signal management for ultralow-latency communication," *IEEE Journal of Solid-State Circuits*, vol. 54, no. 12, pp. 3553–3564, 2019.

- [5] S. Mondal and J. Paramesh, "A reconfigurable 28-/37-GHz MMSE-adaptive hybrid-beamforming receiver for carrier aggregation and multi-standard MIMO communication," *IEEE Journal of Solid-State Circuits*, vol. 54, no. 5, pp. 1391–1406, 2019.

- [6] B. Sadhu, Y. Tousi, J. Hallin, S. Sahl, S. K. Reynolds, Renström, K. Sjögren, O. Haapalahti, N. Mazor, B. Bokinge, G. Weibull, H. Bengtsson, A. Carlinger, E. Westesson, J. Thillberg, L. Rexberg, M. Yeck, X. Gu, M. Ferriss, D. Liu, D. Friedman, and A. Valdés-García, "A 28-GHz 32-element TRX phased-array IC with concurrent dual-polarized operation and orthogonal phase and gain control for 5G communications," *IEEE Journal of Solid-State Circuits*, vol. 52, no. 12, pp. 3373–3391, 2017.

- [7] A. Chakrabarti, C. Thakkar, S. Yamada, D. Choudhury, J. Jaussi, and B. Casper, "4.5 a 64Gb/s 1.4pJ/b/element 60GHz 2x2-Element phased-array receiver with 8b/symbol polarization MIMO and spatial interference tolerance," in *2020 IEEE International Solid- State Circuits Conference - (ISSCC)*, 2020, pp. 84–86.

- [8] N. Oshima and M. Kitsunezuka and K. Tsukamoto and K. Kunihiro, "A 30-MHz–3-GHz CMOS Array Receiver With Frequency and Spatial Interference Filtering for Adaptive Multi-Antenna Systems," *IEEE Transactions on Microwave Theory and Techniques*, vol. 65, no. 2, pp. 362–373, 2017.

- [9] S. Jang, R. Lu, J. Jeong, and M. Flynn, "A 1-GHz 16-element four-beam true-time-delay digital beamformer," *IEEE Journal of Solid-State Circuits*, vol. 54, no. 5, pp. 1304–1314, May 2019.

- [10] E. Ghaderi, A. Sivadasan Ramani, A. A. Rahimi, D. Heo, S. Shekhar, and S. Gupta, "An integrated discrete-time delay-compensating technique for large-array beamformers," *IEEE Transactions on Circuits and Systems I: Regular Papers*, vol. 66, no. 9, pp. 3296–3306, Sep. 2019.

- [11] M. Huang and H. Wang, "21.2 a 27-to-41GHz MIMO receiver with N-Input-N-Output using scalable cascadable autonomous array-based high-order spatial filters for instinctual full-FoV multi-blocker/signal management," in *IEEE International Solid- State Circuits Conference - (ISSCC)*, 2019, pp. 346–348.

- [12] M. Huang, T. Chi, F. Wang, T. Li, and H. Wang, "A full-fov autonomous hybrid beamformer array with unknown blockers rejection and signals tracking for low-latency 5g mm-wave links," *IEEE Transactions on Microwave Theory and Techniques*, vol. 67, no. 7, pp. 2964–2974, 2019.

- [13] S. Jain, Y. Wang, and A. Natarajan, "A 10ghz cmos rx frontend with spatial cancellation of co-channel interferers for mimo/digital beamforming arrays," in *2016 IEEE Radio Frequency Integrated Circuits Symposium (RFIC)*, 2016, pp. 99–102.

- [14] A. Ghaffari, E. Klumperink, F. van Vliet, and B. Nauta, "A 4-element phased array system with simultaneous spatial and frequency-domain filtering at the antenna inputs," *IEEE Journal of Solid-State Circuits*, vol. 49, no. 6, pp. 1303–1316, Jun. 2014.

- [15] L. Zhang and A. Natarajan and H. Krishnaswamy, "Scalable Spatial Notch Suppression in Spatio-Spectral-Filtering MIMO Receiver Arrays for Digital Beamforming," *IEEE Journal of Solid-State Circuits*, vol. 51, no. 12, pp. 3152–3166, 2016.

- [16] J. H. C. van den Heuvel and J. M. G. Linnartz and P. G. M. Baltus and D. Cabric, "Full MIMO Spatial Filtering Approach for Dynamic Range Reduction in Wideband Cognitive Radios," *IEEE Transactions on Circuits and Systems I: Regular Papers*, vol. 59, no. 11, pp. 2761–2773, 2012.

- [17] E. Ghaderi, C. Puglisi, S. Bansal, and S. Gupta, "10.8 a 4-Element 500MHz-modulated-BW 40mw 6b 1GS/s analog-time-to-digital-converter-enabled spatial signal processor in 65nm CMOS," in *2020 IEEE International Solid- State Circuits Conference - (ISSCC)*, 2020, pp. 186–188.

- [18] E. Ghaderi, A. S. Ramani, A. A. Rahimi, D. Heo, S. Shekhar, and S. Gupta, "Four-element wide modulated bandwidth MIMO receiver with >35-db interference cancellation," *IEEE Transactions on Microwave Theory and Techniques*, pp. 1–10, 2020.

- [19] R. Mailloux, *Phased Array Antenna Handbook*, 2005.

- [20] J. Roderick and H. Krishnaswamy and K. Newton and H. Hashemi, "Silicon-Based Ultra-Wideband Beam-Forming," *IEEE Journal of Solid-State Circuits*, vol. 41, no. 8, pp. 1726–1739, 2006.

- [21] T. Chu and H. Hashemi, "True-time-delay-based multi-beam arrays," *IEEE Transactions Microw. Theory Tech*, vol. 61, no. 8, pp. 3072–3082, Aug. 2013.

- [22] S. Garakoui, E. Klumperink, B. Nauta, and F. van Vliet, "Compact cascadable gm-C all-pass true-time-delay cell with reduced delay variation over frequency," *IEEE Journal of Solid-State Circuits*, vol. 50, no. 3, pp. 693–703, Mar. 2015.

- [23] N. Rajesh and S. Pavan, "Design of Lumped-Component Programmable Delay Elements for Ultra-Wideband Beamforming," *IEEE Journal of Solid-State Circuits*, vol. 49, no. 8, pp. 1800–1814, 2014.

- [24] G. Zhu, K. Huang, V. Lau, B. Xia, X. Li, and S. Zhang, "Hybrid beamforming via the Kronecker Decomposition for the millimeter-wave massive MIMO systems," *IEEE Journal of Sel. Areas Communication*, vol. 35, no. 9, pp. 2097–2114, Sep. 2017.

- [25] R. L. Haupt and S. E. Haupt, "Phase-only adaptive nulling with a genetic algorithm," in *1997 IEEE Aerospace Conference*, vol. 3, 1997, pp. 151–160 vol.3.

- [26] P. Osherooff, G. S. L. Rue, and S. Gupta, "A highly linear 4GS/s uncalibrated voltage-to-time converter with wide input range," in *IEEE International Symposium on Circuits and Systems (ISCAS)*, May 2016, pp. 89–92.

- [27] S. Lee, Y. Seo, Y. Suh, H. Park, and J. Sim, "A 1GHz ADPLL with a 1.25ps minimum-resolution sub-exponent TDC in 0.18μm CMOS," in *IEEE International Solid-State Circuits Conference - (ISSCC)*, 2010, pp. 482–483.

- [28] M. Lee and A. Abidi, "A 9b, 1.25 ps resolution coarse-fine time-to-digital converter in 90 nm CMOS that amplifies a time residue," *IEEE Journal of Solid-State Circuits*, vol. 43, no. 4, pp. 769–777, Apr. 2008.

- [29] Keysight Technologies, "What is the difference between an equivalent time sampling oscilloscope and a real-time oscilloscope?" Tech. Rep. [Online]. Available: <https://www.testworld.com/wp-content/uploads/difference-between-equivalent-time-and-real-time-oscilloscopes.pdf>

**Erfan Ghaderi** (S'17) received the B.Sc. degree in electrical engineering from Sharif University of Technology, Tehran, Iran, in 2012, and the M.Sc. degree in circuits and systems from University of Tehran, Tehran, in 2015. He received his Ph.D. degree from the School of Electrical Engineering and Computer Science at Washington State University, Pullman, WA, USA, in 2020. He is currently with Intel Corporation as an Analog Design Engineer. His research interests include integrated circuit design for high speed data converters, phased array applications, and time-domain signal processing.

**Subhanshu Gupta** (S'03-M'11-SM'16) received the B.E. Degree from the National Institute of Technology (NIT), Trichy, India, in 2002, and the M.S. and Ph.D. degrees from the University of Washington in 2006 and 2010, respectively. He is currently an Assistant Professor of Electrical Engineering and Computer Science at Washington State University. From 2011 to 2014, he was with the RFIC group at Maxlinear Inc. where he worked on silicon transceivers and data converters for cable/satellite communication radios.

He has received the National Science Foundation CAREER award in 2020, the Analog Devices Outstanding Student Designer Award in 2008, and the IEEE RFIC Symposium Best Student Paper Award (3rd place) in 2011. He has served as Guest Editor for IEEE Transactions of Circuits and Systems – I and IEEE Design and Test Magazine in 2019 and is serving as the Associate Editor for IEEE Transactions of Circuits and Systems – I for 2020-21. His research interests include large-scale phased arrays and wideband transceivers, low-power time-domain circuits and systems, and stochastic optimization techniques for next-generation wireless communications, biomedical, and cryogenic sensors.