### Single-Rail Adiabatic Logic for Energy-Efficient and CPA-Resistant Cryptographic Circuit in Low-Frequency Medical Devices

Amit Degada, Himanshu Thapliyal, Senior Member, IEEE

Designing energy-efficient and secure cryptographic circuits in low-frequency medical devices are challenging due to low-energy requirements. Also, the conventional CMOS logic-based cryptographic circuits solutions in medical devices can be vulnerable to side-channel attacks (e.g. correlation power analysis (CPA)). In this article, we explored single-rail Clocked CMOS Adiabatic Logic (CCAL) to design an energy-efficient and secure cryptographic circuit for low-frequency medical devices. The performance of the CCAL logic-based circuits was checked with a power clock generator (2N2P-PCG) integrated into the design for the frequency range of 50 kHz to 250 kHz. The CCAL logic gates show an average of approximately 48% energy-saving and more than 95% improvement in security metrics performance compared to its CMOS logic gate counterparts. Further, the CCAL based circuits are also compared for energy-saving performance against dual-rail adiabatic logic, 2-EE-SPFAL, and 2-SPGAL. The adiabatic CCAL gates save on an average of 55% energy saving compared to 2-EE-SPFAL and 2-SPGAL over the frequency range of 50 kHz to 250 kHz. To check the efficacy of CCAL to design a larger cryptographic circuit, we implemented a case-study design of a Substitution-box (S-box) of popular lightweight PRESENT-80 encryption. The case-study implementation (2N2P-PCG integrated into the design) using CCAL shows more than 95% energy saving compared to CMOS for the frequency 50 kHz to 125 kHz and around 60% energy saving at frequency 250 kHz. At 250 kHz, compared to the dual-rail adiabatic designs of S-box based on 2-EE-SPFAL and 2-SPGAL, the CCAL based S-box shows 32.67% and 11.21% of energy savings, respectively. Additionally, the CCAL logic gate structure requires a lesser number of transistors compared to dual-rail adiabatic logic. The case-study implementation using CCAL saves 45.74% and 34.88% transistor counts compared to 2-EE-SPFAL and 2-SPGAL. The article also presents the effect of varying tank capacitance in 2N2P-PCG over energy efficiency and security performance. The CCAL based case-study was also subjected against CPA. The CCAL-based S-box case study successfully protects the revelation of the encryption key against the CPA attack, However, the key was revealed in CMOS-based case-study implementation.

Index Terms—Medical device, healthcare, hardware security, adiabatic logic, power clock generators, side-channel attacks, correlation power analysis attack, cryptographic circuits.

### I. INTRODUCTION

CCORDING to the World Health Organization report, A 1.9 billion adults were overweight, and out of which 35% were obese in 2017. Further, 340 million children and adolescents were obese or overweight in 2020. Higher body weight can lead to chronic diseases, such as cardiovascular diseases, hypertension, diabetes, degenerative to joints, musculoskeletal system disorders, and several cancers, e.g., liver, colon, ovarian, gallbladder, kidney, breast, and prostate [1]. The US Centers for Disease Control (CDC) classify obesity at epidemic proportions. The CDC reports say 6 in 10 adults in the US have a chronic disease and 4 in 10 adults suffers more than one chronic disease [2]. On the other end, the advancement in semiconductor technology has empowered the inclusion of medical devices in many chronic disease diagnostic, therapeutic processes, and patient monitoring. They are pervasive in medical labs, offices of physicians, and even implanted inside a patient's body, e.g. pacemaker, Implantable Cardiac Defibrillators (ICDs), and neurostimulators. Table I lists some of the medical devices and their frequency range of the operation.

Modern medical devices often aggregate physiological data, store the personal information of the patient and communicate

The article was submitted for the review on 6<sup>th</sup> October, 2021. This work is partially supported by National Science Foundation CAREER Award No. 1845448.

Amit Degada is currently Ph.D candidate at Department of Electrical and Computer Engineering, University of Kentucky, Lexington, KY-40506 USA. Himanshu Thapliyal is currently with the Department of Electrical Engineering and Computer Science, University of Tennessee, Knoxville, TN 37996 USA. (e-mail: hthapliyal@ieee.org).

TABLE I: Frequency range in medical applications.

| Reference    | Medical Application                   | Frequency range of operation |  |  |

|--------------|---------------------------------------|------------------------------|--|--|

| [3]          | Low frequency inductive               | Less than 200 kHz            |  |  |

|              | implants (pacemakers, ICD etc.)       |                              |  |  |

| [4] [5]      | Implant communication                 | 9 - 315kHz                   |  |  |

| [6]          | Bioelectrical impedance meter         | 50 kHz, 250 kHz              |  |  |

| [7]          | Electrical Impedance Myography (EIM)  | 50 kHz                       |  |  |

| [8] [9] [10] | Electrical Impedance Tomography (EIT) | 50 kHz to 250 kHz            |  |  |

| [11]         | CMOS wearable non-invasive            | 100 Hz to 1 MHz              |  |  |

|              | impedance meter                       |                              |  |  |

| [12]         | Hearing Aid                           | 32 khz to 8.00 Mhz           |  |  |

| [13]         | Magnetic Particle Imaging             | 1 kHz to 100 kHz             |  |  |

| [14] [15]    | (MPI) systems<br>Low data-rate Body   | 10 kHz to 10 MHz             |  |  |

| [14] [13]    | Couple communication (BCC)            | TO KITZ TO TO WITTZ          |  |  |

| [16]         | Home Health Hub                       | 200 kHz to 1.0 MH:           |  |  |

to the cloud. Some of these devices, e.g. medical implants are battery-powered and their operational life is limited up to 10 years [17] [18]. Over the years, many researchers have raised concerns about compromising sensitive personal and physiological information. The compromised device can perform unauthorized command execution and data transmission [19], create electrical shocks [20] [21] and deplete battery [22]. It can compromise the secrecy and privacy of the patient information, however, in some cases it could be life-threatening. It becomes of utmost importance to protect user-information by including cryptographic coprocessors in device design. Security often comes with the cost of increment in the power consumption [23] [24] [25] [26]. Therefore, designing energy-efficient and secure cryptographic coprocessor circuits in medical devices is an interesting research direction.

2

Lightweight Cryptographic (LWC) cipher is one of the preferred solution to provide encryption at low-energy budgets [27], [28], [29]. However, in recent years, the LWC ciphers have been found vulnerable against Side-Channel Analysis (SCA) attacks, e.g. heat emission, electromagnetic radiation, power analysis [30], [31], and timing attacks [32]. The work in [14] [33] lists several possible SCA over medical devices. Among different possible SCA, the Correlation Power Analysis (CPA) attack is easy to implement and found more lethal to reveal the encryption key.

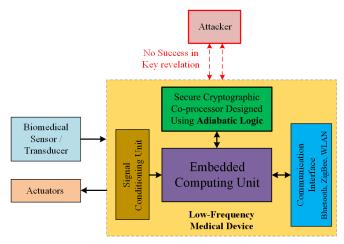

Fig. 1: Adiabatic Logic as preferred choice to design energy-efficient and secure cryptographic coprocessor.

Currently, CMOS-based computing technology is reaching to its limit in energy efficiency with scaling down of the technology. There are two possible directions to reduce the energy consumption: (i) to reduce the energy required to distinct the logic '1' from logic '0' (ii) conserve the energy from one logical operation to the next [34] [35]. The adiabatic logic works on the energy recovery principle and is classified under the second approach mentioned above. Adiabatic logic in bulk MOSFET has emerged as an attractive choice for the designer compared to conventional CMOS due to its superior energy performance and CPA resilience. In this article, we use adiabatic logic to design energy-efficient and secure lightweight cryptographic coprocessors in medical devices (Figure 1). The adiabatic logic circuits recover the energy stored inside the load capacitor (rather than dissipating as heat), thus, results in significantly low-power consumption. Further, the power traces of the adiabatic logic circuits are uniform in shape, unlike the conventional CMOS logic circuits. The uniform power traces is a very important property to disguise the processed information. The above property helps to combat the CPA. Earlier, we proposed two-phase sinusoidal clocking based adiabatic logic 2-phase Energy Efficient Secure Positive Feedback Adiabatic Logic (2-EE-SPFAL) [36] and 2-phase Symmetric Pass Gate Adiabatic Logic (2-SPGAL) [37]. The above solution enables the design of the low-energy and CPA secure circuit. The 2-EE-SPFAL and 2-SPGAL are classified as dual-rail adiabatic logic as they produce two outputs at the logic gate,  $V_{out}$  and  $\overline{V_{out}}$ . The dual-rail adiabatic logic uses the two-transistor logic evaluation network to balance the

switching activities, and therefore have uniform power traces. The above feature results in a larger transistor count overhead.

In this research, we address the above issue by exploring the single-rail adiabatic logic called Clocked CMOS Adiabatic Logic (CCAL). The CCAL was previously proposed in [38] with preliminary analysis limited to reduction in energy consumption for logic gates and a chain of inverters. It is interesting to see the security performance of the CCAL. Further, the energy and security performance of the adiabatic logic circuits largely depends upon the Power-Clock Generator (PCG) integrated with the logic circuit. The poor interfacing suffers a reduction in energy-saving and compromised security (explained in Section II). In this article, we evaluate the energy efficiency and security performance of the CCAL logic to design a secure cryptographic circuit with PCG integrated into the design. Further, the physiological signals in human bodies are typically a few tens to hundreds of the frequency range. In the digital domain, after sampling the operational frequencies are mostly limited up to a few kHz (Table I). The adiabatic logic saves significant energy consumption compared to its CMOS counterpart at low-frequency applications. Some example of the low-frequency medical device includes inductive implants, bioimpedance meter, Electrical Impedance Myography (EIM), hearing aids, Electrical Impedance Tomography (EIT), Magnetic Particle Imaging (MPI), and Body-Coupled Communication (BCC), etc. In this article, we evaluate the performance of the CCAL based cryptographic circuit for the frequency range of 50 kHz to 250 kHz.

#### A. Key Contribution

The key contributions of this work are as follows:

- The article explores CCAL, a novel single-rail Clocked CMOS Adiabatic Logic (CCAL) to design energyefficient and secure cryptographic circuits. The CCAL can be an alternate choice for low-energy and CPAresistant medical devices.

- The case-study implementation of PRESENT-80 S-Box circuitry saves more than 95% energy for frequency range 50 kHz to 125 kHz and approximately 60% more energy saving at 250 kHz compared to its CMOS counterpart. The above energy saving can be highly beneficial to design low-power cryptographic circuits.

- The case-study implementation shows saving of 45.74% and 34.88% of transistors compared to 2-EE-SPFAL [36] and 2-SPGAL [37]. At 250 kHz, compared to the dual-rail adiabatic designs of S-box based on 2-EE-SPFAL and 2-SPGAL, the CCAL based S-box shows 32.67% and 11.21% of energy savings, respectively. Thus, CCAL can be an alternate choice to design a secure and energy-efficient cryptographic circuit with lesser transistor overhead compared to its dual-rail adiabatic logic counterpart.

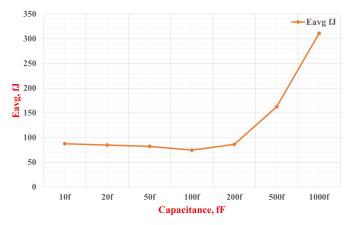

- We also presents the effect of varying tank capacitance in 2N2P-PCG over energy efficiency and security performance. We demonstrate that having 200 fF value of tank capacitor  $(C_E)$  in 2N2P-PCG can provide optimum energy and security features.

- The single-rail CCAL based circuitry removes the need for discharge circuitry required in its dual-rail counterpart. It helps to reduce the external need for the control signals for discharge circuitry.

- We demonstrate that the PRESENT-80 using CCAL can successfully defend the encryption key against the CPA attack for both 2N2P-PCG integrated into the design. However, the encryption key is revealed in the same counterpart design using CMOS.

### B. Organization of the paper

This article is organized as follows. The background information related to the research is briefly explained in Section II. In Section III, we present the CCAL logic gate structure, energy efficiency, and security metric performance. Section IV presents PRESENT-80 S-box design as a case-study implementation, compare the transistor count requirement in CCAL and other competitive logic design choice and provides energy and security performance analysis. Section V discusses the effect of varying tank capacitor values in PCG tank circuit over energy and security performance in case-study implementation. Section VI discusses the simulation of the CPA attack over the PRESENT-80 S-box. Section VII presents the discussion and conclusion.

#### II. BACKGROUND

In recent years, researchers have shown the effectiveness of power-analysis attacks to reveal the encryption key in cryptographic circuits. There have been many countermeasures are proposed, e.g., masking [31], random instruction injection [39], non-deterministic processors [40], random register renaming [41], secure co-processors [42], and cell-level countermeasures [43]. In this work, we employ the cell-level countermeasure, i.e. to build secure logic gates. Adiabatic logic design is one such approach, that can thwart the power-analysis attacks such as CPA.

In this section, we briefly discuss the adiabatic logic and the common metrics used to evaluate CPA resilience. Further, the energy and security performance of adiabatic logic circuits largely depend on the Power-Clock Generator (PCG) integrated into the design. We also provide a brief overview of the type of the PCG integrated with design.

### A. Adiabatic logic

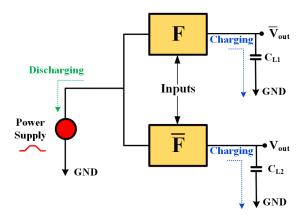

The adiabatic logic circuit techniques have emerged as an attractive choice to design cryptographic circuits in recent years. The adiabatic circuit recovers the stored charge in load capacitance of the logic gates to the power-clock circuits. Compared to the conventional CMOS circuit that uses the DC voltage to power up the circuits, the adiabatic logic circuits use a slow-varying voltage signal. This slow-varying voltage signal appears as a constant current source for a capacitive load [45]. The ramp signal (generated from PCG) is a practical way to achieve the constant current source. Figure 2 illustrates the switching model, discharging and charging current path for the load capacitor current.

3

Fig. 2: Charging and discharging in adiabatic circuits [44].

We can see in Figure 2 that adiabatic logic circuit employs two logic evaluation blocks, F and  $\overline{F}$ , that outputs  $V_{out}$  and  $\overline{V}_{out}$  respectively. The two complementary logical outputs (called dual-rail logic) are necessary to balance the switching activities., that balance the current passing into logic blocks. The above property is helpful to maintain nearly uniform current dissipation for all possible logic inputs. Therefore, dual-rail adiabatic logic circuits are the most commonly employed by researchers to design low-energy and CPA resilience circuits low-frequency devices.

Equation 1 mathematically describes the energy consumption in adiabatic logic circuits. The C is load capacitor, R is lumped resistance, V is the full-swing voltage of the power-clock circuit and T is the time period of charging and discharging operation. We can see that if the given frequency is lower (i.e. higher T) then it is possible to have the energy consumption significantly lower compared to the conventional energy dissipation in CMOS. The above property to thwart CPA attacks and lower energy consumption makes adiabatic logic, an ideal choice to design low-frequency cryptographic circuit in medical Devices. In this research, we explore one such technique called CCAL.

$$E_{\rm diss} = \frac{RC}{T}CV^2 \tag{1}$$

### B. Security Performance Metrics for CPA-Resistance

The Correlation Power Analysis (CPA) attack is one of the widely used power-analysis based side-channel attacks. Its relatively simple implementation and higher success rate have made it an attractive choice for attackers. Further, the CPA is equally effective to reveal the stored encryption key for both symmetric and asymmetric cryptographic algorithms. In the previous section, we have seen that adiabatic logic is an attractive design choice to design the CPA resilient circuit. Normalized Energy Deviation (NED) and Normalized Standard Deviation (NSD) are commonly used metrics to compare the CPA resilience performance against CMOS circuits [44] [46] [47] [48] [49] [50].

$$NED = \frac{(E_{\text{max}} - E_{\text{min}})}{E_{\text{max}}} \tag{2}$$

$$NSD = \frac{\sigma}{E_{avg}} = \frac{1}{E_{avg}} \sqrt{\sum_{k=1}^{N} \frac{(E_i - E_{avg})^2}{N}}$$

(3)

The NED and NSD values are measured for all possible cyclic input permutations. The NED and NSD values are measured in terms of the percentage. The difference between the minimum and maximum energy consumption for all input combinations is referred to as NED (Equation 2). The NSD value (Equation 3) is the mean square difference between the instantaneous energy consumption of input to the average energy consumption for all possible outcomes. NSD gives more insight into how much inputs are deviated compared to average energy consumption in given adiabatic logic circuits. For an ideal adiabatic circuit, there will be equal energy distribution for all possible cyclic inputs, thus NED and NSD values are zero. For practical circuits, lower NED and NSD metrics values make it the better choice for CPA resilience performance.

### C. Integrated Power-Clock Generator

In this section, we explain the design of the Power Clock Generator (PCG) for adiabatic circuits. In the adiabatic circuit, unlike the conventional CMOS, the circuit operates on the slow-varying power-clock signal. The efficient design of the PCG is of utmost importance for adiabatic circuits. The PCG recovers the charge from the adiabatic logic core to the oscillator capacitor as well as inductor during charge-recovery operation. PCG usually consumes a large fraction of the power. Poor design and its inefficient integration with the design result in less energy-efficient and secure design. Therefore, it becomes necessary to evaluate the energy performance of the adiabatic circuit with PCG integrated into the design.

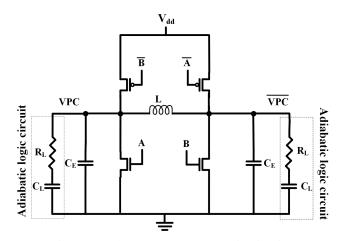

Fig. 3: Synchronous 2N2P-PCG circuit [51].

Over the years, many solutions PCG designs have been proposed to generate sinusoidal power clocking signals. The synchronous resonant PCGs have more energy conversion efficiency. In this work, we integrate 2N2P-PCG with adiabatic logic circuits and its schematic is shown in Figure 3 [51]. The 2N2P-PCG uses an external inductor, two PMOS, two NMOS, and two external capacitor  $C_E$ .

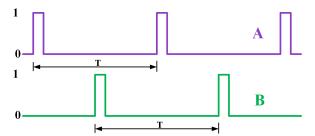

Fig. 4: Control signals in 2-Phase PCG design [51].

In this article, we use the external inductor as on-chip inductors lead to a low Q value. The inherent structure and operation of the CCAL makes the lumped capacitance of the inductor independent of the input logic signal and remains constant. We use the external balancing capacitance  $C_E$  to adjust the capacitance value for better energy efficiency.

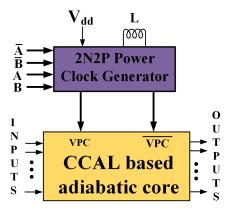

Fig. 5: 2N2P-PCG interfacing with the CCAL based adiabatic logic circuits.

The 2N2P-PCG requires four external time-base signals. The external time-base signals can help to synchronize the adiabatic circuits in larger conventional non-adiabatic circuits. Figure 4 shows the external time-base control signals used to operate 2N2P-PCG. The 2N2P-PCG generates two out-of-phase signals by two identical circuits operating in a lock-step manner. The operation frequency of the 2N2P-PCG is given by Equation 4. CCAL logic requires two out-of-phase sinusoidal power-clock signals, VPC and  $\overline{VPC}$ . Figure 5 shows the interfacing of 2N2P-PCG with the CCAL logic circuits.

$$f_0 = \frac{1}{2\pi\sqrt{L\left(\frac{C}{2}\right)}}\tag{4}$$

# III. CLOCKED CMOS ADIABATIC LOGIC (CCAL) AND ITS EVALUATION IN ENERGY-EFFICIENCY AND SECURITY METRICS

In this section, we will first illustrate the background on the logic gate structure of CCAL. Then, we will present the energy efficiency and security performance evaluation of CCAL logic gates with 2N2P-PCG integrated into the design.

### A. Background on Clocked CMOS Adiabatic Logic (CCAL)

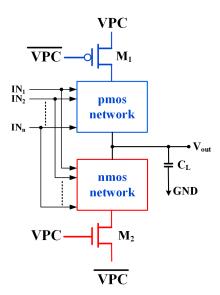

The Clocked CMOS Adiabatic Logic (CCAL) was previously proposed in [38] with preliminary analysis limited to reduction in energy consumption for logic gates and a chain of inverters. Figure 6 shows the generalized gate structure of CCAL. It consists of two primary parts, (i) CMOS logic (ii) clock connection which connects CMOS logic to the sinusoidal clocking part. The signals VPC and  $\overline{VPC}$  are two out-of-phase sinusoidal power clocks. The operation of CCAL can be explained in two stages: (i) Evaluation (E) (ii) Recovery (R). During the Evaluation stage, when the voltage at both clock signals is more than the threshold voltage  $(V_{th})$  then it turns on both transistor M1 and M2 (clock connection network). Then the PMOS and NMOS blocks evaluate the output logic based on the input signal logic. During the Recovery (R) phase, the output voltage stored in load capacitance is held until the next evaluation phase.

There have been many low-energy solutions in the research literature that works low-frequency operation. The adiabatic circuit-based cryptographic circuits are found to defend encryption keys against power-analysis attacks. Earlier, we proposed the two-phase sinusoidal clocking-based dualrail adiabatic logic 2-SPGAL [37] and 2-EE-SPFAL [36]. The CCAL can be an alternate choice to design CPA secure and energy-efficient cryptographic circuits. The single-rail adiabatic, e.g. CCAL has less logic overhead compared to its dualrail adiabatic logic counterpart. The above properties can be highly beneficial for resource-constrained IMDs. Further, the dual-rail logic, 2-EE-SPFAL [36] and 2-SPGAL [37] requires the additional discharge circuitry and corresponding control signals. The CCAL network removes the need for discharge circuitry and the logic gate structure is very similar to the CMOS logic gate.

However, the performance of the adiabatic logic is largely affected by the integration of the PCG. It is important to investigate the performance of the CCAL based cryptographic circuits energy efficiency and security performance with the integration of PCG in design. Therefore, we evaluated the performance of the CCAL based circuits with 2N2P-PCG integrated into the design.

## B. Energy-efficiency and security evaluation of CCAL logic gates

Logic gates are the primary constituent of a larger circuit. It becomes important to check the energy and security metrics performance to build low-energy and secure cryptographic circuits. In this section, we explain the energy-efficiency and security performance of the CCAL logic gates. We have compared the simulation results of the CCAL logic gate with CMOS, 2-EE-SPFAL [36], and 2-SPGAL [37] logic gates.

The energy consumption in medical devices should be as minimal as possible. Further, to build a secure circuit the variation in energy consumption for input combination variation should be ideally zero. The CPA calculates the correlation between hypothetical power traces of all possible keys and collected power traces from the circuit. Uniform power traces disguise the linear dependency. To look at this feature at the

Fig. 6: Clocked CMOS Adiabatic Logic (CCAL) gate schematic [38].

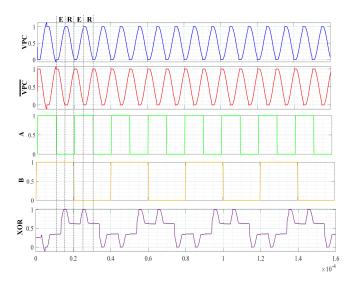

Fig. 7: CCAL-based XOR logic gate waveform with 2N2P-PCG integrated into the design.

circuit level, we check the energy performance of the logic gate at all possible change in input values.

$$E = \int_0^T V_P I_P dt \tag{5}$$

The energy consumption is the integration of the product of voltage  $(V_{\rm p})$  and current  $(I_{\rm p})$ , i.e. power consumption for input signal [52]. We built CCAL logic gates using 45nm technology and considered the load of 10 fF. Further, the energy and security performance of adiabatic logic circuits largely depends upon the PCG integrated into the design. Therefore, the energy and security metric performance was evaluated for logic gates with 2N2P-PCG integrated into the design. We target particularly low-frequency medical device

encryption, therefore, the frequency range of 50 kHz to 250 kHz is considered.

The variation in energy consumption value provides more insight than observing the current traces. We used SPICE simulation to collect energy consumption value for a total of  $2^{2n}$  possible cyclic variations in the n-bit circuit. The energy consumption values can be used in Equation 2 and 3 equation to calculated NED and NSD value. For ideal conditions, equal energy consumption results in zero NED and NSD values. However, for practical scenarios, the NED and NSD value should be as low as possible. Having lower NED and NSD value results in less correlation between hypothetical and actual power traces. Thus, the circuit can protect the stored encryption key.

It is very important to observe the energy saving in CCAL compared to other logic gates. For equal comparision, the dual rail logic circuits 2-EE-SPFAL [36] and 2-SPGAL [37] are designed with 2N2P-PCG integrated into the design, similar to the CCAL counterpart. For the energy performance metric, we have listed  $E_{\min}$ ,  $E_{\max}$  and  $E_{\text{avg}}$ . A smaller difference between  $E_{\min}$ , and  $E_{\max}$  indicates the energy consumption across all possible input combinations is smaller and results in a better secure circuit. Further, the  $_{\text{avg}}$  for each logic gate should be as low as possible for better energy efficiency.

Table II shows the comparison of CCAL AND logic gate with its counterpart in CMOS, 2-EE-SPFAL [36], and 2-SPGAL [37]. The CCAL AND logic gate has the lowest  $E_{\rm avg}$  value for the frequency range of 50 kHz to 250 kHz. The CCAL AND logic gate has on an average of 4.7248 fJ  $E_{\rm avg}$  for the frequency range of 50 kHz to 250 kHz. While in its CMOS, 2-EE-SPFAL [36], and 2-SPGAL [37] counterpart the average of  $E_{\rm avg}$  is 7.7681 fJ, 11.9258 fJ, and 10.7920 fJ. Therefore, we can conclude that the sinusoidal clocking circuits on top of the PMOS and NMOS network help to reduce significant energy consumption compared to conventional CMOS logic and also to its dual-rail adiabatic logic counterpart. Table III summarizes the average energy saving (in %) in CCAL-based AND logic gate compared to its CMOS, 2-EE-SPFAL [36], and 2-SPGAL [37] counterpart.

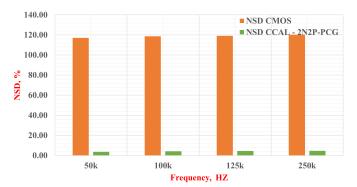

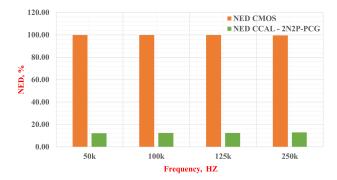

Fig. 8: NED value comparison for AND logic gate.

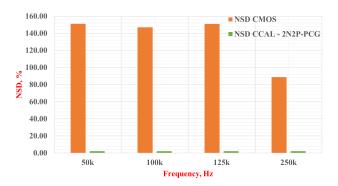

For the secure encryption circuit design, it becomes important to check the NED and NSD performance of the logic gate before building the larger circuits. In this work, we primarily compared the NED and NSD value of CCAL logic gates with

Fig. 9: NSD value comparison for AND logic gate.

their CMOS counterpart. The CMOS circuit is considered the benchmark because has been shown to be vulnerable to CPA attacks. Figure 8 and 9 shows the comparison of NED and NSD security performance metrics for CCAL and CMOS AND logic gate. We can see that CCAL AND logic gate has a significantly smaller value of NED and NSD compared to CMOS AND logic. The average NED value for CCAL AND logic gate is 10.81% compared to 99.39% in its CMOS counterpart for the frequency range of 50 kHz to 250 kHz. This results in 89.13% better NED value in CCAL AND logic. Similarly, we can see an average of 96.45% better NSD value in CCAL AND logic gate compared to its CMOS counterpart in the same frequency range.

Similar to the AND logic gate, we repeated the simulation experiment for the XOR logic gates for all four logic designs in consideration. Table IV lists the summary of simulation results for the XOR logic gate for the frequency range of 50 kHz to 250 kHz. We can see in Table IV that the CCAL XOR logic gate has superior energy performance results. The average of <sub>avg</sub> value, for the frequency range of 50 kHz to 250 kHz, in the CCAL XOR logic gate is 5.40 fJ. However, in the same CMOS, 2-EE-SPFAL [36], and 2-SPGAL [37] counterparts have an average of avg values are 13.0968 fJ, 11.6237 fJ, and 11.0453 fJ. Table V saving lists the energy saving in CCAL XOR logic gate compared to single-rail counterpart, CMOS, and dual-rail adiabatic logic counterpart 22-EE-SPFAL [36], and 2-SPGAL [37]. The CCAL XOR logic gate saves on an average more than 58% energy compared to CMOS, and 53% and 51% more energy saving compared to 2-EE-SPFAL [36], and 2-SPGAL [37] based XOR gate respectively.

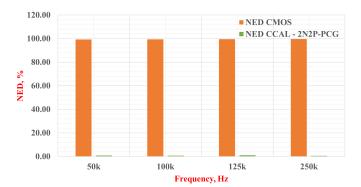

Figure 10 and 11 graphically show the comparison of NED and NSD security metric performance for CCAL and CMOS XOR logic gate. Similar to the AND logic gate, the CCAL based XOR logic gate is superior in NED and NSD security metric performance. The CCAL XOR logic gate has an average of 99.23% better NED value compared to the CMOS XOR logic gate over the frequency range of 50 kHz and 250 kHz. Further, an average of 99.61% better NSD value is noted for the CCAL XOR logic gate compared to its CMOS counterpart in the same frequency range.

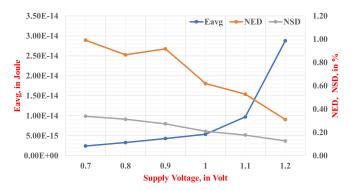

Figure 12 helps to understand the relation between the  $E_{\rm avg}$  and supply voltage at frequency value 100 kHz, for CCALbased XOR logic gate, with 2N2P-PCG integrated into the

$E_{\text{avg}}(fJ)$

NED (%)

NSD (%)

7.2078

99.47

119.18

11.8591

2.07

0.59

TABLE II: Energy-efficiency and security performance comparison for AND logic gate.

|                      | 50 kHz  |                        |              |        | 100 kHz |                        |              |        |

|----------------------|---------|------------------------|--------------|--------|---------|------------------------|--------------|--------|

| Metric               | CMOS    | <b>2-EE-SPFAL</b> [36] | 2-SPGAL [37] | CCAL   | CMOS    | <b>2-EE-SPFAL</b> [36] | 2-SPGAL [37] | CCAL   |

| $E_{\min}(fJ)$       | 0.3745  | 11.8596                | 9.1762       | 4.8398 | 0.1873  | 11.7577                | 11.1575      | 4.5769 |

| $E_{\max}(fJ)$       | 38.0678 | 12.1081                | 9.2971       | 5.3530 | 29.8538 | 11.9808                | 11.3861      | 5.1297 |

| $E_{\text{avg}}(fJ)$ | 9.8487  | 12.0227                | 9.2425       | 4.9780 | 7.6402  | 11.8864                | 11.2964      | 4.7216 |

| NED (%)              | 99.02   | 2.05                   | 1.30         | 9.59   | 99.37   | 1.86                   | 2.01         | 10.78  |

| NSD (%)              | 117.08  | 0.60                   | 0.40         | 3.55   | 118.71  | 0.57                   | 0.58         | 4.24   |

|                      | 125 kHz |                        |              |        |         | 250 kl                 | Hz           |        |

| Metric               | CMOS    | 2-EE-SPFAL [36]        | 2-SPGAL [37] | CCAL   | CMOS    | 2-EE-SPFAL [36]        | 2-SPGAL [37] | CCAL   |

| $E_{\min}(fJ)$       | 0.1498  | 11.7009                | 11.1185      | 4.5224 | 0.0749  | 11.7677                | 11.1600      | 4.3702 |

| $E_{\max}(fJ)$       | 28.2615 | 11.9486                | 11.3740      | 5.0853 | 25.1593 | 12.0363                | 11.4598      | 4.9547 |

TABLE III:  $E_{\text{avg}}$  - Energy saving (in %) in CCAL AND logic gate.

4.6682

11.07

4.42

6.3756

99.70

120.26

11.9351

2.23

0.65

11.3488

2.62

0.78

4.5316

11.80

4.66

11.2804

2.25

0.67

| Type of the logic Baseline Logic to compare |                                 | 50 kHz         | 100 kHz        | 125 kHz        | 250 kHz        |

|---------------------------------------------|---------------------------------|----------------|----------------|----------------|----------------|

| Dual-Rail Adiabatic                         | 2-EE-SPFAL [36]<br>2-SPGAL [37] | 58.60<br>46.14 | 60.28<br>58.20 | 60.64<br>58.62 | 62.03<br>60.07 |

| Single-Rail                                 | Conventional CMOS               | 49.46          | 38.20          | 35.23          | 28.92          |

TABLE IV: Energy-efficiency and security performance comparison for XOR logic gate.

| 50 kHz               |         |                        |              |        | 100 kl  | Hz                     |              |        |

|----------------------|---------|------------------------|--------------|--------|---------|------------------------|--------------|--------|

| Metric               | CMOS    | <b>2-EE-SPFAL</b> [36] | 2-SPGAL [37] | CCAL   | CMOS    | <b>2-EE-SPFAL</b> [36] | 2-SPGAL [37] | CCAL   |

| $E_{\min}(fJ)$       | 0.2459  | 11.7161                | 11.1072      | 5.5896 | 0.1529  | 11.5779                | 11.0179      | 5.3592 |

| $E_{\max}(fJ)$       | 32.5163 | 11.7165                | 11.1077      | 5.6366 | 25.9986 | 11.5783                | 11.0184      | 5.3926 |

| $E_{\text{avg}}(fJ)$ | 16.3697 | 11.7163                | 11.1075      | 5.6114 | 13.0968 | 11.5781                | 11.0181      | 5.3775 |

| NED (%)              | 99.244  | 0.003                  | 0.004        | 0.833  | 99.412  | 0.004                  | 0.004        | 0.619  |

| NSD (%)              | 69.537  | 0.001                  | 0.002        | 0.284  | 69.671  | 0.002                  | 0.002        | 0.210  |

|                      |         | 125 kl                 | Hz           |        |         | 250 kl                 | Hz           |        |

| Metric               | CMOS    | 2-EE-SPFAL [36]        | 2-SPGAL [37] | CCAL   | CMOS    | <b>2-EE-SPFAL</b> [36] | 2-SPGAL [37] | CCAL   |

| $E_{\min}(fJ)$       | 0.1250  | 11.5692                | 10.9915      | 5.3095 | 0.0919  | 11.6306                | 11.0635      | 5.2555 |

| $E_{\max}(fJ)$       | 22.8099 | 11.5698                | 10.9921      | 5.3643 | 22.7796 | 11.6313                | 11.0642      | 5.2870 |

| $E_{\text{avg}}(fJ)$ | 11.4741 | 11.5695                | 10.9918      | 5.3405 | 11.4466 | 11.6309                | 11.0638      | 5.2711 |

| NED (%)              | 99.452  | 0.005                  | 0.006        | 1.1023 | 99.597  | 0.006                  | 0.007        | 0.595  |

| NSD (%)              | 69.752  | 0.003                  | 0.003        | 0.389  | 69.906  | 0.003                  | 0.003        | 0.206  |

TABLE V:  $E_{\text{avg}}$  - Energy saving (in %) in CCAL XOR logic gate.

| Type of the logic   | Type of the logic Baseline Logic to compare |                | 100 kHz        | 125 kHz        | 250 kHz        |

|---------------------|---------------------------------------------|----------------|----------------|----------------|----------------|

| Dual-Rail Adiabatic | 2-EE-SPFAL [36]<br>2-SPGAL [37]             | 52.11<br>49.48 | 53.55<br>51.19 | 53.84<br>51.41 | 54.68<br>52.36 |

| Single-Rail         | Conventional CMOS                           | 65.72          | 58.94          | 53.46          | 53.95          |

design. We also plotted the corresponding NED and NSD value along with  $E_{\rm avg}$  on the same graph. We see that  $E_{\rm avg}$  is decreasing with lowering the supply voltage. However, the security performance metric NED and NSD are higher with low supply voltage. The CCAL-based XOR logic gate shows better security performance as the supply voltage reaches a higher value. The better security performance is attributed to the minimum deviation in energy number.

It is important to note that NED and NSD values in dualrail adiabatic logic (2-EE-SPFAL [36], and 2-SPGAL [37]) compared to single-rail adiabatic logic CCAL. This is expected behavior as dual-rail circuit uses two balanced switching logic evaluation networks F and  $\overline{F}$ . The switching in the evaluation block happens in a complementary fashion. Thus, the more uniformity in current results in logic gate output. However, for practical side-channel attacks (e.g. CPA in our case), it becomes important to check whether the CCAL based encryption circuit can prevent the revelation of the encryption key. The later part of the paper explains the CPA attack performance results over CCAL logic-based case-study implementation of the lightweight cryptographic cipher.

Fig. 10: NED value comparison for XOR logic gate.

Fig. 11: NSD value comparison for XOR logic gate.

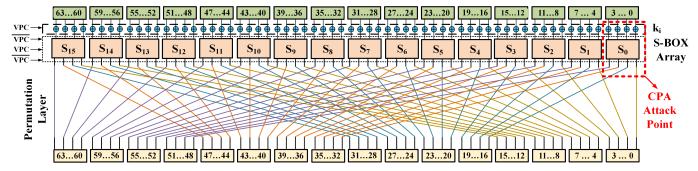

### IV. A CRYPTOGRAPHIC CIRCUIT CASE-STUDY: PRESENT-80 S-BOX DESIGNED USING CCAL

In this section, first, we provide background information on lightweight cryptographic cipher PRESENT. The Substitution-box (S-box) is a vital component in the PRESENT cipher. We use the S-box as case-study implementation and show the comparison of transistor count implementation in adiabatic logic CCAL, 2-EESPFAL [36] and 2-SPGAL [37]. We also provide energy and security metric performance of the case-study design with 2N2P-PCG integrated into the design.

### A. Background on PRESENT-80

The cryptographic cipher used in medical devices should be low-power and lightweight as they run on battery and have lim-

Fig. 12:  $E_{\text{avg}}$ , NED and NSD metric in CCAL-based XOR logic gate as a function of the supply voltage.

ited silicon space. PRESENT is one such popular lightweight cryptographic cipher [53]. Further, the counter mode operation in the PRESENT makes it suitable in challenge-response authentication [54]. The PRESENT comes in two variants based on the key size, 80-bit or 120-bit. The PRESENT-80, is an 80-bit key variant with a total of 32 rounds of encryption. In PRESENT-80, the first 31 rounds of encryption are identical and its schematic is shown in Figure 13.

The PRESENT-80 has three fundamental operations. First, the plain text is XORed with 64 bits of the key. During the second operation, the Substitution-box (S-box) does a nonlinear transformation of the 4-bit blocks, with a total of 16 such operations happening in parallel. The last operation is the permutation of S-box output to create further randomization. The S-box is the key constituent of PRESENT-80. Therefore, in this work, we have evaluated the transistor counts, energy efficiency, and security metrics performance comparison for S-box for 2-EE-SPFAL [36], 2-SPGAL [37], CCAL, and CMOS.

### B. Transistor Count Saving analysis in CCAL-based casestudy implementation of PRESENT-80 S-box

We can see from Figure 13 that S-box is a critical part of the PRESENT-80 implementation. In this section, we explain the S-box circuit implementation using four different logic circuits, i.e. 2-EE-SPFAL [36], 2-SPGAL [37], CCAL, and CMOS.

TABLE VI: Transistor count in PRESENT-80 S-box designed using dual-rail logic.

| Logic  | Number of   | <b>Total Transistor Counts</b> |              |  |  |  |

|--------|-------------|--------------------------------|--------------|--|--|--|

| Gates  | Logic Gates | <b>2-EE-SPFAL</b> [36]         | 2-SPGAL [37] |  |  |  |

| Buffer | 12          | 96                             | 72           |  |  |  |

| AND    | 16          | 224                            | 192          |  |  |  |

| OR     | 8           | 112                            | 96           |  |  |  |

| XOR    | 7           | 84                             | 70           |  |  |  |

Table VI illustrates the number of the transistors required to implement PRESENT-80 S-box using dual-rail adiabatic logic. The dual-rail adiabatic logic inherently works in pipeline fashion. In other words, the successive blocks of the circuits operate on different phases. In case of 2-phase clock, they are in-phase and out-of-phase [36] [37]. In order to make the output appear on the same clock phase, we need to put extra buffers for synchronization.

TABLE VII: Transistor count in PRESENT-80 S-box designed using single-rail logic.

| Logic       | Number of   | Total Trai | al Transistor Counts |  |  |

|-------------|-------------|------------|----------------------|--|--|

| Gates       | Logic Gates | CCAL       | CMOS                 |  |  |

| AND         | 16          | 128        | 96                   |  |  |

| OR          | 8           | 64         | 48                   |  |  |

| XOR         | 4           | 40         | 32                   |  |  |

| <b>XNOR</b> | 4           | 48         | 40                   |  |  |

Table VII represents the number of logic gates and transistor count for PRESENT-80 S-box implemented using single-phase logic. The PRESENT-80 S-box implementation using CCAL is similar to CMOS-based implementation, except it requires

Fig. 13: one round of PRESENT-80 implementation using 2-phase adiabatic logic [37].

two complementary sinusoidal power clocks and two extra transistors for clocking circuitry on top of the logic evaluation network. In the previous section, we have seen that the CCAL logic gates require significantly less energy consumption, as well as improve the resilience against the CPA attack.

TABLE VIII: Transistor count comparison for CCAL, 2-EE-SPFAL [36], 2-SPGAL [37] and conventional CMOS for PRESENT-80 S-box design.

| Logic           | Number of<br>Transistors | Overhead compared to CMOS, in % | Transistor Saving in CCAL, in % |

|-----------------|--------------------------|---------------------------------|---------------------------------|

| 2-EE-SPFAL [36] | 516                      | 138.89                          | 45.74                           |

| 2-SPGAL [37]    | 430                      | 99.07                           | 34.88                           |

| CCAL            | 280                      | 29.63                           | -                               |

| CMOS            | 216                      |                                 | -                               |

Table VIII presents the comparison of the number of transistors required to implement PRESENT-80 S-box for different logic. The dual-rail adiabatic logic has more balanced switching activities, thus resulting in a more secure structure against CPA. However, the inherent structure of dual-rail logic results in more transistor counts. The transistor count overhead in 2-EE-SPFAL [36], and 2-SPGAL [37] compared to their CMOS-based S-box counterpart is approximately 139% and 99% respectively. On the other hand, the transistor overhead in CCAL based CMOS is 29.63%. Further, the CCAL based S-box implementation saves 34.88% and 45.74% of transistor count compared to dual-rail logic 2-EE-SPFAL [36], and 2-SPGAL [37] respectively. For the space-limited IoT structure, the CCAL logic presents an alternative to design secure cryptographic circuits with less transistor overhead.

### C. Energy and Security Performance Evaluation of Case-Study Design PRESENT-80 S-Box

The CCAL based logic gates shows promising results for the NED, and NSD metrics. The CPA attack collects the power traces at the output of the S-box, thereby it is a vital component of the PRESENT-80 design. We implemented the S-Box design using the proposed CCAL and CMOS logic gates. The S-Box implementation requires both VPC and  $\overline{VPC}$  phases (Figure 13) of power clock to operate. The S-box designs using adiabatic logic were tested with 2N2P-PCG.

Table IX lists the energy-efficiency performance and calculated NED and NSD metrics. The energy consumption for adiabatic circuits was calculated for 2N2P-PCG integrated into

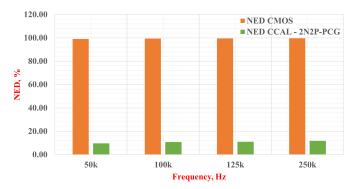

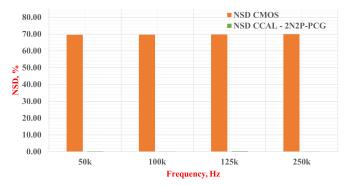

Fig. 14: NED value comparison for PRESENT-80 S-box.

Fig. 15: NSD value comparison for PRESENT-80 S-box.

the design. Similar to the logic gates, we collected the energy number in SPICE simulation for the frequency range 50 kHz to 250 kHz. The PRESENT-80 S-box circuit was designed at 45 nm technology and the load value was considered 10 fF. We can see in Table IX that CCAL based S-box shows better energy performance than CMOS, 2-EE-SPFAL [36] and 2-SPGAL [37] over frequency range 50 kHz to 250 kHz. The average of  $E_{\rm avg}$  for CCAL based S-box is 74.23 fJ for the frequency range 50 kHz to 250 kHz. For the same frequency range, the average of  $E_{\rm avg}$  in CMOS, 2-EE-SPFAL [36] and 2-SPGAL [37] is approximately 1981 fJ, 110 fJ and 80 fJ respectively. Therefore, adding a clocking network on top of the pmos and nmos circuit helps to reduce the energy consumption value.

Similar to logic gate, it is interesting to see the NED and NSD performance between CCAL and CMOS. Figure 14 and 15 shows graphical comparison for NED and NSD values

$E_{\text{avg}}(fJ)$

NED (%)

NSD (%)

1785.2113

99.94

151.00

70.4930

12.90

2.19

5.86

1.20

50 kHz 100 kHz 2-SPGAL [37] Metric **CMOS** 2-EE-SPFAL [36] 2-SPGAL [37] **CMOS** 2-EE-SPFAL [36] **CCAL** CCAL 106.7929 78.3831 16.1017 111.8714 80 0749 72.1344 68.4080  $E_{\min}(fJ)$ 8.0508  $E_{\text{max}}(fJ)$ 24427.7700 120.2409 84.0927 82.1965 13822.5800 114.3578 84.5114 78.1032 81.4804 2251.8734 110.3418 80.0390  $E_{\text{avg}}(fJ)$ 3713.2974 116.3666 78.5836 74.4624 NED (%) 99.94 7.25 99.93 12.24 6.62 12.41 NSD (%) 0.96 147.00 151.09 1.28 2.07 1.31 1.18 2.10 125 kHz 250 kHz 2-EE-SPFAL [36] 2-EE-SPFAL [36] 2-SPGAL [37] Metric **CMOS** 2-SPGAL [37] **CMOS CCAL** CCAL  $E_{\min}(fJ)$ 6.4407 105.8047 78.1838 67.3192 3.2203 103.2192 77.6512 64.2043  $E_{\max}(fJ)$ 11375.7700 113.0351 83.0035 76.8905 709.6414 110.2786 82.4870 73.7168 73.3781 79.3894

TABLE IX: Energy-efficiency and security performance comparison for PRESENT-80 S-Box.

TABLE X:  $E_{\text{avg}}$  - Energy saving (in %) in CCAL based PRESENT-80 S-Box.

12.45

2.11

175.7356

99.55

88.77

79.8261

5.81

1.19

| Type of the logic Baseline Logic to compare |                                 | 50 kHz        | 100 kHz       | 125 kHz       | 250 kHz        |

|---------------------------------------------|---------------------------------|---------------|---------------|---------------|----------------|

| Dual-Rail Adiabatic                         | 2-EE-SPFAL [36]<br>2-SPGAL [37] | 32.47<br>3.56 | 32.52<br>6.97 | 32.70<br>8.08 | 32.67<br>11.21 |

| Single-Rail                                 | Conventional CMOS               | 97.88         | 96.69         | 95.89         | 59.89          |

in CCAL and CMOS for S-box circuit. The NED and NSD values in CCAL based PRESENT-80 S-box is overall lower for the frequency range 50 kHz to 250 kHz. The average NED value for the CCAL S-box is 12.50%, while in CMOS Sbox it is 99.84% over frequency range 50 kHz to 250 kHz. The CCAL based S-box shows overall 97.48% improvement in NED security metric. Similarly, the NSD performance in CCAL-based S-box is average of 2.12% over frequency range 50 kHz to 250 kHz. For same frequency range, CMOS-based S-box have an average NSD value 134.46%. The CCALbased S-box have overall 98.43% better NSD performance for frequency range 50 kHz to 250 kHz.

109.0232

6.40

1.30

The CCAL-based S-box shows better security metric performance compared to its CMOS counterpart. We can see that CCAL-based S-box has better energy-efficiency performance compared to its dual-rail adiabatic counterpart. However, the dual-rail adiabatic logic, 2-EE-SPFAL [36] and 2-SPGAL [37] have better NED and NSD performance. The better security performance in dual-rail logic is an attribute of the balance switching activities in logic evaluation network. However, the CCAL has significant security performance improvement compared to CMOS. It will be interesting to see the performance of the CCAL based circuit against the CPA attack (explained in the next section).

### V. EFFECT OF VARYING CAPACITOR AND INDUCTOR IN LC TANK IN 2N2P-PCG FOR ENERGY-EFFICIENCY AND SECURITY PERFORMANCE ANALYSIS IN CASE-STUDY

The Q factor is a key parameter in the power analysis of the RLC resonator circuit. When the adiabatic circuit is integrated with 2N2P-PCG (Figure 3) then it can be modeled as an RLC circuit. Equation 6 shows the relation between the Q factor and average power dissipation. We need a larger Q factor in order to have minimum power dissipation. However, in the RLC circuit, the Q factor of the LC tank circuit depends upon the Q factor of inductor and capacitor with their parasitic resistance respectively [55].

106.2688

6.40

1.30

$$Q = 2\pi \frac{\text{Maximum Energy Stored}}{\text{Energy Dissipated per Cycle}}$$

(6)

Equation 7 shows the dependence of the Q factor of 2N2P-PCG tank circuit on Q factor of inductor  $(Q_L = \frac{R_L}{\omega_0 L})$ and capacitor  $(Q_C = \omega_0 CR_C)$  respectively. In the above equations,  $R_L$  is the parasitic resistance of the inductor, and  $R_C$  is the parasitic resistance of the capacitor [55]. Therefore, we hypothesize that there will be a certain value of the inductor and capacitor for which the Q factor is maximum. Higher Q can result in lower energy dissipation. Further, it will also be interesting to see the effect on security performance metrics.

$$Q_{\text{tank}} = \omega_0 C \left( R_L || R_C \right) = Q_L || Q_C \tag{7}$$

To check our hypothesis, we fixed the frequency value to 100 kHz. We calculated the different combinations of L and C (Equation 4) for the frequency 100 kHz. Similar to the logic gate energy and security experiment, we collected energy consumption values for a total of 256 cyclic combinations of the inputs in CCAL-based S-box circuitry. Figure 16 shows the  $E_{\text{avg}}$  at different capacitive value in LC tank circuit in 2N2P-PCG circuit. We can see that the lowest  $E_{avg}$  value of 74.46 fJ at capacitor value 100 fF.

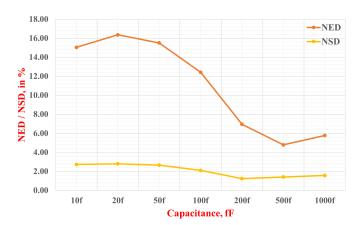

Further, we can also observe the effect on security performance metrics NED and NSD. Figure 17 shows the change in NED and NSD values at different values of the capacitors. The lowest NED and NSD values are observed are 4.79% and 1.40% at capacitor value 500 fF. The graph in Figure 17 helps to understand the capability of the circuit to thwart the Correlation Power Analysis (CPA) attack. The lowest value of

Fig. 16: Effect of varying capacitor and inductor values over Average energy consumption in PRESENT-80 S-xox.

Fig. 17: Effect of varying capacitor and inductor values over NED and NSD in PRESENT-80 S-box.

NED and NSD indicates that the circuit is more robust against CPA at 500 fF capacitance value in 2N2P-PCG.

Fig. 18: Energy-security trade-off in PRESENT-80 S-box designed using CCAL.

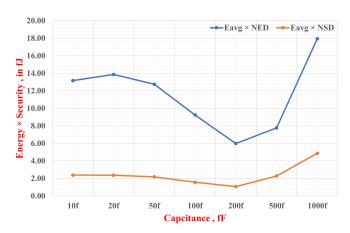

We define the energy-security trade-off product as  $Energy \times Security$  and measure in Joule. Previously, we have seen that the energy and security metrics performance shows the different trend for PCG tank capacitor  $C_E$  values.

The case-study implementation shows optimum energy performance for  $C_E$  value of 100 fF and security performance at 500 fF. For optimum energy and security performance, the trade-off product  $Energy \times Security$  should be minimum. Figure 18 shows an insight for the energy and security performance metrics together at different tank capacitor values. We can see that for capacitor value 200 fF has the lowest  $E_{avg} \times NED$  and  $E_{avg} \times NSD$  equal to 5.98fJ and 1.07fJ respectively. Thus, we can say that having 200 fF value of tank capacitor  $(C_E)$  in 2N2P-PCG can provide optimum energy and security performance together.

### VI. CPA ATTACK SIMULATION

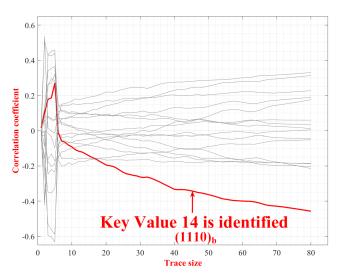

In the previous section, we demonstrated the efficacy of the CCAL to design low-energy and CPA resilient cryptographic circuits. The CCAL based S-box was energy efficient, however, the NED and NSD performance were relatively higher compared to Dual-Rail adiabatic logics 2-EE-SPFAL [36] and 2-SPGAL [37]. In this section, we subject the CCAL based S-box design against the CPA. The article [56] illustrates the procedure to carry out the CPA in SPICE simulation. We can see in Figure 13 that one round of PRESENT-80 encryption contains 16 identical blocks. Each block has four XOR logic gates and a non-linear transformation circuit, called S-box. Therefore, the output of S-box is considered as CPA attack point in the literature [56], [36], [37], [44]. The S-box takes the 4-bit input coming after XOR operation between the 4-bit key value and plain-text.

Fig. 19: Successful Revelation of Key=14 in on one round of PRESENT-80 encryption designed with CMOS.

The CPA attack requires the power traces collected from the attack point. The SPICE simulation was performed with a load value of 10 fF to collect the power traces. The simulation environment is noise-free and requires fewer traces for successful CPA. If a CPA attack is carried out in a noisy environment then it requires a larger number of traces. We collected power traces for the CMOS-based PRESENT-80 S-Box. The CPA attacks reveal the correct encryption key after 5120 power traces. Figure 19 shows the correlation

coefficient starts appearing different after 40 power traces. The distinct power consumption, therefore, the current makes the CPA successful over the CMOS-based S-box of PRESENT-80 encryption.

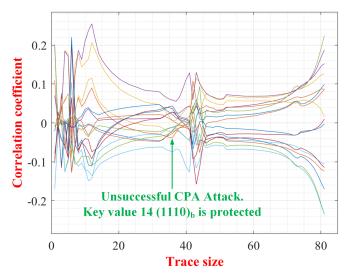

Fig. 20: Unsuccessful CPA attack on one round of PRESENT-80 encryption designed with CCAL and 2N-PCG.

The CCAL based S-box has better NED and NSD performance compared to CMOS. However, dual-rail adiabatic logic, e.g. 2-EE-SPFAL [36], and 2-SPGAL [37] have better NED and NSD values. It becomes important to see if CCAL based PRESENT-80 S-box is safe against the CPA attack. Similar to CMOS, we collected 12,000 power traces for the CCAL based PRESENT-80 S-box with 2N2P-PCG integrated into the design. Similar to our previous work on dual-rail adiabatic logic, 2-EE-SPFAL [36] and 2-SPGAL [37], the CCAL based S-box circuit protects the revelation of the encryption key (Figure 20). Therefore, higher NED and NSD value in CCAL compared to dual-rail logic does not affect the properties to protect the encryption key against the CPA attack.

### VII. DISCUSSION AND CONCLUSION

The cost and the reliability of the medical devices are the important factors to consider while selecting a technology with adiabatic logic. Bulk MOSFET at 45nm combined with adiabatic logic will provide a low-cost solution for medical devices that can also provide an energy-efficient and secure solution. Novel devices such as Junctionless MOSFET [57] and Tunnel FET [58] can also be explored with adiabatic logic for developing low-power and secure solutions. However, the designer should consider the cost and the reliability of the emerging devices when combined with adiabatic logic while making the design choice for medical devices. The low-frequency medical devices are vulnerable to side-channel attacks (e.g. Correlation Power Analysis (CPA) attack). The conventional approach to improve the CPA resistance results in an increase in power consumption. In this article, we used the single rail adiabatic circuit design technique called Clocked CMOS Adiabatic Logic (CCAL) to design cryptographic circuits in low-frequency medical devices. CCAL shows encouraging energy-saving and security performance compared to its dual-rail adiabatic logic and CMOS counterparts. Further, the CCAL enables the designer to reduce the transistor count in cryptographic hardware compared to existing solutions based on adiabatic logic proposed in the literature. We also demonstrated the capability of the CCAL based logic to thwart the CPA attack and protect the encryption key. Therefore, CCAL can be a promising design choice for the designer of medical devices to increase their battery longevity with improved CPA resistance while keeping the transistor overhead to minimal. While designing single rail adiabatic logic circuits, the stability in the outputs should be considered while cascading the designs. The stable outputs can be produced by inserting the flip-flop to sample the correct output at each stage [59]. Another alternative approach to provide stable outputs could be to use noise reduction circuitry that can be added to restore the signal degraded [60]. Some possible future research direction would be to check the performance of the CCAL-based circuit implementation with different types of Power Clock Generator, e.g., switch capacitor, stepwise charging, etc.

### REFERENCES

- "Obesity and overweight." World Health Organization, https://www. who.int/news-room/fact-sheets/detail/obesity-and-overweight, Last Accessed: 10-2-2021.

- [2] "Chronic disease in america." Center for Disease Control (CDC), https://www.cdc.gov/chronicdisease/tools/infographics.htm, Last Accessed: 10-2-2021.

- [3] T. G. Mahn, "Wireless medical technologies: Navigating government regulation in the new medical age," Fishs Regulatory & Government Affairs Group, 2013.

- [4] "Short Range Devices (SRD); Ultra Low Power Active Medical Implants (ULP-AMI) and accessories (ULP-AMI-P) operating in the frequency range 9 kHz to 315 kHz Harmonised Standard covering the essential requirements of article 3.2 of the Directive 2014/53/EU," ETSI (European Telecommunications Standards Institute), Sophia-Antipolis, France, Standard, Jun. 2016.

- [5] S. Hanna, "Regulations and standards for wireless medical applications," in *Proceedings of the 3rd international symposium on medical informa*tion and communication technology. Citeseer, 2009, pp. 23–26.

- [6] E. Völgyi, F. A. Tylavsky, A. Lyytikäinen, H. Suominen, M. Alén, and S. Cheng, "Assessing body composition with dxa and bioimpedance: effects of obesity, physical activity, and age," *Obesity*, vol. 16, no. 3, pp. 700–705, 2008.

- [7] S. B. Rutkove, K. S. Lee, C. A. Shiffman, and R. Aaron, "Test-retest reproducibility of 50 khz linear-electrical impedance myography," *Clinical Neurophysiology*, vol. 117, no. 6, pp. 1244–1248, 2006.

- [8] H. Wi, H. Sohal, A. L. McEwan, E. J. Woo, and T. I. Oh, "Multi-frequency electrical impedance tomography system with automatic self-calibration for long-term monitoring," *IEEE transactions on biomedical circuits and systems*, vol. 8, no. 1, pp. 119–128, 2013.

- [9] Y. Yang and J. Jia, "A multi-frequency electrical impedance tomography system for real-time 2d and 3d imaging," *Review of Scientific Instruments*, vol. 88, no. 8, p. 085110, 2017.

- [10] "Eit pioneer set." Swisstom AG, Switzerland, http://www.swisstom.com/wp-content/uploads/Swisstom\_brochure-PioneerSet\_GB\_1ST500-102\_Rev002\_web.pdf, Last Accessed: 10-1-2021.

- [11] A. Hedayatipour, S. Aslanzadeh, S. H. Hesari, M. A. Haque, and N. McFarlane, "A wearable cmos impedance to frequency sensing system for non-invasive impedance measurements," *IEEE Transactions* on Biomedical Circuits and Systems, vol. 14, no. 5, pp. 1108–1121, 2020.

- [12] L. Gerlach, G. Payá-Vayá, and H. Blume, "A survey on application specific processor architectures for digital hearing aids," *Journal of Signal Processing Systems*, pp. 1–16, 2021.

- [13] C. Kuhlmann, A. P. Khandhar, R. M. Ferguson, S. Kemp, T. Wawrzik, M. Schilling, K. M. Krishnan, and F. Ludwig, "Drive-field frequency dependent mpi performance of single-core magnetite nanoparticle tracers," *IEEE transactions on magnetics*, vol. 51, no. 2, pp. 1–4, 2015.

- [14] M. Zhang, A. Raghunathan, and N. K. Jha, "Trustworthiness of medical devices and body area networks," *Proceedings of the IEEE*, vol. 102, no. 8, pp. 1174–1188, 2014.

- [15] M. Zhang, A. Raghunathan, and J. K, "Towards trustworthy medical devices and body area networks," in *Proceedings of the 50th Annual Design Automation Conference*, 2013, pp. 1–6.

- [16] "Medical applications user guide." NXP Semiconductors, https://www. nxp.com/docs/en/user-guide/MDAPPUSGDRM118.pdf, Last Accessed: 10-1-2021.

- [17] L. Bu and M. G. Karpovsky, "A design of secure and reliablewireless transmission channel for implantable medical devices." in *ICISSP*, 2017, pp. 233–242.

- [18] L. Bu, M. G. Karpovsky, and M. A. Kinsy, "Bulwark: Securing implantable medical devices communication channels," *Computers & Security*, vol. 86, pp. 498–511, 2019.

- [19] C. Li, A. Raghunathan, and N. K. Jha, "Hijacking an insulin pump: Security attacks and defenses for a diabetes therapy system," in *IEEE 13th Int. Conf. on e-Health Networking, Applications and Services*, 2011, pp. 150–156.

- [20] D. Halperin, T. S. Heydt-Benjamin, B. Ransford, S. S. Clark, B. Defend, W. Morgan, K. Fu, T. Kohno, and W. H. Maisel, "Pacemakers and implantable cardiac defibrillators: Software radio attacks and zero-power defenses," in *IEEE Symp. on Security and Privacy (sp 2008)*. IEEE, 2008, pp. 129–142.

- [21] S. Gollakota, H. Hassanieh, B. Ransford, D. Katabi, and K. Fu, "They can hear your heartbeats: non-invasive security for implantable medical devices," in *Proc. of the ACM SIGCOMM 2011 Conf.*, 2011, pp. 2–13.

- [22] N. Ellouze, S. Rekhis, N. Boudriga, and M. Allouche, "Powerless security for cardiac implantable medical devices: Use of wireless identification and sensing platform," *J. of Netw. and Computer Appl.*, vol. 107, pp. 1–21, 2018.

- [23] G. Hunt, G. Letey, and E. Nightingale, "The seven properties of highly secure devices," tech. report MSR-TR-2017-16, 2017.

- [24] V. Vakhter, B. Soysal, P. Schaumont, and U. Guler, "Minimum on-the-node data security for the next-generation miniaturized wireless biomedical devices," in 2020 IEEE 63rd International Midwest Symposium on Circuits and Systems (MWSCAS). IEEE, 2020, pp. 1068–1071.

- [25] X. Hei, X. Du, J. Wu, and F. Hu, "Defending resource depletion attacks on implantable medical devices," in 2010 IEEE global telecommunications conference GLOBECOM 2010. IEEE, 2010, pp. 1–5.

- [26] M. Zhang, A. Raghunathan, and N. K. Jha, "Medmon: Securing medical devices through wireless monitoring and anomaly detection," *IEEE Transactions on Biomedical circuits and Systems*, vol. 7, no. 6, pp. 871–881, 2013.

- [27] D. Halperin, T. S. Heydt-Benjamin, K. Fu, T. Kohno, and W. H. Maisel, "Security and privacy for implantable medical devices," *IEEE Pervasive Computing*, vol. 7, no. 1, pp. 30–39, 2008.

- [28] S. Hosseini-Khayat, "A lightweight security protocol for ultra-low power asic implementation for wireless implantable medical devices," in 205th Int. Symp. on Medical Information and Communication Technology, 2011, pp. 6–9.

- [29] J. Fan, O. Reparaz, V. Rožić, and I. Verbauwhede, "Low-energy encryption for medical devices: Security adds an extra design dimension," in *Proceedings of the 50th Annual Design Automation Conference*, 2013, pp. 1–6.

- [30] M. M. Kermani, M. Zhang, A. Raghunathan, and N. K. Jha, "Emerging frontiers in embedded security," in 26th Int. Conf on VLSI design and 2013 12th Int. conf. on embedded systems. IEEE, 2013, pp. 203–208.

- [31] P. Kocher, J. Jaffe, and B. Jun, "Differential power analysis," in Annu. Int. cryptology Conf. Springer, 1999, pp. 388–397.

- [32] J.-F. Dhem, F. Koeune, P.-A. Leroux, P. Mestre, J.-J. Quisquater, and J.-L. Willems, "A practical implementation of the timing attack," in *Int. Conf. on Smart Card Research and Advanced Applications*. Springer, 1998, pp. 167–182.

- [33] M. M. Kermani, M. Zhang, A. Raghunathan, and N. K. Jha, "Emerging frontiers in embedded security," in 26th Int. Conf. on VLSI Design and 12th Int. Con. on Embedded Systems, 2013, pp. 203–208.

- [34] T. N. Theis and P. M. Solomon, "In quest of the "next switch": prospects for greatly reduced power dissipation in a successor to the silicon fieldeffect transistor," *Proceedings of the IEEE*, vol. 98, no. 12, pp. 2005– 2014, 2010.

- [35] T. N. Theis and H.-S. P. Wong, "The end of moore's law: A new beginning for information technology," *Computing in Science & Engineering*, vol. 19, no. 2, pp. 41–50, 2017.

- [36] Z. Kahleifeh and H. Thapliyal, "2-phase energy-efficient secure positive feedback adiabatic logic for cpa-resistant iot devices," in 2020 IEEE 6th World Forum on Internet of Things (WF-IoT), 2020, pp. 1–5.

- [37] A. Degada and H. Thapliyal, "2-spgal: 2-phase symmetric pass gate adiabatic logic for energy-efficient secure consumer iot," in 2021 IEEE International Conference on Consumer Electronics (ICCE), 2021, pp. 1–6

- [38] H. Li, Y. Zhang, and T. Yoshihara, "Clocked cmos adiabatic logic with low-power dissipation," in 2013 International SoC Design Conference (ISOCC). IEEE, 2013, pp. 064–067.

- [39] J. A. Ambrose, R. G. Ragel, and S. Parameswaran, "Rijid: random code injection to mask power analysis based side channel attacks," in *Proc.* of the 44th Annu. Design Automation Conf., 2007, pp. 489–492.

- [40] D. May, H. L. Muller, and N. P. Smart, "Non-deterministic processors," in *Australasian Conf. on Information Security and Privacy*. Springer, 2001, pp. 115–129.

- [41] D. May, H. Muller, and N. Smart, "Random register renaming to foil dpa," in *Int. Workshop on Cryptographic Hardware and Embedded Systems*. Springer, 2001, pp. 28–38.

- [42] K. Tiri, D. Hwang, A. Hodjat, B. Lai, S. Yang, P. Schaumont, and I. Verbauwhede, "A side-channel leakage free coprocessor ic in 0.18 μm cmos for embedded aes-based cryptographic and biometric processing," in *Proc. of the 42nd Annu. Design Automation conf.*, 2005, pp. 222–227.

- [43] A. Moradi and A. Poschmann, "Lightweight cryptography and dpa countermeasures: A survey," in *Int. Conf. on Financial Cryptography* and *Data Security*. Springer, 2010, pp. 68–79.

- [44] S. D. Kumar, H. Thapliyal, A. Mohammad, and K. S. Perumalla, "Design exploration of a symmetric pass gate adiabatic logic for energy-efficient and secure hardware," *Integr. the VLSI J.*, vol. 58, pp. 369–377, 2017.

- [45] W. C. Athas, L. J. Svensson, J. G. Koller, N. Tzartzanis, and E. Y.-C. Chou, "Low-power digital systems based on adiabatic-switching principles," *IEEE Trans. Very Large Scale Integr. (VLSI) Syst*, vol. 2, no. 4, pp. 398–407, 1994.

- [46] M. Avital, H. Dagan, I. Levi, O. Keren, and A. Fish, "Dpa-secured quasi-adiabatic logic (sqal) for low-power passive rfid tags employing s-boxes," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 62, no. 1, pp. 149–156, 2014.

- [47] H. S. Raghav, V. A. Bartlett, and I. Kale, "Investigating the effectiveness of without charge-sharing quasi-adiabatic logic for energy efficient and secure cryptographic implementations," *Microelectronics J.*, vol. 76, pp. 8–21, 2018.

- [48] H. S. Raghav and I. Kale, "A balanced power analysis attack resilient adiabatic logic using single charge sharing transistor," *Integr. the VLSI J.*, vol. 69, pp. 147–160, 2019.

- [49] C. Monteiro, Y. Takahashi, and T. Sekine, "Robust secure charge-sharing symmetric adiabatic logic against side-channel attacks," in 36th IEEE Int. Conf. on Telecommunications and Signal Processing (TSP), 2013, pp. 732–736.

- [50] B. Fadaeinia and A. Moradi, "3-phase adiabatic logic and its sound sca evaluation," *IEEE Trans. on Emerging Topics in Computing*, 2020.

- [51] H. Mahmoodi-Meimand and A. Afzali-Kusha, "Efficient power clock generation for adiabatic logic," in *The 2001 IEEE Int. Symp. on Circuits* and Systems (ISCAS) (Cat. No. 01CH37196), vol. 4, 2001, pp. 642–645.

- [52] Y. Takahashi, T. Sekine, and M. Yokoyama, "Two-phase clocked cmos adiabatic logic," Far East J. Electronics and Communications, vol. 3, no. 1, pp. 17–34, 2009.

- [53] A. Bogdanov, L. R. Knudsen, G. Leander, C. Paar, A. Poschmann, M. J. Robshaw, Y. Seurin, and C. Vikkelsoe, "Present: An ultralightweight block cipher," in *Int. Workshop on cryptographic hardware* and embedded systems. Springer, 2007, pp. 450–466.

- [54] M. J. Dworkin, Sp 800-38A. Recommendation for Block Cipher Modes of Operation: Methods and Techniques. National Institute of Standards & Technology, 2001, [Online: accessed 05-May-2021].

- [55] Y. Zhang, "Research on low power technology by ac power supply circuits," Ph.D. dissertation, Waseda University, Tokyo, Japan, 2012.

- [56] J. Wu, Y. Shi, and M. Choi, "Measurement and evaluation of power analysis attacks on asynchronous s-box," *IEEE Trans. Instrum. Meas.*, vol. 61, no. 10, pp. 2765–2775, 2012.

- [57] S. Roy, G. Jana, and M. Chanda, "Analysis of sub-threshold adiabatic logic model using junctionless mosfet for low power application," *Silicon*, pp. 1–9, 2021.

- [58] J.-S. Liu, M. B. Clavel, and M. K. Hudait, "Tbal: Tunnel fet-based adiabatic logic for energy-efficient, ultra-low voltage iot applications," *IEEE Journal of the Electron Devices Society*, vol. 7, pp. 210–218, 2019.

- [59] C. Rolfes, A. Poschmann, G. Leander, and C. Paar, "Ultra-lightweight implementations for smart devices–security for 1000 gate equivalents," in *International Conference on Smart Card Research and Advanced Applications*. Springer, 2008, pp. 89–103.

- [60] Y. Ye and K. Roy, "Qserl: Quasi-static energy recovery logic," *IEEE Journal of Solid-State Circuits*, vol. 36, no. 2, pp. 239–248, 2001.

Amit Degada is currently a Ph.D candidate in the Department of Electrical and Computer Engineering, University of Kentucky, Lexington, KY, USA. He has completed his Masters of Technology from Sardar Vallabhbhai National Institute of Technology (NIT) Surat, India. His research interest is on the development of hardware assisted cybersecurity primitives for consumer IoT applications.

Himanshu Thapliyal (SM'16) is currently an Associate Professor with the Department of Electrical Engineering and Computer Science, University of Tennessee, Knoxville, Tennessee, USA. He received a PhD degree in Computer Science and Engineering from the University of South Florida, Tampa, in 2011 where he received the 'Distinguished Graduate Achievement Award'. From 2012-14, he worked as a designer of processor test solutions at Qualcomm, where he received the Qualcomm QualStar Award for contributions to memory built-in self-test. He

joined as an Assistant Professor at the University of Kentucky, Lexington in 2014 where he got promoted to Associate Professor in 2020. He is the recipient of the NSF CAREER award, and IEEE-CS TCVLSI Mid-Career Research Achievement Award. He received the Provost's Wethington Award for contributions to the University of Kentucky Research Program. He has authored over 150 publications that have resulted in over 4700 citations with hindex=40 (Google Scholar). He has been ranked in the top 50 among scientists throughout the world in the field of Computer Hardware & Architecture for the calendar years 2019 and 2020. He has received Best Paper awards at the 2021 IEEE International Conference on Consumer Electronics, 2020 IEEE World Forum on Internet of Things (WF-IoT), 2017 Cyber and Information Security Research Conference (CISR), and 2012 IEEE Computer Society Annual Symposium on VLSI (ISVLSI). He is the steering committee vicechair of the IEEE Symposium on Smart Electronic Systems. He served as the General Chair of the 2020 IEEE Symposium on Smart Electronic Systems. He has served as the Program Chair of the 2020 IEEE International Conference on Consumer Electronics, 2019 IEEE Computer Society Annual Symposium on VLSI, and 2018 IEEE Symposium on Smart Electronic Systems. He is serving as the Section Editor of the Springer Nature Computer Science and is leading two sections: (i) Quantum Computing and Emerging Technologies, and (ii) Emerging Trends in Sensors, IoT and Smart Systems. He is also serving as the Senior Associate Editor of the IEEE Consumer Electronics Magazine, Associate Editor of the IEEE Internet of Things Journal, and the editorial board member of the Microelectronics Journal. His research interests hardware security of IoT and vehicles, quantum computing, and smart healthcare solutions for older adults and Alzheimer's Disease and Related Dementias (ADRD).