# Sub-3 V, MHz-Class Electrolyte-Gated Transistors and Inverters

Fazel Zare Bidoky and C. Daniel Frisbie\*

Cite This: <https://doi.org/10.1021/acsami.2c01585>

Read Online

ACCESS |

Metrics & More

Article Recommendations

Supporting Information

**ABSTRACT:** Electrolyte-gated transistors (EGTs) have emerging applications in physiological recording, neuromorphic computing, sensing, and flexible printed electronics. A challenge for these devices is their slow switching speed, which has several causes. Here, we report the fabrication and characterization of n-type ZnO-based EGTs with signal propagation delays as short as 70 ns. Propagation delays are assessed in dynamically operating inverters and five-stage ring oscillators as a function of channel dimensions and supply voltages up to 3 V. Substantial decreases in switching time are realized by minimizing parasitic resistances and capacitances that are associated with the electrolyte in these devices. Stable switching at 1–10 MHz is achieved in individual inverter stages with 10–40  $\mu$ m channel lengths, and analysis suggests that further improvements are possible.

**KEYWORDS:** electrolyte-gated transistors, ion gel, ZnO, propagation delay, switching frequency

## INTRODUCTION

The use of polarized electrolytes to modulate or “gate” the conductance of a semiconducting channel is an old idea that has its origins in the development of the first solid-state transistors at Bell Labs in the 1940s.<sup>1</sup> There are now many examples of semiconductor devices that can generally be called electrolyte-gated transistors (EGTs),<sup>2,3</sup> though they go by different names. Over the last 70 years, EGTs have had several rebirths associated with the development of new EGT applications, or new materials that enhance performance, or discovery of new transport phenomena within EGTs. The ion-sensitive field-effect transistor (ISFET) developed in the 1970s is an early example of an EGT,<sup>4,5</sup> where ion adsorption on gate oxides of Si FETs is exploited to make high sensitivity ion sensors. Microelectrochemical transistors, extensively developed by Wrighton and co-workers in the 1980s,<sup>6,7</sup> were another important milestone. These devices employ gate potentials to modulate the conductivity of conducting polymers in direct contact with electrolytes. Currently, EGTs are again enjoying a resurgence of interest associated with their applications in physiological recording,<sup>8–10</sup> neuromorphic computing,<sup>11–16</sup> and biosensing,<sup>17–22</sup> as well as in fundamental physics,<sup>23–26</sup> where the high charge densities achieved in electrolyte-gated semiconductors are leading to exciting discoveries.

A principal problem with EGTs for many applications is that their switching speed is limited.<sup>2</sup> This is easily understandable because the mechanisms of electrolyte gating rely on ion fluxes to form electrical double layers at the gate–electrolyte and semiconductor–electrolyte interfaces or—in the electrochem-

ical mode—to penetrate into the semiconductor. Ion mobilities are orders of magnitude smaller than electron or hole mobilities in semiconductors, which means the ionic resistance of the intervening electrolyte between the gate electrode and the semiconductor channel is relatively large. This ionic resistance can be viewed as a parasitic resistance  $R_p$  in series with the gate, and it is dependent on intrinsic electrolyte conductivity, electrolyte thickness, and cross-sectional area.<sup>27–29</sup> As we demonstrate below, for an EGT-based circuit, it can unfortunately be the case that the limiting ON-state resistance  $R_{\text{total}}^{\text{ON}}$  controlling signal propagation delay is not determined by the semiconductor channel resistance  $R_{\text{channel}}^{\text{ON}}$  or the source–drain contact resistance  $R_{\text{contact}}^{\text{ON}}$  but rather is dominated by  $R_p$  due to slow ion motion in the electrolyte (i.e.,  $R_{\text{total}}^{\text{ON}} = R_{\text{channel}}^{\text{ON}} + R_{\text{contact}}^{\text{ON}} + R_p$ , where  $R_p$  dominates).<sup>30–32</sup> We, and others, have measured ionic conductivity for gel electrolyte films based on ionic liquids and polymers and found it to be as large as 4 mS/cm depending on the precise gel composition.<sup>33–35</sup> Thus, for typical EGTs with channel areas of  $\sim$ 1000  $\mu\text{m}^2$ , and gel film thicknesses of  $\sim$ 1  $\mu\text{m}$ ,  $R_p$  is on the order of 1 k $\Omega$ , which is a large value. Less resistive, ultrathin gate–electrolyte films are a clear goal for EGTs.<sup>36</sup> Khodagholy and co-workers<sup>8</sup> have

Received: January 25, 2022

Accepted: April 19, 2022

recently minimized electrolyte polarization times by mixing gel electrolytes with a semiconducting polymer to make a composite mixed ionic and electronic channel material. In their EGTs, single current step rise and fall times of  $1\ \mu\text{s}$  were achieved, which they argued were due to short migration path lengths for ions between electronically conducting polymer domains and internal, phase-separated ion reservoirs. However,  $R_p$  was not reported in that work and continuous MHz-level switching was not demonstrated.

Another challenge for EGT switching speed is parasitic capacitance,  $C_p$ .<sup>30–32</sup> Parasitic capacitance arises from contact between the electrolyte and the source and drain electrodes of the transistor. Specifically, the double-layer polarization of the source–electrolyte and drain–electrolyte interfaces must change when the gate voltage switches. Thus, the double-layer capacitances of these interfaces lumped together constitute  $C_p$ , which is in parallel with the electrolyte–channel capacitance,  $C_{\text{channel}}$ . The presence of parasitic capacitance increases the total ON-state capacitive load  $C_{\text{total}}^{\text{ON}}$  that the gate must switch, i.e.,  $C_{\text{total}}^{\text{ON}} = C_{\text{channel}}^{\text{ON}} + C_p$ . This, in turn, increases the EGT signal propagation delay  $\tau$  in a circuit. If one takes the common approximation that  $\tau \approx R_{\text{total}}^{\text{ON}} C_{\text{total}}^{\text{ON}}$  (reasonable for inverters described below), then it becomes clear that for optimized operation (smallest  $\tau$ ) not only must  $R_p$  be minimized so that  $R_p \ll (R_{\text{channel}}^{\text{ON}} + R_{\text{contact}})$  but  $C_p \ll C_{\text{channel}}^{\text{ON}}$ .

The role of parasitic capacitance is well recognized in thin-film transistor (TFT) technology, where it is also a problem.<sup>37</sup>  $C_p$  is minimized in conventional TFTs by reducing the projected areal overlap between the gate and the source and drain electrodes. For EGTs, the parasitic penalty on  $\tau$  is exacerbated by the enormous specific capacitance associated with metal–electrolyte interfaces, of order  $10\ \mu\text{F}/\text{cm}^2$ , which means that essentially any source–electrolyte or drain–electrolyte contact results in relatively large  $C_p$ .

In this work, we apply these ideas to fabricate fast EGTs and EGT circuits, and we establish that MHz-class devices can be realized with switching delays below 100 ns for the fastest devices. In our view, there are clear reasons why EGTs will not rival the speed of Si MOSFETs<sup>2</sup> (though perhaps not everyone agrees),<sup>38</sup> but for envisioned applications of EGTs, gigahertz speeds do not appear necessary. As EGTs are being developed as physiological recording amplifiers,<sup>9,10</sup> and integrated into circuits<sup>36,39–41</sup> and neural nets,<sup>4,11,13,14,16</sup> it is nevertheless important to establish the limits of performance that can be obtained by rational design. We note that there are other limitations to EGT performance like high dielectric loss tangents and quasistatic leak currents associated with electrolytes that are important for power consumption,<sup>2</sup> but these are not our focus here.

## RESULTS AND DISCUSSION

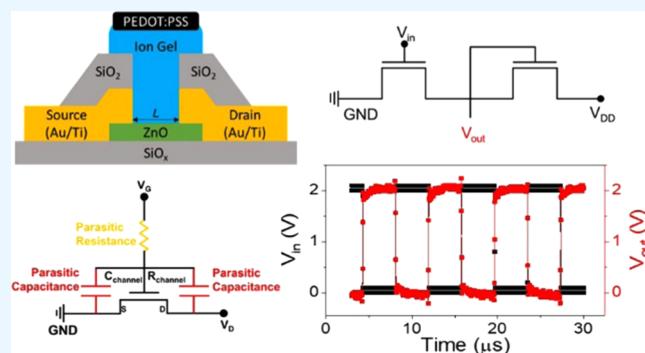

Our EGT device design is shown in Figure 1a. We employ a thin film of ZnO as the semiconductor channel because of its high electron mobility ( $\sim 5\ \text{cm}^2/\text{V s}$ ), its stability in contact with electrolytes, and its ease of growth and patterning by atomic layer deposition (ALD) and photolithography.<sup>32,42</sup> The source and drain electrodes are Au/Ti and channel lengths  $L$  are systematically varied from 10 to  $40\ \mu\text{m}$ , scaling the channel width  $W$  such that the aspect ratio is fixed at  $W/L = 20$ , unless otherwise noted. The electrolyte is a soft solid called an ion gel that we and others have developed previously for EGTs.<sup>43–45</sup> Its attributes are high ionic conductivity ( $\sim 4\ \text{mS}/\text{cm}$ ), a wide electrochemical stability window, chemical inertness, hydro-

**Figure 1.** (a) Scheme of an n-channel ZnO EGT. The  $\text{SiO}_2$  insulating overlayers on top of the source and drain electrodes reduce parasitic capacitance  $C_p$  by minimizing electrolyte–metal contact. Channel length  $L$  is indicated. (b) Plan view photograph of a completed EGT. Channel width  $W = 400\ \mu\text{m}$  as shown. (c) Quasistatic  $I_{\text{D}}-V_{\text{G}}$  (transfer) characteristic on log and linear scales for an n-channel ZnO EGT with  $W/L = 400/20\ \mu\text{m}$ .  $V_{\text{D}} = 0.1\ \text{V}$  and  $V_{\text{G}}$  sweep rate is 3 V/s. (d) Corresponding quasistatic  $I_{\text{D}}-V_{\text{D}}$  (output) characteristics as a function of  $V_{\text{G}}$ .  $V_{\text{D}}$  sweep rate is 3 V/s.

phobicity, which allows it to serve as a kind of channel encapsulation, and its facile patterning by aerosol jetting. The gate electrode is also aerosol jet printed and is made of the conducting polymer PEDOT:PSS, which has a large volumetric capacitance ( $\sim 1\ \text{F}/\text{cm}^3$ ) by virtue of its permeability to ions. The large volumetric capacitance reduces the impedance of the PEDOT–ion gel interface and ensures that when a gate voltage  $V_{\text{G}}$  is applied, the majority of the voltage drops at the electrical double layer formed at the smaller, impermeable ion gel–ZnO interface. Importantly, the broad top surfaces of the Au source and drain electrodes are insulated from the ion gel by patterned  $\text{SiO}_x$  overlayers to reduce the parasitic capacitance. We have shown previously that unencapsulated source and drain electrodes can dominate total capacitance in EGTs.<sup>30</sup> Figure 1b shows an optical micrograph of a completed ZnO EGT; images of the devices at various stages of completion are shown in the Supporting Information (see Figure S1). We note that this device design is similar to a design we reported earlier,<sup>32</sup> with the crucial difference that we have employed a much more conductive ion gel, as discussed later.

Typical quasistatic drain current ( $I_{\text{D}}$ )–gate voltage ( $V_{\text{G}}$ ) curves are displayed in Figure 1c for an EGT with  $W/L = 400/20\ \mu\text{m}$ . One sees minor hysteresis in the forward and reverse sweeps at a gate voltage sweep rate of 3 V/s. The current onset occurs near  $V_{\text{G}} = 0\ \text{V}$  and the ON/OFF ratio is  $10^5$ . The relatively large OFF current of 10 nA (see Figure S2) can be attributed to the large size of the device and the inherent leakage through electrolytes, which is often due to impurities such as  $\text{H}_2\text{O}$  (the PEDOT gate is printed from an aqueous ink). The corresponding output curves ( $I_{\text{D}}$  vs drain voltage  $V_{\text{D}}$ ) are shown in Figure 1d. The device exhibits reasonable current saturation and square law saturation current scaling up to  $V_{\text{G}} = +0.8\ \text{V}$ . Beyond  $V_{\text{G}} = +0.8\ \text{V}$ , true saturation is hard to obtain

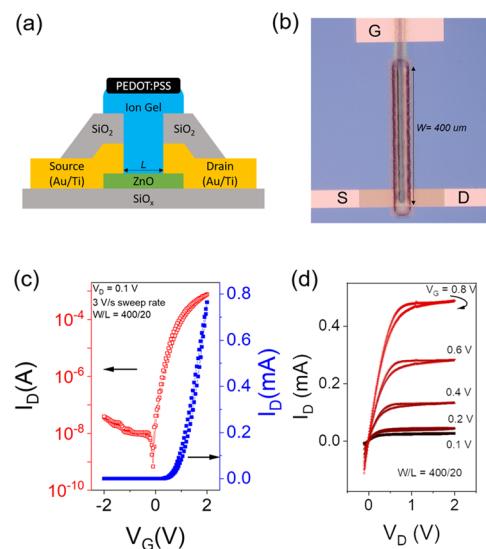

**Figure 2.** (a) EGT equivalent circuit highlighting parasitic resistance  $R_p$  and parasitic capacitance  $C_p$ . (b) Two-terminal  $R$ – $V_G$  and  $C$ – $V_G$  behavior determined by impedance analysis of an EGT at 100 kHz and AC amplitude  $V_{AC} = 50$  mV.  $V_G$  sweep rate = 100 mV/s. The inset shows the measurement configuration with  $V_G + V_{AC}$  applied to the gate with source and drain grounded. Total two-terminal resistance  $R_{total}$  and  $C_{total}$  in the fully ON and OFF states are indicated.  $W/L = 200/10 \mu\text{m}$ .

because of the practical limits set on  $V_D$  by electrolyte breakdown ( $V_D$  must be  $\leq 2$  V, see also the Supporting Information, Figure S3). Additional quasistatic transfer and output behaviors are shown for EGTs with  $W/L = 200/10$  and  $400/20 \mu\text{m}$  in the Supporting Information, Figures S4 and S5, and statistics for key figures of merit (threshold voltage  $V_T$ , transconductance  $g_m$ , and ON/OFF current ratio) for nine  $W/L = 200/10 \mu\text{m}$  devices are displayed in Table S1.

To characterize parasitic resistances and capacitances that affect dynamic performance, we have undertaken impedance analysis of ZnO EGTs as a function of voltage and frequency. Figure 2a shows an equivalent circuit for an EGT in which gate-source and gate-drain parasitic capacitances  $C_p$  are identified, as well as the parasitic resistance  $R_p$ , due to a combination of the ionic resistance of the electrolyte between the gate and the channel, discussed above, and the resistance of the PEDOT gate. In the two-terminal impedance measurement, the source and drain are grounded and a small AC bias (50 mV amplitude) with a DC offset is applied to the PEDOT gate (see inset in panel (b)). Figure 2b displays the  $R$ – $V_G$  and  $C$ – $V_G$  results at 100 kHz for a device with  $W/L = 200/10 \mu\text{m}$ . As  $V_G$  increases, two-terminal resistance drops (black curve) and capacitance increases (red curve) as the channel opens and floods with electrons. The channel is fully conducting at voltages  $>+1$  V, and the resistance plateaus at  $R_{total}^{ON} = 800 \Omega$ , whereas capacitance plateaus at  $C_{total}^{ON} = 630 \text{ pF}$ . For these two-terminal measurements, we take  $R_{total}^{ON} \sim (R_{channel}^{ON} + R_{contact})/2 + R_p$ . From  $I_D$ – $V_G$  measurements, we estimate  $R_{channel}^{ON} + R_{contact} = 100 \Omega$  (at  $V_D = 0.1$  V and  $V_G = +2$  V) and therefore the entire ON-state resistance  $R_{total}^{ON}$  is effectively  $R_p$ , that is  $R_p \sim 750 \Omega$ . Clearly,  $R_p$  dominates the ON-state resistance in our devices ( $R_p \gg R_{channel}^{ON} + R_{contact}$ ). On the other hand, in the case of capacitance, we take  $C_{channel}^{ON} = C_{total}^{ON} - C_{total}^{OFF} = 630 \text{ pF}$  and  $C_p = C_{total}^{OFF} \sim 0 \text{ pF}$ , i.e.,  $C_p$  is below our detection limit. We thus conclude that  $C_p \ll C_{channel}^{ON}$  and that  $C_p$  does not dominate the transistor response because of our efforts to minimize the electrode–electrolyte contact by insulating the source and drain electrodes.  $R_p$ , on the other hand, remains a limiting factor.

Importantly, from the values of  $R_{total}^{ON} = R_p$  and  $C_{total}^{ON} = C_{channel}^{ON}$ , we can make an estimate of the expected switching time of our EGTs with  $L = 10 \mu\text{m}$ , i.e.,  $R_{total}^{ON} C_{total}^{ON} = 800 \Omega \times 630 \times 10^{-12} \text{ F} \sim 500 \text{ ns}$ . We thus expect that these devices, even with the  $R_p$  limitation, should be capable of MHz switching, which has not been reported previously.

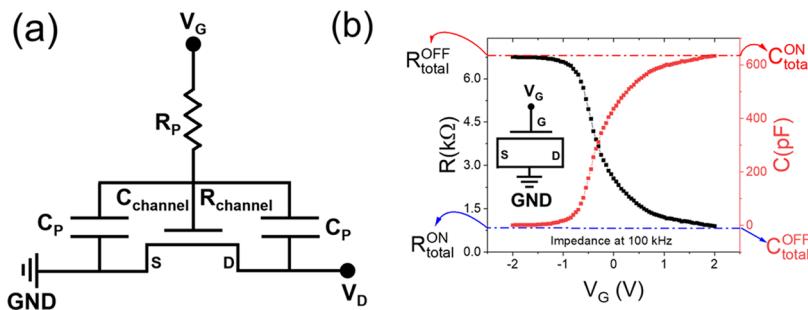

To assess the dynamic response, we have fabricated EGT-based inverters in the internal feedback configuration in which

the gate of the load EGT is connected to  $V_{out}$ , Figure 3a. A typical quasistatic inverter transfer characteristic is shown in

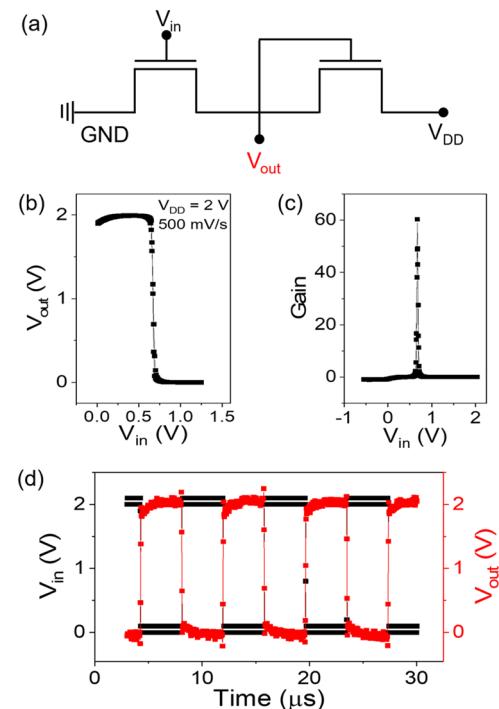

**Figure 3.** (a) Scheme of an inverter based on two n-channel ZnO EGTs ( $W/L = 800/40 \mu\text{m}$ ) in the feedback configuration in which  $V_{out}$  is connected to the gate of the load transistor. (b) Quasistatic inverter transfer characteristic with  $V_{DD} = +2$  V and (c) the corresponding inverter gain. (d) Dynamic inverter operation at 130 kHz. The input signal is the black square wave and the output is shown in red. For this inverter,  $W/L = 600/30 \mu\text{m}$  for the pair of EGTs.  $V_{DD} = +2$  V.

Figure 3b, and the corresponding gain ( $V_{out}/V_{in}$ ) for  $V_{DD} = +2$  V is displayed in Figure 3c. One can see in Figure 3b that a rail-to-rail voltage swing is achieved over a very small voltage interval  $\Delta V_{in} = 50$  mV. The gain is consequently 60 at  $V_{DD} = +2$  V, a high gain for an EGT inverter, and the gain increases with increasing  $V_{DD}$  from +0.5 to +2 V as expected, Figure S6. Figure S7 demonstrates that the inverter noise margins are 0.6 V and  $\sim 80\%$  of the theoretical maximum. Further, dynamic inverter performance at 130 kHz drive frequency is displayed in Figure 3d, where it is evident that  $V_{out}$  follows  $V_{in}$  nicely with a full rail-to-rail voltage swing. For this device,  $W/L = 600/30 \mu\text{m}$

μm for the EGTs. Figure S4j shows comparable quasistatic and dynamic performance for an inverter with  $W/L = 200/10$  μm.

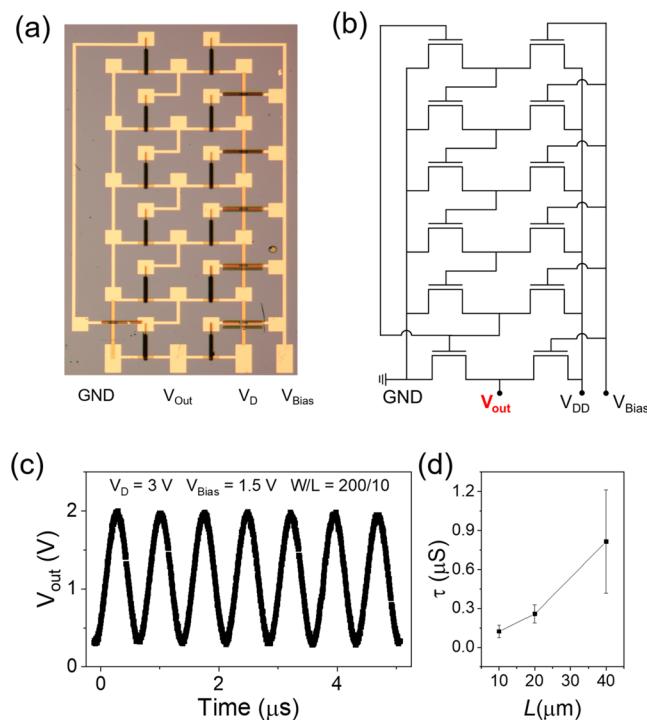

To further quantify dynamic performance, we have fabricated five-stage ring oscillators based on six EGT inverters in which the static load transistor is tuned with a separate supply voltage  $V_{\text{Bias}}$ , Figure 4a,b. Figure 4c shows the dynamic

**Figure 4.** (a) Optical image of a five-stage ring oscillator based on EGT inverters in the static load configuration. Resistance of the load transistor is set by  $V_{\text{Bias}}$ . (b) Corresponding circuit diagram. (c) 1.4 MHz dynamic output for a five-stage oscillator at  $V_{\text{DD}} = +3$  V and  $V_{\text{Bias}} = +1.5$  V. EGTs have dimensions  $W/L = 200/10$  μm. (d) Propagation delay  $\tau$  vs channel length  $L$  extracted from a series of ring oscillators. Channel aspect ratios  $W/L = 20$  for each data point. Ring oscillators with  $L = 10$  μm yielded an average  $\tau = 120$  ns. Error bars represent one standard deviation.

output at  $V_{\text{DD}} = +3$  V for a ring oscillator with 12 EGTs having channel dimensions  $W/L = 200/10$  μm. The oscillation frequency  $f = 1.4$  MHz. This corresponds to an average stage delay  $\tau = 1/(2Nf) = 0.1/f = 70$  ns, where  $N = 5$  is the number of stages. To our knowledge, this is the shortest propagation delay reported to date for EGT devices. Note that in comparison to our previous work,<sup>32</sup> we have obtained a nearly 1000-fold decrease in propagation delay. This improvement is essentially entirely due to the huge difference in ionic conductivity of the ion gels used in this study vs our previous work. In our prior study, we employed a heavily chemically cross-linked ion gel to facilitate vapor deposition of a gold gate electrode, but cross-linking decreased ionic conductivity to  $10^{-6}$ – $10^{-5}$  S/cm vs the  $10^{-3}$ – $10^{-2}$  S/cm conductivity of the un-cross-linked gel employed here.

To assess the impact of device scaling, we have fabricated a series of ring oscillators with systematically varying EGT channel lengths  $L$  from 10 to 40 μm and have measured dynamic performance and the corresponding propagation delays. It is evident in Figure 4d that the average delay time  $\tau$  is ~120 ns for the oscillators with the smallest ( $L = 10$  μm)

channel lengths. Furthermore,  $\tau$  increases with increasing  $L$ , and for the largest devices with  $L = 40$  μm, the average  $\tau$  is still less than 1 μs. There is considerably more circuit-to-circuit variability in the  $L = 40$  μm oscillators, likely due to details associated with the fabrication process. Nevertheless, the central conclusion of Figure 4d is clear, namely, that propagation delays for EGT inverters can be in the regime of 100 ns.

An increase in propagation delay  $\tau$  with  $L$  is generally anticipated by analogy to conventional TFTs. Because  $W/L = 20$ , the EGT channel area  $WL = 20L^2$ .  $C_{\text{channel}}^{\text{ON}}$  and therefore  $C_{\text{total}}^{\text{ON}}$  are proportional to channel area and thus will increase as  $L^2$ . For conventional TFTs,  $R_{\text{total}}^{\text{ON}}$  does not vary with  $L$  when  $W/L$  is fixed, so the prediction would be that  $\tau = R_{\text{total}}^{\text{ON}} C_{\text{total}}^{\text{ON}} \propto L^2$ . However, for our EGTs, the dominant role of  $R_p$  potentially introduces a different  $L$ -dependence. Considering first the ionic resistance between the gate and channel, one expects  $R_p$  to scale *inversely* with device area, i.e., the larger the device footprint, the larger the cross-sectional area for ion conduction normal to the channel, and the smaller the ionic resistance. With this line of thought, one predicts  $R_p \propto L^{-2}$  and thus the product  $R_{\text{total}}^{\text{ON}} C_{\text{total}}^{\text{ON}} \propto L^{-2} \cdot L^2$  would be independent of  $L$ . That is, scaling up the device area increases  $C_{\text{total}}^{\text{ON}}$  but decreases  $R_{\text{total}}^{\text{ON}}$  commensurately. The data in Figure 4d are clearly at odds with this simple prediction.

Here, we must consider that  $R_p$  actually has two components, the ionic resistance of the gate electrolyte mentioned earlier,  $R_{\text{ion}}$ , and the resistance of the PEDOT:PSS gate electrode itself,  $R_{\text{gate}}$ , i.e.,  $R_p = R_{\text{ion}} + R_{\text{gate}}$ . PEDOT:PSS has a far lower conductivity than typical metals (500 S/cm vs  $10^5$  S/cm for good metals) and thus  $R_{\text{gate}}$  can be significant. Using  $R_{\text{gate}} = \rho_{\text{PEDOT}} W/(L \cdot h) = \rho_{\text{PEDOT}} \cdot 20L/(L \cdot h) = \rho_{\text{PEDOT}} \cdot 20/h$ , where  $\rho_{\text{PEDOT}}$  is the PEDOT:PSS resistivity and  $h = 1$  μm is the approximate thickness of the ion gel, we estimate that  $R_{\text{gate}} = 500$ – $1000$  Ω for all devices. This is comparable to the resistance of the electrolyte,  $R_{\text{ion}}$ , and for the larger devices it may be the case that  $R_{\text{gate}}$  is greater than  $R_{\text{ion}}$ . That is, because  $R_{\text{gate}}$  is relatively large and approximately independent of channel dimensions for our fixed  $W/L$  devices, its contribution to  $R_p$  can dominate  $R_{\text{ion}}$  at large  $L$  and the scaling of  $R_{\text{total}}^{\text{ON}} = R_p = R_{\text{ion}} + R_{\text{gate}}$  for our devices may not be simple. Our empirical finding is that  $\tau$  increases with  $L$ , broadly consistent with expectations based on  $C_{\text{total}}^{\text{ON}}$  which dictates that larger devices should be slower. Further work is necessary to develop a quantitative model of the overall dependence of  $\tau$  on device dimensions. Still, the  $L$ -dependence in Figure 4d suggests that there is still room to shorten EGT signal propagation delays if  $L$  is decreased below 10 μm, and strategies are found to further diminish  $R_p$  (and contact resistance).

## CONCLUSIONS

In summary, we have demonstrated here that by minimizing parasitic resistance and capacitance and by selecting a high-mobility thin-film semiconductor—in this case ZnO—propagation delays for EGT inverters can be decreased into the 100 ns regime for applied biases less than 3 V. For our devices, parasitic resistance remains a significant factor and further decreases in switching time will require decreases in the electrolyte, gate electrode, and source–drain contact resistances. Standardization of EGT fabrication procedures will also enhance our ability to develop quantitative models for how the EGT static  $I$ – $V$  characteristics and dynamic performance scale

with device dimensions. Overall, continuous improvements in EGT performance should boost ongoing efforts to employ these devices in sensors, amplifiers, neural networks, and various types of flexible, wearable devices.

## ■ EXPERIMENTAL SECTION

**Materials.** Ion gels were made from the ionic liquid 1-ethyl-3-methylimidazolium bis(trifluoro-methylsulfonyl)imide ([EMI]-[TFSI]) and the triblock copolymer poly(styrene-*b*-ethyl acrylate-*b*-styrene) (SEAS). The SEAS polymer was synthesized in-house using previously reported procedures.<sup>43</sup> [EMI][TFSI] ionic liquid was purchased from EMD Chemicals (Gibbstown, NJ) and stored in an inert atmosphere. Aerosol jettable ion gel inks were made by preparing a solution with a mass ratio of 1:9:90 SEAS polymer: [EMI][TFSI] ionic liquid:ethyl acetate solvent. The aqueous PEDOT:PSS ink, PH1000, was purchased from Heraeus (Germany), and 6 vol % ethylene glycol was added to the ink to enhance the PEDOT conductivity on drying.

**Device Fabrication.** A similar fabrication process is described in prior work.<sup>30,32</sup> Briefly, a 50 nm thick ZnO film was deposited using atomic layer deposition (ALD) (Savannah Series, Cambridge NanoTech) with diethylzinc and water vapor as precursors. The ZnO film was annealed in a rapid thermal annealer (RTP-600S, Modular Process Technology). The first anneal at 300 °C in N<sub>2</sub> lasted 15 min. The second anneal followed at 400 °C in O<sub>2</sub> for another 15 min. The ZnO was then patterned with standard photolithographic procedures with aqueous HCl used as an etchant.

Standard lithography processes using Shipley S1813 resist were used to make the contact pads, interconnects, and source and drain electrodes. Interconnects and contact pads were deposited in an electron beam evaporator (Temescal) with 5 nm Cr as an adhesion layer followed by 25 nm thick Au. The source and drain electrodes, which were insulated with SiO<sub>x</sub>, were made in a separate series of lithographic steps. The metal layers (60 nm Au on 10 nm Ti) were deposited via e-beam evaporation (Varian 3118). Then, another photolithography process was used to deposit 10 nm Ti on top of the Au, followed by 200 nm SiO<sub>x</sub> again by e-beam evaporation. The gate dielectric (ion gel) and gate contact (PEDOT:PSS) were sequentially printed with an aerosol jet printer (AJ 100, Optomec) (see Figure S1). A 150 μm diameter nozzle was used to print the ion gel layers, and a 100 μm nozzle was used for PEDOT:PSS. The sheath/feed gas flow rates (in standard cm<sup>3</sup>/min) for ion gel and PEDOT:PSS depositions were 28/8 and 17/12, respectively.

## ■ ASSOCIATED CONTENT

### SI Supporting Information

The Supporting Information is available free of charge at <https://pubs.acs.org/doi/10.1021/acsami.2c01585>.

Device fabrication procedure and additional device measurements ([PDF](#))

## ■ AUTHOR INFORMATION

### Corresponding Author

C. Daniel Frisbie – Department of Chemical Engineering and Materials Science, University of Minnesota, Minneapolis, Minnesota 55455, United States;  [orcid.org/0000-0002-4735-2228](https://orcid.org/0000-0002-4735-2228); Email: [frisbie@umn.edu](mailto:frisbie@umn.edu)

### Author

Fazel Zare Bidoky – Department of Chemical Engineering and Materials Science, University of Minnesota, Minneapolis, Minnesota 55455, United States; DuPont Electronics and Industrial, Emerging Technologies, Experimental Station, Wilmington, Delaware 19803, United States;  [orcid.org/0000-0003-0739-5992](https://orcid.org/0000-0003-0739-5992)

Complete contact information is available at:

<https://pubs.acs.org/10.1021/acsami.2c01585>

## Notes

The authors declare no competing financial interest.

## ■ ACKNOWLEDGMENTS

This work was primarily supported by the MRSEC program of the National Science Foundation under Grant Number DMR-2011401. Parts of this work were carried out in the Characterization Facility, University of Minnesota, which receives partial support from the NSF through the MRSEC program. Other portions of this work were conducted in the Minnesota Nano Center, which is supported by the National Science Foundation through the National Nano Coordinated Infrastructure Network (NNCI) under Award Number ECCS-2025124.

## ■ REFERENCES

- (1) John Bardeen – Nobel Lecture. Nobel Prize Outreach AB 2022, 2022. <https://www.nobelprize.org/prizes/physics/1956/bardeen/lecture>.

- (2) Kim, S. H.; Hong, K.; Xie, W.; Lee, K. H.; Zhang, S.; Lodge, T. P.; Frisbie, C. D. Electrolyte-Gated Transistors for Organic and Printed Electronics. *Adv. Mater.* **2013**, *25*, 1822–1846.

- (3) Rivnay, J.; Inal, S.; Salleo, A.; Owens, R. M.; Berggren, M.; Malliaras, G. G. Organic Electrochemical Transistors. *Nat. Rev. Mater.* **2018**, *3*, No. 17086.

- (4) Bergveld, P. Development of an Ion-Sensitive Solid-State Device for Neurophysiological Measurements. *IEEE Trans. Biomed. Eng.* **1970**, *BME-17*, 70–71.

- (5) Bergveld, P. Development, Operation, and Application of the Ion-Sensitive Field-Effect Transistor as a Tool for Electrophysiology. *IEEE Trans. Biomed. Eng.* **1972**, *BME-19*, 342–351.

- (6) White, H. S.; Kittlesen, G. P.; Wrighton, M. S. Chemical Derivatization of an Array of Three Gold Microelectrodes with Polypyrrole: Fabrication of a Molecule-Based Transistor. *J. Am. Chem. Soc.* **1984**, *106*, 5375–5377.

- (7) Paul, E. W.; Ricco, A. J.; Wrighton, M. S. Resistance of Polyaniline Films as a Function of Electrochemical Potential and the Fabrication of Polyaniline-Based Microelectronic Devices. *J. Phys. Chem. A* **1985**, *89*, 1441–1447.

- (8) Spyropoulos, G. D.; Gelinis, J. N.; Khodagholy, D. Internal Ion-Gated Organic Electrochemical Transistor: A Building Block for Integrated Bioelectronics. *Sci. Adv.* **2019**, *5*, No. eaau7378.

- (9) Venkatraman, V.; Friedlein, J. T.; Giovannitti, A.; Maria, I. P.; McCulloch, I.; McLeod, R. R.; Rivnay, J. Subthreshold Operation of Organic Electrochemical Transistors for Biosignal Amplification. *Adv. Sci.* **2018**, *5*, No. 1800453.

- (10) Tyrrell, J. E.; Petkos, K.; Drakakis, E. M.; Boutelle, M. G.; Campbell, A. J. Organic Electrochemical Transistor Common-Source Amplifier for Electrophysiological Measurements. *Adv. Funct. Mater.* **2021**, *31*, No. 2103385.

- (11) Krauhausen, I.; Koutsouras, D. A.; Melianas, A.; Keene, S. T.; Lieberth, K.; Ledanseur, H.; Sheelamanthula, R.; Giovannitti, A.; Torricelli, F.; McCulloch, I.; Blom, P. W. M.; Salleo, A.; van de Burgt, Y.; Gkoupidenis, P. Organic Neuromorphic Electronics for Sensorimotor Integration and Learning in Robotics. *Sci. Adv.* **2021**, *7*, No. eabl5068.

- (12) Ji, X.; Paulsen, B. D.; Chik, G. K. K.; Wu, R.; Yin, Y.; Chan, P. K. L.; Rivnay, J. Mimicking Associative Learning Using an Ion-Trapping Non-Volatile Synaptic Organic Electrochemical Transistor. *Nat. Commun.* **2021**, *12*, No. 2480.

- (13) Yamamoto, S.; Polyravas, A. G.; Han, S.; Malliaras, G. G. Correlation between Transient Response and Neuromorphic Behavior in Organic Electrochemical Transistors. *Adv. Electron. Mater.* **2022**, *8*, No. 2101186.

- (14) Eckel, C.; Lenz, J.; Melianas, A.; Salleo, A.; Weitz, R. T. Nanoscopic Electrolyte-Gated Vertical Organic Transistors with Low Operation Voltage and Five Orders of Magnitude Switching Range for Neuromorphic Systems. *Nano Lett.* **2022**, *22*, 973–978.

- (15) Yang, J.-T.; Ge, C.; Du, J.-Y.; Huang, H.-Y.; He, M.; Wang, C.; Lu, H.-B.; Yang, G.-Z.; Jin, K.-J. Artificial Synapses Emulated by an Electrolyte-Gated Tungsten-Oxide Transistor. *Adv. Mater.* **2018**, *30*, No. 1801548.

- (16) Wang, J.; Li, Y.; Yang, Y.; Ren, T.-L. Top-Gate Electric-Double-Layer IZO-Based Synaptic Transistors for Neuron Networks. *IEEE Electron Device Lett.* **2017**, *38*, 588–591.

- (17) Torricelli, F.; Adrahtas, D. Z.; Bao, Z.; Berggren, M.; Biscarini, F.; Bonfiglio, A.; Bortolotti, C. A.; Frisbie, C. D.; Macchia, E.; Malliaras, G. G.; McCulloch, I.; Moser, M.; Nguyen, T.-Q.; Owens, R. M.; Salleo, A.; Spanu, A.; Torsi, L. Electrolyte-Gated Transistors for Enhanced Performance Bioelectronics. *Nat. Rev. Methods Primers* **2021**, *1*, No. 66.

- (18) White, S. P.; Sreevatsan, S.; Frisbie, C. D.; Dorfman, K. D. Rapid, Selective, Label-Free Aptameric Capture and Detection of Ricin in Potable Liquids Using a Printed Floating Gate Transistor. *ACS Sens.* **2016**, *1*, 1213–1216.

- (19) Pappa, A.-M.; Curto, V. F.; Braendlein, M.; Strakosas, X.; Donahue, M. J.; Fiocchi, M.; Malliaras, G. G.; Owens, R. M. Organic Transistor Arrays Integrated with Finger-Powered Microfluidics for Multianalyte Saliva Testing. *Adv. Healthcare Mater.* **2016**, *5*, 2295–2302.

- (20) Ghafari, A. M.; Domínguez, S. E.; Järvinen, V.; Gounani, Z.; Schmit, A.; Sjöqvist, M.; Sahlgren, C.; Salo-Ahen, O. M. H.; Kvarnström, C.; Torsi, L.; Österbacka, R. In Situ Coupled Electrochemical-Goniometry as a Tool to Reveal Conformational Changes of Charged Peptides. *Adv. Mater. Interfaces* **2022**, *9*, No. 2101480.

- (21) Urbina, P. A. M.; Berto, M.; Greco, P.; Sensi, M.; Borghi, S.; Borsari, M.; Bortolotti, C. A.; Biscarini, F. Physical Insights from the Frumkin Isotherm Applied to Electrolyte Gated Organic Transistors as Protein Biosensors. *J. Mater. Chem. C* **2021**, *9*, 10965–10974.

- (22) Blasi, D.; Viola, F.; Modena, F.; Luukkonen, A.; Macchia, E.; Picca, R. A.; Gounani, Z.; Tewari, A.; Österbacka, R.; Caironi, M.; Kovacs Vajna, Z. M.; Scamarcio, G.; Torricelli, F.; Torsi, L. Printed, Cost-Effective and Stable Poly(3-Hexylthiophene) Electrolyte-Gated Field-Effect Transistors. *J. Mater. Chem. C* **2020**, *8*, 15312–15321.

- (23) Saito, Y.; Nojima, T.; Iwasa, Y. Highly Crystalline 2D Superconductors. *Nat. Rev. Mater.* **2017**, *2*, No. 16094.

- (24) Leighton, C. Electrolyte-Based Ionic Control of Functional Oxides. *Nat. Mater.* **2019**, *18*, 13–18.

- (25) Xu, K.; Fullerton-Shirey, S. K. Electric-Double-Layer-Gated Transistors Based on Two-Dimensional Crystals: Recent Approaches and Advances. *J. Phys. Mater.* **2020**, *3*, No. 032001.

- (26) Thiburce, Q.; Giovannitti, A.; McCulloch, I.; Campbell, A. J. Nanoscale Ion-Doped Polymer Transistors. *Nano Lett.* **2019**, *19*, 1712–1718.

- (27) Friedlein, J. T.; Donahue, M. J.; Shaheen, S. E.; Malliaras, G. G.; McLeod, R. R. Microsecond Response in Organic Electrochemical Transistors: Exceeding the Ionic Speed Limit. *Adv. Mater.* **2016**, *28*, 8398–8404.

- (28) Friedlein, J. T.; McLeod, R. R.; Rivnay, J. Device Physics of Organic Electrochemical Transistors. *Org. Electron.* **2018**, *63*, 398–414.

- (29) Delavari, N.; Tybrandt, K.; Berggren, M.; Piro, B.; Noël, V.; Mattana, G.; Zozoulenko, I. Nernst–Planck–Poisson Analysis of Electrolyte-Gated Organic Field-Effect Transistors. *J. Phys. D: Appl. Phys.* **2021**, *54*, No. 415101.

- (30) Zare Bidoky, F.; Frisbie, C. D. Parasitic Capacitance Effect on Dynamic Performance of Aerosol-Jet-Printed Sub 2 V Poly(3-Hexylthiophene) Electrolyte-Gated Transistors. *ACS Appl. Mater. Interfaces* **2016**, *8*, 27012–27017.

- (31) Zare Bidoky, F.; Hyun, W. J.; Song, D.; Frisbie, C. D. Printed, 1 V Electrolyte-Gated Transistors Based on Poly(3-Hexylthiophene)

- Operating at >10 KHz on Plastic. *Appl. Phys. Lett.* **2018**, *113*, No. 053301.

- (32) Zare Bidoky, F.; Tang, B.; Ma, R.; Jochem, K. S.; Hyun, W. J.; Song, D.; Koester, S. J.; Lodge, T. P.; Frisbie, C. D. Sub-3 V ZnO Electrolyte-Gated Transistors and Circuits with Screen-Printed and Photo-Crosslinked Ion Gel Gate Dielectrics: New Routes to Improved Performance. *Adv. Funct. Mater.* **2020**, *30*, No. 1902028.

- (33) Lee, K. H.; Zhang, S.; Lodge, T. P.; Frisbie, C. D. Electrical Impedance of Spin-Coatable Ion Gel Films. *J. Phys. Chem. B* **2011**, *115*, 3315–3321.

- (34) Susan, M. A. B. H.; Kaneko, T.; Noda, A.; Watanabe, M. Ion Gels Prepared by in Situ Radical Polymerization of Vinyl Monomers in an Ionic Liquid and Their Characterization as Polymer Electrolytes. *J. Am. Chem. Soc.* **2005**, *127*, 4976–4983.

- (35) Fujii, K.; Asai, H.; Ueki, T.; Sakai, T.; Imaizumi, S.; Chung, U.; Watanabe, M.; Shibayama, M. High-Performance Ion Gel with Tetra-PEG Network. *Soft Matter* **2012**, *8*, 1756–1759.

- (36) Liang, J.; Xu, K.; Wu, M.; Hunt, B. M.; Wang, W.-H.; Cho, K.; Fullerton-Shirey, S. K. Molecularly Thin Electrolyte for All Solid-State Nonvolatile Two-Dimensional Crystal Memory. *Nano Lett.* **2019**, *19*, 8911–8919.

- (37) *Thin-Film Transistors*, In Kagan, C. R.; Andry, P., Eds.; CRC Press, 2003.

- (38) Xu, K.; Islam, M. M.; Guzman, D.; Seabaugh, A. C.; Strachan, A.; Fullerton-Shirey, S. K. Pulse Dynamics of Electric Double Layer Formation on All-Solid-State Graphene Field-Effect Transistors. *ACS Appl. Mater. Interfaces* **2018**, *10*, 43166–43176.

- (39) Yang, C.; Tu, D.; Ruoko, T.; Gerasimov, J. Y.; Wu, H.; Harikesh, P. C.; Masetti, M.; Stoeckel, M.; Kroon, R.; Müller, C.; Berggren, M.; Fabiano, S. Low-Power/High-Gain Flexible Complementary Circuits Based on Printed Organic Electrochemical Transistors. *Adv. Electron. Mater.* **2021**, *8*, No. 2100907.

- (40) Zabihipour, M.; Tu, D.; Strandberg, J.; Berggren, M.; Engquist, I.; Andersson Ersman, P. Designing Inverters Based on Screen Printed Organic Electrochemical Transistors Targeting Low-Voltage and High-Frequency Operation. *Adv. Mater. Technol.* **2021**, *6*, No. 2100555.

- (41) Hong, K.; Kim, Y. H.; Kim, S. H.; Xie, W.; Xu, W. D.; Kim, C. H.; Frisbie, C. D. Aerosol Jet Printed, Sub-2 V Complementary Circuits Constructed from P- and N-Type Electrolyte Gated Transistors. *Adv. Mater.* **2014**, *26*, 7032–7037.

- (42) Hong, K.; Kim, S. H.; Lee, K. H.; Frisbie, C. D. Printed, Sub-2V ZnO Electrolyte Gated Transistors and Inverters on Plastic. *Adv. Mater.* **2013**, *25*, 3413–3418.

- (43) Tang, B.; White, S. P.; Frisbie, C. D.; Lodge, T. P. Synergistic Increase in Ionic Conductivity and Modulus of Triblock Copolymer Ion Gels. *Macromolecules* **2015**, *48*, 4942–4950.

- (44) Cho, J. H.; Lee, J.; Xia, Y.; Kim, B.; He, Y.; Renn, M. J.; Lodge, T. P.; Frisbie, C. D. Printable Ion-Gel Gate Dielectrics for Low-Voltage Polymer Thin-Film Transistors on Plastic. *Nat. Mater.* **2008**, *7*, 900–906.

- (45) Thiburce, Q.; Porcarelli, L.; Mecerreyes, D.; Campbell, A. J. High Performance Photolithographically-Patterned Polymer Thin-Film Transistors Gated with an Ionic Liquid/Poly(Ionic Liquid) Blend Ion Gel. *Appl. Phys. Lett.* **2017**, *110*, No. 233302.