# Effects of Temperature and Structural Geometries on a Skyrmion Logic Gate

Chunli Tang<sup>®</sup>, *Graduate Student Member, IEEE*, Laith Alahmed, *Student Member, IEEE*, Jihao Xu, *Student Member, IEEE*, Maokang Shen<sup>®</sup>, *Student Member, IEEE*, Nicholas Alex Jones, Mehdi Sadi, Ujjwal Guin<sup>®</sup>, *Member, IEEE*, Wenfeng Zhao, *Member, IEEE*, and Peng Li<sup>®</sup>, *Member, IEEE*

*Abstract*—We design a skyrmion-magnetic domain interconversion logic gate (SkyMDILogic) gate and use it as a model system to study the geometrical and thermal effects. We particularly focus on the effects of temperature and structural defects. Micromagnetic simulations are used to study the skyrmion movement and characterize the relevant properties. We also construct an equivalent circuit model to calculate the energy consumption and logic operations at different temperatures. We find that temperature significantly affects the stability of a skyrmion. At elevated temperatures, the skyrmion propagation is more robust against the pinning effect of structural defects. Our results highlight the effects of thermal and structural defects, which remained largely unexplored in previous logic gate designs.

*Index Terms*—Skyrmion logic gate, skyrmion memory, spintronic logic, thermal fluctuations.

## I. INTRODUCTION

AGNETIC skyrmions represent a realizable topological magnetic texture in real space and can work as an ideal candidate for implementing novel logic designs and magnetic memories [1]–[3]. Skyrmions have been observed in various magnetic systems lacking inversion symmetry [1], [4]. They arise from the competition between Dzyaloshinskii–Moriya interaction (DMI) and perpendicular energy interactions, such as Heisenberg exchange, or a combination of various uniaxial

Manuscript received August 15, 2021; revised October 5, 2021 and November 2, 2021; accepted November 16, 2021. Date of publication December 10, 2021; date of current version March 28, 2022. This work was supported in part by the Ralph E. Powe Junior Faculty Enhancement Award funded by Oak Ridge Associated Universities (OARU), in part by the Research Support Program funded by Auburn University, and in part by the U.S. National Science Foundation under Grant DMR-2129879335. The review of this article was arranged by Editor B. K. Kaushik. (*Chunli Tang, Laith Alahmed, and Jihao Xu contributed equally to this work.*) (*Corresponding author: Peng Li.*)

Chunli Tang, Laith Alahmed, Jihao Xu, Nicholas Alex Jones, Mehdi Sadi, Ujjwal Guin, and Peng Li are with the Department of Electrical and Computer Engineering, Auburn University, Auburn, AL 36849 USA (e-mail: peng.li@auburn.edu).

Maokang Šhen is with the School of Optical and Electronic Information, Huazhong University of Science and Technology, Wuhan 430074, China.

Wenfeng Zhao is with the Department of Electrical and Computer Engineering, SUNY-Binghamton University, Binghamton, NY 13902 USA.

Color versions of one or more figures in this article are available at https://doi.org/10.1109/TED.2021.3130217.

Digital Object Identifier 10.1109/TED.2021.3130217

anisotropy energy terms, or dipolar interaction in magnetic materials [5]. Skyrmions have many interesting properties, including nanometer diameters for high-density storage, roomtemperature stability, current-controlled motion, topological charge, and symmetry protection against large defects. Various logic and memory devices have been proposed based on the unique properties of skyrmions [5]-[10]. Many of these devices rely on the linear motion of skyrmions from the input to the output. Such skyrmion motion suffers from transverse deviation due to the skyrmion Hall effect and requires extra components to facilitate desired skyrmion propagation [9]. Recent findings show that such issues can be overcome by exploiting the interconversion of skyrmion-magnetic domain walls at the joining part of narrow and wide nanowires. This technique offers advantages such as lower driving electrical currents and higher speeds [11], [12]. Moreover, a recent study has shown that a skyrmion can be generated at a gigahertz (GHz) frequency through skyrmion-domain wall pair interconversion [5]. However, the effects of thermal and structural defects on the performance of skyrmion logic gates remain largely overlooked [13].

In this work, we design a logic gate based on skyrmionmagnetic domain interconversion (SkyMDILogic) and use it as a model system to study the dependences of skyrmion stability and velocity and skyrmion stability on elevated temperatures, structural defects, electrical current density, and magnetic damping. We also carry out circuit simulations at different temperatures. Our work paves the way to engineer skyrmion devices for practical computing applications. The primary contributions of this article are summarized as follows.

- Identify the impact of temperature on skyrmion propagation and logic gate performance.

- Demonstrate the SkyMDILogic performance with coexisting structural defects and temperature effects.

- Estimate the energy-delay product (EDP) of SkyMDI-Logic through temperature-dependent circuit simulations.

- 4) Study the effects of current density and magnetic damping on the skyrmion propagation velocity and stability.

In the following sections, we discuss the device structure and basic operation principles, the characterization of the

0018-9383 © 2021 IEEE. Personal use is permitted, but republication/redistribution requires IEEE permission. See https://www.ieee.org/publications/rights/index.html for more information.

Authorized licensed use limited to: Auburn University. Downloaded on May 02,2022 at 21:26:37 UTC from IEEE Xplore. Restrictions apply.

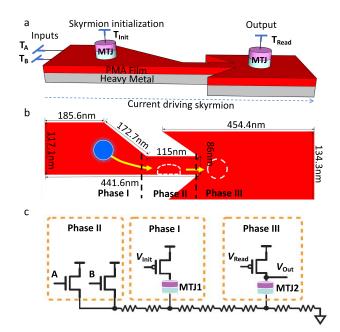

Fig. 1. Two-input AND SkyMDILogic gate structure and circuit model. (a) 3-D view of the SkyMDILogic device structure. In the figure, the red/gray layers are PMA film/HM film, respectively. MTJ1 is to nucleate a skyrmion and MTJ2 is for sensing the skyrmion. The pink and light blue layers in the MTJs represent a pinned magnet and MgO tunneling layer, respectively.  $T_A$  and  $T_B$  are both nMOS transistors for two-terminal inputs.  $T_{\text{Init}}$  is a pMOS transistor to generate skyrmion.  $T_{\text{Read}}$  is a pMOS transistor for skyrmion detection. (b) Geometry of the nanotrack and skyrmion-magnetic domain interconversion and propagation processes. (c) Resistive model and device operation phases. The resistors in series at the bottom represent the resistances of the HM layer.

SkyMDILogic properties, circuit modeling, and device performance evaluation.

### II. DEVICE STRUCTURE AND BASIC OPERATIONS

As shown in Fig. 1(a), the SkyMDILogic device comprises several components as follows.

- 1) The bottom section of the device is a specially designed nanotrack that is patterned out of a bi-layer structure consisting of a CoFeB magnetic layer with perpendicular magnetic anisotropy (PMA) and a Pt heavy metal (HM) layer. The layers are chosen such that the strong DMI required for stabilizing skyrmions is realized. The dimensions of the device are annotated in Fig. 1(b). Two nMOS transistors,  $T_A$  and  $T_B$ , are used to generate skyrmion propagation currents at the input terminal.

- 2) A skyrmion initialization section, consisting of a magnetic tunnel junction (MTJ1) and a pMOS transistor  $T_{\text{Init}}$ , is used to create a skyrmion at the beginning of the logic operation.

- 3) At the output terminal, a second MTJ (MTJ2) and a pMOS transistor ( $T_{\text{Read}}$ ) are used near the end of the device to sense the skyrmion.

The design principle of SkyMDILogic is inspired by the dynamic CMOS logic family. The device illustrated in Fig. 1(a) works as a two-input AND gate. The logic operation is performed in three separate phases as follows: Phase I is the skyrmion nucleation phase (Skyr-Nuc Phase). If a voltage  $V_{\text{Init}}$  is applied to the  $T_{\text{Init}}$  transistor such that  $V_{\text{Init}} < V_{\text{Th}}$ , where  $V_{\text{Th}}$  is the threshold voltage of  $T_{\text{Init}}$  and since  $T_{\text{Init}}$  is a pMOS transistor, current flows into MTJ1 and a skyrmion is created in the nanotrack. This initiates the logic process, which is similar to the precharge phase in the dynamic logic of CMOS gates.

Phase II is the skyrmion propagation phase (Skyr-Prop Phase). Two input voltages are applied to the two-input nMOS transistors  $T_A$  and  $T_B$  (the outputs of other gates can be used as inputs for cascading). Depending on the applied input voltages, currents can flow from  $T_A$  and  $T_B$  into the HM layer. If the summation of the two currents exceeds the threshold for skyrmion propagation, the skyrmion (created in Phase I) will travel from the input terminal, through the bridge, to the readout terminal due to the spin Hall effect. As the skyrmion propagates longitudinally along the nanotrack, it also experiences a transverse motion due to skyrmion-edge repulsion from the sloped upper boundary [6], [9]. As demonstrated in Fig. 1(b), this repulsion force pushes the skyrmion down and squeezes it into a magnetic domain and through the bridge, as indicated by the broken-line circles. After the magnetic domain passes the bridge, it gradually nucleates back into a new skyrmion and moves toward MTJ2 [5].

Phase III is the skyrmion detection phase (Skyr-Det Phase). For skyrmion detection, a pMOS transistor  $T_{\text{Read}}$  is connected to MTJ2. T<sub>Read</sub> can be used for readout and logic cascading [14]. During the non-reading time,  $V_{\text{Read}}$  remains HIGH and the pMOS  $T_{\text{Read}}$  is turned off, therefore the output voltage  $V_{\text{Out}}$  is LOW (Logic "0") due to the low MTJ magnetoresistance ( $R_{\rm MTJ,LOW} = 1 \ k\Omega$ ). During the Skyr-Det Phase,  $V_{\rm Read}$ is LOW, thus, the pMOS  $T_{\text{Read}}$  is turned on. The output node voltage is detected by the presence of a skyrmion beneath MTJ2. If no skyrmion is present, then the pull-down nodes will still exhibit a low resistance, leading to a LOW (Logic "0") output. On the contrary, if a skyrmion arrives at the output, it will be detected by MTJ2. By setting the magnetization direction of the pinned magnet to be the opposite direction to that of the skyrmion, a high magnetoresistance ( $R_{\text{MTJ,HIGH}} =$  $3 \text{ k}\Omega$ ) can be expected. This will lead to a HIGH output voltage at the output node  $V_{Out}$ , representing logic "1." The Skyr-Det Phase is similar to the evaluation phase in CMOS dynamic logic. The three phases are shown in Fig. 1(c), which will be discussed in Section IV.

To analyze the dynamic behaviors of skyrmions in our design, we performed micromagnetic simulations using objectoriented micromagnetic framework (OOMMF), which is a public micromagnetics program developed at the National Institute of Standards and Technology [15]. In the OOMMF simulations, an HM/PMA-magnet bilayer device was used, with a configuration that is similar to previous studies [6], [9]. Table I summarizes the parameters used in the simulation, which we have adopted from [9]. The current-induced skyrmion motion is modeled by the Landau–Lifshitz–Gilbert equation with spin-transfer torque terms as shown below [16]

$$\frac{d\mathbf{m}}{dt} = -|\gamma| \mathbf{m} \times \mathbf{H}_{\text{eff}} + \alpha \left(\mathbf{m} \times \frac{d\mathbf{m}}{dt}\right) +|\gamma| \beta \epsilon \left(\mathbf{m} \times \mathbf{m}_p \times \mathbf{m}\right) - |\gamma| \beta \epsilon' \left(\mathbf{m} \times \mathbf{m}_p\right) \quad (1)$$

| Parameter                                     | Value                                                  |

|-----------------------------------------------|--------------------------------------------------------|

| Gilbert damping factor                        | 0.25                                                   |

| Spin Hall Angle $\theta_{\rm A}$              | 0.4                                                    |

| Saturation magnetization $M_s$                | $5.8 \times 10^5 \text{A/m}$                           |

| DMI Constant D                                | $3.5 \text{ mJ/m}^2$                                   |

| Perpendicular magnetic anisotropy $K_{\rm u}$ | $0.9 	imes 10^6 	ext{ J/m}^3$                          |

| Exchange stiffness $A_{ex}$                   | $1.5 \times 10^{-11} \text{ J/m}$                      |

| Mesh Size $d_x \times d_y \times d_z$         | $2 \text{ nm} \times 1 \text{ nm} \times 1 \text{ nm}$ |

| PMA Film Resistivity                          | $1.7 \times 10^{-7}  \Omega \cdot m$                   |

| HM Film Resistivity                           | $1.06 \times 10^{-7} \Omega \cdot m$                   |

| MTJ HIGH Resistance                           | 3 kΩ                                                   |

| MTJ LOW Resistance                            | 1 kΩ                                                   |

| Nucleation Time                               | 5 ps                                                   |

| Propagation Time                              | 3 ns                                                   |

| Read Time                                     | 3 ns                                                   |

| Nucleation Current                            | 565 μΑ                                                 |

| Driving Current                               | 70 µA                                                  |

TABLE I DEVICE SIMULATION PARAMETERS

where **m** is the magnetization,  $\mathbf{m}_p$  denotes the electron polarization direction,  $\alpha$  is the Gilbert damping constant,  $\gamma$  is the gyromagnetic ratio,  $\beta = |(\hbar/\mu_0 e)|(J/tM_s)$ , and  $\epsilon$  and  $\epsilon'$ are functions of **m** and other constants. In our simulation, we consider an interfacial DMI at the HM/PMA-magnet interface. For the simulation, the corresponding DMI extension module has been added to the OOMMF software [17].

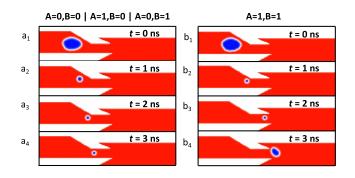

The AND gate operations are illustrated by the micromagnetic simulation graphs in Fig. 2. Two inputs, A and B, each equaling either logic "1" or logic "0," are applied to the input nMOS transistors  $T_A$  and  $T_B$ . Here, a logic "0" input means applying zero voltage  $(V_{Low})$ , and logic "1" input means applying a high voltage  $(V_{High})$  to turn on the transistor. When an input transistor is turned on, it provides a current with density  $J = 1 \times 10^{11}$  A/m<sup>2</sup>. Fig. 2(a) shows the time evolution of the skyrmion motion for three input cases: 1) A = "0,"B = "0"; 2) A = "1," B = "0"; and 3) A = "0," B = "1."In all of these cases, the electric current density is below the threshold  $J_{\text{prop}} = 2 \times 10^{11} \text{ A/m}^2$  required to drive a skyrmion to the output. The repulsion from the sloped upper boundary exerts a strong Magnus force on the skyrmion, squeezing and pushing it toward the bottom of the structure, as shown in Fig.  $2(a_1)-(a_4)$ . However, the skyrmion remains at the entrance of the bridge location when the operation is finished. In these cases, no skyrmion is detected at MTJ2; thus, the output reads a low magnetoresistance and stays LOW, with a corresponding output logic signal "0." Fig. 2(b) shows the case when A = "1" and B = "1." In this case, the total current density is  $2 \times 10^{11}$  A/m<sup>2</sup>, which equals  $J_{\text{prop}}$ . Thus, the current is strong enough to drive the skyrmion to MTJ2, resulting in the logic signal "1." The total time for skyrmion propagation is t = 3 ns.

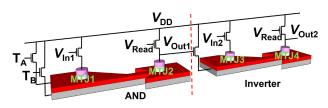

It should be noted that our design can be used to realize other logic operations as well. Fig. 3 shows a sketch of the NAND gate comprising an AND gate cascaded with an inverter. The operation of the AND gate is illustrated above. The inverter works similar to the AND gate, except that the pinned magnet in MTJ4 at the output of the inverter has the same

Fig. 2. Micromagnetic simulations of the AND logic gate. (a<sub>1</sub>)–(a<sub>4</sub>) For the three cases (1) A = "0," B = "0," (2) A = "1," B = "0," and (3) <math>A = "0," B = "1," the skyrmion does not reach the output, thus output  $C = "0." (b_1)-(b_4)$  When A = "1," B = "1," the skyrmion reaches the output, thus C = "1."

Fig. 3. NAND gate comprising an AND gate cascaded with an inverter.

magnetization as the skyrmion. Thus, a low magnetoresistance can be expected when a skyrmion appears. In this regard, a HIGH  $V_{Out1}$  signal leads to a LOW  $V_{Out2}$  signal, and vice versa. Since the NAND gate is a universal gate, all other gates can be constructed using a combination of NAND gates.

# III. CHARACTERIZATION OF SKYMDILOGIC SKYRMION PROPERTIES

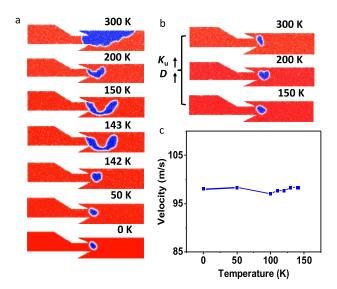

We start by investigating the effects of temperature on the shape and stability of the skyrmions. Fig. 4 shows the temperature dependence of the skyrmion stability and skyrmion propagation velocity. The velocity is calculated as  $v_{\text{skrymion}} =$ propagation distance/propagation time. In Fig. 4(a), the damping constant is 0.25, the current density  $J = 2 \times 10^{11}$  A/m<sup>2</sup>, and the driving current pulse is 3 ns. From the results, the following was observed. First, the skyrmion maintains the circular shape at lower temperatures but deforms into a U-shape magnetic domain above 142 K [see Fig. 4(a)]. The stabilization of the skyrmion depends on the balances of different energies, such as exchange energy, anisotropy energy, thermal energy, and so on. Higher temperatures can lead to spin perturbations and destabilize a skyrmion [18], [19]. To improve the working temperature range, we have carried out simulations with different parameters. We have found that if both the anisotropy constant  $K_u$  and the DMI constant D are increased (e.g.,  $K_u = 1.1 \times 10^6 \text{ J/m}^3$ ,  $D = 3.8 \text{ mJ/m}^2$ at 300 K), the skyrmion can be stabilized at a higher temperate, as shown in Fig. 4(b). While temperature strongly affects the skyrmion stability, the skyrmion propagation velocity is largely unperturbed by temperature, as shown in Fig. 4(c). Thus, we conclude that increased temperatures can hinder the expected behavior of our design, but not its performance

Fig. 4. (a) Skyrmion movement and shape evolution at different temperatures. (b) Stabilization of the skyrmion at higher temperatures. (c) Dependence of the skyrmion propagation velocity on temperature.

Fig. 5. Effect of geometrical defects on skyrmion movement and shape evolution at (a) 0 K, (b) 100 K, and (c) 142 K.

(i.e., propagation velocity). Our results highlight the importance of temperature considerations in designing skyrmionbased logic gates.

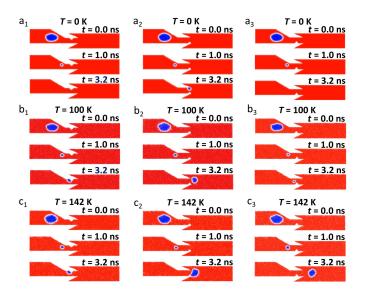

Next, we introduce several structural defects (notches) into SkyMDILogic to study their effects on the skyrmion propagation at different temperatures. Fig. 5 shows the simulation results of structural defects on the logic gate functions at 0 K, 100 K, and 142 K, respectively. In Fig. 5(a<sub>1</sub>), (b<sub>1</sub>), and (c<sub>1</sub>), a top-notch in the middle of the bridge is studied. In this case, the skyrmion tends to move up in the bridge due to the skyrmion Hall effect. This makes it move toward the top notch and gets pinned by it. At T = 0 K, the skyrmion disappears at the bridge boundary at t = 3.2 ns. At 100 K and 142 K, the skyrmion still exists, though it does not have enough energy to get depinned from the top notch.

Fig. 6. Skyrmion propagation with different geometrical parameters. (a) Effect of input slope angle by  $(a_1) - 10^\circ$  and  $(a_2) + 10^\circ$ . (b) Effect of output slope angle by  $(b_1) - 5^\circ$  and  $(b_2) + 15^\circ$ . (c) Effect of bridge length  $((c_1) = 215 \text{ nm}, (c_2) = 190 \text{ nm}, (c_3) = 165 \text{ nm}, (c_4) = 140 \text{ nm})$ . (d) Skyrmion propagation time versus bridge length.

In Fig. 5(a<sub>2</sub>), (a<sub>3</sub>), (b<sub>2</sub>), (b<sub>3</sub>), (c<sub>2</sub>), and (c<sub>3</sub>), notches are introduced into the bottom boundary of the bridge structure. At T = 0 K, the skyrmion is again not able to pass the bridge to the output due to the significant notch pinning effect [see Fig. 5(a<sub>2</sub>) and (a<sub>3</sub>)]. As *T* increases to 100 K, the skyrmion can overcome the strong notch pinning effect and move toward the output region [see Fig. 5(b<sub>2</sub>) and (b<sub>3</sub>)]. At T = 142 K, as shown in Fig. 5(c<sub>2</sub>) and (c<sub>3</sub>), the raised temperature adds more energy to the skyrmion and drives it further. The results shown in Fig. 5 indicate that an elevated temperature can help overcome the structural defects and increase the propagation velocity due to more energy being generated from thermal fluctuations, which facilitates the skyrmion propagation process in the presence of defects.

We then study how geometrical variation affects the skyrmion propagation in the AND gate. Fig. 6 shows simulations of skyrmion propagation in structures with different upper boundary slope angles and bridge lengths. Fig.  $6(a_1)$  and  $(a_2)$  shows the effect of the input slope angle change. Compared to the original design, where the input slope angle is  $30^\circ$ , reducing the input slope angle by  $10^\circ$  lowers the propagation velocity slightly [see Fig.  $6(a_1)$ ]. This is a result of the more gradual squeezing of the skyrmion into the bridge. As shown in Fig.  $6(a_2)$ , the  $10^\circ$  increment leads to the annihilation of the skyrmion at the entrance of the bridge due to skyrmion–edge interaction [20]. Fig.  $6(b_1)$  and  $(b_2)$  shows the effect of the output slope angle change. Reducing the output slope angle by  $5^\circ$  leads to the annihilation of the skyrmion. The reduction of the output slope angle shortens

Fig. 7. (a) Skyrmion movement and shape evolution at different current densities. (b) Dependence of skyrmion propagation velocity on current density.

the distance between the input and output sloped structures, thus leading to a stronger skyrmion–edge interaction to impede its movement. On the other hand, as the output slope increases by  $15^{\circ}$ , it pins the skyrmion at the right end of the bridge. Fig.  $6(c_1)-(c_4)$  studies the effect of the bridge length. As one can expect, when the length increases (reduces), the skyrmion needs more (less) time to propagate through the bridge. Based on our simulations, we see a linear relationship between the skyrmion propagation time and bridge length as shown in Fig. 6(d). Therefore, the bridge length significantly affects the propagation time.

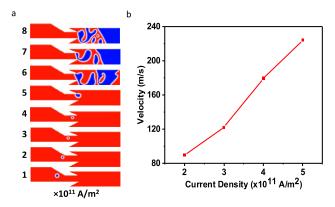

After that, we analyze the effects of varying the input current density and the PMA magnetic damping constant on the shape of the skyrmion in our AND gate. Fig. 7 shows the skyrmion movement and evolution as a function of driving current density, respectively. In Fig 7(a), the driving current pulse was set to 1 ns. The damping constant was set to the default value of 0.25. One can see that: 1) a higher current density moves the skyrmion further and 2) the skyrmion evolves into multiple magnetic domains beyond  $J = 5 \times 10^{11}$  A/m<sup>2</sup>. This sets the maximum current density that is allowed in the SkyMDILogic device. Fig. 7(b) plots the skyrmion propagation velocity as a function of current density. The results indicate that the velocity of a skyrmion evolves with the current density; a higher current density will lead to a faster skyrmion motion, which is consistent with previous studies [21].

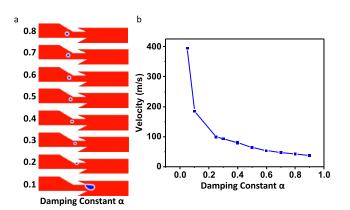

Similarly, we discuss how the damping constant  $\alpha$  affects the skyrmion propagation velocity. Fig. 8 shows the skyrmion movement and evolution images as a function of damping constant. Fig. 8(a) shows the skyrmion movement and evolution with different damping constants at a fixed current of  $2 \times 10^{11}$  A/m<sup>2</sup> pulsed for 1.4 ns. One can see that when  $\alpha = 0.1$ , the skyrmion is pinned at the end of the bridge. Our other simulations show that the skyrmion can propagate through the bridge when  $\alpha \ge 0.2$ . Our results in Fig. 8(a) and (b) suggest that an operational sweet spot for  $\alpha$  must be chosen for the successful propagation and reconstruction of the traveling skyrmion.  $\alpha$  must be high enough to stabilize the skyrmion but low enough to allow for the skyrmion propagation through the bridge at reasonable velocities.

Fig. 8. (a) Skyrmion movement and shape evolution at different damping constants. (b) Dependence of skyrmion propagation velocity on damping constant.

Thus, in future, skyrmion-based logic gate designs and manufacturing processes, careful consideration of geometrical parameters, structural defects, operational current densities, thermal effects, and the magnetic damping constant must be taken to ensure optimal operation speeds and device stability. A resistive circuit model representation of our device will help determine what operation speeds and power consumption can be reasonably expected from our design and will be discussed in the following section.

# IV. CIRCUIT MODELING AND PERFORMANCE EVALUATION

To evaluate the timing and energy performances for SkyMDILogic, we build an equivalent circuit model, illustrated in Fig. 1(c), as proposed in [22]. The different device parameters, including resistances of MTJ and nanotrack, the timing (skyrmion nucleation and propagation times), as well as the required current densities for skyrmion nucleation and propagation were all extracted from the OOMMF simulations discussed in Sections II and III. The circuit simulation parameters are listed in Table I. These parameters, along with the geometry of the proposed device, were converted into equivalent circuit element values for SPICE simulations. Table I lists all the parameters used. For transistor modeling, we adopt a 16-nm HP predictive technology model (PTM) [23] for our implementation.

From the OOMMF simulations, the critical current density required for skyrmion nucleation is found to be  $5 \times 10^{11}$  A/m<sup>2</sup> for Phase I (Skyr-Nuc Phase). Combining the geometry information of the proposed device, this is equivalent to a critical current of  $I_{sky-nuc} = 565 \ \mu$ A needed to nucleate a skyrmion by MTJ1. Though the nucleation time in MTJ1 is 1.5 ps from the OOMMF simulations, during the circuit simulation, a longer  $V_{Init}$  pulse is recommended; therefore, a 5-ps nucleation current pulse was used, activating the pMOS  $T_{Init}$  and ensuring skyrmion nucleation through MTJ1.

In Phase II (Skyr-Prop Phase), the two input voltages  $V_A$  and  $V_B$  are pulsed for  $t_{\text{Skyr-Prop}} = 3$  ns to ensure sufficient time for the skyrmion to propagate from the MTJ1 site, through the bridge, and into the MTJ2 site. As discussed in Section II, each input of the AND gate provides  $J = 1 \times 10^{11} \text{ A/m}^2$ ; this leads

Fig. 9. Transient simulation results of SkyMDIlogic AND gate voltage waveforms.

-2.0 10 15 Time (ps) 2 3 0 1 4 5 6 Time (ns)

0.5

0.0 Current (mA)

-0.5

-1.0

-1.5

-2.0

566 u.A

Is (nuc)

Is (prop)

0.5

0.0

-0.5

-1.0

-1.5

Current (mA)

Fig. 10. Transient simulation results of SkyMDILogic AND gate Skyrmion nucleation and propagation currents.

to a total driving current of  $I_{\text{Skyr-Prop}} = 140 \ \mu\text{A}$  (each input contributes 70  $\mu$ A) in the nanotrack.

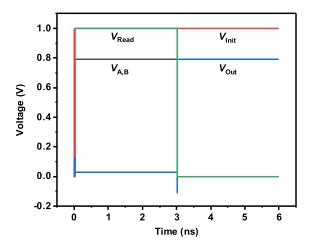

In Phase III (Skyr-Det Phase), V<sub>Read</sub> is turned to LOW for  $t_{\text{Read}} = 3$  ns, activating pMOS and ensuring the detection of the skyrmion, as well as passing the result to the input of the next gate. Once the skyrmion successfully reaches MTJ2 (or without a propagating skyrmion due to LOW inputs),  $V_{\text{Read}}$  was set to LOW and turned on the pMOS transistor for reading. If a skyrmion is present (absent) underneath MTJ2,  $V_{\text{Out}}$  reads HIGH (LOW), as discussed in detail in Section II.  $V_{\text{Init}}$ ,  $V_A$ ,  $V_B$ , and  $V_{\text{Read}}$  signals are summarized in Fig. 9.

It should be noted that the output voltage of the AND gate should be appropriate for cascading to a consecutive logic gate input, that is, the nMOS transistor input of the next gate. As a result, this HIGH voltage should be high enough to ensure the ON current for the next stage nMOS transistor for input signals. Moreover, to ensure the skyrmion propagation in the gate of the next stage, the skyrmion detection time in the detection phase (Skyr-Det Phase) should be at least equal to the skyrmion propagation time. Taking those conditions into consideration, we use 3 ns for the propagation current in the SPICE simulation of the AND gate. Fig. 10 shows the nucleation and propagation current profiles.

The above discussion summarizes reasonable operation times and parameters for the SkyMDILogic and its equivalent circuit, as well as the optimization procedures for the MTJs. We considered the circuit modeling at 50 K. It is found that the modeling results vary by 2%–3% between 0 K and 142 K. Taking into consideration the resistances, transistors sizing, and pulse widths, a conservative estimation of our AND gate delay is approximately 6 ns. As mentioned previously, we used a 16-nm HP PTM model to simulate the circuit in the SPICE simulation. The power consumption of this AND gate is 170  $\mu$ W and the energy consumption is 1.24 pJ (in a 6-ns window). The EDP is evaluated to be  $3.7 \times 10^{-21}$  J  $\cdot$  s. Considering that most skyrmion-based logic designs have not performed circuit-level simulations or evaluated EDPs [5]-[9], our work provides a more comprehensive study on skyrmion logic gate performance.

SkyMDILogic has several unique advantages. The write current is much lower than most of the previous skyrmion and domain wall-based logic designs while achieving a high skyrmion movement velocity [5], [6], [9], [11]-[13]. A low writing current is helpful to improve the lifetime of the device. In addition, SkyMDILogic has a simple design, and does not require extra structures to avoid the transverse motion of skyrmions [9], [13]. Moreover, SkyMDILogic uses a single skyrmion for the logic operation and is not subject to requirements such as multi-skyrmion synchronization [12].

#### V. CONCLUSION

In this work, we design a skyrmion-magnetic domain interconversion logic gate (SkyMDILogic) and use it as a model structure to study the effects of elevated temperatures and structural defects on speed and skyrmion stability using various geometrical and magnetic parameters. We have found that elevated temperatures can significantly disrupt skyrmion stability. On the other hand, the elevated temperature can help with the depinning of magnetic domains in the presence of structural defects, thus improving the propagation process. The EDP is estimated to be  $3.6 \times 10^{-21}$  J  $\cdot$  s at 50 K, and it differs by 2%-3% at different temperatures. Our findings have paved the way for developing skyrmion-based logic gates, which suggest that thermal effects and structural defects need careful consideration to ensure optimal operation speeds and device stability.

#### REFERENCES

- [1] A. Fert, V. Cros, and J. Sampaio, "Skyrmions on the track," Nature Nanotechnol., vol. 8, no. 3, pp. 152-156, Mar. 2013, doi: 10.1038/nnano. 2013 29

- [2] S. Li et al., "Magnetic skyrmions for unconventional computing," Mater. Horizons, vol. 8, no. 3, pp. 854-868, Mar. 2021, doi: 10.1039/D0MH01603A

- [3] Z. Guo et al., "Spintronics for energy-efficient computing: An overview and outlook," Proc. IEEE, vol. 109, no. 8, pp. 1398-1417, Aug. 2021, doi: 10.1109/JPROC.2021.3084997.

- W. Jiang, G. Chen, K. Liu, J. Zang, S. G. T. Velthuis, and A. Hoffmann, [4] "Skyrmions in magnetic multilayers," Phys. Rep., vol. 704, pp. 1-49, Aug. 2017, doi: 10.1016/j.physrep.2017.08.001.

- [5] A. M. Cheghabouri and M. C. Onbasli, "Direct current-tunable MHz to multi-GHz skyrmion generation and control," *Sci. Rep.*, vol. 9, no. 1, p. 9496, Jul. 2019, doi: 10.1038/s41598-019-45972-9.

- [6] S. Luo *et al.*, "Reconfigurable skyrmion logic gates," *Nano Lett.*, vol. 18, no. 2, pp. 1180–1184, Feb. 2018, doi: 10.1021/acs.nanolett.7b04722.

- [7] C. Deger, I. Yavuz, and F. Yildiz, "Current-driven coherent skyrmion generation," *Sci. Rep.*, vol. 9, no. 1, p. 3513, Mar. 2019, doi: 10.1038/ s41598-019-40220-6.

- [8] Z. He, S. Angizi, and D. Fan, "Current-induced dynamics of multiple skyrmions with domain-wall pair and skyrmion-based majority gate design," *IEEE Magn. Lett.*, vol. 8, pp. 1–5, 2017, doi: 10.1109/Imag.2017.2689721.

- [9] M. G. Mankalale, Z. Zhao, J.-P. Wang, and S. S. Sapatnekar, "SkyLogic—A proposal for a skyrmion-based logic device," *IEEE Trans. Electron Devices*, vol. 66, no. 4, pp. 1990–1996, Apr. 2019, doi: 10.1109/TED.2019.2899263.

- [10] S. Li, W. Kang, Y. Huang, X. Zhang, Y. Zhou, and W. Zhao, "Magnetic skyrmion-based artificial neuron device," *Nanotechnology*, vol. 28, no. 31, Jul. 2017, Art. no. 31LT01, doi: 10.1088/1361-6528/aa7af5.

- [11] Y. Zhou and M. Ezawa, "A reversible conversion between a skyrmion and a domain-wall pair in a junction geometry," *Nature Commun.*, vol. 5, p. 4652, Aug. 2014, doi: 10.1038/ncomms5652.

- [12] X. Zhang, M. Ezawa, and Y. Zhou, "Magnetic skyrmion logic gates: Conversion, duplication and merging of skyrmions," *Sci. Rep.*, vol. 5, p. 9400, Mar. 2015, doi: 10.1038/srep09400.

- [13] X. Zhang, Y. Zhou, M. Ezawa, G. P. Zhao, and W. Zhao, "Magnetic skyrmion transistor: Skyrmion motion in a voltage-gated nanotrack," *Sci. Rep.*, vol. 5, Jun. 2015, Art. no. 11369, doi: 10.1038/srep11369.

- [14] N. E. Penthorn, X. Hao, Z. Wang, Y. Huai, and H. W. Jiang, "Experimental observation of single skyrmion signatures in a magnetic tunnel junction," *Phys. Rev. Lett.*, vol. 122, no. 25, Jun. 2019, Art. no. 257201, doi: 10.1103/PhysRevLett.122.257201.

- [15] M. J. Donahue and M. Donahue, "OOMMF user's guide, version 1.0," U.S. Dept. Commerce, Nat. Inst. Standards Technol., Washington, DC, USA, Tech. Rep., 1999. [Online]. Available: http://math.nist.gov/oommf

- [16] X. Zhang, M. Ezawa, and Y. Zhou, "Thermally stable magnetic skyrmions in multilayer synthetic antiferromagnetic racetracks," *Phys. Rev. B, Condens. Matter*, vol. 94, no. 6, Aug. 2016, Art. no. 064406, doi: 10.1103/PhysRevB.94.064406.

- [17] D. Cortés-Ortuño, M. Beg, V. Nehruji, R. A. Pepper, and H. Fangohr, "OOMMF extension: Dzyaloshinskii–Moriya interaction (DMI) for crystallographic classes T and O," Tech. Rep., Mar. 2018, doi: 10.5281/ zenodo.1196820.

- [18] A. Sonntag, J. Hermenau, S. Krause, and R. Wiesendanger, "Thermal stability of an interface-stabilized skyrmion lattice," *Phys. Rev. Lett.*, vol. 113, no. 7, Aug. 2014, Art. no. 077202. [Online]. Available: https://link.aps.org/doi/10.1103/PhysRevLett.113.077202

- [19] S. Luo, N. Xu, Y. Wang, J. Hong, and L. You, "Thermally assisted skyrmion memory (TA-SKM)," *IEEE Electron Device Lett.*, vol. 41, no. 6, pp. 932–935, Jun. 2020, doi: 10.1109/LED.2020.2986312.

- [20] X. Liang *et al.*, "Antiferromagnetic skyrmion-based logic gates controlled by electric currents and fields," *Appl. Phys. Lett.*, vol. 119, no. 6, Aug. 2021, Art. no. 062403, doi: 10.1063/5.0056259.

- [21] J. Ding, X. Yang, and T. Zhu, "Manipulating current induced motion of magnetic skyrmions in the magnetic nanotrack," *J. Phys. D*, *Appl. Phys.*, vol. 48, no. 11, Mar. 2015, Art. no. 115004. [Online]. Available: https://iopscience.iop.org/article/10.1088/0022-3727/48/11/ 115004

- [22] C. Wang, Z. Wang, M. Wang, X. Zhang, Y. Zhang, and W. Zhao, "Compact model of Dzyaloshinskii domain wall motion-based MTJ for spin neural networks," *IEEE Trans. Electron Devices*, vol. 67, no. 6, pp. 2621–2626, Jun. 2020, doi: 10.1109/TED.2020.2985115.

- [23] W. Zhao and Y. Cao. (2008). Predictive Technology Model (PTM). [Online]. Available: http://ptm.asu.edu