# Localized Self-Assembly of InAs Nanowire Arrays on Reusable Si Substrates for Substrate-Free Optoelectronics

Alireza Abrand, Mohadeseh A. Baboli, Anastasiia Fedorenko, Stephen J. Polly, Evan Manfreda-Schulz, Seth M. Hubbard, and Parsian K. Mohseni\*

Cite This: *ACS Appl. Nano Mater.* 2022, 5, 840–851

Read Online

ACCESS |

Metrics & More

Article Recommendations

Supporting Information

**ABSTRACT:** We present a low-cost and scalable approach for the synthesis of wafer-scale InAs nanowire (NW) arrays on photolithographically patterned, reusable Si wafers using a localized self-assembly (LSA) epitaxial growth technique. Conventional *i*-line lithography is used to define arrays of 500 nm diameter pores through 50 nm thick SiO<sub>2</sub> layers, which serve as the LSA mask. A two-step, flowrate-modulated growth sequence is implemented to optimize selective-area self-assembly of NW arrays with over 80% yield and excellent control over the placement of one NW, with a mean diameter of 130 nm, inside each 500 nm pore. As-grown NW arrays are delaminated from the growth substrate, enabling fabrication of flexible membrane devices as well as reuse of Si wafers and growth masks while preserving the template pattern fidelity. Reuse of Si substrates for III–V epitaxy is demonstrated with and without pre-growth substrate restoration treatments. In both cases, the yield of NWs on reused wafers is comparable to that achieved in the original growth run. Without substrate restoration procedures, the remnant base segments of NWs on parent wafers act as preferential sites for regrowth of vertical NWs. Transmission electron microscopy analysis reveals that the InAs lattice is coherently extended from the remnant NW base segments during regrowth. The delaminated InAs NW arrays are transferred to carrier wafers for the fabrication of substrate-free photodetectors through the use of an anchoring procedure, which preserves the original NW position and orientation. Under broadband illumination, the NW array-based photodetectors produce a photo-to-dark current ratio of 10<sup>2</sup>, demonstrating the utility of the fabrication procedure employed. This work establishes a low-cost route toward III–V semiconductor-based flexible optoelectronics via LSA epitaxial growth of NW arrays on reusable Si wafers.

**KEYWORDS:** InAs nanowires, localized self-assembly, regrowth, substrate reuse, photodetectors

## INTRODUCTION

Semiconductor nanowires (NWs) have received great interest for optoelectronic applications due to their unique properties, as well as their controllable epitaxial growth and *in situ* doping.<sup>1–3</sup> In contrast to conventional thin-film geometries, a broad range of material compositions can be grown heteroepitaxially in the NW form due to efficient strain relaxation.<sup>4–6</sup> In particular, III–V semiconductor NWs are promising for photodetector applications. Using periodic arrays of coaxial NWs, the traditional tradeoff between external quantum efficiency and response speed can be overcome due to orthogonalization of the directions of photon absorption and carrier collection.<sup>7</sup> Photodetectors that utilize NW array device geometries also benefit from highly selective resonant absorption and tunable spectral range of operation.<sup>8–10</sup>

Growth of periodically arranged III–V NW arrays can be realized through various template-assisted epitaxial methods. One of the most common NW growth techniques is the Au-assisted vapor–liquid–solid (VLS) approach.<sup>11</sup> High growth rates, wide variability in dopant concentrations, and excellent

control over the NW crystal structure can be achieved using this growth mode.<sup>12–15</sup> However, the VLS approach faces several challenges, including (a) compositional phase segregation effects, particularly during growth of ternary alloys;<sup>16</sup> (b) undesired incorporation of Au atoms from the catalyst;<sup>17,18</sup> and (c) formation of graded junctions and compositionally smeared heterointerfaces due to the catalyst droplet reservoir effect.<sup>19,20</sup> Moreover, in some cases, Au nanoparticles must be selectively etched in order to better accommodate the growth of coaxial NW architectures or to mitigate optical reflection losses.<sup>21,22</sup> This introduces additional synthesis and processing complexity.

Received: October 23, 2021

Accepted: January 12, 2022

Published: January 20, 2022

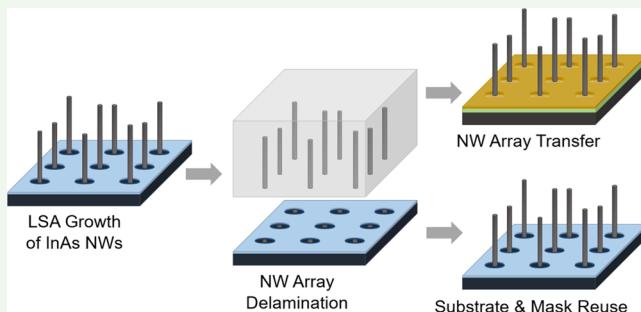

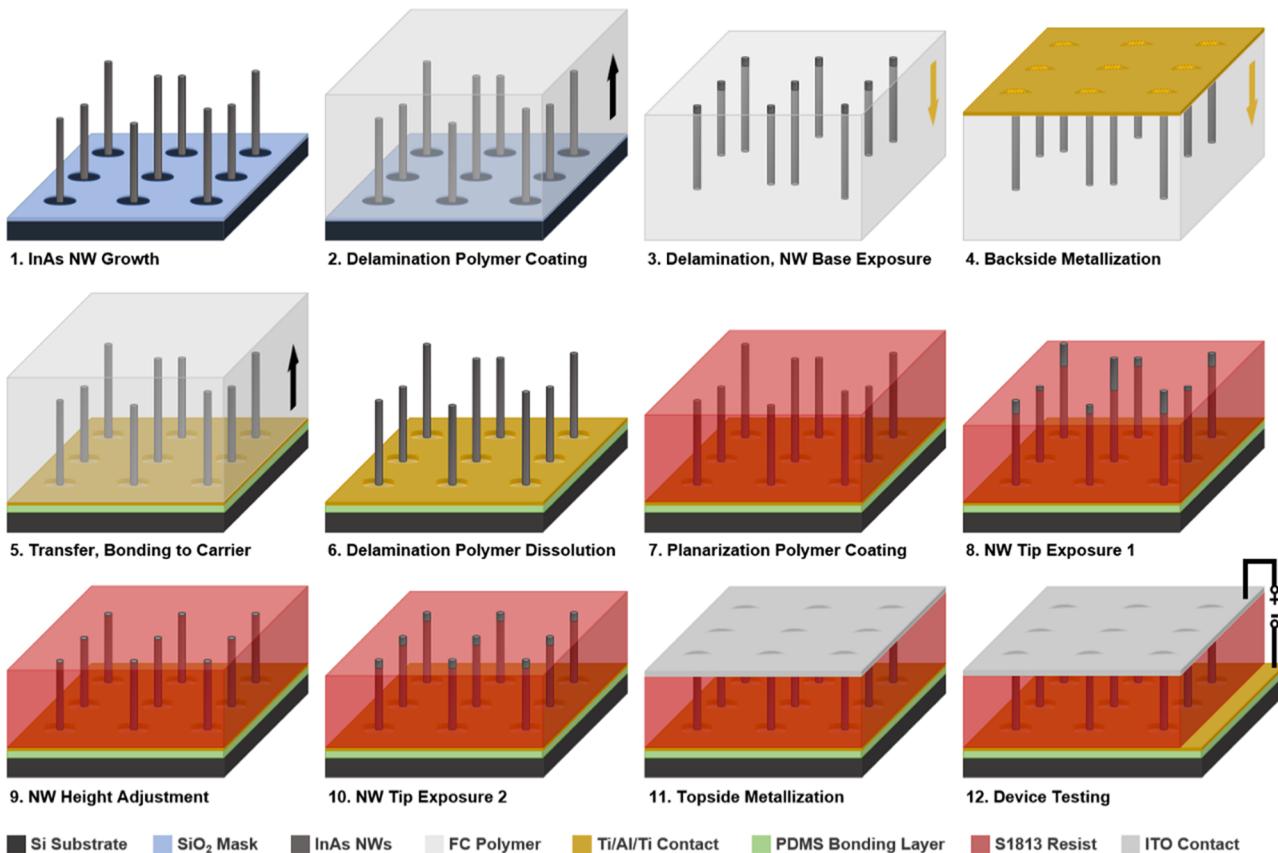

**Scheme 1. Schematic Representation of LSA Growth of an InAs NW Array on a Photolithography-Patterned Si Substrate Followed by NW Array Delamination and Transfer for Subsequent Device Fabrication and Substrate Reuse**

The above challenges can be either reduced or, at best, entirely overcome through the growth of NWs via selective-area epitaxy (SAE). The SAE growth mode enables several key advantages, including the ability to (a) grow complex core–shell heterostructures; (b) realize abrupt junctions and heterointerfaces; and (c) avoid the need for Au nanoparticle deposition and selective etching steps.<sup>23</sup>

Regardless of the growth mode, one of the main challenges for large-scale production of epitaxial III–V NW arrays is their synthesis cost.<sup>24,25</sup> Some synthesis costs are inevitable; these include, for example, the costs of instrumentation, operation, and precursor sources. However, other major cost contributions, such as those associated with the growth substrate, are largely reducible and can be separated into two categories (1) the cost of III–V wafers as the NW growth platform and (2) the lesser cost of pre-epitaxial processing of masking templates used for position-controlled synthesis of periodic NW arrays. Novel nanofabrication procedures that can overcome both cost streams are desired for large-scale implementation of III–V NW-based technologies.

Key substrate requirements for most applications include epitaxial guidance for the growth of vertically oriented NWs and the ability to serve as a robust carrier platform for handling during device fabrication. Low-cost foreign substrates such as Si(111) wafers fulfil both of these requirements, and they have been routinely used instead of bulk III–V wafers in order to considerably curtail the manufacturing costs.<sup>26–28</sup> However, site-specific NW synthesis still requires the patterning of masking templates on starting wafers, which presents an additional cost barrier. A possible strategy for simultaneously reducing pre-growth processing costs and complexity is to reuse Si substrates with existing predefined growth masks for site-selective and seed-free growth of III–V NW arrays. Such a process requires delamination of as-grown NWs from the “parent” Si substrate and transfer to alternative handling platforms for further device processing in order to accommodate substrate reuse and preservation of the original masking template. Moreover, Si substrates would need to be reused fewer times than III–V substrates for recovery of wafer costs.

For conventional SAE growth, masking templates are used to define the number density, position, and periodic arrangement of the NWs.<sup>23</sup> Growth templates are typically defined by first depositing a thin  $\text{SiO}_x$  or  $\text{SiN}_x$  layer on the substrate and subsequently patterning arrays of nanopores, which expose the substrate through the masking layer and serve as sites for preferential nucleation and NW crystal growth. The nanopore arrays can be defined using various lithography techniques, such as electron-beam lithography (EBL), nanoimprint

lithography (NIL), or nanosphere lithography (NSL), followed by either wet-etching or reactive-ion etching for substrate exposure inside the nanopores. Each of these lithographic approaches have their own limitations. For example, EBL is a costly and low-throughput approach, while NIL suffers from reproducibility challenges, and NSL faces limitations with respect to the formation of patterns with long-range periodic order.<sup>29,30</sup> Comparatively, conventional photolithographic patterning for the fabrication of nanoporous masking templates is preferred with respect to cost, reproducibility, throughput, long-range order, wafer-scale manufacturing, and compatibility with existing foundry processing lines. However, conventional photolithography is commonly prohibited for the synthesis of NWs due to the resolution limit.

Using a combination of the above strategies, in this paper, we establish a procedure for the low-cost and wafer-scale, selective-area self-assembly of III–V NWs with sub-lithographic dimensions on photolithographically patterned and reusable Si substrates. We present an optimized growth parameter space with respect to the yield and aspect ratio of InAs NWs synthesized under a seed-free growth mode, whereby the NWs self-assemble inside predefined nanopores without occupying the full extent of each growth site. We chose InAs as a model material system for demonstration of this approach for two main reasons. First, InAs serves as the binary basis for the growth of ternary III–V NW systems that enable tunability across a wide spectral range from short-wavelength infrared (using ternary  $\text{In}_x\text{Ga}_{1-x}\text{As}$ ) to long-wavelength infrared (using ternary  $\text{InAs}_y\text{Sb}_{1-y}$ ) for applications in photodetection. Second, the lattice mismatch between InAs and the underlying Si substrate is sufficiently high to accommodate localized NW growth under a strain-limited, self-assembly regime (additional details regarding the growth mechanism are discussed further below).<sup>31–36</sup> We provide a procedure for the delamination of as-grown NW arrays, which allows for Si substrates to be reused without additional patterning of masking templates between subsequent regrowth steps. We demonstrate the growth of NW arrays on recycled substrates with comparable aspect ratio and yield upon regrowth. We provide two approaches for substrate reuse, including with and without the introduction of intermediate substrate restoration procedures, and we discuss the merits of both approaches. In the absence of an intermediate restoration procedure, remnant NW base segments left below the delamination fracture plane serve as preferential growth sites in subsequent growth runs. We show that the vertically oriented InAs NW lattice is coherently extended along the axial growth direction during regrowth cycles. Lastly, we demonstrate a unique process flow for the fabrication of substrate-free

**Table 1. Summary of Relevant Growth Conditions and NW Details for all Samples**

| sample | pre-growth processing                      | substrate reuse | growth sequence | growth time (s) | TMIn ( $\mu\text{mol}/\text{min}$ ) | V/III | NW aspect ratio | single NW occupation yield (%) |

|--------|--------------------------------------------|-----------------|-----------------|-----------------|-------------------------------------|-------|-----------------|--------------------------------|

| A      | solvent cleaning, 5 s BOE                  | no              | growth step     | 1500            | 1                                   | 365   | 100 $\pm$ 12    | 31                             |

| B      | solvent cleaning, 5 s BOE                  | no              | nucleation step | 60              | 16                                  | 22.8  | 11 $\pm$ 5      | 68                             |

| C      | solvent cleaning, 5 s BOE                  | no              | growth step     | 1500            | 1                                   | 365   | 81              |                                |

|        |                                            |                 | nucleation step | 30              | 16                                  | 22.8  | 34 $\pm$ 9      |                                |

| D      | citric acid etch solvent cleaning, 5 s BOE | yes             | growth step     | 1500            | 1                                   | 365   | 75              |                                |

|        |                                            |                 | nucleation step | 30              | 16                                  | 22.8  | 38 $\pm$ 10     |                                |

| E      | solvent cleaning                           | yes             | growth step     | 1500            | 1                                   | 365   | 61 $\pm$ 11     | 80                             |

|        |                                            |                 | growth step     | 1500            | 1                                   | 365   |                 |                                |

NW-based infrared (IR) photodetectors that allows delaminated arrays to be transferred to foreign platforms while preserving the original position and orientation of the as-grown NWs. **Scheme 1** shows the overall process flow for NW array growth, delamination, and transfer as well as substrate reuse. The main focus of this work is the locally confined self-assembly of InAs NWs with sub-lithographic dimensions on photolithographically patterned Si wafers and the reuse of the parent wafers for subsequent III–V crystal growth runs without the need for intermediate processing steps prior to substrate reuse. This work enables the reduction of manufacturing cost of optoelectronic devices through selective-area self-assembly growth of III–V nanostructures on reusable Si substrates.

## EXPERIMENTAL DETAILS

**Substrate Patterning and NW Growth.** Si(111) wafers were used as the substrates for all crystal growth experiments. Masking templates were prepared by coating 150 mm “parent” Si wafers with 50 nm thick  $\text{SiO}_2$  films via plasma-enhanced chemical vapor deposition, followed by conventional *i*-line lithography using a ASML PAS 5500/200 stepper and reactive ion etching (RIE) using a AME PS000 instrument to obtain wafer-scale arrays of hexagonally arranged nanopores with 500 nm diameter and 1000 nm pitch. Next, vertically oriented InAs NW arrays were grown using a 3  $\times$  2” close-couple showerhead AIXTRON metalorganic chemical vapor deposition (MOCVD) reactor. Three distinct sets of growth conditions were investigated (henceforth, referred to as Samples A, B, and C) under different group-III precursor flowrates in order to optimize the NW yield and single NW per pore placement. Prior to loading in the MOCVD reactor, samples were rinsed with standard solvents and the native oxide of the Si substrate exposed through each pore was etched during a 5 s buffered-oxide etching (BOE) treatment. Trimethylindium [TMIn;  $\text{In}(\text{CH}_3)_3$ ] and arsine ( $\text{AsH}_3$ ) were used as gas-phase precursors for the supply of In and As growth species, respectively. All samples were first subjected to a 5 min annealing treatment at 850 °C under  $\text{AsH}_3$  flow in order to improve the growth yield, similar to what was reported to favor NW growth along the vertical ⟨111⟩ direction over other equivalent ⟨111⟩ directions.<sup>37,38</sup> Next, the reactor was cooled to a growth temperature of 700 °C. All temperature values reported here refer to the thermocouple-controlled reactor set-point value. The  $\text{AsH}_3$  flowrate and the chamber pressure were maintained at 365  $\mu\text{mol}/\text{min}$  and 100 mbar, respectively, for all growths. **Table 1** summarizes the key growth conditions for the various samples investigated in this study. Sample A growth was performed using a TMIn flowrate of 1  $\mu\text{mol}/\text{min}$  over a 25 min growth duration. A two-step, flowrate-modulated growth sequence was introduced for Samples B and C to increase the NW yield. In order to increase the number of nucleation sites, during the first growth step (i.e., the nucleation step), the substrate surface was flooded with a high TMIn flowrate of 16  $\mu\text{mol}/\text{min}$  for a period of 60 and 30 s for Samples B

and C, respectively. During the second step (i.e., the growth step), the TMIn flowrate was reduced to 1  $\mu\text{mol}/\text{min}$  for a period of 25 min.

**Delamination Procedure, Substrate Restoration, and Reuse.** For delamination of InAs NW arrays, the Colorless First Contact (CFC) polymer was applied to as-grown samples by drop-casting small volumes of the polymer solution. After drying under ambient conditions for  $\sim$ 24 h, the NW array-embedded membranes were mechanically delaminated from their native growth substrates through shear-induced fracture. After delamination, all substrates were treated with the First Contact Thinner solution to ensure the dissolution of residual CFC polymers on the surface. Then, two different methods were investigated for substrate reuse. In the first method, substrate restoration to the pre-growth state was investigated. In this case, substrates were treated with either a citric acid solution ( $\text{C}_6\text{H}_8\text{O}_7/\text{H}_2\text{O}_2$ , 20:1) solution or a piranha solution ( $\text{C}_2\text{SO}_4/\text{H}_2\text{O}_2$ , 3:1) for 5 min in order to selectively etch the InAs NW base segments that remained attached to the substrate in each pore (i.e., below the NW fracture plane). After rinsing with standard solvents and a pre-growth BOE treatment, the restored substrates (i.e., Sample D) were loaded in the MOCVD reactor for reuse and growth of second generation InAs NW arrays using a two-step growth sequence (i.e., same growth sequence as Sample C). In the second substrate reuse method, post-delamination wafers (i.e., Sample E) were simply rinsed with standard solvents and then directly reloaded in the MOCVD reactor for growth of second generation InAs NW arrays without intermediate substrate restoration steps to etch the remnant NW base segments formed during the initial growth cycle. Sample E NWs were grown under otherwise identical growth conditions as Sample A NWs.

**Transfer of NW Arrays and Device Fabrication.** To transfer the delaminated NW arrays for subsequent device fabrication, the backside surfaces of the exfoliated polymer membranes were subjected to an RIE process to expose  $\sim$ 150 nm along the base segments of the embedded NWs. Next, a trilayer stack of Ti/Al/Ti (25 nm/300 nm/25 nm) was sputtered on the backside of the membranes to serve as a backside contact and supportive medium to preserve the as-grown vertical orientation and original position of the NWs in the delaminated arrays. The membranes were then bonded to corona-treated Si carrier wafers using uncured PDMS as the bonding matrix, followed by a 3 h baking step at 60 °C. Next, the bonded membranes were submerged in the First Contact Thinner solution for 12 h to dissolve the delamination matrix. For device fabrication, a S1813 photoresist layer was spin-coated to encapsulate the transferred NW arrays and then thinned using an RIE treatment to expose the tip segments of the NWs. The samples were then submerged in a citric acid solution ( $\text{C}_6\text{H}_8\text{O}_7/\text{H}_2\text{O}_2$ , 20:1) for 30 s to selectively etch the exposed NW tip segments in order to generate a more homogeneous height profile for all NWs in the large-area arrays. The photoresist layer was again subjected to a short RIE step to expose the NW tip segments prior to sputter deposition of a 300 nm indium–tin–oxide (ITO) layer as a transparent conductive topside contact. Lastly, samples were annealed at 250 °C for 1 h.

**Materials Characterization and Device Measurements.** A Hitachi S-4000 scanning electron microscope (SEM) was used to image the morphology of as-grown NWs. A Bruker DI-3000 atomic

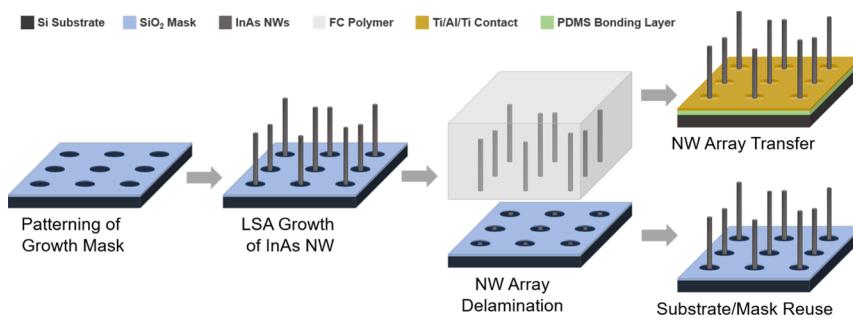

**Figure 1.** (a–e) 45° tilted-view SEM images of LSA-grown InAs NWs corresponding to Samples A–E presented in this work. (a) Sample A, grown in a one-step process without a separate nucleation step. (b) Sample B, grown using the two-step, flowrate-modulated sequence with a 60 s nucleation step. Arrows point to three examples of nanopores in which more than one NW are formed. (c) Sample C, grown using the two-step sequence with a 30 s nucleation step. (d) Sample D, grown on a reused Si substrate following a citric acid restoration procedure and BOE treatment. (e) Sample E, grown directly on a reused substrate after delamination of the parent NW array without an intermediate restoration procedure or BOE treatment (only solvent cleaning). All scale bars represent 2  $\mu$ m. (f) Measured values for total yield (light gray bars) and single NW occupation yield (dark gray bars), as well as the mean NW aspect ratio (blue data points; error bars represent  $\pm$  one standard deviation from the mean) for Samples A–E.

force microscope (AFM) was used in the intermittent contact mode for imaging and NW base segment height profilometry. A FEI Strata 400 STEM focused ion beam (FIB) was used for the preparation of lamellae for analytical transmission electron microscopy (TEM) experiments. The crystal structure of re-grown NWs was characterized using a FEI F20 high-resolution transmission electron microscope (HR-TEM). Energy-dispersive X-ray spectrometry (EDXS), acquisition of elemental maps and linescans, and collection of selected-area electron diffraction (SAED) patterns were performed using the same instrument. Electrical measurements were performed by probing the top and backside device contacts using a Keithley 2400 SourceMeter Unit (SMU). All electrical measurements were conducted at room temperature under dark and illuminated conditions. Broadband illumination (i.e., 350 to 2500 nm) was provided by a tungsten halogen source with power density of 57 mW/cm<sup>2</sup>.

## RESULTS AND DISCUSSION

Epitaxial growth of III–V NW arrays under the SAE regime is commonly carried out using oxide masking templates that are defined by EBL.<sup>39–41</sup> This technique provides excellent control over the position, growth rate, and, consequently, dimensions of the SAE NWs. However, EBL is also associated with high costs and prohibitively long processing times for wafer-scale template fabrication. To overcome these limitations, standard *i*-line photolithography is employed here to prepare oxide masking templates on 150 mm-diameter Si wafers.

The first objective of this work is to tune the MOCVD growth parameters in order to realize a high total yield of NWs with only single NW occupation per nanopore. Three different sets of growth conditions are investigated toward optimization of yield and aspect ratio of InAs NWs. The samples grown under these three sets of conditions are referred to as Samples

A, B, and C, as summarized in Table 1, and are described in the Experimental Details.

Figure 1 shows representative tilted-view SEM images obtained from as-grown Samples A–E. For each sample set, dimensional analysis is performed by measuring more than 100 NWs from different sample locations, while yield analysis is conducted based on the occupancy of more than 400 nanopores across four regions on each sample. Based on these measurements, the calculated mean NW aspect ratio (blue data points) and NW yield (gray bars) values for each of the three samples are presented in Figure 1f. The yield measurements are sub-categorized as the total yield, which is defined as the percentage of nanopores occupied by at least one vertical InAs NW (light gray bar), and as single NW occupation yield, which is defined as the percentage of nanopores occupied by exactly one vertical InAs NW (dark gray bar). For Sample A NWs, which are grown without a high flowrate nucleation step, a mean length of  $11320 \pm 1250$  nm and mean diameter of  $113 \pm 9$  nm is measured (errors represent one standard deviation from the mean). We note from Figure 1 that most NWs are grown near the peripheral pore regions. While the exact basis of this effect is currently unclear, we speculate that it may be related to the higher capture probability of stable nuclei, which preferentially form at the edge of the pores due to a greater supply of diffusive adatoms from the neighboring oxide field. Yield analysis reveals that 32% of all patterned nanopores are occupied by NWs, while only a negligible fraction of nanopores are occupied by two or more NWs, resulting in a measured single NW occupation yield of 31%.

To increase the number of occupied pores, a two-step sequence is introduced during the growth of Sample B NWs. First, the substrate is flooded with a high TMIn flowrate of 16  $\mu\text{mol}/\text{min}$  for 60 s in order to promote NW nucleation inside the exposed pores. Next, the TMIn flow is reduced to 1  $\mu\text{mol}/\text{min}$  for a period of 25 min in order to promote adatom surface migration, leading to axial extension of the InAs lattice at each nucleation site. Sample B NWs, shown in Figure 1b, exhibit a mean length of  $2216 \pm 548$  nm and a mean diameter of  $176 \pm 21$  nm. Use of the two-step growth sequence results in a total yield of 93%. However, a higher fraction of pores are occupied by more than one NW. The white arrows in Figure 1b point to the three examples of nanopores in which two NWs are formed. This effect results in a single NW occupation yield of only 68% in Sample B.

The undesired multiple NW occupancy effect is resolved in Sample C, simply by reducing the duration of the initial high-flowrate nucleation step from 60 to 30 s. A reduction in the number of nucleation sites and distribution of growth species amongst correspondingly fewer NWs lead to the formation of higher aspect ratio structures in comparison to Sample B. This is quantified by a mean length of  $4377 \pm 878$  nm and a mean diameter of  $132 \pm 17$  nm for Sample C NWs. Figure 1c shows an image of Sample C NWs, which exhibit a total yield of 82% and a single NW occupation yield of 81%, indicating that only a negligible fraction of the nanopores contain multiple NWs. The growth conditions of Sample C provide a suitable basis, with respect to the NW yield and aspect ratio, for additional Si wafer reuse and substrate-free device fabrication experiments. For all three samples, no parasitic crystal growth is observed on the oxide mask, which is one indication that growth may proceed under a selective-area regime.

During SAE growth, island nucleation occurs preferentially inside the patterned nanopores due to the large sticking coefficient differential between the masking layer (i.e.,  $\text{SiO}_2$ ) and the exposed substrate (i.e., Si). In the current work, the large lattice mismatch between InAs and Si (i.e.,  $\sim 11.6\%$ ) and the corresponding lattice strain lead to a high interfacial surface energy, which limits lateral expansion of nuclei inside the template pores. Thus, direct InAs island nucleation from the vapor phase becomes energetically favorable without wetting layer formation according the Volmer–Weber growth mode, which can proceed in the absence of metallic seeding agents.<sup>33,34</sup> Since the InAs islands are epitaxially registered to an atomically flat Si substrate with (111) surface orientation, crystal growth proceeds preferentially along the vertical  $\langle 111 \rangle$  direction of the InAs lattice.<sup>35</sup> Thus, vertical and free-standing NWs can be formed under a pseudo-Volmer–Weber regime.<sup>33,34</sup>

Due to the large pore size of 500 nm used here, strain-limited self-assembly results in NWs that do not fully occupy the exposed substrate area inside each pore.<sup>41</sup> This allows only coarse control over the exact position of NWs inside the template pores of relatively larger diameter and, under certain conditions, can lead to the formation of multiple NWs in a single pore. This is in contrast to the case of a more closely lattice-matched system, such as GaAsP on Si, for which the SAE-grown nanocrystals extend across the full area of the template nanopores under otherwise comparable SAE conditions (refer to Figure S1 of the Supporting Information document). For growth of InAs on Si, the fact that NW diameter is not strictly dictated by the template nanopore diameter also results in the formation of NWs with a range of

heights. The large standard deviation values associated with the aspect ratio data shown in Figure 1f illustrate this point.

These features distinguish the current approach from the conventional NW SAE growth mode, where NW diameters are commonly equal to or exceed the nanopore dimensions. We emphasize this distinction by referring to our growth mode as “localized self-assembly” (LSA). A similar description was recently adopted by Dubrovskii et al. for Ga-droplet assisted epitaxy of GaAs NWs on Si substrates through microscale pores of oxide masking layers.<sup>42</sup> We also note that Gao et al. have reported a dual growth regime wherein InP NW epitaxy can simultaneously proceed via both SAE and VLS regimes under the same growth conditions depending on NW diameter.<sup>43</sup> To investigate the possibility of In-droplet-mediated NW synthesis in the current work, we have carried out an additional growth under Sample C conditions, but in the absence of  $\text{AsH}_3$  flow during the cooling stage. Thus, NW growth was terminated by simultaneously stopping both group-III and group-V precursor flows. Here, no isolated In phase (i.e., seeding droplet) was observed at the NW tip, as determined by TEM and EDXS analysis (Figure S2). This is in contrast to the observation of In droplets at the tip of thinner InP NWs grown under otherwise SAE conditions reported by Gao and colleagues.<sup>43</sup> Given that our growth process precludes a group-III species pre-deposition step and that In droplets were not observed at the NW tip under  $\text{AsH}_3$ -free cooling conditions, we believe that the current LSA growth mode is more comparable to the seed-free SAE mechanism than localized VLS growth.

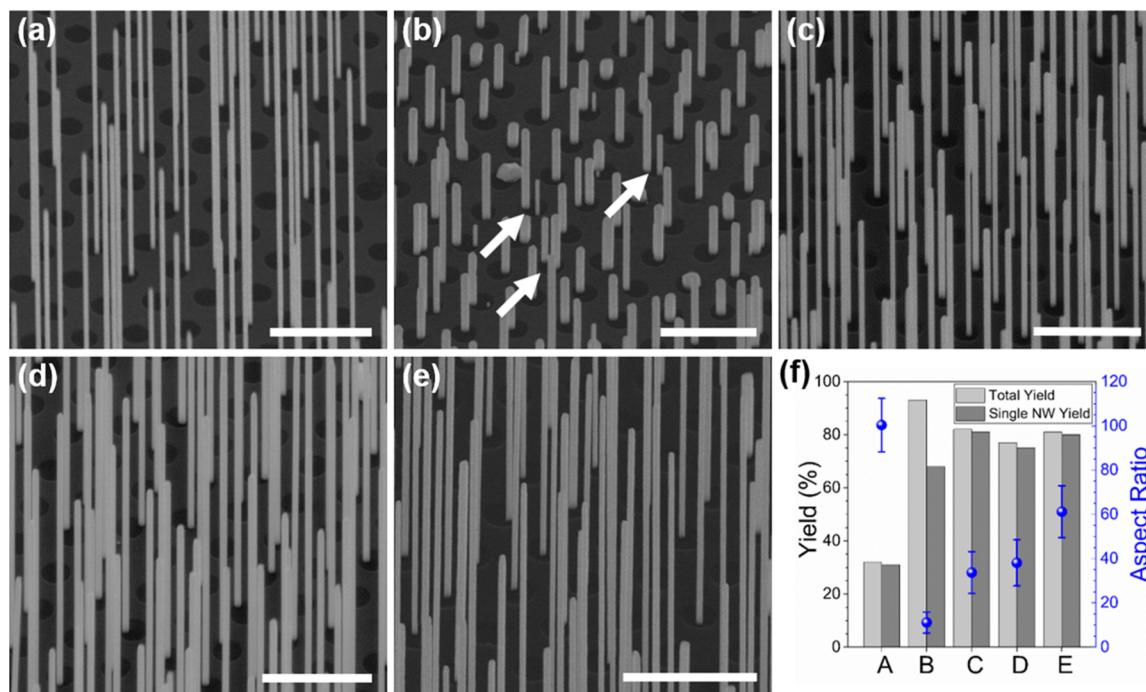

Before investigating the reuse of Si substrates for multiple III–V crystal growth runs, Sample C NW arrays are delaminated from the parent wafer. Figure 2a shows a representative image of the Sample C Si substrate and an oxide masking template immediately after the delamination step. After NW array peel-off, the oxide masking layer remains fully intact. However, short NW base segments are observed inside the pores, which reveal the fracture plane. Three examples of clearly identifiable remnant NW base segments are indicated by white arrows in Figure 2a.

The fracture surface profile and average height of the remnant base segments are measured using AFM. Figure 2b shows an AFM image of a representative nanopore in which a NW base segment is visible after the delamination step. The height profile of this base structure is shown in Figure 2c, which corresponds to the line segment spanning points A to B marked in Figure 2b. A graded fracture profile is observed and a base segment height of  $\sim 16$  nm is measured at its apex (i.e., maximum height relative to substrate surface baseline). Based on similar analysis of over 30 pores, a mean apex height of  $20.6 \pm 5.1$  nm is measured for the NW base segments after peel-off.

For Si substrate reuse investigations, two different strategies are employed. In the first approach, after NW array delamination, the substrates are restored to their pre-growth condition using a simple citric acid treatment to preferentially etch the InAs segments inside the template nanopores. For comparison, Figure S3a of the Supporting Information shows the surface of the parent Si wafer immediately after NW array delamination. As shown in Figure S3b, the citric acid treatment fully restores the Si substrate to its initial pre-growth state without damaging or unintentionally inducing porosity in the oxide masking template. An alternative substrate restoration procedure utilizing a piranha solution treatment is also described in the Supporting Information (Figure S3c).

**Figure 2.** (a)  $45^\circ$  tilted-view SEM images of the parent,  $\text{SiO}_2$ -templated growth substrate immediately after NW array delamination. The white arrows point to three examples of pores in which remnant NW base segments can be seen. Scale bar represents  $2\ \mu\text{m}$ . (b) AFM image collected in the tapping mode along a masking template nanopore after NW array peel-off, revealing a NW base segment inside the pore that was left behind below the NW's fracture plane. The hexagonal cross-section profile of the NW can be seen toward the left-hand side of the base segment. The color scale legend is normalized to the Si substrate surface baseline. (c) Corresponding AFM height profile measured across points A to B in (b).

In order to verify the feasibility of the restoration process as an intermediate step toward reuse of Si substrates with masking templates, the flowrate-modulated LSA sequence (i.e., under Sample C growth conditions) is performed on parent Si wafers after InAs NW array delamination and citric acid treatment. Figure 1d shows a representative SEM image of as-grown NWs on a restored and reused Si substrate, henceforth, referred to as Sample D. A mean length of  $5065 \pm 1244\ \text{nm}$  and a mean diameter of  $133 \pm 16\ \text{nm}$  are measured in the case of Sample D NWs. Total yield and single NW occupation yield values are measured to be 77 and 75%, respectively, on the reused substrates after the restoration treatment. Thus, similar NW dimensions and yield values are realized in the preliminary

growth run on parent substrates (Sample C) and in the secondary growth run on reused substrates (Sample D). Compared to the conventional substrate reuse methods for thin films that are intended to mitigate the high cost of III–V wafers, such as the epitaxial liftoff (ELO) technique,<sup>44</sup> the NW array delamination and wet chemical etching approach reported here offers the following advantages: (a) liberation of active device structures without the need for either growth or subsequent chemical etching of sacrificial release layers; (b) elimination of the additional processing steps, dedicated instrumentation, and high costs associated with chemomechanical polishing (CMP) procedures (we note that prior demonstration of an ELO procedure without use of CMP has also been presented by Cheng et al.<sup>45</sup>); and (c) replacement of starting III–V wafers with reusable Si substrates.

However, the substrate reuse approach described for Sample D has a critical drawback. Due to the formation of a native oxide layer inside the nanopores of the LSA making template after substrate restoration, a pre-growth BOE treatment is needed prior to loading the reused substrates in the growth reactor. This imposes a limit on the number of times each oxide-templated substrate can be reused due to continual dissolution of the masking layer, which has an etch rate of  $\sim 80\ \text{nm}/\text{min}$  in the BOE solution employed here.<sup>46</sup> We were able to reuse the patterned Si substrate three times when employing the intermediate citric acid treatment and BOE procedure before the  $\text{SiO}_2$  template was dissolved as a result of the pre-growth oxide etching step. One approach for extending the longevity of the masking layer is to use a silicon nitride template,<sup>47</sup> which allows a high etch rate selectivity of the native oxide over the LSA mask.<sup>48</sup> However, an even simpler alternative is adopted here. This alternative approach involves elimination of the substrate restoration procedure and pre-growth BOE step, such that parent Si wafers with masking templates and remnant NW base segments are reused after NW array delamination. Here, the remnant NW base segment inside each pore serves as a preferred growth site for direct extension of the InAs lattice along the substrate normal direction (i.e., axial NW growth direction). This approach potentially allows a greater number of substrate reuse cycles to be realized compared to a procedure that requires pre-growth wet etching of the substrate native oxide.

To investigate the potential for direct re-growth, Sample E substrates are loaded in the MOCVD reactor following the NW array delamination procedure and a solvent rinsing step. Since the template pores are occupied by remnant NW base segments that serve as preferential growth initiation sites, the nucleation step, which is necessary in the case of Samples B–D, is eliminated from the Sample E growth sequence. Figure 1e shows a representative tilted-view SEM image of as-grown Sample E NWs after growth on reused substrates with no restoration procedure. Vertical extension of the remnant base segments is realized, leading to the growth of NWs with a mean length of  $6285 \pm 1474\ \text{nm}$  and a mean diameter of  $99 \pm 11\ \text{nm}$ . Total NW yield and single NW occupation yield values of 81 and 80% are measured for Sample E, respectively, which match well with the yield values of the initial LSA growth run on parent substrates (i.e., Sample C). A comparison of the NW aspect ratio and yield data for Sample D (substrate reuse after citric acid restoration) and Sample E (substrate reuse without restoration) is shown in Figure 1f. In both substrate reuse approaches, the original pattern fidelity and NW verticality is preserved.

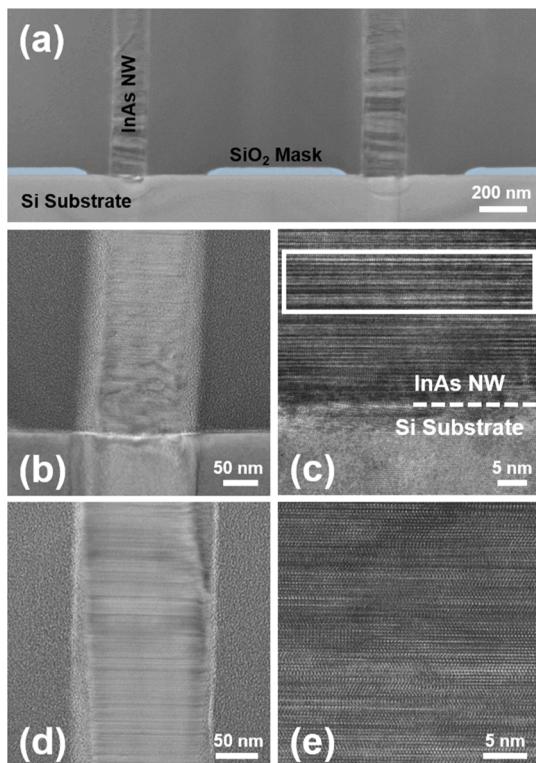

Next, the crystal structure of Sample E NWs that are extended from the remnant base segments on reused Si wafers is investigated using TEM. Emphasis is placed on inspecting the crystal structure along the NW base region about the anticipated delamination fracture plane. As noted above from AFM analysis, this region of interest is located  $\sim 20.6 \pm 5.1$  nm from the InAs/Si interface and serves as the location of InAs lattice extension during the regrowth sequence. Figure 3a

**Figure 3.** Bright-field TEM images of InAs NWs grown from remnant base segments on parent Si substrates, which were reused without restoration procedures. (a) Low-magnification bright-field image of two adjacent NWs. The oxide masking layer between NWs is false-colored in blue. (b) Bright-field TEM and (c) HR-TEM images collected at the InAs NW/Si substrate interface. The white box in (c) indicates the anticipated region of InAs lattice extension during the regrowth sequence. (d) Bright-field TEM and (e) HR-TEM images collected along a region approximately 500 nm above the NW/substrate interface.

shows a low-magnification, bright-field TEM image of two neighboring vertical InAs NWs on the reused substrate, where the  $\text{SiO}_2$  masking template is false-colored in blue. Figure 3b,c shows higher-magnification bright-field and HR-TEM images, respectively, collected along the reused substrate/InAs interface of the NW seen on the left-hand side of panel (a). In Figure 3c, the substrate interface is marked by a white dashed line, while the region corresponding to the anticipated delamination fracture plane (i.e., regrowth initiation region) is marked by a white border. Figure 3d,e shows bright-field and HR-TEM images, respectively, collected along a segment of the same NW that is located approximately 500 nm from the Si/InAs interface. Along the entire length of the NW, including the regions corresponding to the remnant base segment of the parent NW and the regions above the regrowth initiation plane, a mixed crystal structure consisting of a combination of zinc-blende and wurtzite phases is observed. Fast Fourier

transform (FFT) patterns generated from the lattice-resolved HR-TEM images are shown in Figure S4 of the *Supporting Information*. The coincident symmetries of the FFT patterns and comparable streaking along the growth direction confirm the mixed phase lattice arrangement that is common to both remnant base and regrowth segments. This polytypic crystal structure is characteristic of InAs NWs grown under both SAE<sup>49,50</sup> and self-assembly<sup>33,51</sup> growth modes on various substrates. Considering that the polytype crystal structure is commonly observed under the growth condition used in this work,<sup>37,51,52</sup> no additional lattice discontinuities, variations in the crystal structure, or extended defect phases are introduced as a result of the regrowth procedure. A higher magnification image and corresponding SAED pattern obtained at the interface between the regrown NW and reused substrate, along with elemental linescans and maps obtained using EDXS, are provided in Figure S4 of the *Supporting Information*.

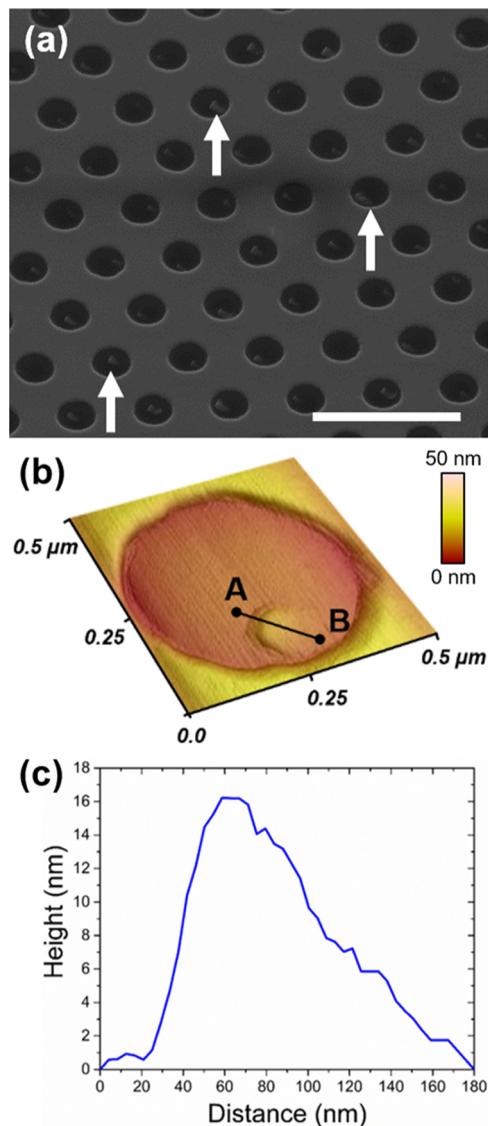

The NW array delamination and substrate reuse procedure is intended to enable the fabrication of substrate-free, III–V membranes for optoelectronic device applications, such as broadband photodetectors. Figure 4 shows the process flow utilized in the current work for NW array transfer and device fabrication, as described in the *Experimental Details*. The black and yellow arrows in Steps 2 to 5 represent the NW array when positioned in the upright (i.e., as-grown) and inverted orientations, respectively. In contrast to alternative fabrication approaches for NW-embedded flexible membrane devices that require device processing on the growth substrate,<sup>53</sup> the current approach allows the direct transfer of NW arrays to any foreign platform (e.g., carrier wafer, contact layer, etc.) while preserving the orientation and position of as-grown NWs during subsequent processing steps.

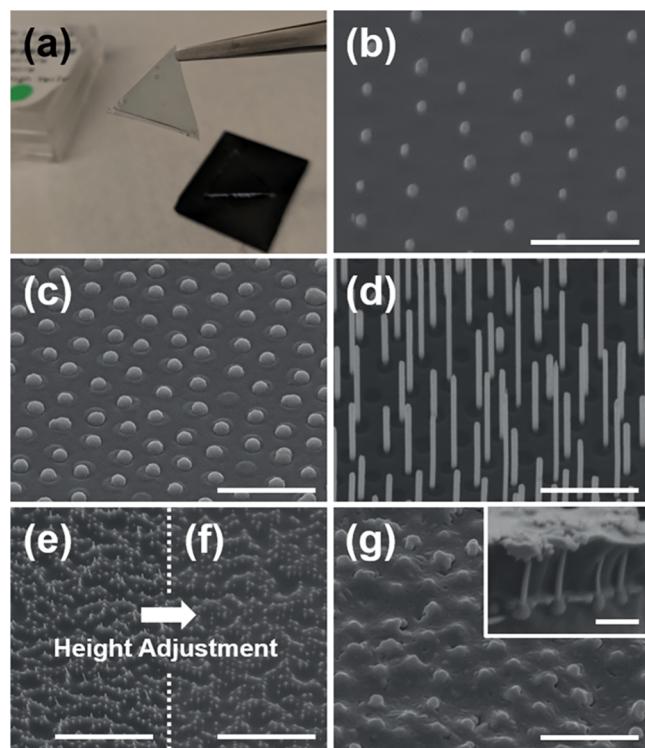

Figure 5a shows a photograph of a delaminated membrane containing a NW array that is embedded in the CFC polymer layer and held by a pair of tweezers. A tilted-view SEM image of the membrane's backside surface is shown in Figure 5b. The bases of the delaminated NWs are visible through the encapsulating polymer layer after an RIE step to expose NWs for contact deposition. In Figure 5c, the same backside surface is shown after deposition of a Ti/Al/Ti trilayer stack, which simultaneously serves as a reflective rear contact layer and a mechanical anchor. This anchoring medium preserves the original NW array spacing and orientation upon transfer to foreign carriers, and it ensures reliable fidelity of the original array geometry during subsequent processing steps. In Figure 5c, the contact points of the anchoring contact layer to individual NWs appear as hemispherical protrusion beyond the surface of the enclosing polymer matrix.

Since important optical properties of NW arrays, such as spectral range and wavelength-selective resonant absorption, can be engineered as a function of NW orientation, diameter, and pitch values,<sup>54–56</sup> maintaining NW verticality and array geometry during fabrication is critical. An image of an upright NW array, anchored by the backside contact stack, after dissolution of the encapsulating CFC membrane, is shown in Figure 5d; this corresponds to Step 6 of the process flow in Figure 4. As seen in the micrograph, successful transfer of the NW array is realized with a near-unity yield. After dissolution of the delamination polymer, the original orientation and relative position of each NW in the array is preserved. Alignment angle measurements collected after the CFC dissolution step show that approximately 90% of all transferred NWs are positioned within  $\pm 1^\circ$  of the vertical orientation,

**Figure 4.** Schematic diagram of NW array transfer and the device fabrication process: (1) LSA growth of NW arrays via MOCVD; (2) CFC polymer deposition (black arrow shows the as-grown, upright array orientation); (3) delamination of the NW-embedded polymer, followed by membrane inversion and RIE treatment to expose NW base segments (yellow arrow shows the inverted array orientation); (4) deposition of anchoring backside contact; (5) PDMS bonding of the NW-embedded membrane to carrier wafer for further device fabrication; (6) dissolution of the CFC polymer membrane, which results in NWs being transferred from their native growth substrate to a new carrier wafer with preserved position and vertical orientation; (7) coating and planarization of the S1813 resist layer; (8) RIE treatment to expose the NW tip segments to a common height of  $\sim 1.75 \mu\text{m}$ ; (9) wet-etching of exposed NW tips using citric acid solution for height adjustment; (10) RIE treatment to expose NW tip segments for top contacting; (11) ITO top contact deposition followed by annealing treatment; and (12) the final device structure and probing configuration.

while the remaining 10% of NWs are aligned within  $\pm 2^\circ$  of the vertical angle. Distributions of the angles of orientation of as-grown and transferred NWs are provided in the *Supporting Information* (Figure S5).

Several alternative NW array peel-off and substrate reuse approaches have been presented to date. Spurgeon et al. first demonstrated the delamination of Si NW arrays and reuse of a parent Si(111) substrate along with the porous oxide masking layer in 2008.<sup>46</sup> After mechanical separation, the authors selectively etched the remnant NW base segments inside the template nanopores prior to electrodeposition of Au inside the pores, which served as catalysts for Si NW regrowth via the VLS mechanism. Similarly, Cavalli et al. showed reuse of NIL-patterned InP(111) substrates through delamination of InP NW arrays using PDMS membranes. For substrate cleaning, diluted tetra-butyl-ammonium fluoride solution was used to remove the residual polymer followed by a dilute HCl treatment to remove the base part of the InP NWs.<sup>57</sup> More recently, Zhang et al. published an elegant approach for NW array peel-off. This involved spin-coating bilayers of S1818 and SU-8 polymers separated by Pd/Pt alloy films and double-exposure to selectively remove the S1818 layer at the base of the NWs, while leaving the remainder of the NWs embedded in the SU-8 layer.<sup>58</sup> The authors noted that these approaches

enabled array delamination due to the built-in stress within the SU-8 layer and reduced potential inhomogeneity at the NW feature plane. Jafari Jam et al. recently presented another practical method, which involved VLS growth of GaAs/AlAs/GaAs NWs through a patterned  $\text{SiN}_x$  porous template.<sup>59</sup> After growth, the NWs were embedded in a PDMS layer and mechanically fractured across the AlAs segment, which was subsequently selectively etched. Thus, the AlAs segment served as a sacrificial layer and generated a homogeneous surface for the underlying GaAs segment inside the pores of the masking template for selective re-electrodeposition of Au catalysts, enabling regrowth of NWs on the parent GaAs substrate. The NW array transfer and substrate reuse methods presented in the current work combines some of the strategic advantages of the recently demonstrated approaches, including (a) use of high-throughput and reproducible *i*-line photolithography to pattern oxide masking templates on 150 mm wafers; (b) absence of foreign seeding agents in exchange for a simplified LSA growth mechanism; (c) use of the CFC polymer as a delamination medium, which enables process simplicity by eliminating the need for polymer bilayer deposition and double-exposure; and (d) ease of dissolving the CFC polymer membrane while preserving the vertical NW orientation, which enables potential use in biomedical applications.<sup>60</sup> A

**Figure 5.** (a) Photograph of the InAs NW array membrane held with tweezers. 45° tilted-view SEM images obtained at various stages of the device fabrication process: (b) backside of the delaminated membrane after the RIE step to expose the NW base segments; (c) backside of the delaminated membrane after Ti/Al/Ti trilayer stack deposition (hemispherical features represent the location of NW base segments); (d) transferred, free-standing NW array on carrier wafer after backside PDMS bonding and CFC dissolution, showing that the original vertical orientation and positions of NWs are preserved; (e) S1813 polymer layer coating and planarization before height adjustment and (f) after citric acid treatment for height adjustment; and (g) topside of the NW membrane device after ITO top contact deposition. Inset shows a cross-sectional view of the fabricated device with 4 visible vertical NWs anchored in place by the backside contact (anchoring bulbs visible under each NW). Scale bars in (b–g) represent 3  $\mu\text{m}$ . Scale bar in the inset of (g) represents 1  $\mu\text{m}$ .

distinguishing aspect of the current work is that remnant NW base segments are exploited as preferential sites for NW regrowth on parent substrates, which avoids growth and selective etching of sacrificial NW segments as well as additional substrate restoration steps.

In comparison to the above approaches, however, the LSA growth mode utilized here has a notable disadvantage: The inhomogeneity in the length distribution of as-grown NWs presents a challenge for planarization and subsequent top contact deposition. During conventional SAE NW growth, the high degree of lateral confinement provided by the narrow-diameter template pores enables growth of NWs with uniform diameters and, therefore, more homogeneous length distributions. In contrast, during LSA of InAs on Si, the diameter of NWs is not strictly defined by the size of the larger template pores. Rather, the NW diameter and axial-to-radial growth rate ratio depend upon other parameters. These parameters include the lattice-mismatch between InAs and Si, the number of nearest neighbor NWs, the spacing of nanopores, and the epitaxial growth conditions. The wider distribution of NW

diameters resulting from LSA synthesis introduces NW length non-uniformities in the case of large-area arrays.

To normalize the NW height distribution and mitigate top contact deposition challenges, two planarization steps are introduced. After re-encapsulating the transferred NW array in a S1813 photoresist planarization medium (Figure 4, Step 7), an RIE procedure is used to expose ~90% of all NWs in the array, as shown in Figure 5e (corresponding to Figure 4, Step 8). At this stage, the embedded NWs are buried in the S1813 polymer to a common height of ~1.75  $\mu\text{m}$ . Next, a citric acid treatment is used to etch the excess length of the NWs exposed beyond the surface of the encapsulation medium (Figure 4, Step 9). This process effectively corrects NW length disparities over large areas and generates a more homogeneous array height. Lastly, a short RIE treatment is used to uniformly expose the top 150 nm of the NWs for ITO deposition, as shown in Figure 5f (corresponding to Figure 4, Step 10). Figure 5g shows the planarized top surface of the NW array after top contact deposition (corresponding to Figure 4, Step 11). The locations of individual NWs are visible through the ITO film. The inset of Figure 5g shows a cross-sectional view of the fabricated device, where four vertical NWs are seen that are partially embedded in the planarization medium and anchored in place by the backside trilayer contact. Each anchoring point can be seen as a bulb-like protrusion in the underlying PDMS bonding layer. Samples are subjected to a thermal annealing treatment prior to device testing to form Ohmic contacts, as well as to improve the transparency of the ITO film and reduce its sheet resistance.

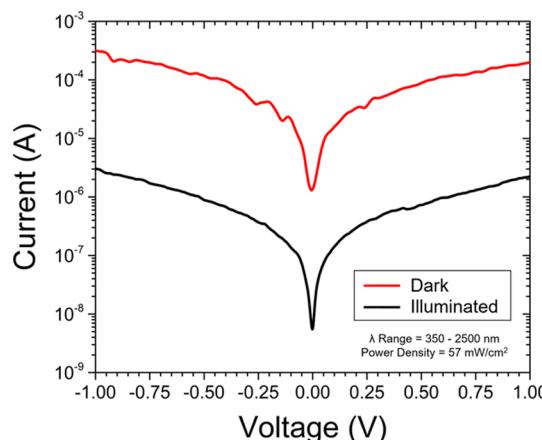

The photoresponse of the substrate-free, vertical InAs NW array-based metal–semiconductor–metal (MSM) photoconductors is measured at room-temperature by probing the top and backside contacts, as depicted in Step 12 in Figure 4.<sup>35,36,61</sup> A tungsten halogen lamp is used as the broadband source, which provides illumination over the 350 to 2000 nm wavelength range, with an incident power density of 57 mW/cm<sup>2</sup>. Figure 6 shows the semi-log current–voltage ( $I$ – $V$ ) characteristics of a representative NW array device under dark (black curve) and illuminated (red curve) conditions over the –1 to +1 V bias range. A reverse dark current of ~3  $\mu\text{A}$  is measured at –1 V. Upon illumination, the production of photogenerated carriers results in a clear current enhancement, characterized by a photocurrent of roughly 0.3 mA at –1 V.

**Figure 6.** Output characteristics of the substrate-free InAs NW array-based MSM photodetector under dark (black curve) and illuminated (red curve) conditions.

Thus, a room-temperature on/off current ratio ( $I_{ON}/I_{OFF}$ ) of approximately  $10^2$  is measured. The detected photoresponse validates the feasibility of the fabrication process described above. It also demonstrates that the delaminated NWs that are regrown on reused Si substrates are optically active and remain structurally stable during the transfer process. Using the substrate reuse and processing protocols established here, the performance and functionality of NW-based photodetectors can be improved in future works through implementation of several proven strategies, such as introduction of p-i-n junctions and heterojunctions during NW growth,<sup>62</sup> as well as modulation of NW diameter and array geometry for enhanced selective resonant absorption.<sup>10,63</sup>

While the LSA growth technique offers a series of practical advantages, it also has some notable limitations. The main drawbacks of the LSA method include (a) inherent inhomogeneity in diameter and length of as-grown NWs and sample-to-sample variability in NW dimensions; (b) limited control over the exact position of NWs inside wider nanopores, which leads to array aperiodicity; (c) strain-limited self-assembly requires a high degree of lattice mismatch between the substrate and epi-layer, which limits the number of materials combinations that can be synthesized under this growth mode; and (d) challenges associated with the growth of axial and coaxial NW heterostructures with equivalent geometries. However, the LSA growth mode enables heterogeneous epitaxy of vertical and high aspect ratio InAs NWs and micropillars with a wide range of tunable dimensions including diameters ranging from 100 nm to 1  $\mu\text{m}$  and lengths tunable from 0.1  $\mu\text{m}$  to greater than 10  $\mu\text{m}$ , using template pores varying from 0.5 to 4  $\mu\text{m}$  in diameter and array pitch values in the 1 to 10  $\mu\text{m}$  range (not shown here; to be reported in a separate publication).

## CONCLUSIONS

The LSA growth mode by MOCVD provides a low-cost path toward III-V NW array growth on large-area Si substrates. Scalable photolithography is employed for patterning of selective-area masking templates. The growth sequence uses flowrate modulation, which provides global NW yields exceeding 80% and allows control over the arrangement of only a single NW per template nanopore. As-grown InAs NW arrays are embedded in a polymer encapsulation medium, mechanically delaminated from the growth surface, and anchored by a metallic trilayer stack. The latter serves as a backside device contact layer and ensures that the original position and vertical orientation of the free-standing NWs are preserved upon transfer to foreign carrier wafers for device processing. Parent Si wafers and their masking templates are reused for subsequent LSA growth runs using two separated regrowth approaches. In the first approach, a citric acid (or a piranha solution) treatment is used to restore the parent substrates and nanoporous oxide masking layers to their pre-growth state. In an alternative approach, the original substrates, which contain short NW base segments that remain inside the template pores after delamination, are directly reused without introduction of intermediate substrate restoration steps. In this case, the remnant NW base segments act as preferential sites for the extension of the InAs lattice in the vertical direction. In both approaches, the original LSA masking template pattern fidelity is preserved upon substrate reuse and no parasitic nucleation is observed on the mask, consistent with crystal growth under a selective-area self-assembly regime. The

transferred InAs NW arrays are processed for proof-of-concept demonstration of substrate-free MSM photodetectors with  $I_{ON}/I_{OFF}$  ratios of  $10^2$  under broadband illumination. Future extensions of the current work include detailed characterization of the optical properties of delaminated InAs NW arrays of various dimensions in dissimilar encapsulating polymer media, analysis of the influence of anchoring backside contact layers on their optical properties, and detailed performance analysis of substrate-free membrane photodetectors fabricated using type-II heterojunction NWs. This work establishes the LSA growth mode as a feasible approach for the heteroepitaxial synthesis of large-area III-V NW arrays on oxide-templated Si wafers that can be reused without dedicated restoration between regrowth cycles for applications in substrate-free and flexible optoelectronic membrane devices.

## ASSOCIATED CONTENT

### Supporting Information

The Supporting Information is available free of charge at <https://pubs.acs.org/doi/10.1021/acsanm.1c03557>.

Comparison of InAs LSA and GaAsP SAE on Si; analysis of the NW tip structure and composition; description of citric acid and piranha surface treatment for substrate and masking template restoration; analytical TEM results of InAs NW growth on the reused Si substrate; and statistical analysis of the alignment angle of delaminated NWs (PDF)

## AUTHOR INFORMATION

### Corresponding Author

Parsian K. Mohseni – *Microsystems Engineering, Rochester Institute of Technology, Rochester, New York 14623, United States; NanoPower Research Laboratories and Department of Electrical and Microelectronic Engineering, Rochester Institute of Technology, Rochester, New York 14623, United States; [orcid.org/0000-0002-9377-7454](https://orcid.org/0000-0002-9377-7454); Email: [pkmohseni@rit.edu](mailto:pkmohseni@rit.edu)*

### Authors

Alireza Abran – *Microsystems Engineering, Rochester Institute of Technology, Rochester, New York 14623, United States; NanoPower Research Laboratories, Rochester Institute of Technology, Rochester, New York 14623, United States; [orcid.org/0000-0003-0912-1979](https://orcid.org/0000-0003-0912-1979)*

Mohadeseh A. Baboli – *Microsystems Engineering, Rochester Institute of Technology, Rochester, New York 14623, United States; NanoPower Research Laboratories, Rochester Institute of Technology, Rochester, New York 14623, United States*

Anastasiia Fedorenko – *Microsystems Engineering, Rochester Institute of Technology, Rochester, New York 14623, United States; NanoPower Research Laboratories, Rochester Institute of Technology, Rochester, New York 14623, United States*

Stephen J. Polly – *NanoPower Research Laboratories, Rochester Institute of Technology, Rochester, New York 14623, United States; [orcid.org/0000-0002-7563-6738](https://orcid.org/0000-0002-7563-6738)*

Evan Manfreda-Schulz – *Microsystems Engineering, Rochester Institute of Technology, Rochester, New York 14623, United States; School of Physics and Astronomy, Rochester Institute of Technology, Rochester, New York 14623, United States*

Seth M. Hubbard – *Microsystems Engineering, Rochester Institute of Technology, Rochester, New York 14623, United States; NanoPower Research Laboratories and School of*

Physics and Astronomy, Rochester Institute of Technology, Rochester, New York 14623, United States

Complete contact information is available at:

<https://pubs.acs.org/10.1021/acsanm.1c03557>

## Author Contributions

A.A. and P.K.M. conceived the research project and designed the experiments. A.A. and M.A.B. conducted sample preparation and epitaxial growth experiments. S.J.P. and E.-M.S. supported and assisted with growth experiments. A.A. carried out SEM imaging, sample processing, device fabrication, device testing, and related data analysis. A.F. performed AFM measurements. A.A. conducted analysis of AFM and analytical-TEM results. S.M.H. and P.K.M. supervised the research. All the authors discussed the results. A.A. and P.K.M. wrote the manuscript with the assistance of all the authors.

## Funding

This material is based upon work supported by the National Science Foundation under Award No. 1665086. This work made use of the Cornell Center for Materials Research Shared Facilities which are supported through the National Science Foundation MRSEC program (DMR-1719875).

## Notes

The authors declare no competing financial interest.

## ACKNOWLEDGMENTS

We gratefully acknowledge Salwan Omar for his assistance with MOCVD growths, as well as Malcom Thomas and John Grazul for their assistance with FIB sample preparation and analytical TEM characterization.

## REFERENCES

- (1) Logeeswaran, V. J.; Oh, J.; Nayak, A. P.; Katzenmeyer, A. M.; Gilchrist, K. H.; Grego, S.; Kobayashi, N. P.; Wang, S.; Talin, A. A.; Dhar, N. K.; Islam, M. S. A Perspective on Nanowire Photodetectors: Current Status, Future Challenges, and Opportunities. *IEEE J. Sel. Top. Quantum Electron.* **2011**, *17*, 1002–1032.

- (2) Tian, B.; Zheng, X.; Kempa, T. J.; Fang, Y.; Yu, N.; Yu, G.; Huang, J.; Lieber, C. M. Coaxial Silicon Nanowires as Solar Cells and Nanoelectronic Power Sources. *Nature* **2007**, *449*, 885–889.

- (3) Yan, R.; Gargas, D.; Yang, P. Nanowire Photonics. *Nat. Photonics* **2009**, *3*, 569–576.

- (4) Dasgupta, N. P.; Sun, J.; Liu, C.; Brittman, S.; Andrews, S. C.; Lim, J.; Gao, H.; Yan, R.; Yang, P. 25th Anniversary Article: Semiconductor Nanowires – Synthesis, Characterization, and Applications. *Adv. Mater.* **2014**, *26*, 2137–2184.

- (5) Björk, M. T.; Ohlsson, B. J.; Sass, T.; Persson, A. I.; Thelander, C.; Magnusson, M. H.; Deppert, K.; Wallenberg, L. R.; Samuelson, L. One-Dimensional Steeplechase for Electrons Realized. *Nano Lett.* **2002**, *2*, 87–89.

- (6) Kästner, G.; Gösele, U. Stress and Dislocations at Cross-Sectional Heterojunctions in a Cylindrical Nanowire. *Philos. Mag.* **2004**, *84*, 3803–3824.

- (7) LaPierre, R. R.; Robson, M.; Azizur-Rahman, K. M.; Kuyanov, P. A Review of III–V Nanowire Infrared Photodetectors and Sensors. *J. Phys. D: Appl. Phys.* **2017**, *50*, 123001.

- (8) Soci, C.; Zhang, A.; Bao, X.-Y.; Kim, H.; Lo, Y.; Wang, D. Nanowire Photodetectors. *J. Nanosci. Nanotechnol.* **2010**, *10*, 1430–1449.

- (9) Mokkapati, S.; Saxena, D.; Tan, H. H.; Jagadish, C. Optical Design of Nanowire Absorbers for Wavelength Selective Photodetectors. *Sci. Rep.* **2015**, *5*, 15339.

- (10) Azizur-Rahman, K. M.; LaPierre, R. R. Wavelength-Selective Absorptance in GaAs, InP and InAs Nanowire Arrays. *Nanotechnology* **2015**, *26*, 295202.

- (11) Wagner, R. S.; Ellis, W. C. Vapor-liquid-solid Mechanism of Single Crystal Growth. *Appl. Phys. Lett.* **1964**, *4*, 89–90.

- (12) Caroff, P.; Bolinsson, J.; Johansson, J. Crystal Phases in III–V Nanowires: From Random Toward Engineered Polytypism. *IEEE J. Sel. Top. Quantum Electron.* **2011**, *17*, 829–846.

- (13) Bolinsson, J.; Caroff, P.; Mandl, B.; Dick, K. A. Wurtzite–Zincblende Superlattices in InAs Nanowires Using a Supply Interruption Method. *Nanotechnology* **2011**, *22*, 265606.

- (14) Mohseni, P. K.; LaPierre, R. R. A Growth Interruption Technique for Stacking Fault-Free Nanowire Superlattices. *Nanotechnology* **2008**, *20*, 025610.

- (15) Dheeraj, D. L.; Patriarche, G.; Zhou, H.; Hoang, T. B.; Moses, A. F.; Grønsberg, S.; van Helvoort, A. T. J.; Fimland, B.-O.; Weman, H. Growth and Characterization of Wurtzite GaAs Nanowires with Defect-Free Zinc Blende GaAsSb Inserts. *Nano Lett.* **2008**, *8*, 4459–4463.

- (16) Guo, Y.-N.; Xu, H.-Y.; Auchterlonie, G. J.; Burgess, T.; Joyce, H. J.; Gao, Q.; Tan, H. H.; Jagadish, C.; Shu, H.-B.; Chen, X.-S.; Lu, W.; Kim, Y.; Zou, J. Phase Separation Induced by Au Catalysts in Ternary InGaAs Nanowires. *Nano Lett.* **2013**, *13*, 643–650.

- (17) Breuer, S.; Pfüller, C.; Flissikowski, T.; Brandt, O.; Grahn, H. T.; Geelhaar, L.; Riechert, H. Suitability of Au- and Self-Assisted GaAs Nanowires for Optoelectronic Applications. *Nano Lett.* **2011**, *11*, 1276–1279.

- (18) Allen, J. E.; Hemesath, E. R.; Perea, D. E.; Lensch-Falk, J. L.; Li, Z. Y.; Yin, F.; Gass, M. H.; Wang, P.; Bleloch, A. L.; Palmer, R. E.; Lauhon, L. J. High-Resolution Detection of Au Catalyst Atoms in Si Nanowires. *Nat. Nanotechnol.* **2008**, *3*, 168–173.

- (19) Dick, K. A.; Bolinsson, J.; Borg, B. M.; Johansson, J. Controlling the Abruptness of Axial Heterojunctions in III–V Nanowires: Beyond the Reservoir Effect. *Nano Lett.* **2012**, *12*, 3200–3206.

- (20) Dubrovskii, V. G.; Sibirev, N. V. Factors Influencing the Interfacial Abruptness in Axial III–V Nanowire Heterostructures. *Cryst. Growth Des.* **2016**, *16*, 2019–2023.

- (21) Anttu, N.; Dagtye, V.; Zeng, X.; Otnes, G.; Borgström, M. Absorption and Transmission of Light in III–V Nanowire Arrays for Tandem Solar Cell Applications. *Nanotechnology* **2017**, *28*, 205203.

- (22) Heurlin, M.; Hultin, O.; Storm, K.; Lindgren, D.; Borgström, M. T.; Samuelson, L. Synthesis of Doped InP Core–Shell Nanowires Evaluated Using Hall Effect Measurements. *Nano Lett.* **2014**, *14*, 749–753.

- (23) Tomioka, K.; Ikejiri, K.; Tanaka, T.; Motohisa, J.; Hara, S.; Hiruma, K.; Fukui, T. Selective-Area Growth of III-V Nanowires and Their Applications. *J. Mater. Res.* **2011**, *26*, 2127–2141.

- (24) Barrigón, E.; Hultin, O.; Lindgren, D.; Yadegari, F.; Magnusson, M. H.; Samuelson, L.; Johansson, L. I. M.; Björk, M. T. GaAs Nanowire pn-Junctions Produced by Low-Cost and High-Throughput Aerotaxy. *Nano Lett.* **2018**, *18*, 1088–1092.

- (25) Heurlin, M.; Magnusson, M. H.; Lindgren, D.; Ek, M.; Wallenberg, L. R.; Deppert, K.; Samuelson, L. Continuous Gas-Phase Synthesis of Nanowires with Tunable Properties. *Nature* **2012**, *492*, 90–94.

- (26) Mårtensson, T.; Svensson, C. P. T.; Wacaser, B. A.; Larsson, M. W.; Seifert, W.; Deppert, K.; Gustafsson, A.; Wallenberg, L. R.; Samuelson, L. Epitaxial III–V Nanowires on Silicon. *Nano Lett.* **2004**, *4*, 1987–1990.

- (27) Roest, A. L.; Verheijen, M. A.; Wunnicke, O.; Serafin, S.; Wondergem, H.; Bakkers, E. P. A. M. Position-Controlled Epitaxial III–V Nanowires on Silicon. *Nanotechnology* **2006**, *17*, S271–S275.

- (28) Mohseni, P. K.; Maunders, C.; Botton, G. A.; LaPierre, R. R. GaP/GaAsP/GaP Core–Multishell Nanowire Heterostructures on (111) Silicon. *Nanotechnology* **2007**, *18*, 445304.

- (29) Barbillon, G.; Hamouda, F.; Bartenlian, B. Large Surface Nanostructuring by Lithographic Techniques for Bioplasmonic Applications. *Manufacturing Nanostructures*; One Central Press, 2014; pp 244–262.

- (30) Hasan, R. M. M.; Luo, X. Promising Lithography Techniques for Next-Generation Logic Devices. *Nanomanuf. Metrol.* **2018**, *1*, 67–81.

- (31) Hertenberger, S.; Rudolph, D.; Bichler, M.; Finley, J. J.; Abstreiter, G.; Koblmüller, G. Growth Kinetics in Position-Controlled and Catalyst-Free InAs Nanowire Arrays on Si(111) Grown by Selective Area Molecular Beam Epitaxy. *J. Appl. Phys.* **2010**, *108*, 114316.

- (32) Koblmüller, G.; Hertenberger, S.; Vizbaras, K.; Bichler, M.; Bao, F.; Zhang, J.-P.; Abstreiter, G. Self-Induced Growth of Vertical Free-Standing InAs Nanowires on Si(111) by Molecular Beam Epitaxy. *Nanotechnology* **2010**, *21*, 365602.

- (33) Shin, J. C.; Kim, K. H.; Yu, K. J.; Hu, H.; Yin, L.; Ning, C.-Z.; Rogers, J. A.; Zuo, J.-M.; Li, X. In<sub>x</sub>Ga<sub>1-x</sub>As Nanowires on Silicon: One-Dimensional Heterogeneous Epitaxy, Bandgap Engineering, and Photovoltaics. *Nano Lett.* **2011**, *11*, 4831–4838.

- (34) Shin, J. C.; Lee, A.; Katal Mohseni, P.; Kim, D. Y.; Yu, L.; Kim, J. H.; Kim, H. J.; Choi, W. J.; Wasserman, D.; Choi, K. J.; Li, X. Wafer-Scale Production of Uniform InAs<sub>y</sub>P<sub>1-y</sub> Nanowire Array on Silicon for Heterogeneous Integration. *ACS Nano* **2013**, *7*, 5463–5471.

- (35) Wei, W.; Bao, X.-Y.; Soci, C.; Ding, Y.; Wang, Z.-L.; Wang, D. Direct Heteroepitaxy of Vertical InAs Nanowires on Si Substrates for Broad Band Photovoltaics and Photodetection. *Nano Lett.* **2009**, *9*, 2926–2934.

- (36) Jing, Y.; Bao, X.; Wei, W.; Li, C.; Sun, K.; Aplin, D. P. R.; Ding, Y.; Wang, Z.-L.; Bando, Y.; Wang, D. Catalyst-Free Heteroepitaxial MOCVD Growth of InAs Nanowires on Si Substrates. *J. Phys. Chem. C* **2014**, *118*, 1696–1705.

- (37) Tomioka, K.; Motohisa, J.; Hara, S.; Fukui, T. Control of InAs Nanowire Growth Directions on Si. *Nano Lett.* **2008**, *8*, 3475–3480.

- (38) Tomioka, K.; Tanaka, T.; Hara, S.; Hiruma, K.; Fukui, T. III–V Nanowires on Si Substrate: Selective-Area Growth and Device Applications. *IEEE J. Sel. Top. Quantum Electron.* **2011**, *17*, 1112–1129.

- (39) Chiba, K.; Yoshida, A.; Tomioka, K.; Motohisa, J. Vertical InGaAs Nanowire Array Photodiodes on Si. *ACS Photonics* **2019**, *6*, 260–264.

- (40) Farrell, A. C.; Lee, W.-J.; Senanayake, P.; Haddad, M. A.; Prikhodko, S. V.; Huffaker, D. L. High-Quality InAsSb Nanowires Grown by Catalyst-Free Selective-Area Metal–Organic Chemical Vapor Deposition. *Nano Lett.* **2015**, *15*, 6614–6619.

- (41) Björk, M. T.; Schmid, H.; Breslin, C. M.; Gignac, L.; Riel, H. InAs Nanowire Growth on Oxide-Masked {111} Silicon. *J. Cryst. Growth* **2012**, *344*, 31–37.

- (42) Dubrovskii, V. G.; Kim, W.; Piazza, V.; Güniat, L.; Fontcuberta i Morral, A. Simultaneous Selective Area Growth of Wurtzite and Zincblende Self-Catalyzed GaAs Nanowires on Silicon. *Nano Lett.* **2021**, *21*, 3139–3145.

- (43) Gao, Q.; Dubrovskii, V. G.; Caroff, P.; Wong-Leung, J.; Li, L.; Guo, Y.; Fu, L.; Tan, H. H.; Jagadish, C. Simultaneous Selective-Area and Vapor–Liquid–Solid Growth of InP Nanowire Arrays. *Nano Lett.* **2016**, *16*, 4361–4367.

- (44) Ward, J. S.; Remo, T.; Horowitz, K.; Woodhouse, M.; Sopori, B.; VanSant, K.; Basore, P. Techno-Economic Analysis of Three Different Substrate Removal and Reuse Strategies for III-V Solar Cells. *Prog. Photovolt. Res. Appl.* **2016**, *24*, 1284–1292.

- (45) Cheng, C.-W.; Shiu, K.-T.; Li, N.; Han, S.-J.; Shi, L.; Sadana, D. K. Epitaxial Lift-off Process for Gallium Arsenide Substrate Reuse and Flexible Electronics. *Nat. Commun.* **2013**, *4*, 1577.

- (46) Spurgeon, J. M.; Plass, K. E.; Kayes, B. M.; Brunschwig, B. S.; Atwater, H. A.; Lewis, N. S. Repeated Epitaxial Growth and Transfer of Arrays of Patterned, Vertically Aligned, Crystalline Si Wires from a Single Si(111) Substrate. *Appl. Phys. Lett.* **2008**, *93*, 032112.

- (47) Brubaker, M. D.; Genter, K. L.; Roshko, A.; Blanchard, P. T.; Spann, B. T.; Harvey, T. E.; Bertness, K. A. UV LEDs Based on p–i–n Core–Shell AlGaN/GaN Nanowire Heterostructures Grown by N-Polar Selective Area Epitaxy. *Nanotechnology* **2019**, *30*, 234001.

- (48) Williams, K. R.; Gupta, K.; Wasilik, M. Etch Rates for Micromachining Processing-Part II. *J. Microelectromech. Syst.* **2003**, *12*, 761–778.

- (49) Liu, Z.; Merckling, C.; Rooyackers, R.; Richard, O.; Bender, H.; Mols, Y.; Vila, M.; Rubio-Zuazo, J.; Castro, G. R.; Collaert, N.; Thean, A.; Vandervorst, W.; Heyns, M. Correlation between Surface Reconstruction and Polytypism in InAs Nanowire Selective Area Epitaxy. *Phys. Rev. Mater.* **2017**, *1*, 074603.

- (50) Tomioka, K.; Izhizaka, F.; Fukui, T. Selective-Area Growth of InAs Nanowires on Ge and Vertical Transistor Application. *Nano Lett.* **2015**, *15*, 7253–7257.

- (51) Baboli, M. A.; Slocum, M. A.; Kum, H.; Wilhelm, T. S.; Polly, S. J.; Hubbard, S. M.; Mohseni, P. K. Improving Pseudo-van der Waals Epitaxy of Self-Assembled InAs Nanowires on Graphene via MOCVD Parameter Space Mapping. *CrystEngComm* **2019**, *21*, 602–615.

- (52) Baboli, M. A.; Abrand, A.; Burke, R. A.; Fedorenko, A.; Wilhelm, T. S.; Polly, S. J.; Dubey, M.; Hubbard, M.; Mohseni, K. Mixed-Dimensional InAs Nanowire on Layered Molybdenum Disulfide Heterostructures via Selective-Area van Der Waals Epitaxy. *Nanoscale Adv.* **2021**, *3*, 2802–2811.

- (53) Seo, J.-H.; Swinnich, E.; Zhang, Y.-Y.; Kim, M. Low Dimensional Freestanding Semiconductors for Flexible Optoelectronics: Materials, Synthesis, Process, and Applications. *Mater. Res. Lett.* **2020**, *8*, 123–144.

- (54) Anttu, N.; Xu, H. Q. Efficient Light Management in Vertical Nanowire Arrays for Photovoltaics. *Opt. Express* **2013**, *21*, A558–A575.

- (55) Wang, B.; Leu, P. W. Tunable and Selective Resonant Absorption in Vertical Nanowires. *Opt. Lett.* **2012**, *37*, 3756.

- (56) Aghaeipour, M.; Anttu, N.; Nylund, G.; Samuelson, L.; Lehmann, S.; Pistol, M.-E. Tunable Absorption Resonances in the Ultraviolet for InP Nanowire Arrays. *Opt. Express* **2014**, *22*, 29204–29212.

- (57) Cavalli, A.; Dijkstra, A.; Haverkort, J. E. M.; Bakkers, E. P. A. M. Nanowire Polymer Transfer for Enhanced Solar Cell Performance and Lower Cost. *Nano-Struct. Nano-Objects* **2018**, *16*, 59–62.

- (58) Zhang, Y.; Hrachowina, L.; Barrigón, E.; Åberg, I.; Borgström, M. Self-Limiting Polymer Exposure for Vertical Processing of Semiconductor Nanowire-Based Flexible Electronics. *ACS Appl. Nano Mater.* **2020**, *3*, 7743–7749.

- (59) Jafari Jam, R.; Beech, J. P.; Zeng, X.; Johansson, J.; Samuelson, L.; Pettersson, H.; Borgström, M. T. Embedded Sacrificial AlAs Segments in GaAs Nanowires for Substrate Reuse. *Nanotechnology* **2020**, *31*, 204002.

- (60) Li, X.; Mo, J.; Fang, J.; Xu, D.; Yang, C.; Zhang, M.; Li, H.; Xie, X.; Hu, N.; Liu, F. Vertical Nanowire Array-Based Biosensors: Device Design Strategies and Biomedical Applications. *J. Mater. Chem. B* **2020**, *8*, 7609–7632.

- (61) Mallorquí, A. D.; Alarcón-Lladó, E.; Russo-Averchi, E.; Tütüncüoglu, G.; Matteini, F.; Rüffer, D.; Morral, A. F. i. Characterization and Analysis of InAs/p–Si Heterojunction Nanowire-Based Solar Cell. *J. Phys. D: Appl. Phys.* **2014**, *47*, 394017.

- (62) Thompson, M. D.; Alhodaib, A.; Craig, A. P.; Robson, A.; Aziz, A.; Krier, A.; Svensson, J.; Wernersson, L.-E.; Sanchez, A. M.; Marshall, A. R. J. Low Leakage-Current InAsSb Nanowire Photodetectors on Silicon. *Nano Lett.* **2016**, *16*, 182–187.

- (63) Wu, P. M.; Anttu, N.; Xu, H. Q.; Samuelson, L.; Pistol, M.-E. Colorful InAs Nanowire Arrays: From Strong to Weak Absorption with Geometrical Tuning. *Nano Lett.* **2012**, *12*, 1990–1995.