# 1200 V/650 V/160 A SiC+Si IGBT 3L Hybrid T-Type NPC Power Module With Enhanced EMI Shielding

Asif Imran Emon<sup>✉</sup>, Zhao Yuan<sup>✉</sup>, Abdul Basit Mirza<sup>✉</sup>, Amol Deshpande<sup>✉</sup>, Mustafeez Ul Hassan, and Fang Luo<sup>✉</sup>

**Abstract**—Three-level (3L) inverters suffer from higher parasitic inductance due to the increased number of series-connected switches in a single current commutation loop (CCL) results in a larger size of CCL compared to their two-level (2L) counterparts. As such, semiconductors are subjected to higher voltage stress and severe ringing at the switching transient. While silicon carbide's (SiC) faster switching speed improves overall efficiency by reducing switching loss, the faster voltage, and current gradient ( $dv/dt$  and  $di/dt$ ) generate electromagnetic interference (EMI) noise, requiring a larger and complicated filter stage design. To solve this problem, an optimized 3L T-type neutral point clamped power module has been proposed with a hybrid combination of the switch (SiC MOSFET + Si IGBT) rated for 1200 V/160 A. Two direct bonded copper (DBC) substrates have been stacked to have a vertical power loop using laser-drilled vias, which provides low commutation loop inductance as low as 4.6 nH for the major CCLs including the wire bond. Other associated CCLs have also been identified and optimized. Additional DBC in the package will be acting as an EMI shield. The EMI noise has been compared to a traditional power module and a 21 dB reduction of common-mode noise has been observed.

**Index Terms**—Electromagnetic interference (EMI) shielding, hybrid power module, Three-level (3L) T-type neutral point clamped (NPC).

## I. INTRODUCTION

THREE-LEVEL (3L), T-type neutral point clamped (NPC) topology is getting attention in renewable energy generation application, high-speed motor drives, and hybrid turboelectric aircraft propulsion system [1]–[3]. 3L converters are more desirable than 2L converters as they come with higher

Manuscript received November 29, 2020; revised March 3, 2021 and April 29, 2021; accepted June 8, 2021. Date of publication June 16, 2021; date of current version August 16, 2021. This work was supported by the National Science Foundation under Grant 1846917. Recommended for publication by Associate Editor M. Shen. (*Corresponding author: Asif Imran Emon.*)

Asif Imran Emon, Abdul Basit Mirza, and Fang Luo are with the Department of Electrical and Computer Engineering, Stony Brook University, Stony Brook, NY 11794 USA (e-mail: asifimran.emon@stonybrook.edu; abdulbasit.mirza@stonybrook.edu; fang.luo@stonybrook.edu).

Zhao Yuan is with the ELEG, University of Arkansas Fayetteville, Fayetteville, AR 72701 USA (e-mail: zhaoyuan@uark.edu).

Amol Deshpande is with the Department of Electrical Engineering, University of Arkansas Fayetteville, Fayetteville, AR 72701 USA (e-mail: ardeshp@uark.edu).

Mustafeez Ul Hassan is with the Stony Brook University, Stony Brook, NY 11794 USA (e-mail: mustafeez.hassan@stonybrook.edu).

Color versions of one or more figures in this article are available at <https://doi.org/10.1109/TPEL.2021.3089578>.

Digital Object Identifier 10.1109/TPEL.2021.3089578

converter efficiency, lesser voltage stress in device, lower total harmonic distortion, resulting in lower total harmonic machine loss and reduced input and output filter requirement [4]. Moreover, it has been shown in the literature that, 3L T-type NPC topology provides maximum efficiency and lower cost compared to other 3L topologies such as 3L NPC, 3L active NPC, and 3L flying capacitor topology in certain range of operating condition due to its low switch count, lesser number of isolated gate driver requirements, and simple operation principle [5], [6]. Due to improved material properties offered by wide bandgap (WBG) devices such as silicon carbide (SiC), lowering the dimension of die size and high-speed switching has become possible resulting in lower switching loss [7]. As the switching loss is optimized, the switching frequency can be pushed around hundreds of kHz. As SiC MOSFETs enable higher efficiency than Si IGBTs in power converters due to their fast switching ability, the overall increased efficiency of the inverter can be achieved [8]. However, the state-of-the-art die dimension and cost of the SiC is the bottleneck for high power application. To block higher voltage with tolerable leakage current, the length of the drift region of the transistors needs to be increased which incurs additional ON-state resistance. To achieve the capability of pumping high current through the transistor chip, the area of the die increases [9]. To address this issue, a hybrid switch, composed of SiC and Si IGBT by adjusting their gating sequence has been proposed [17] and the concept is demonstrated for T-type NPC topology. In this configuration, lower switching loss from SiC and lower conduction loss from IGBT can be achieved at the same time by soft switching the Si IGBT by controlling the gating sequence. However, due to the long tail current in IGBT during turn OFF, the hybrid switch is limited by the minimum duty cycle and maximum switching frequency constrain. Current ratio between Si and SiC also needs to be optimized to ensure the integrity of the hard switching SiC device. In addition to that, it involves system complexity in gate driver design and power loop optimization during the layout [10].

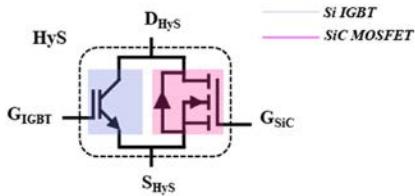

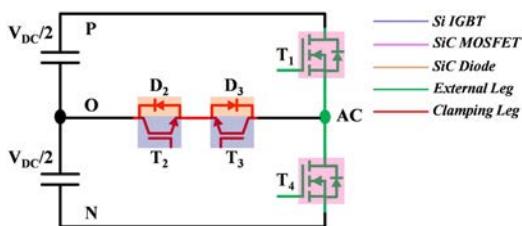

Hence, to reduce the system complexity, the hybrid switch concept is modified and a new switch combination comprises Si IGBT, SiC MOSFET Schottky diode is proposed as shown in Fig. 2. Si IGBTs with SiC Schottky diode constitute the clamping leg and SiC MOSFETs are placed in the half-bridge position. IGBT's in the clamping leg will be soft switching under the unity power factor; hence, the introduction of Si IGBT will not contribute to additional switching loss [11].

Fig. 1. Hybrid switch structure [9].

Fig. 2. Hybrid combination of the switch in T-type NPC topology.

Despite having the capacity to achieve faster switching speed, the layout of the power stage and device package itself impedes fully harnessing the advantage offered by the WBG devices due to the associated parasitics [12]–[14]. In high-speed switching transient, the device suffers from excessive voltage stress from voltage overshoot, which harms the reliability of the system and curtails overall lifetime [15]. Evaluation of the commutation loop in the particular topology and optimization of layout accordingly can reduce the parasitics and electromagnetic interference (EMI) noise despite using traditional packaging technology [16], [17]. P-cell, N-cell concept brought a substantial improvement in optimizing half-bridge phase leg topology, where switches constituting the commutation loop placed adjacent to each other to reduce the loop area [18]. Utilizing the same concept, Wang *et al.* introduced symmetrical power loop design using a “double-ended source” busbar structure [19] in a 15 kW multichip SiC module. It reduced the circulating current, and improved the dynamic current sharing among paralleled die in a two-dimensional (2-D) power loop on single direct bonded copper (DBC) substrate. To further reduce the loop inductance, hybrid-packaging structure (PCB+DBC or DBC+DBC) has been proposed [20], [21]. Semiconductor chips are attached in the DBC while the additional PCB constitutes a vertical or 3-D power loop. Vertical power loop enables mutual cancellation of magnetic flux and brings a substantial reduction in commutation loop inductance, reported as low as 3.3 nH. X. Lyu *et al.* demonstrated vertical power loop concept using a single DBC substrate achieving 1.1 nH. Through hole vias in the DBC substrate enabled the implementation of vertical power loop. To isolate the bottom copper from the heatsink, thermal interface material has been used which curtails the thermal performance of the module [22]. A similar concept has been demonstrated by Dutta *et al.* using multiple DBCs with spring-loaded interconnect in LTCC interposer [23].

All these reported works were done for packaging half-bridge phase leg only. Cree has its common source module, which

is widely used with their half-bridge phase leg to constitute 3L T-type NPC that involves a complex busbar design due to optimization of multiple loops and interaction between the loops through coupling [24], [25]. Here, in addition to the module parasitics, busbar inductance is also added to the power loop. The lowest 3L T-type NPC busbar inductance reported in the literature is 11 nH without including module inductance [26]. Hence, there is a demand of packaging the topology itself in single module.

In commercial space, Infineon, Onsemi, Semikron, Vincotech, and Microsemi have their individual T-type NPC module with 2-D power loop. Infineon’s T-type NPC module comes in “EconoPACK” and press-fit type “Easy 2B/1B” package [27]. Onsemi’s 1200 V rated T-type NPC IGBT module comes in their Q0 and Q2 pack with press-fit pins [28]. Semikrons has commercialized its 3L T-type NPC module in the “Semix5p” package for 1200 and 1700 V applications [29]. Microsemi has brought their 3L T-type NPC IGBT module in its press-fit “SP3F” package for 1200 V applications [30]. Vincotech’s T-type NPC module is rated for 600/1200 V application and packaged in their press-fit “Flow” package and PCB/DBC hybrid “X4” package [31]. All the reported packages from commercial space are the modification of their pre-existing half-bridge phase leg packages and the lowest loop inductance reported so far is 14 nH [27]. Hence, there is room for research in active integration of the T-type NPC topology in a single module with systematic analysis.

The concept of vertical commutation loop was reported for 2-L converters [20], [21]. In multilevel converter topology, the scenario is different. It is shown that with increased number of power loops, optimization of stray inductance and reduction of interaction among the loops become much more difficult than in 2L converters [26]. In 3L T-type NPC topology, we have five different loops that needs to be optimized simultaneously. The first contribution of this article is that the article proposes a systematic approach to optimize multiple commutation loops simultaneously also taking care of interaction between the loops, which is important for multilevel converters. The second contribution is that this approach introduces an integrated EMI shield to self-contain the common-mode (CM) EMI noise inside the module. Experiment shows a reduction of 21 dB CM noise by proposed scheme. The third contribution of this article is to present a systematic approach toward global optimization, where stray inductances and CM EMI from the module is reduced by a balanced trade-off with thermal resistance. This proposed design methodology of co-optimization of thermomechanical and electrical parameters by implementation of vertical power loop can be extended for other multilevel topologies.

The organization of the article is as follows. In Section II, the stray inductance optimization technique using vertical power loop is explained, and stacked-DBC-based module structure is introduced followed by the analysis of the associated power loops in 3L TNPC and their optimization in the proposed structure. Section III describes the fabrication steps, while in Section IV the switching result of the fabricated module is presented. In Section V, the EMI performance of the module is modeled, and finally validated by experimental results. The

Fig. 3. Mutual inductance cancellation.

thermal performance is discussed in Section VI with the simulation result and loss calculation process. Finally, the article has been concluded in Section VII by discussing the findings and scope of future research.

## II. LOW INDUCTIVE PACKAGE WITH STACKED DBC

### A. Mutual Inductance Cancellation in Vertical Loop

In the conventional packages with 2-D power loop, commutation loop inductance can be optimized by reducing the loop area. However, during the layout, the minimum spacing between the dies needed to be maintained to meet the insulation as well as thermal dissipation requirements.

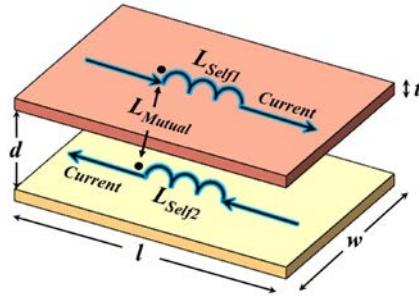

Moreover, total inductance also depends on the number of wire bonds employed per semiconductor die and the diameter of each wire. Selection of the bond number and gauge depends on the surface area of the chip and the total current to be handled. As such, the maximum achievable reduction of inductance by reducing the size of the power loop has a boundary in the conventional packages. To further reduce the parasitic inductance, the vertical power loop is one of the preferable options. This method can utilize the mutual inductance cancellation effect to reduce the parasitic inductance significantly, as shown in Fig. 3.

This technology has been adopted in the laminated busbar design and low inductance PCB design [34], [35]. Total power loop inductance can be expressed as

$$L_{\text{Total}} = L_{S1} + L_{S2} - 2L_M \quad (1)$$

where  $L_{S1}$  and  $L_{S2}$  are the self-inductances of top and bottom trace, respectively, and  $L_M$  is the mutual inductance in between them. Self-inductance depends on the width ( $w$ ), thickness ( $t$ ), and length ( $l$ ) of the trace, while the mutual inductance depends on one more variable; the distance between the two current carrying traces ( $d$ ). Self-inductance and mutual inductance can be calculated using the equation listed as follows:

$$L_S = 2l \left[ \ln \left( \frac{2l}{w+t} \right) + 0.5 + 0.2235 \left( \frac{w+t}{l} \right) \right] \quad (2)$$

$$L_M = \frac{\mu_0 l}{2\pi} \left[ \ln \left( \frac{l}{d} + \sqrt{1 + \left( \frac{l}{d} \right)^2} \right) - \sqrt{1 + \left( \frac{d}{l} \right)^2} + \frac{d}{l} \right] \quad (3)$$

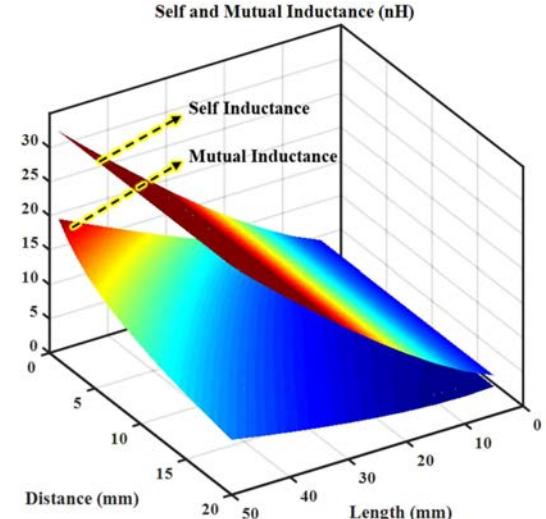

Fig. 4. Impacts of length and distance of traces on the inductance.

Effect of interlayer distance and trace length on the value of self and mutual inductance has been shown in Fig. 4. To maximize the reduction of inductance, interlayer distance and length of current-carrying trace should be minimized.

### B. Introduction to the Proposed Module Structure

The designed T-type NPC module consists of two DBCs made of aluminum nitride (AlN) substrate due to its high thermal conductivity compared to other choices. Beryllium oxide (BeO) based substrate has the best thermal conductivity (200–250 W/mK) and high dielectric constant, which makes it suitable to be used as the substrate. Nevertheless, it is unfeasible as the powder of BeO is extremely poisonous to human health. It produces toxic gas by the reaction between Cu, BeO, and O<sub>2</sub> at 1065°C –1085°C, which is needed to make copper on the BeO substrate. On the other hand, AlN's thermal conductivity is around 150–170 W/mK which is higher than other available ceramics such as Al<sub>2</sub>O<sub>3</sub> (20–30 W/mK) and Si<sub>3</sub>N<sub>4</sub> (60–70 W/mK), hence chosen as the material for DBC substrate.

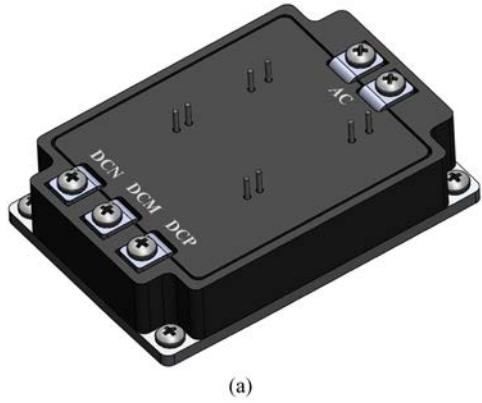

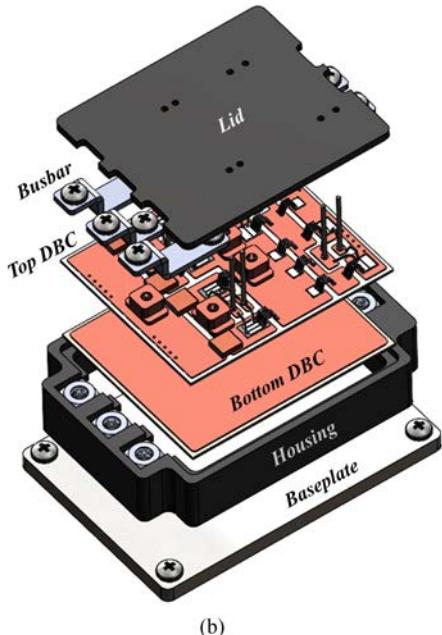

LASER drilled through hole vias on the top DBC makes the interconnection between two stacked substrates. The structure of the module with appropriate labels has been shown in Fig. 5. Input terminals and output terminals are placed in the opposite direction for the ease of installation of the module in system-level design. Protruding gate driver pins for four individual switching positions are located in the middle. In Fig. 6, the internal view of the module is revealed.

### C. Inductance Optimization for All Associated Power Loops

The switching states of a 3L T-type NPC topology can be defined as P, O, and N. States of switches and output is included in Table I.

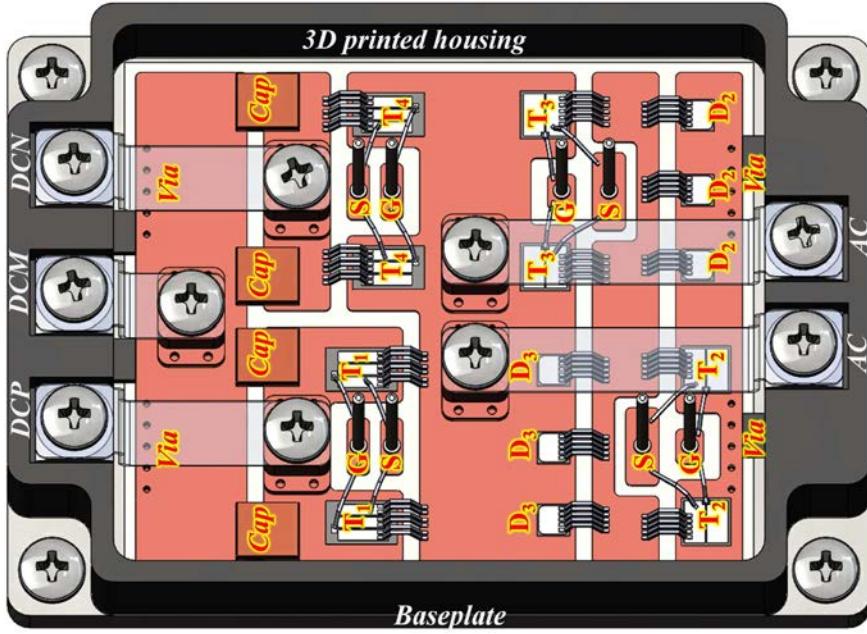

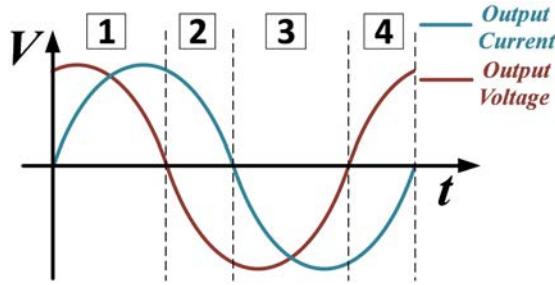

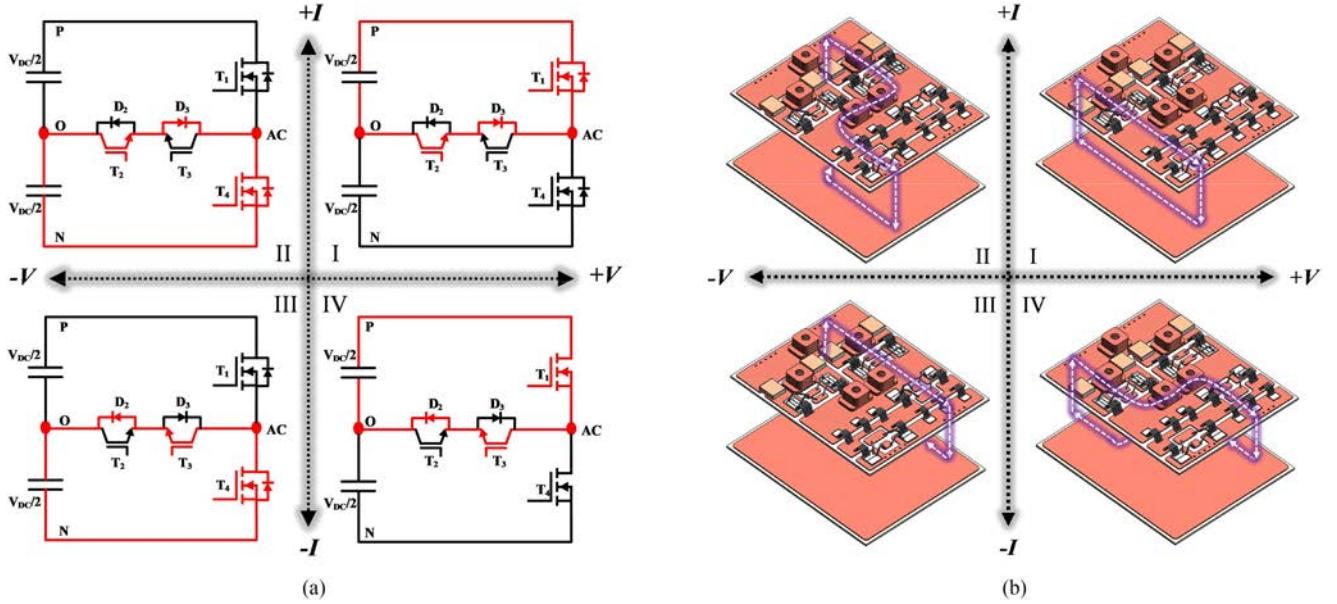

With real load when power factor is not unity, the overall operating region can be spaced in four quadrants as shown in Fig. 7 depending on the current and voltage polarity.

(a)

(b)

Fig. 5. Structure of the proposed module. (a) CAD drawing of the module. (b) Exploded view of the module.

TABLE I

SWITCHING STATES OF 3L T-TYPE NPC

| State | $V_{out}$   | $T_1$ | $T_2$ | $T_3$ | $T_4$ |

|-------|-------------|-------|-------|-------|-------|

| P     | $+V_{DC}/2$ | On    | on    | off   | off   |

| O     | 0           | Off   | on    | on    | off   |

| N     | $-V_{DC}/2$ | Off   | off   | on    | on    |

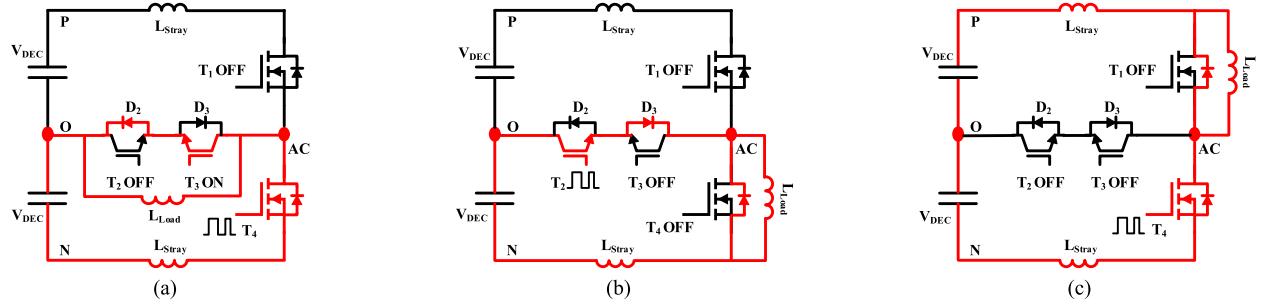

In each quadrant, 3L T-type NPC topology shows a unique commutation loop. During the transition between state P $\leftrightarrow$ O, when current is positive or coming out of the cell, switch position marked as  $T_1$ ,  $T_2$ , and  $D_3$  will constitute the commutation loop.  $T_1$  (SiC) will be hard switching and  $T_2$  (IGBT) will be soft switching. This commutation loop represents the first quadrant operation mode shown in Fig. 7. Similarly, for the transition of

TABLE II

EXTRACTED LOOP INDUCTANCES

| Inductance (nH) | Commutation Loops in 3L Operation |      |      |      | 2L Operation |

|-----------------|-----------------------------------|------|------|------|--------------|

|                 | CCL1                              | CCL2 | CCL3 | CCL4 |              |

| 4.6             | 4.93                              | 4.6  | 4.93 | 8.02 |              |

states O $\leftrightarrow$ N but current in negative direction or entering the cell, switch position  $T_4$  (SiC),  $T_3$  (IGBT), and  $D_2$  will constitute the power loop. This one represents the third quadrant operation mode. For unity, lagging or leading power factor, the peak current will appear between first and third quadrant and it is the most desirable operation mode as only SiC devices will be hard switching and IGBT's will be soft switching. Therefore, the power loops in first and third quadrant is given most importance in the layout. However, for the other two operation modes, IGBTs will be hard switching and the switching loss will be aggravated. Hence, from a layout point of view, irrespective of switching scheme, these loops need to be optimized with the same importance as well.

For the transition between states O $\leftrightarrow$ N and when current is positive or leaving out of the cell,  $T_4$ ,  $T_2$ , and  $D_3$  will constitute the power loop and this represents the second quadrant operation mode. During this mode of operation,  $T_2$  (IGBT) will be hard switched and majority of the switching loss will be coming from this switching position. On the other hand, during the transition of states P $\leftrightarrow$ O, but current in negative direction or entering into the cell this instance,  $T_1$ ,  $T_3$ , and  $D_2$  will constitute the commutation loop and it represents the fourth quadrant operation mode. In this configuration, the body diode of the  $T_1$  will be conducting and  $T_3$  (IGBT) will be hard switched. All these loops are shown in red in Fig. 8 along with their physical location in the module.

Again, the external loop between the switch  $T_1$  and  $T_4$  needs attention as well. For instance, when the transition is happening between O $\leftrightarrow$ N, and  $T_4$  is hard switched ON, the voltage stress across the  $T_1$  will be doubled. It would happen the same way for  $T_4$  during P $\leftrightarrow$ O transition when  $T_1$  is hard switched ON. Moreover, in light load condition to operate the module as a 2L inverter, current will commutate between  $T_1$  and  $T_4$ . Optimization of this loop is also done as shown in Fig. 9 and an overall optimized layout has been achieved finally.

After optimizing the loops, the stray inductances of individual loops have been extracted using Q3D including bonding wires. The result has been presented in Table II.

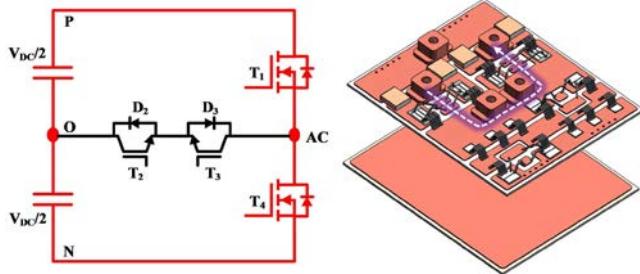

### III. FABRICATION OF THE MODULE

The fabrication process starts with the preparation of the two AlN DBCs. Using  $FeCl_3$  solution, DBCs are etched according to the layout. After that, top DBC is drilled using LASER. The inner wall of those holes is plated using thick plated copper process to make them conductive. Once the DBCs are ready, attachments and assembly process has been carried out. Two different kinds of solder paste with different melting temperature have been used during reflow soldering steps. A 3 mm thick nickel-plated copper baseplate is used as heat spreader at the bottom of the module.

Fig. 6. Internal layout of the module.

TABLE III

INFORMATION OF THE DIES USED

|            | Information of Selected Die |                 |                   |                   |                                  |

|------------|-----------------------------|-----------------|-------------------|-------------------|----------------------------------|

|            | Manufacturer                | Part Number     | Rated Voltage (V) | Rated Current (A) | Operating Temperature Range (°C) |

| SiC MOSFET | Cree                        | CPM2-1200-0025B | 1200              | 98                | -40 to +175                      |

| Si IGBT    | OnSemi                      | NGTD21T65F2     | 650               | 45                | -55 to +175                      |

| SiC Diode  | Cree                        | CPW5-0650-Z050B | 650               | 50                | -55 to +175                      |

Fig. 7. Four operating region when p.f ≠ 1.

Attachment process starts by applying solder paste to the top surface of the baseplate using stencil. Bottom DBC is placed on top of it. Custom-built graphite fixture has been used so that the components are aligned. Next, same solder paste is dispensed on the top surface of the bottom DBC and top DBC is stacked on top of that. Finally, the top surface of the top DBC is stencil printed and semiconductor chips are placed on their designated locations. Everything is attached together by a single reflow soldering using SAC 305 solder paste of melting temperature 220°C.

Once the semiconductor chips were attached, wire bonding has been done using manual wire bonder machine. For gate

connection, 5 mil aluminum wire bond and for power routing, 12 mil aluminum wire bonds have been used. Next, the gate pins and screw terminals for busbar connection and decoupling capacitors are attached using Pb37Sn63 eutectics solder paste of 183°C melting temperature.

Fig. 10 shows fabrication steps of the module, while Table III gives a list of semiconductor dies and their properties.

#### IV. EXPERIMENT RESULTS

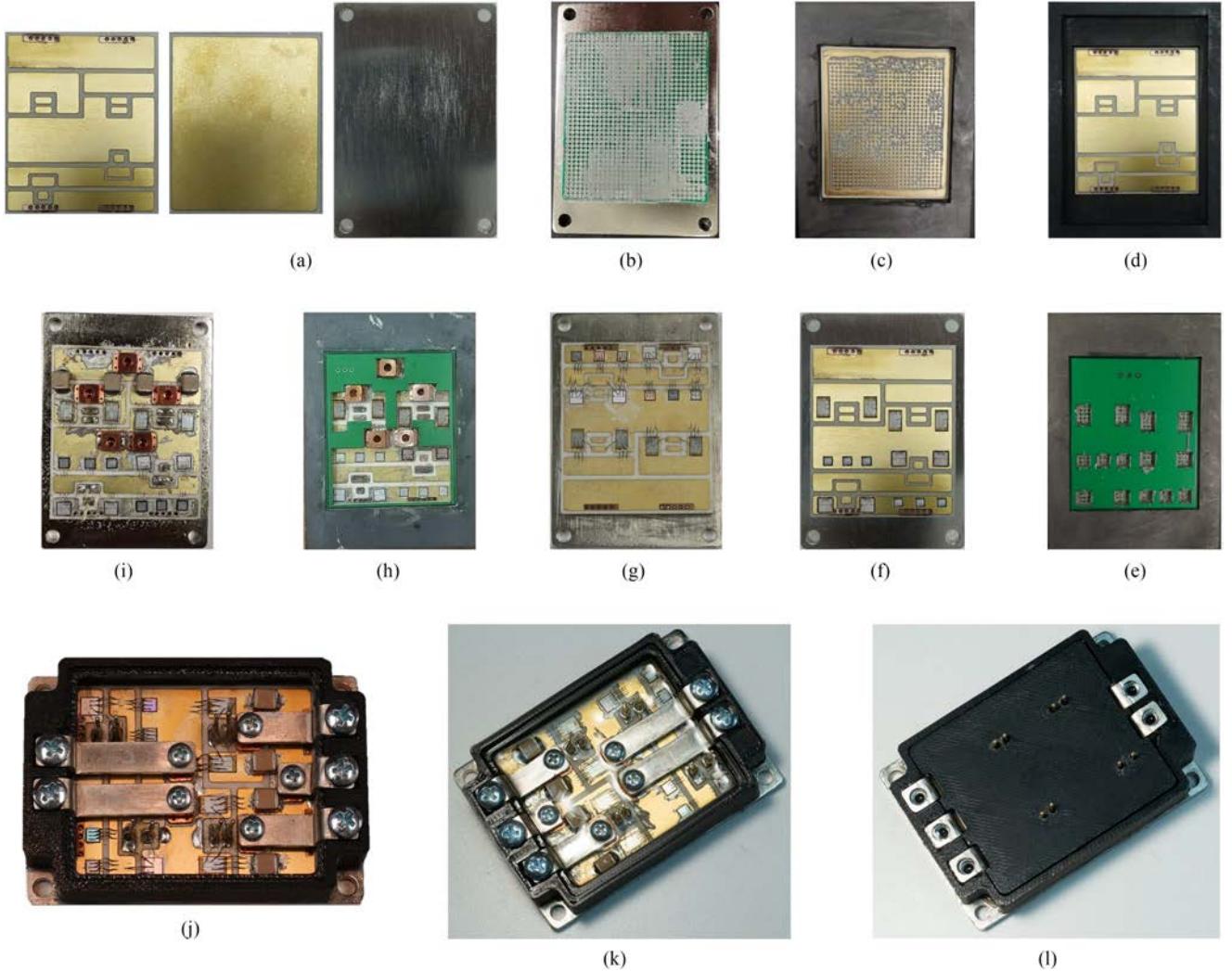

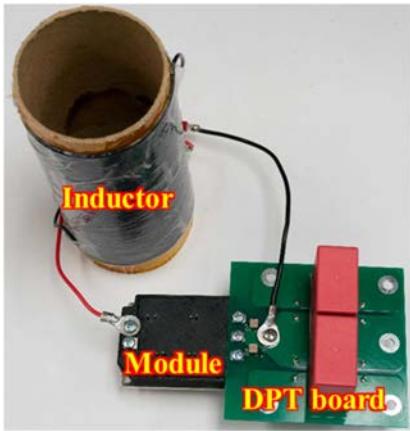

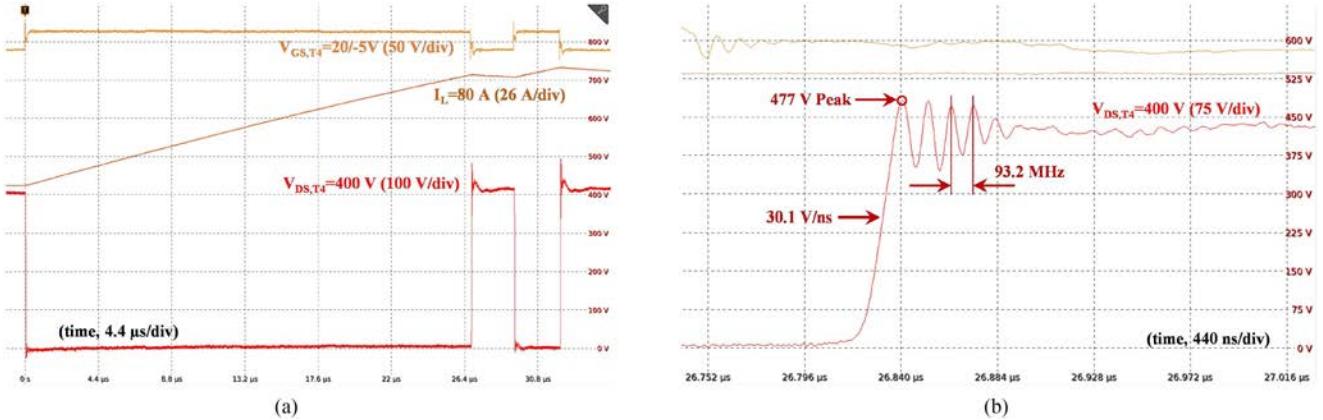

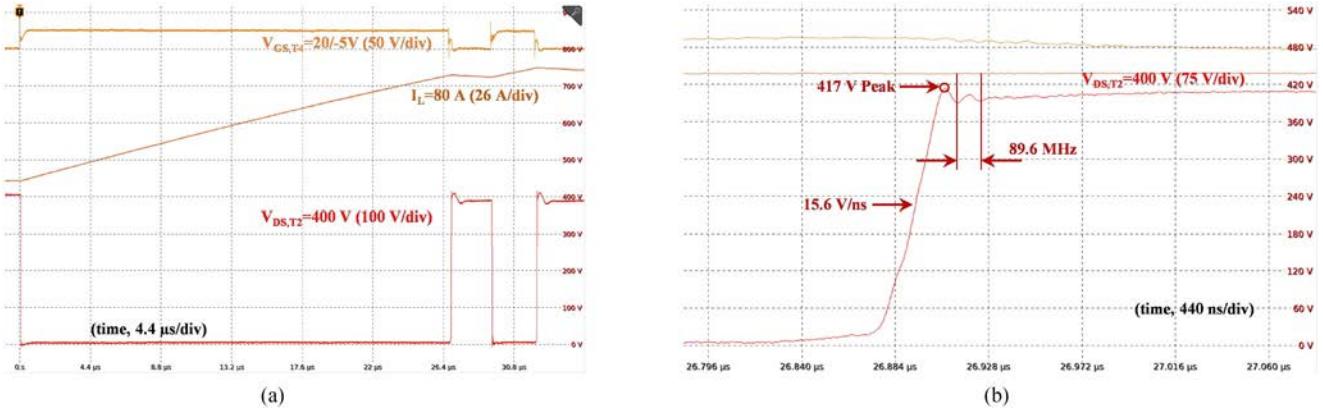

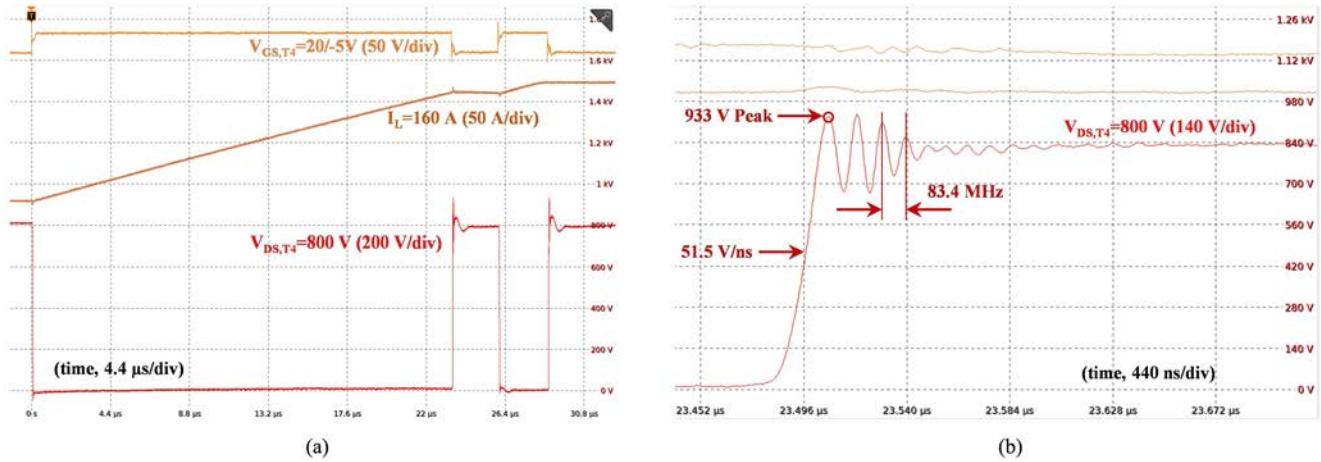

After the fabrication of the module, to evaluate the switching performance, set of standard double pulse test has been performed. As explained in the Section II, during 3L operation, there are four separate commutation loops. For 3L operation, as the commutation loops 1 and 3 have very similar loop with close stray inductance, only loop 1 is tested. It is true for loops 2 and 4. Hence, loop 2 is tested for this case. For 3L case, all the commutation loops individually see the half of dc link voltage, so  $V_{DS}$  is at 400 V and load current is pushed around 80 A. Moreover, there is another commutation loop coming from 2L operation of the module where the clamping leg is not involved. A separate test is done to verify the switching characteristics of that loop. For 2L operation,  $V_{DS}$  is kept at 800 V and the device current was pushed around 160 A. Device current measurement

Fig. 8. Commutation loops involved in 3L operation. (a) Commutation loops in 3L operation (marked in red). (b) Physical commutation loops in designed module.

Fig. 9. Commutation loop in 2L operation.

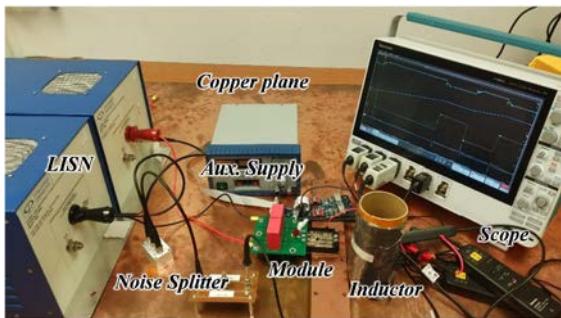

was not possible as the module comes with integrated decoupling capacitors so only load current was monitored. An air core inductor of  $131 \mu\text{H}$  with optimized winding capacitance has been used as clamping load. Off the shelf gate driver from CREE was used to drive the module during testing. Fig. 11 shows the test setup for DPT test.

The test schematics for mentioned three test and their switching waveforms have been shown in Figs. 12–15. Loop inductance can also be extrapolated from the ringing frequency of  $V_{DS}$  during turn OFF transient. If the frequency is measured and the datasheet is available for the die under test, inductance can be calculated using

$$L_{\text{loop}} = \frac{1}{4\pi^2 \times f^2 \times C_{\text{OSS}}} . \quad (4)$$

Here,  $L_{\text{loop}}$  is the stray inductance,  $f$  is the ringing frequency, and  $C_{\text{OSS}}$  is the output capacitance of the die under test. Placement of decoupling capacitor closer to the device pair helps to reduce the size of power loop as well as the stray inductance,  $L_{\text{loop}}$ , which will eventually bring down the energy associated to this oscillation, hence prevent the capacitor to get over heated

[36]–[38]. During the test for capturing the data, 2 GHz oscilloscope from Tektronix has been used. A total of 200 MHz isolated voltage probe has been used for voltage measurement and current was measured using a current probe of 120 MHz bandwidth. During turn-ON,  $5 \Omega$  gate resistance and for turn-OFF,  $1 \Omega$  resistance was used. For instance, to verify the extracted result 4.6 nH for current commutation loop (CCL3), inductance has calculated from  $C_{\text{OSS}}$  of  $T_4$  switching position at 400 V is around 560 pF as two devices are paralleled at that position. From the 93.2 MHz switching frequency, the inductance can be extrapolated as 5.1 nH, which is very close to the extracted value. Due to the nonideality of manufacturing process, placement of probe and inductance of the measurement point at 0.5 nH deviation is there. Same analysis is done for other CCL as well and no more than 0.5 nH deviation was found from the Q3D extracted value.

When SiC switch position is switching, a turn OFF  $dv/dt$  is achieved around 30.1 and 51.5 V/ns for 400 V (3L) and 800 V (2L) blocking voltage, respectively. For IGBT due to the long tail current of the device during turn OFF, turn OFF  $dv/dt$  is 15.6 V/ns. Highest overshoot of 133 V is seen for 2L operation, which is 16.6% of the applied dc link voltage.

## V. CM NOISE CURRENT REDUCTION

### A. Modeling of CM EMI Network

When a voltage gradient is applied across a capacitor, a displacement current passes through it, which is governed by (5)

$$i_C = C \frac{dv}{dt} \quad (5)$$

$$C = \frac{A\varepsilon}{d} . \quad (6)$$

Fig. 10. Fabrication steps of the module. (a) Top DBC, bottom DBC, and baseplate. (b) Screen printing on baseplate. (c) Screen printing on bottom DBC. (d) Alignment using fixture. (e) Screen printing for die attachment. (f) Attached die, DBC, and substrate after first reflow. (g) Preparation of second reflow to attach screw terminals. (h) Preparation of second reflow to attach screw terminals. (i) Module after second reflow. (j) Module after attachment of housing and connectors. (k) Encapsulation of module using silicone gel. (l) Finished module after fabrication.

This displacement current is the primary source of CM EMI in power modules. The parasitic capacitance between switching node to ground provides the path for the noise current to be injected in the ground through the baseplate, as the baseplates are grounded in most of the systems. As decreasing the  $dv/dt$  is not a desirable solution to control the noise current by sacrificing the switching speed, one of the popular solutions is to minimize the value of parasitic capacitance itself, which can be achieved either by increasing the thickness of ceramic substrates ( $d$ ) or by reducing the area of the switching node ( $A$ ) as shown in (6).

Increasing the thickness of the ceramic substrate will offer higher thermal resistance and hinder the thermal performance of the module. Moreover, the parasitic inductance cancellation will be hampered too, as the coupling will go down with the increase of the distance between two conducting layers. The number of die the switching node is accommodating, die footprint, and number of interconnects landing on that island also limits the reduction of the area of the switching node. Hence, in most of the cases, there is a very small room to play with the value of this

capacitance. The proposed approach in this article is different from the conventional one and similar to embedding  $Y$  capacitor in module proposed in [39] where noise is routed back to the source. Drawback of embedding  $Y$  capacitor is its value is limited by the safety standard and it increases fabrication complexity.

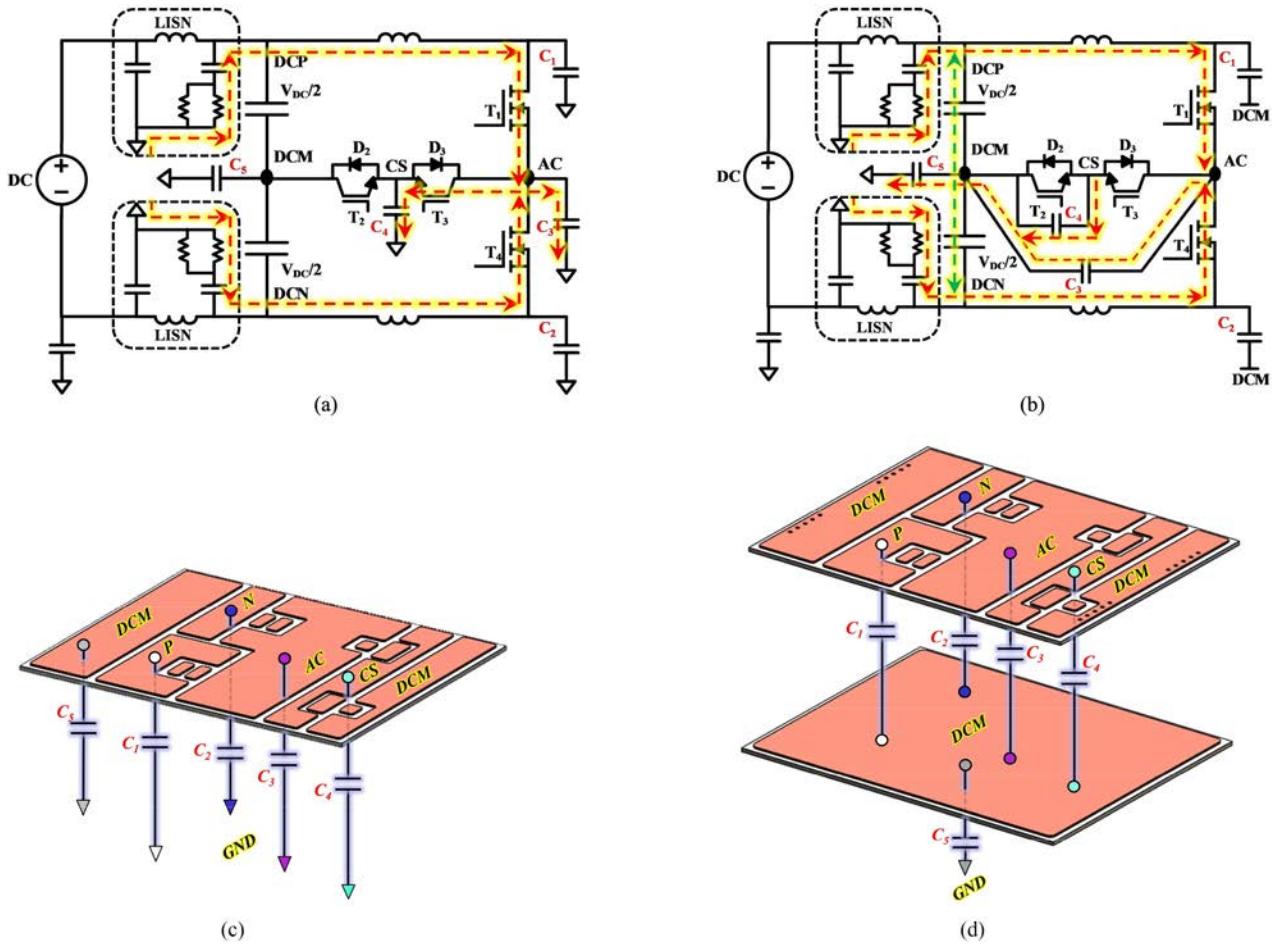

In the proposed approach, instead of embedding a passive capacitor, the noise is routed back to the noise source by using the parasitic capacitance of the module itself. In Fig. 16(a) and (b), the parasitic network of conventional module and the proposed module is presented.

Due to the introduction of the additional DBC, whose entire conducting plane is fixed to DCM potential, it acts as an EMI shield and provides a bypass path for noise. To evaluate the performance of the designed module and have an apple-to-apple comparison, one more module with same pattern but with single DBC is manufactured. Top and bottom copper of this DBC is isolated, as it does not have any via. Associated parasitic capacitance for both modules from individual nodes has been presented as  $C_1-C_5$  in Fig. 16(c) and (d). The values of all

Fig. 11. Test setup.

TABLE IV

EXTRACTED PARASITIC CAPACITANCES

|                  | C <sub>1</sub> | C <sub>2</sub> | C <sub>3</sub> | C <sub>4</sub> | C <sub>5</sub> |

|------------------|----------------|----------------|----------------|----------------|----------------|

| Single DBC (pF)  | 29.68          | 18.2           | 96             | 27.8           | 52             |

| Stacked DBC (pF) | 29.68          | 18.2           | 96             | 27.8           | 340            |

the parasitic capacitances are extracted using Q3D and listed in Table IV.

To model the equivalent circuit of EMI propagation path, we have considered all the associated commutation loops and modeled them separately. For modeling the noise circuit, according to the substitution theorem, a MOSFET can be replaced by a voltage source including all the parasitics at its branch, keeping the circuit behavior the same. Similarly, a diode can be replaced by a current source [40]. After replacing all the switches and decoupling capacitors with voltage and current source, we can apply superposition theorem to see the resultant EMI voltage on LISN. In our analysis, MOSFET is replaced by voltage source  $V_{ac}$  and diode is replaced by current source  $I_D$ . Apart from the stray capacitance of the module shown in Table IV, one additional capacitance has been considered. Here, the additional capacitance  $C_8$  represents the additional CM noise path such as the stray capacitance of load to ground, barrier capacitance of the isolated gate driver, and power supply. Its value is estimated to be 10 pF.

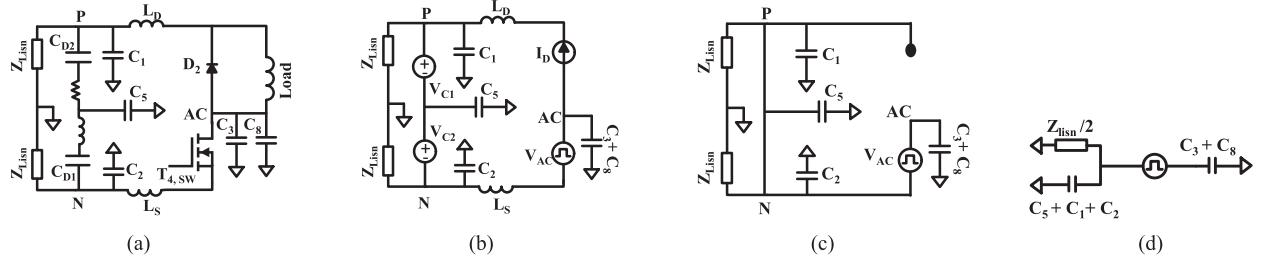

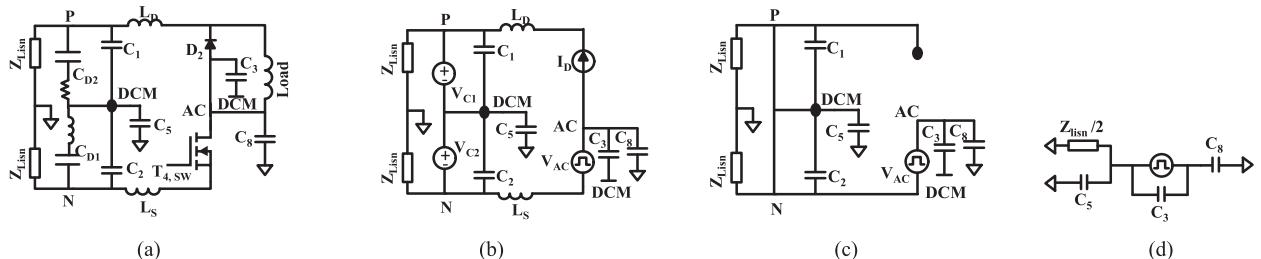

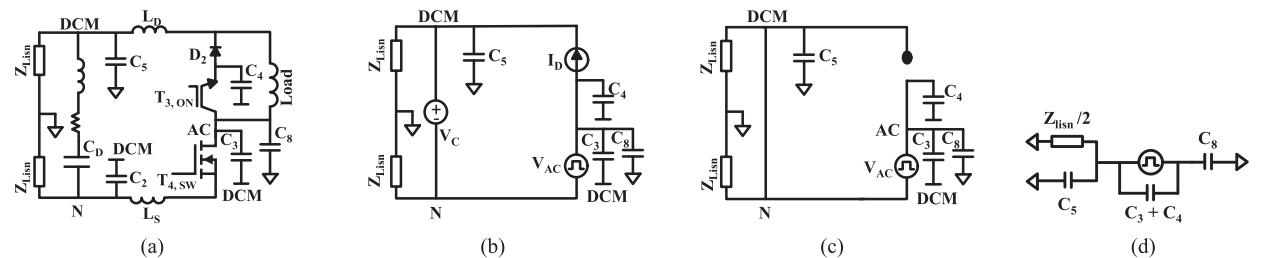

Primarily, a CM noise equivalent circuit is developed from the parasitic capacitance network of single DBC module shown in Fig. 16(c) and the simplified equivalent model is shown in Fig. 17. Similarly, the CM equivalent is drawn for the 2L operation of stacked DBC module and shown in Fig. 18. Though there are four separate loops associated with 3-L operation, it is shown previously that CCL1 is mirror of CCL3. Same is true for CCL2 and CCL4. Primarily, CM equivalent network for CCL3 out of four associated loops is drawn in Fig. 19. The noise voltage across LISN for single DBC module is given as follows:

$$V_{LISN} (\text{Single DBC}) = \frac{\frac{Z_{LISN}}{2} \| Z_{C1+C2+C5}}{Z_{C3+C8} + \frac{Z_{LISN}}{2} \| Z_{C1+C2+C5}} V_{ac} \quad (7)$$

$$V_{LISN} (\text{Stacked DBC}) = \frac{\frac{Z_{LISN}}{2} \| Z_{C5}}{Z_{C8} + \frac{Z_{LISN}}{2} \| Z_{C5}} V_{ac}. \quad (8)$$

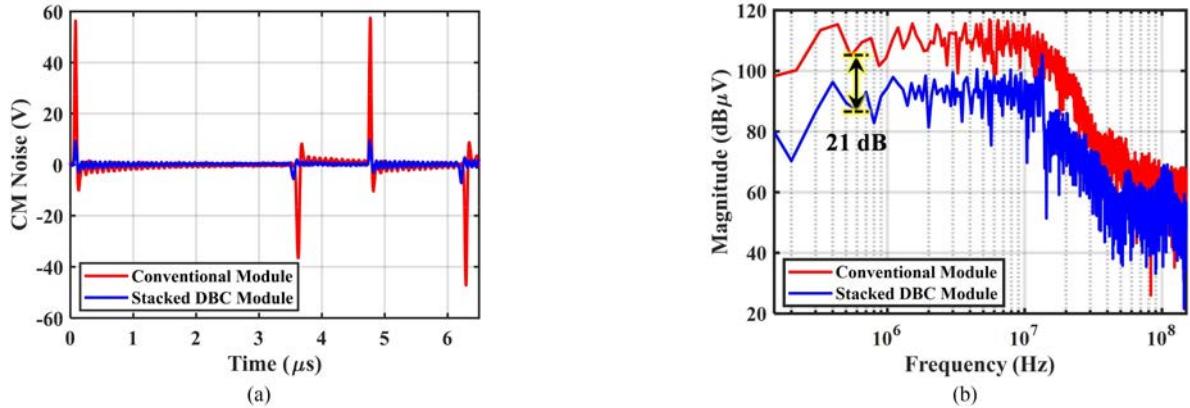

For stacked DBC solution, CM EMI noise equivalent circuit of all the commutation loops are very similar to the model shown in Figs. 18 and 19. CM noise voltage measured for stacked DBC can be presented by (8) for all the associated loops. In (7) and (8), if the value of denominator increases, the noise measured at LISN terminal will go down. That is exactly happening at the case of stacked DBC module. Due to the EMI shielding provided by the bottom DBC, the  $C_3$  capacitance is routed back to the middle point of the dc link whose voltage is ideally zero. Now,  $C_8$  capacitance is the only path for the CM noise to be injected in the ground. Hence, value of the denominator will be higher for stacked DBC solution and the noise voltage will go down accordingly. The ratio between  $Z_{C3}$  and  $Z_{C3+C8}$  is 9.6 using values from Table IV, and noise voltage of stacked DBC module should be around 20 dB lower according to the developed equivalent model.

### B. Experimental Validation

Standard EMI test setup was utilized to measure conducted CM EMI noise from the modules to be compared [46], [47]. Baseplate of the modules are placed on top of a grounded copper plane, which is representing the grounded chassis of motor. Switching test has been done in external loop dedicated for 2L operation for single DBC and stacked DBC module as the schematic shown in Fig. 12(c). The noise has been measured using well-grounded LISN (COMPOWER LI-4100) pair. As the highest voltage rating of the LISN was 780 V dc, test was performed using 400 V dc link. The output from both of the LISN is passed through a noise combiner to get the CM voltage reading according to (9):

$$V_{CM} = \frac{V_{N1} + V_{N2}}{2}. \quad (9)$$

Here,  $V_{N1}$  and  $V_{N2}$  are the voltage measured across the output of each LISN. The output of the noise combiner is terminated across an external 50 Ω resistance and time domain CM noise data is captured in the oscilloscope by probing voltage across that resistor. Standard EMI test bench used in experiment is shown in Fig. 20.

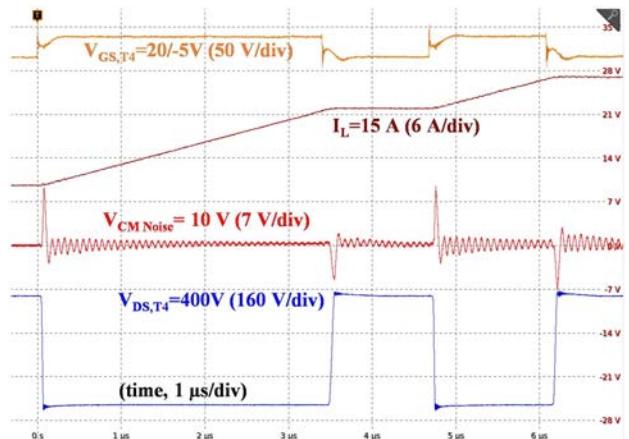

Gate resistance, load current, and the value of inductive load were kept the same for both the modules during testing. As the layout is kept same for both the modules, the parasitic inductance and area of the switching node remained unaltered. Time domain noise and switching waveform for stacked DBC module are shown in Fig. 21.

For comparison, measured time domain CM noise for both the case is plotted one top of other in Fig. 19(a) using two different colors. Subsequently, fast Fourier transform is performed and the results are shown in Fig. 22 (b). It shows a reduction of CM noise as much as 21 dB is achieved using the proposed shielding approach. The experiment results verify the self-containment capability of EMI noise of the designed module. Within the considered frequency range of conducted EMI (150 kHz–30

Fig. 12. Schematics of performed double pulse test (DPT). (a) Schematic for DPT of CCL3. (b) Schematic for DPT of CCL2. (c) Schematic for DPT of 2L operation.

Fig. 13. Switching performance of CCL3. (a) Switching waveform from DPT of CCL3. (b) Zoomed view of turn OFF from DPT of CCL3.

Fig. 14. Switching performance of CCL2. (a) Switching waveform from DPT of CCL2. (b) Zoomed view of turn OFF from DPT of CCL2.

MHz), our designed module shows a consistent performance to reduce CM EMI emission. We believe that the same approach that we have proposed should work for even higher frequency given refined modeling and tailoring to extended frequencies.

## VI. THERMAL SIMULATION

To evaluate the thermal performance of the module, an FEA simulation has been done from where the maximum junction temperature and overall thermal resistance (junction to case)

of the module can be evaluated. Before starting the thermal simulation, loss calculation was done using MATLAB-based program by utilizing datasheet provided value. The analytical model for loss calculation is according to the literature [41], [42] and modified for hybrid structure as shown in (10)–(15), where  $i(k)$  is the transient current,  $f_0$  is the line frequency,  $f_{sw}$  is switching frequency,  $\varphi$  is power factor angle,  $M$  is modulation index,  $R$  represents channel resistance, and  $V_{fw}$  is forward voltage drop. As schottky diodes are used in the layout, only conduction loss of the diodes is considered.

Fig. 15. Switching performance of 2-L operation. (a) Switching waveform from DPT of 2L operation. (b) Zoomed view of turn OFF from DPT of 2L operation.

Fig. 16. Representation of CM EMI network. (a) CM noise path for single DBC conventional module. (b) CM noise path for stacked-DBC-based proposed module. (c) Physical location of parasitic capacitance in single DBC module. (d) Physical location of parasitic capacitance in stacked DBC module.

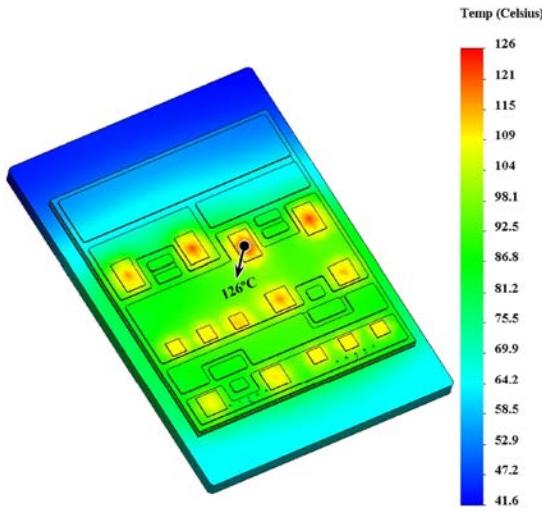

Considering rated current and voltage at 0.95 power factor, 0.8 modulation index, and 70 kHz switching frequency, loss at individual has been calculated. The loss at each die for switching position  $T_1$  and  $T_4$  was found to be 130 W. For clamping leg, the

loss was 80 W per IGBT and 53 W per Schottky diode. Simulation was performed in Solidworks at ambient temperature with a convection coefficient ( $h$ ) at the baseplate equal to 5000 W/m<sup>2</sup>K. The maximum junction temperature 126°C was found in SiC

Fig. 17. Equivalent CM EMI circuit of conventional single DBC module. (a) DPT setup: 2L operation. (b) Substitution applied. (c) Superposition applied. (d) Equivalent circuit.

Fig. 18. Equivalent CM EMI circuit of stacked DBC module (loop analyzed: 2-L operation). (a) DPT setup: 2-L operation. (b) Substitution applied. (c) Superposition applied. (d) Equivalent circuit.

Fig. 19. Equivalent CM EMI circuit of proposed module (loop analyzed: CCL3). (a) DPT setup: CCL3 loop (3L). (b) Substitution applied. (c) Superposition applied. (d) Equivalent circuit.

Fig. 20. EMI test bench for CM noise measurement.

MOSFET at  $T_4$  position. Junction to case resistance for the module was calculated to be  $0.217^\circ\text{C}/\text{W}$  from simulation result. Similar analysis is done for the single DBC-based conventional module and it was found that the thermal resistance for this solution is  $0.168^\circ\text{C}/\text{W}$ .

Fig. 21. EMI measurement of stacked DBC module.

Fig. 22. Comparison of CM noise between stacked DBC and single DBC module. (a) Time domain noise waveform comparison. (b) FFT of CM EMI for stacked and single DBC module.

Fig. 23. Thermal simulation result at rated condition.

In the proposed design, we did a co-optimization where by stacking two DBC's the stray inductance and CM EMI goes down by 3.5 times and 10 times, respectively, but the thermal resistance increases by 1.29 times. From a global optimization point of view, benefit in EMI and stray inductance reduction overwhelms the sacrifice of thermal resistance.

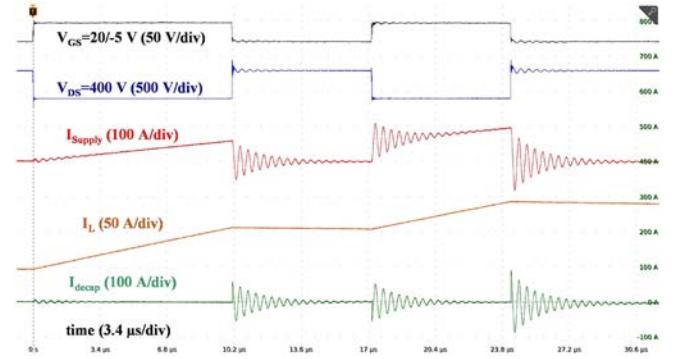

Temperature rise of the embedded decoupling capacitor is primarily related to the equivalent series resistance (ESR) and current ( $I_{\text{decap}}$ ) flowing through it. An experiment is performed to measure the current between main dc bus capacitor and module ( $I_{\text{Supply}}$ ), by putting the module in DPT setup. Waveforms are shown in Fig. 24. Waveform of  $I_{\text{decap}}$  is obtained from the current supplied to the load inductor ( $I_L$ ) and the current between main dc bus capacitor and module ( $I_{\text{Supply}}$ ). Based on the waveform, we can see that, there is charging and discharging current flowing through the embedded ceramic decoupling capacitor ( $I_{\text{decap}}$ ) in every switching instants, and it resonates with the busbar inductance and embedded decoupling capacitor. Estimation of the  $I_{\text{decap}}$  helps to select the appropriate ceramic decoupling capacitor. The ESR of the selected capacitor is 40 mΩ at the frequency of oscillation. The estimated loss per

Fig. 24. Test waveform showing current in decoupling capacitor.

capacitor is 4.52 W at rated condition due to  $I_{\text{decap}}$ , assuming 70 kHz switching frequency.

$$P_{\text{Loss}}(x) = P_{\text{Cond}}(x) + P_{\text{sw}(x)} \quad (10)$$

$$P_{\text{Cond}}(\text{MOSFET}) = \frac{1}{\pi} \int_0^\pi i^2(k) R_{\text{DS(on)}} M |\text{Sin}\theta| d\theta \quad (11)$$

$$P_{\text{sw}(\text{MOSFET})} = 2f_0 \sum_{k=\frac{\varphi f_{\text{sw}}}{2\pi f_0}}^{\frac{\pi f_{\text{sw}}}{2\pi f_0}} (E_{\text{MOSFET(on)}} + E_{\text{MOSFET(off)}}) \quad (12)$$

$$P_{\text{Cond}(\text{IGBT})} = \frac{1}{\pi} \int_0^\pi (|i(k)| V_{\text{fw}(\text{IGBT})} + i^2(k) R_{(\text{IGBT})}) \times (1 - M |\text{Sin}\theta|) d\theta \quad (13)$$

$$P_{\text{sw}(\text{IGBT})} = 2f_0 \sum_{k=\frac{0 f_{\text{sw}}}{2\pi f_0}}^{\frac{\varphi f_{\text{sw}}}{2\pi f_0}} (E_{\text{MOSFET(on)}} + E_{\text{MOSFET(off)}}) \quad (14)$$

$$P_{\text{Cond}(\text{Diode})} = \frac{1}{\pi} \int_0^\pi (|i(k)| V_{\text{fw}(\text{Diode})} + i^2(k) R_{(\text{Diode})}) \times (1 - M |\text{Sin}\theta|) d\theta. \quad (15)$$

Decoupling capacitors of module are located in a way that the chance of thermal coupling with the die is minimal. From the simulation, the location of the decoupling capacitor has a temperature of 66.8°C. Moreover, the capacitors are attached on the same DBC substrate with the semiconductor die; hence, share the same thermal management. So overheating issue of capacitors are duly considered during the design process. In our design, the chosen decoupling capacitor is X7R graded which can operate safely until 125°C. The X7R graded multilevel ceramic capacitor is mainly constructed by BaTiO<sub>3</sub>. The heat capacity, thermal conductivity, and thermal diffusivity of BaTiO<sub>3</sub> is discussed and verified in previous literatures [43], [44]. Considering CTE mismatch between AlN and BaTiO<sub>3</sub>, literatures [38], [45] show that the strain due to thermal expansion in rated operating condition inside power module package is considerably low. It is concluded that this strain will not pose any reliability concerns which holds for our case as well.

## VII. CONCLUSION

A 3L T-type NPC module has been designed, analyzed, fabricated, and tested which has the same DBC size as Infineon's Easy 2B press fit package. Stacking of two DBCs has been proposed to achieve a vertical power loop to reduce commutation loop inductance. A detailed fabrication steps process has been developed. The electrical switching test has been performed to the rated voltage and current. The fabricated module shows the coherent result of the simulated one. CM EMI has been reduced substantially and verified using experimental result. Thermal simulations have been done to evaluate the thermal performance of the module, which has helped to determine maximum power that can be pushed through the module without overheating and degrading the performance of the die.

## REFERENCES

- [1] Y. Chen, Z. Yuan, and F. Luo, "A model-based multi-objective optimization for high efficiency and high power density motor drive inverters for aircraft applications," in *Proc. IEEE Nat. Aerosp. Electron. Conf.*, 2018, pp. 36–42.

- [2] J. Mookken, B. Agrawal, and J. Liu, "Efficient and compact 50kW gen2 SiC device based PV string inverter," in *Proc. Int. Exhib. Conf. Power Electron. Intell. Motion Renewable Energy Energy Manage.*, 2014, pp. 1–7.

- [3] M. Schweizer and J. W. Kolar, "Design and implementation of a highly efficient three-level T-type converter for low-voltage applications," *IEEE Trans. Power Electron.*, vol. 28, no. 2, pp. 899–907, Feb. 2013.

- [4] [Online]. Available: [www.pespublications.ee.ethz.ch/uploads/ttx\\_ethpublications/workshop\\_publications/ecpe\\_multilevel\\_schweizer.pdf](http://www.pespublications.ee.ethz.ch/uploads/ttx_ethpublications/workshop_publications/ecpe_multilevel_schweizer.pdf)

- [5] M. Schweizer, T. Friedli, and J. W. Kolar, "Comparative evaluation of advanced three-phase three-level inverter/converter topologies against two-level systems," *IEEE Trans. Ind. Electron.*, vol. 60, no. 12, pp. 5515–5527, Dec. 2013.

- [6] M. Schweizer, "System-oriented efficiency optimization of variable speed drives," Ph.D. dissertation, ETH Zurich, Switzerland, 2012.

- [7] E. A. Jones, F. F. Wang, and D. Costinett, "Review of commercial GaN power devices and GaN-based converter design challenges," *IEEE J. Emerg. Sel. Topics Power Electron.*, vol. 4, no. 3, pp. 707–719, Sep. 2016.

- [8] Y. Yan, Z. Wang, C. Chen, Y. Kang, Z. Yuan, and F. Luo, "An analytical SiC MOSFET switching behavior model considering parasitic inductance and temperature effect," in *Proc. IEEE Appl. Power Electron. Conf. Expo.*, 2020, pp. 2829–2833.

- [9] A. Deshpande and F. Luo, "Practical design considerations for a Si IGBT + SiC MOSFET hybrid switch: Parasitic interconnect influences, cost, and current ratio optimization," *IEEE Trans. Power Electron.*, vol. 34, no. 1, pp. 724–737, Jan. 2019.

- [10] H. Peng *et al.*, "Improved space vector modulation for neutral-point balancing control in hybrid-switch-based T-type neutral-point-clamped inverters with loss and common-mode voltage reduction," *CPSS Trans. Power Electron. Appl.*, vol. 4, no. 4, pp. 328–338, Dec. 2019.

- [11] H. Peng, Z. Yuan, B. Narayanasamy, X. Zhao, A. Deshpande, and F. Luo, "Comprehensive analysis of three-phase three-level T-type neutral-point-clamped inverter with hybrid switch combination," in *Proc. IEEE 10th Int. Symp. Power Electron. Distrib. Gener. Syst.*, 2019, pp. 816–821.

- [12] Z. Chen, D. Boroyevich, and R. Burgos, "Experimental parametric study of the parasitic inductance influence on MOSFET switching characteristics," in *Proc. Int. Power Electron. Conf.*, 2010, pp. 164–169.

- [13] Z. Chen and D. Boroyevich, "Modeling and simulation of SiC MOSFET fast switching behavior under circuit parasitics," in *Proc. Conf. Grand Challenges Model. Simul.*, 2010, pp. 352–359.

- [14] Z. Dong, X. Wu, K. Sheng, and J. Zhang, "Impact of common source inductance on switching loss of SiC MOSFET," in *Proc. IEEE 2nd Int. Future Energy Electron. Conf.*, 2015, pp. 1–5.

- [15] Z. Zhang, B. Guo, F. F. Wang, E. A. Jones, L. M. Tolbert, and B. J. Blalock, "Methodology for wide band-gap device dynamic characterization," *IEEE Trans. Power Electron.*, vol. 32, no. 12, pp. 9307–9318, Dec. 2017.

- [16] Y. Li *et al.*, "A high performance 1200 V/120 a SiC power module based on a novel Multi-dbc hybrid packaging structure," in *Proc. 10th Int. Conf. Integr. Power Electron. Syst.*, 2018, pp. 1–6.

- [17] C. Chen, F. Luo, and Y. Kang, "A review of SiC power module packaging: Layout, material system and integration," *CPSS Trans. Power Electron. Appl.*, vol. 2, no. 3, pp. 170–186, Sep. 2017.

- [18] S. Li, L. M. Tolbert, F. Wang, and F. Z. Peng, "P-cell and N-cell based IGBT module: Layout design, parasitic extraction, and experimental verification," in *Proc. 26th Annu. IEEE Appl. Power Electron. Conf. Expo.*, 2011, pp. 372–378.

- [19] M. Wang, F. Luo, and L. Xu, "A double-end sourced wire-bonded multi-chip SiC MOSFET power module with improved dynamic current sharing," *IEEE J. Emerg. Sel. Topics Power Electron.*, vol. 5, no. 4, pp. 1828–1836, Dec. 2017.

- [20] Z. Chen, Y. Yao, D. Boroyevich, K. Ngo, and W. Zhang, "An ultra-fast SiC phase-leg module in modified hybrid packaging structure," in *Proc. IEEE Energy Convers. Congr. Expo.*, 2014, pp. 2880–2886.

- [21] C. Chen, Y. Chen, Y. Li, Z. Huang, T. Liu, and Y. Kang, "An SiC-based half-bridge module with an improved hybrid packaging method for high power density applications," *IEEE Trans. Ind. Electron.*, vol. 64, no. 11, pp. 8980–8991, Nov. 2017.

- [22] X. Lyu, X. Tian, H. Li, H. You, and J. Wang, "Design of a lightweight low inductance power module with ceramic baseplates," in *Proc. IEEE Appl. Power Electron. Conf. Expo.*, 2020, pp. 2782–2787.

- [23] A. Dutta and S. S. Ang, "A 3-D stacked wire bondless silicon carbide power module," in *Proc. IEEE 4th Workshop Wide Bandgap Power Devices Appl.*, 2016, pp. 11–16.

- [24] Z. Yuan *et al.*, "Design and evaluation of a 150 kVA SiC MOSFET based three level TNPC Phase-leg PEBC for aircraft motor driving application," in *Proc. IEEE Energy Convers. Congr. Expo.*, 2019, pp. 6569–6574.

- [25] Z. Wang, Y. Wu, M. Mahmud, Z. Yuan, Y. Zhao, and H. A. Mantooh, "Busbar design and optimization for voltage overshoot mitigation of a silicon carbide high-power three-phase T-type inverter," *IEEE Trans. Power Electron.*, vol. 36, no. 1, pp. 204–214, Jan. 2021.

- [26] Z. Yuan *et al.*, "Design and evaluation of laminated busbar for three-level T-type NPC power electronics building block with enhanced dynamic current sharing," *IEEE J. Emerg. Sel. Topics Power Electron.*, vol. 8, no. 1, pp. 395–406, Mar. 2020.

- [27] [Online]. Available: [https://www.infineon.com/dgdl/Infineon-F3L100R12W2H3\\_B11-DS-v02\\_03-EN.pdf?fileId=5546d4624a0bf290014a143e7b41535a](https://www.infineon.com/dgdl/Infineon-F3L100R12W2H3_B11-DS-v02_03-EN.pdf?fileId=5546d4624a0bf290014a143e7b41535a)

- [28] [Online]. Available: <https://www.onsemi.com/pub/Collateral/NXH80T120L2Q0S1G-D.PDF>

- [29] [Online]. Available: <https://www.semikron.com/products/product-lines/semix/semix-5.html>

- [30] [Online]. Available: <https://www.microsemi.com/existing-parts/part/115459>

- [31] [Online]. Available: [https://www.vincotech.com/fileadmin/user\\_upload/product\\_media/Vincotech\\_70-W212NMA600SC-M200P\\_FD-Rev\\_09.pdf](https://www.vincotech.com/fileadmin/user_upload/product_media/Vincotech_70-W212NMA600SC-M200P_FD-Rev_09.pdf)

- [32] A. I. Emon, Z. Yuan, A. Deshpande, H. Peng, R. Paul, and F. Luo, "A 1200V/650V/160A sic+Si IGBT 3-level T-type NPC power module with optimized loop inductance," in *Proc. IEEE Energy Convers. Congr. Expo.*, 2020, pp. 717–722.

- [33] A. K. Huber and R. Kennel, "Ultra-low inductive power module design with integrated common mode noise shielding," in *Proc. 19th Eur. Conf. Power Electron. Appl.*, 2017, pp. P.1–P.9.

- [34] X. Zhang, N. Haryani, Z. Shen, R. Burgos, and D. Boroyevich, "Ultra-low inductance phase leg design for gan-based three-phase motor drive systems," in *Proc. IEEE 3rd Workshop Wide Bandgap Power Devices Appl.*, 2015, pp. 119–124.

- [35] C. Chen, X. Pei, Y. Chen, and Y. Kang, "Investigation, evaluation, and optimization of stray inductance in laminated busbar," *IEEE Trans. Power Electron.*, vol. 29, no. 7, pp. 3679–3693, Jul. 2014.

- [36] Q. Liu, S. Wang, A. C. Baisden, F. Wang, and D. Boroyevich, "EMI suppression in voltage source converters by utilizing dc-link decoupling capacitors," *IEEE Trans. Power Electron.*, vol. 22, no. 4, pp. 1417–1428, Jul. 2007.

- [37] L. Li, P. Ning, Z. Duan, D. Zhang, and X. Wen, "A study on the effect of DC-link decoupling capacitors," in *Proc. IEEE Transp. Electricif. Conf. Expo.*, 2017, pp. 1–5.

- [38] Y. Ren *et al.*, "Voltage suppression in wire-bond-based multi-chip phase-leg SiC MOSFET module using adjacent decoupling concept," *IEEE Trans. Ind. Electron.*, vol. 64, no. 10, pp. 8235–8246, Oct. 2017.

- [39] R. Robutel *et al.*, "Design and implementation of integrated common mode capacitors for SiC-JFET inverters," *IEEE Trans. Power Electron.*, vol. 29, no. 7, pp. 3625–3636, Jul. 2014.

- [40] S. Wang, P. Kong, and F. C. Lee, "Common mode noise reduction for boost converters using general balance technique," *IEEE Trans. Power Electron.*, vol. 22, no. 4, pp. 1410–1416, Jul. 2007.

- [41] D. Graovac, M. Purschel, and A. Kiep, "Mosfet power losses calculation using the data-sheet parameters," Infineon Application Note, Infineon Technologies AG, München, Germany, vol. 1, pp. 1–23, 2006.

- [42] A. Nawawi *et al.*, "Design and demonstration of high power density inverter for aircraft applications," *IEEE Trans. Ind. Appl.*, vol. 53, no. 2, pp. 1168–1176, Mar./Apr. 2017.

- [43] D. S. Erdahl and I. C. Ume, "Online-offline laser ultrasonic quality inspection tool for multilayer ceramic capacitors—Part II," *IEEE Trans. Adv. Packag.*, vol. 28, no. 2, pp. 264–272, May 2005.

- [44] Y. He, "Heat capacity, thermal conductivity, and thermal expansion of barium titanate-based ceramics," *Thermochim. Acta*, vol. 419, pp. 135–141, 2004.

- [45] M. Hart, "CCGA solder column reliable solution for absorbing large CTE mismatch," in *Proc. Eur. Microelectron. Packag. Conf.*, 2015, pp. 1–5.

- [46] C. M. DiMarino, B. Mouawad, C. M. Johnson, D. Boroyevich, and R. Burgos, "10-kV SiC MOSFET power module with reduced common-mode noise and electric field," *IEEE Trans. Power Electron.*, vol. 35, no. 6, pp. 6050–6060, Jun. 2020.

- [47] D. N. Dalal *et al.*, "Impact of power module parasitic capacitances on medium-voltage SiC MOSFETs switching transients," *IEEE J. Emerg. Sel. Topics Power Electron.*, vol. 8, no. 1, pp. 298–310, Mar. 2020.