# Comparison of Electrical Characteristics of Schottky Junctions based on CdS Nanowires and Thin Film

Hongmei Dang<sup>1</sup>, Esther Ososanya<sup>1</sup> and Nian Zhang<sup>1</sup>

<sup>1</sup>Department of Electrical and Computer Engineering, University of the District of Columbia

## Abstract:

CdS nanowires and film Schottky diodes are fabricated and diode properties are compared. Effect of SnO<sub>2</sub> on CdS film diode properties is investigated. CdS film/ Au on 100nm SnO<sub>2</sub> substrate demonstrates like-resistor characteristics and increase in SnO<sub>2</sub> thickness corrects resistor behavior, however the effective reverse saturation current density  $J_o$  is significantly high and shunt resistance are considerably low, implying that SnO<sub>2</sub> slightly prevents impurities migration from CdS films into ITO but cause additional issues. Thickness of CdS film on diode properties is further investigated and increasing CdS film thickness improved  $J_o$  by one order of magnitude, however shunt resistance is obviously low, suggesting intrinsic issues in CdS film. 100nm CdS nanowire/Au diodes reduce  $J_o$  by three orders of magnitude in the dark and two orders of magnitude in the light respectively and their shunt resistance is significantly enhanced by 70 times when comparing with those of the CdS film diodes. The wide difference can be attributed to the fact that CdS nanowires overcome intrinsic issues in CdS film and thus demonstrate significantly well-defined diode behavior. Simulation found that CdS nanowire diodes have low compensating acceptor type traps and interface state density of  $5.0 \times 10^9/\text{cm}^2$ , indicating that interface recombination isn't a dominated current transport mechanism in the nanowire diodes. CdS film diodes are simulated with acceptor traps and interface state density increased by two order of magnitude and shunt resistance reduced by one order of magnitude, indicating that high density of interface states and shunt paths occur in the CdS film diodes.

**Keywords** Nanowire Schottky diodes, reverse saturation current, shunt resistance, recombination

## 1 2 3 4 5 Introduction

6 Cadmium sulphide (CdS) is one of the most promising II-VI semi-conductor materials

7 because of appropriate band structure [1, 2]. It's film form has a direct, energy gap of 2.4 eV,

8 resulting in an absorption coefficient  $>10^4 \text{ cm}^{-1}$  for wavelength less than 500nm [1-3]. Due to high

9 light absorption coefficient, it needs only thin layer to absorb  $>90\%$  of light above the band gap.

10 CdS can be natively *n*-doped and the carrier density even reaches  $1.6 \times 10^{18} \text{ cm}^{-3}$  [4]. CdS has been

11 widely used in sensors [5, 6], photodetectors[7], light emitting diodes[8], logic circuits[9],

12 photocatalyst for water splitting [1] as fuel cells which are applied for electrical vehicles. In

13 addition, CdS was recognized to be the most effective heterojunction partner of II-VI solar cells

14 and has been widely applied into these II-VI solar cells such as CdTe [10, 11], CZTS [12] and

15 Sb<sub>2</sub>Se<sub>3</sub> solar cells[13]. However, there is a great challenge regarding the application CdS film,

16 because the fast recombination of photo-excited electron hole pairs in CdS film reduce

17 photocatalytic activity, photodetector response and photocurrent in solar cells etc[1, 10].

18 Considerable efforts have been carried out to exploit feasible approaches to reduce recombination

19 and enhance photo-response of CdS film based devices, including reducing CdS thickness [10],

20 doping strategy [14] and co-catalyst modifying methods [1].

21 Nanoparticles, nanorods and nanowires have been used to tune optical and electrical properties,

22 improve photon generation and electron-hole combination[1, 2, 15, 16]. Oriented and aligned

23 nanostructures have shown excellent performance in various piezoelectric nanogenerator [17],

24 optoelectronics [15, 18] and electronic devices[19, 20]. Inspired by wide applications of CdS and

25 nanostructures, here we fabricate CdS nanowires and configure the CdS nanowire into Schottky

26 diodes. As comparison, CdS film/Au diodes are fabricated. We further characterize electrical

27 properties of CdS nanowires/Au diodes, develop a simulation model to quantitatively analyze their

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

50

I-V characteristics and further compare their properties with CdS film diodes. Investigation in this work gives novel insight into CdS nanowires and can find wide applications such as fuel cells for electrical vehicles[1, 21], various solar cells [11] and photodetectors [7], transistors etc [19, 22].

## 1. Experimental Procedures

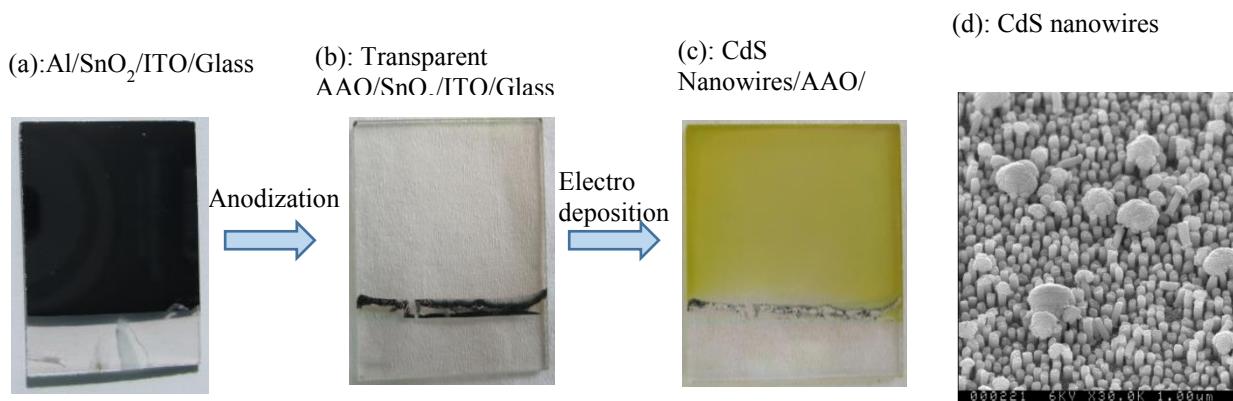

1.1 Formation of Alumina Matrix: CdS nanowires were grown with highly oriented and well aligned arrays by an alumina- matrix-assisted deposition method. Figure 1 shows visual images of fabrication steps for CdS nanowires. Firstly, alumina- matrix was prepared by following procedures. RF sputtering deposited 100nm intrinsic tin oxide  $\text{SnO}_2$  and then 5nm titanium on ITO glass substrate. Electron beam evaporation deposited 100nm/200nm thick aluminum on the substrate, as shown Figure 1(a). Next, 0.3M oxalic acid solution was prepared to anodize Al/Ti/ $\text{SnO}_2$ /ITO glass substrate under 50V DC bias until Al substrate became transparent, indicating that Al layer has become to alumina- matrix. It has been found that there was a barrier layer between alumina- matrix and  $\text{SnO}_2$ /ITO glass substrate due to insertion of 5nm titanium, which prevents growth of nanowires by alumina- matrix. Therefore, 5% phosphoric acid was used to etch samples for 30 minutes to partially remove the barrier layer. Reactive ion etch (RIE) process was set with RF and ICP power to completely remove the barrier layer. The samples were etched in 5% phosphoric acid for 5 minutes and rinsed by deionized water[11]. The barrier-free transparent alumina- matrix with nanopores were formed on  $\text{SnO}_2$ /ITO glass substrate, where the visual image is shown in Figure 1(b).

1.2 Growth of CdS Nanowire: An eletrodeposition method was developed to embed CdS into alumina- matrix nanopores. The visual image of CdS nanowires/  $\text{SnO}_2$ / ITO/ the glass is shown in Figure 1(c), and the corresponding SEM image for the CdS nanowires is shown in Figure 1(d). Specifically, the CdS nanowires were grown in electrolyte with a mixture of 0.055M cadmium chloride and 0.19M

1

2

3 sulfur in 50mL dimethyl-sulfoxide (DMSO) solution, under dc current density of 7mA/cm<sup>2</sup> and

4 deposition temperature of 120-160°C. It is observed that all of the nanopores with completely

5 removed barrier layer can be filled efficiently with CdS nanowires under dc bias. Therefore, the

6 barrier layer removing procedure is crucial to form uniform and dense CdS nanowires. Following

7 growth, the CdS nanowires were annealed at 400°C for 30 minutes with 100-sccm Argon purge[11].

8

9

10

11

12

13

14

15 1.3 Formation of CdS/Au diode structure: CdS/Au diode structure was formed by following

16 procedures. 0.1M NaOH solution is used to selectively remove alumina-matrix for 1 min and

17 partially expose CdS nanowires. The thermal evaporation is used to deposit 100nm Au on the CdS

18 nanowires, resulting in CdS nanowires/Au Schottky diodes. For comparison,

19 100nm/200nm/400nm planar CdS thin film was deposited on 100nm/175nm/250nm/325nm

20 SnO<sub>2</sub>/ITO glass substrate by well-established chemical bath deposition and 100nm Au was

21 deposited on the top to form CdS film/Au Schottky diode structure.

22

23

24

25

26

27

28

29

30

31

32 1.4 Characterization: Material characterization of the CdS nanowires was conducted with a

33 scanning electron microscope (Hitachi S-900 field emission SEM). For diode characterization,

34 electrical properties of CdS nanowire /Au Schottky diodes and CdS film/Au Schottky diodes were

35 characterized as comparison. The current density versus voltage (J-V) were measured at

36 illumination intensity of 100 mW cm<sup>-2</sup> and at the dark, where gold contact was biased positively

37 with respect to the bottom ITO. Simulations of J-V characteristics of CdS nanowires/Au and CdS

38 film/Au diodes were performed by SCAPS software[23]. By fitting J-V simulations with measured

39 J-V characteristics, we established numerical models to investigate electrical property mechanism

40 of CdS nanowires/Au diodes compared with CdS film/Au diodes. This work focuses on CdS

41 nanowire mechanism, investigation in this work will give insight into other CdS nanowire-based

42 devices and can find wide application in solar cells, fuel cells and photodetectors ect [1].

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

Figure 1. Visual images of fabrication steps for CdS nanowires including (a) aluminum deposited on the top of a substrate, (b) formation of AAO matrix and (c) CdS nanowires filled in the nanopores of AAO matrix; and (d) top view SEM image of CdS nanowires.

## 2. Results and Discussion

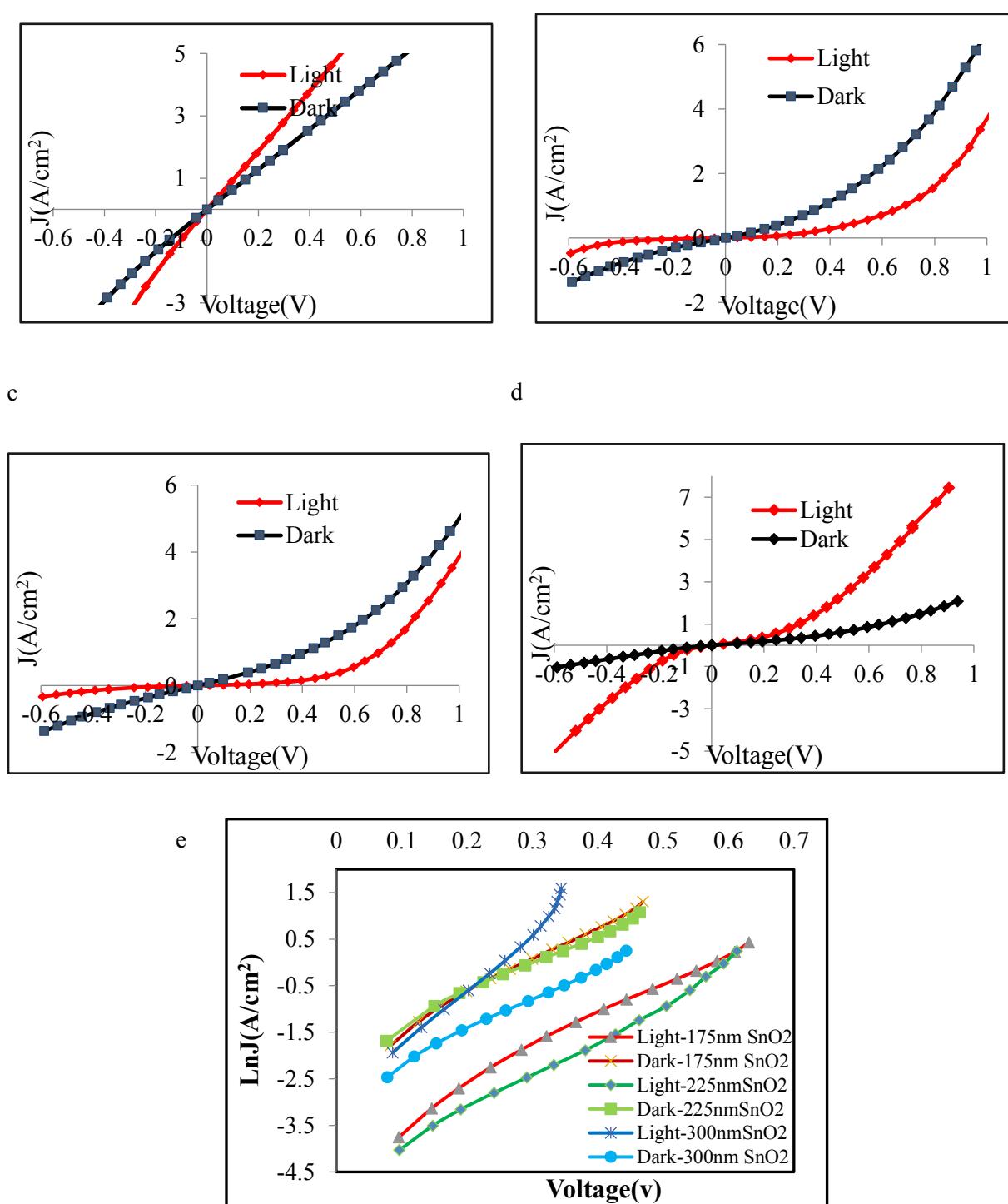

For comparison, J-V characteristics of Au/ CdS film with 100nm thickness on 100nm SnO<sub>2</sub>/ITO glass substrate (100nm CdS film diodes on 100nm SnO<sub>2</sub>) were measured in dark and under “one sun” illumination, shown in the Figure 2 (a). In order to understand the effect of SnO<sub>2</sub> on CdS film diodes, J-V characteristics of 100nm CdS film/Au diodes on 175nm/225nm/300nm SnO<sub>2</sub> substrate (CdS film diodes on 175nm SnO<sub>2</sub>, CdS film diodes on 225nm SnO<sub>2</sub> CdS film diodes on 300nm SnO<sub>2</sub>) were characterized, shown in Figure 2 (b) and (c) and (d) respectively.

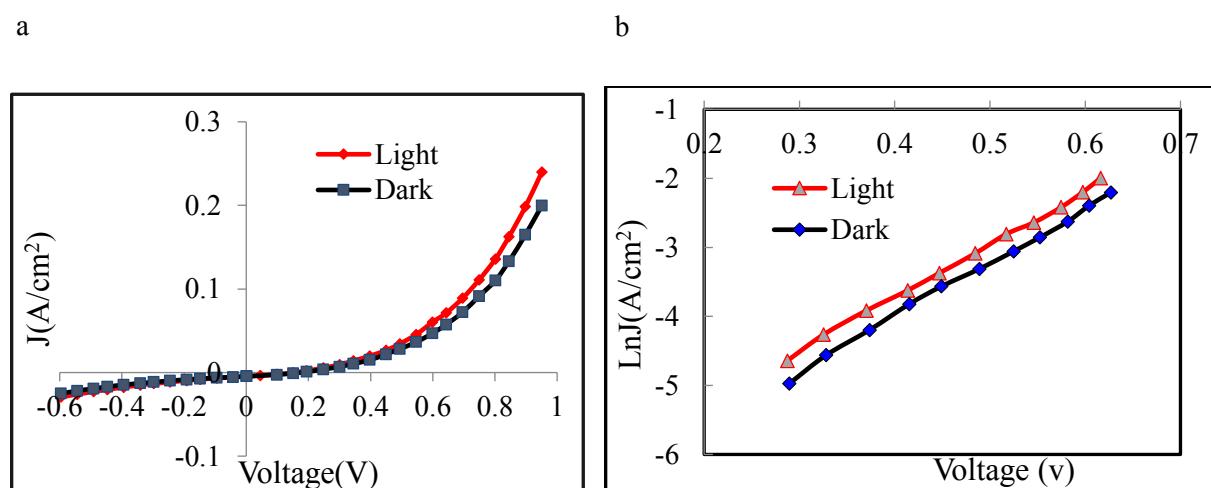

Furthermore, effect of CdS film thickness on electron transport was investigated, and CdS films with 200nm and 400nm thickness/Au Schottky diodes on 100nm SnO<sub>2</sub>/ITO glass substrate (200nm CdS film diodes and 400nm CdS film diodes) were measured in dark and under “one sun” illumination, shown in the Figure 3 (a) and (b) respectively.

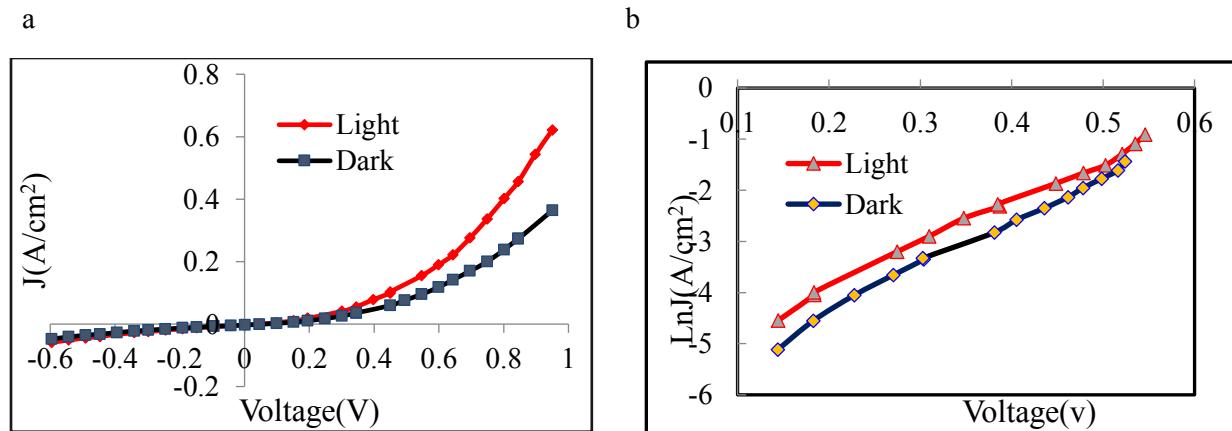

For insight about CdS nanowire arrays, CdS nanowires with 100nm and 200nm length were configured into 100nm CdS nanowires/Au Schottky diodes on 100nm SnO<sub>2</sub>/ITO glass substrate (100nm CdS nanowire diodes on 100nm SnO<sub>2</sub>) and 200nm CdS nanowires/Au Schottky diodes

1

2

3 on 100nm SnO<sub>2</sub>/ITO glass substrate (200nm CdS nanowire diodes on 100nm SnO<sub>2</sub>). Their Current

4

5 density (J)-voltage (V) characteristics were measured in dark and under “one sun” illumination,

6

7 shown in the Figure 4 (a) and (c) respectively.

8

9

10

11

## 12 **2.1 Effect of SnO<sub>2</sub> on Current-Voltage Characteristics of CdS film/Au Schottky Diodes**

13

14 Figure 2 (a), (b) and (c) and (d) show J-V characteristics of 100nm CdS film diodes on

15 100nm/175nm/225nm/300nm SnO<sub>2</sub> substrate respectively. Figure 2 (e) shows LnJ verse V

16 characteristics of these diodes in order to extract diode ideality factor (n) and reverse saturation

17 current density (J<sub>0</sub>). Extracted diode parameters of these CdS film diodes are illustrated in the

18

19 Table 1.

20

21

22

23 J-V characteristics of 100nm CdS film diodes on 100nm SnO<sub>2</sub> demonstrate resistor-like

24 behavior, where J is nearly linearly dependent on voltage. Analysis its J-V data yielded series

25 resistance of 0.48Ω/cm<sup>2</sup> and 0.3Ω/cm<sup>2</sup> respectively, and shunt resistance of 0.4/cm<sup>2</sup> and shunt

26 resistance 0.2/cm<sup>2</sup> in the light and dark irrespectively. The very low series and shunt resistance

27 indicate that there are an abundant of shunt paths in 100nm CdS film deposited by CBD and these

28 high density of shunt paths form low resistivity of resistors which are in parallel with diodes. These

29 parallel resistors become dominated factors, forming resistor-like J-V curves.

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

Figure 2, Current density ( $J$ ) versus voltage  $V$  characteristics of 100nm CdS film/Au Schottky diodes on (a): 100nm  $\text{SnO}_2$  substrate. (b): 175nm  $\text{SnO}_2$  substrate. (c): 225nm  $\text{SnO}_2$  substrate. (d): 300nm  $\text{SnO}_2$  substrate. (e)  $\text{Ln}J$  verse  $V$  characteristics of 100nm CdS film/Au on 100nm/175nm/225nm/300nm  $\text{SnO}_2$  substrate.

1

2

3 In order to solve resistor-like J-V curves, CdS film was maintained 100nm thickness but SnO<sub>2</sub>

4 thickness were increased to 175nm, 225nm and 300nm. As shown in Figure 2 (b), CdS film diodes

5 on 175nm SnO<sub>2</sub> thickness obviously reduce shunt issues and show rectifying diode characteristics.

6

7

8

9 Current density in the light is lower than its dark value, which is thought to be due to additional

10 light generated defects in CdS film. Analysis of J vs. V data in Figure 2 (b) demonstrated the

11 effective reverse saturation current density ( $J_0$ ), diode ideality factor (n), series and shunt resistance

12 values of  $1.1 \times 10^{-2}$  A/cm<sup>2</sup>, 3.1, 0.08Ω/cm<sup>2</sup> and 0.04Ω/cm<sup>2</sup> in the dark and  $2.0 \times 10^{-3}$  A/cm<sup>2</sup>, 3.6,

13 0.1Ω/cm<sup>2</sup> and 2.2 Ω/cm<sup>2</sup> in light, as illustrated in the Table 1. However, the low  $J_0$  and shunt

14 resistance reveal that shunt and tunneling are the dominant processes for electron transport in these

15 devices.

16

17

18 Further increasing thickness of SnO<sub>2</sub> to 225nm, similar diode behavior was observed.

19 Compared with 100nm CdS film diodes on 175nm SnO<sub>2</sub> substrate, the diodes on 225nm SnO<sub>2</sub>

20 substrate exhibited higher diode ideality factor and reverse saturation current density and similar

21 value of series and shunt resistance, shown in the Table 1. The higher diode ideality factor and

22 reverse saturation current density imply degraded diode performance. When thickness of SnO<sub>2</sub> is

23 increase to 300nm, diode ideality factors are approximately increased by 2 times, reverse saturation

24 current density are further increased by one order of magnitude, series resistance is obviously

25 increased and shunt resistance is further reduced to 0.46 Ω/cm<sup>2</sup> and 0.12Ω/cm<sup>2</sup> in the dark and

26 light respectively. Significantly increased diode ideality factor and reduced  $J_0$  and shunt resistance

27 demonstrate that diode behavior has been deteriorated. The reason is thought to be related to our

28 hypothesis that thick SnO<sub>2</sub> increases resistance of the diodes and interface recombination between

29 CdS and SnO<sub>2</sub> becomes more obvious with increasing SnO<sub>2</sub> thickness. As a result, increase of

30 SnO<sub>2</sub> thickness can overcome resistor-like behavior in 100nm CdS film diodes, however high

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

1

2

3 reverse saturation current density low shunt resistance are main issues in these diodes.

4

5

6

## 7 **2.2 Effect of CdS film thickness on Current-Voltage Characteristics of Diodes** 8

9

10 Thickness of CdS film on J-V characteristics of the CdS film/Au Schottky diodes was

11 investigated. Figure 3 (a) and (b) show J-V characteristics of 200nm CdS film and 400nm CdS

12 film diodes under dark and one-sun illumination. Figure 3 (c) shows their LnJ verse V

13 characteristics under dark and one-sun illumination to extract diode ideality factor and reverse

14 saturation current density, which are demonstrated in the Table 1. When CdS film thickness is

15 increased to 200nm, the J-V curves of CdS film diodes eliminate resistor-like characteristics

16 founded in the 100nm CdS film diodes and exhibit Schottky diode behavior.

17

18

19 J-V data of 200nm CdS film diodes was analyzed and yielded the reverse saturation current

20 density ( $J_0$ ) and diode ideality factor (n) values of  $1.2 \times 10^{-4} \text{ A/cm}^2$  and 3.1 in the light and  $5.8 \times 10^{-4} \text{ A/cm}^2$  and 4 in the dark. Compared with 100nm CdS film diodes, 200nm CdS film diodes reduce

21  $J_0$  by approximately 19 times in the dark and 16 times in the light, and maintain diode ideality

22 factor, series and shunt resistances in the similar range. It is thought that thicker CdS film alleviates

23 pinholes impact and reduces migration of metal from CdS film into  $\text{SnO}_2$  and ITO, hence

24 decreasing interface recombination and generation. Reducing interface recombination and

25 generation lead to improvement of  $J_0$ . Measurements of shunt resistance reveal less resistance in

26 the light than dark. It is possible that the additional light generated electron-hole pairs contribute

27 to additional tunneling currents, resulted in lower shunt resistance in the light. It is observed that

28 shunt resistance in the light and dark maintains low values, suggesting poor quality of CdS film.

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

Figure 3, Dark and light current density ( $J$ ) versus voltage  $V$  characteristics of (a): 200nm CdS film/Au Schottky diodes on 175nm SnO<sub>2</sub> substrate. (b): 400nm CdS film/Au Schottky diodes on 175nm SnO<sub>2</sub> substrate. (c): Dark and light  $\ln J$  verse  $V$  characteristics of these 200nm and 400nm CdS diodes.

As shown in Figure 3 (b), when CdS thickness is further increased to 400nm, the diode demonstrates similar performance as the diode with 200nm CdS film. The main difference between the diodes made from 200nm and 400nm CdS films are reverse saturation current density ( $J_0$ ) and shunt resistance under illumination. When CdS thickness is increased to 400nm, the  $J_0$  is

significantly increased from  $1.2 \times 10^{-4}$  to  $3.2 \times 10^{-2}$ , increased by approximately two order of magnitude. A significant increase in  $J_0$  value indicates non-ideal generation events become severe in the interface and depletion region. As shown in the Table 1, slightly increased shunt resistance implies that additional light generated electron-holes pairs transport through pinholes or 3D defects in the thicker CdS film to interface and ITO substrate. Thus, it can be concluded that an approach increasing CdS film thickness eliminates like-resistor behavior, however the approach presents significant challenges of its own. Low shunt resistance and relative low  $J_0$  caused by poor quality of CdS film deteriorate diode performance.

Table 1 Extracted diode parameters of CdS nanowires/Au and CdS film/Au diodes

| Diode Type                                   | Test Condition | Diode Ideality Factor (A) | Reverse Saturation Current Density $J_0$ (A/cm <sup>2</sup> ) | Series Resistance (Ω/cm <sup>2</sup> ) | Shunt Resistance (Ω/cm <sup>2</sup> ) |

|----------------------------------------------|----------------|---------------------------|---------------------------------------------------------------|----------------------------------------|---------------------------------------|

| 100nm CdS film/Au                            | Dark           | N/A                       | N/A                                                           | 0.48/cm <sup>2</sup>                   | 0.4/cm <sup>2</sup>                   |

|                                              | Illumination   | N/A                       | N/A                                                           | 0.3/cm <sup>2</sup>                    | 0.2/cm <sup>2</sup>                   |

| 100nm CdS film/Au on 175nm SnO <sub>2</sub>  | Dark           | 3.1                       | $1.1 \times 10^{-2}$                                          | 0.08/cm <sup>2</sup>                   | 0.44/cm <sup>2</sup>                  |

|                                              | Illumination   | 3.6                       | $2 \times 10^{-3}$                                            | 0.1/cm <sup>2</sup>                    | 2.2/cm <sup>2</sup>                   |

| 100nm CdS film /Au on 225nm SnO <sub>2</sub> | Dark           | 6.0                       | $1.37 \times 10^{-1}$                                         | 0.1/cm <sup>2</sup>                    | 0.44/cm <sup>2</sup>                  |

|                                              | Illumination   | 3.7                       | $2.3 \times 10^{-3}$                                          | 0.09/cm <sup>2</sup>                   | 1.9/cm <sup>2</sup>                   |

|                                                        |              |      |                      |                      |                      |

|--------------------------------------------------------|--------------|------|----------------------|----------------------|----------------------|

|                                                        |              |      |                      |                      |                      |

| <b>100nm CdS film/Au on 300nm SnO<sub>2</sub></b>      | Dark         | 13   | $3.6 \times 10^{-1}$ | 0.11/cm <sup>2</sup> | 0.46/cm <sup>2</sup> |

|                                                        | Illumination | 12.8 | $7.1 \times 10^{-1}$ | 0.07/cm <sup>2</sup> | 0.12/cm <sup>2</sup> |

| <b>200nm CdS film/Au on 175nm SnO<sub>2</sub></b>      | Dark         | 4.06 | $5.8 \times 10^{-4}$ | 0.24/cm <sup>2</sup> | 1.8/cm <sup>2</sup>  |

|                                                        | Illumination | 3.14 | $1.2 \times 10^{-4}$ | 0.12/cm <sup>2</sup> | 0.88/cm <sup>2</sup> |

| <b>400nm CdS film/Au on 175nm SnO<sub>2</sub></b>      | Dark         | 3.54 | $3.1 \times 10^{-4}$ | 0.13/cm <sup>2</sup> | 1.9/cm <sup>2</sup>  |

|                                                        | Illumination | 3.17 | $3.2 \times 10^{-2}$ | 0.12/cm <sup>2</sup> | 0.56/cm <sup>2</sup> |

| <b>100nm CdS nanowires/Au on 100nm SnO<sub>2</sub></b> | Dark         | 3.3  | $8.0 \times 10^{-5}$ | 1.58/cm <sup>2</sup> | 30.8/cm <sup>2</sup> |

|                                                        | Illumination | 3.1  | $6.9 \times 10^{-5}$ | 1.37/cm <sup>2</sup> | 24.4/cm <sup>2</sup> |

| <b>200nm CdS nanowires/Au on 100nm SnO<sub>2</sub></b> | Dark         | 2.2  | $1.2 \times 10^{-4}$ | 1.16/cm <sup>2</sup> | 13.4/cm <sup>2</sup> |

|                                                        | Illumination | 2.6  | $2.4 \times 10^{-5}$ | 0.64/cm <sup>2</sup> | 10.9/cm <sup>2</sup> |

### 2.3 Characterization of CdS nanowires/Au Schottky Diode

CdS nanowires/Au Schottky diodes are presented to overcome these challenges. Figure 4 (a) illustrates current density J dependence on voltage V, where the junctions were formed by Au

1

2

3 deposited on CdS nanowires with 100nm length on 100nm SnO<sub>2</sub> substrate. The J-V characteristics

4 of the junctions show rectification behavior, which indicates the formation of a Schottky diode in

5 the 100nm CdS nanowires/Au structure. As shown in the Figure 4(a), current under illumination

6 increased slightly over its dark value due to photoresponse which is additional electron-hole pairs

7 generated by the light. The reverse J-V characteristics demonstrate current dependence on applied

8 voltage bias due to barrier lowering effect. The forward J-V characteristics in Figure 4 (a) can be

9 classified into two regions based on the applied forward bias. Above 0.6V,  $\ln(J)$  dependence on

10 voltage deviates from linearity, which is impacted by series resistance and interface between CdS

11 nanowires/Au structure. Below 0.6V,  $\ln(J)$  exhibits linear dependence on voltage, as shown in

12 Figure 4(b). Thus, diode ideality factor  $n$  and reverse saturation current density  $J_0$  are obtained by

13 using the slope and intercept of Figure 4(b) curve, which are tabulated in the Table 1.

14

15

16 The diode ideality factor  $n$  was obtained with value of 3.3 and 3.1 under dark and illumination.

17 The value of  $n$  larger than 2 can be related with the presence of recombination current through the

18 interface states. It is found that 100nm CdS nanowires/Au diode on 100nm SnO<sub>2</sub> has lower value

19 of  $n$  comparing with 100nm CdS film/Au diode on 175 nm SnO<sub>2</sub> substrate. Thus inclusion of

20 nanowires to form diode has lower recombination current through the interface states.

21

22

1

2

3 Figure 4, (a) : Current density (J) versus voltage V characteristics (b) : LnJ verse V characteristics of

4

5 100nm CdS nanowires/Au Schottky diodes on 100nm SnO<sub>2</sub> substrate.

6

7

8 It is seen that reverse saturation current density  $J_o$  gives considerably low values of  $6.9 \times 10^{-5}$

9

10 A/cm<sup>2</sup> and  $8.0 \times 10^{-5}$  A/cm<sup>2</sup> in the light and the dark respectively. Compared with  $J_o$  of 100nm CdS

11 film diodes,  $J_o$  of 100nm nanowire diodes is significantly reduced by three orders of magnitude in

12 the dark and two orders of magnitude in the light. According to equation 1 (a) and (b),  $J_o$  is

13 dependent on Richardson constant, temperature and barrier height. Due to same materials used for

14 CdS film and CdS nanowires and all of the measurements at room temperature, equation 1(a) gives

15 same value of  $J_o$  for CdS film and nanowire diodes when electron thermionic emission current

16 dominates.

17

18

$$J = J_0 \left[ \exp\left(\frac{q(V - JR_s)}{nkT}\right) - 1 \right] \quad \text{Equation 1(a)}$$

$$J_0 = A^* T^2 e^{-\Phi_B/KT} \quad \text{Equation 1(b)}$$

33 where  $A^*$  is the effective Richardson constant and  $\Phi_B$  is barrier height.

34

35

36 It is highly possible that transport mechanism in these diodes is not purely thermionic emission.

37

38 The possible phenomenon that explains the enormous difference of  $J_o$  between CdS film and

39 nanowire diodes includes tunneling current and recombination current by traps. Tunneling through

40 pinholes of CdS film to SnO<sub>2</sub>/ITO substrate and defect recombination in CdS films become

41 dominated current transport mechanism. CdS nanowires have significantly low defect features and

42 uniformly and densely distribution. Very low  $J_o$  in CdS nanowire diodes indicates that tunneling

43 current and recombination by trap are strongly suppressed due to low defect feature of nanowires.

44

45

46 It is found (table 1) that series resistance and shunt resistance of CdS nanowire diodes are 1.37

47 Ω/cm<sup>2</sup> and 24.4 Ω/cm<sup>2</sup> under illumination and corresponding values are 1.58 Ω/cm<sup>2</sup> and 30.8

48 Ω/cm<sup>2</sup> under dark condition.

49

50

$\Omega/cm^2$  in the dark. Shunt resistance of CdS nanowire diode is significantly enhanced by 70 times when comparing with shunt resistance of 100nm CdS film diode. This widely difference of shunt resistance could be related with the fact that CdS nanowires considerably reduces shunt paths and hence improve diode properties, contributing to high shunt resistance.

Table 1 also lists that CdS nanowire diode has higher series resistance than that of CdS film diodes. It is possible that large shunt current flows through shunt paths in CdS film, leading to obvious increase in total current and impact and lower extracted value of series resistance for CdS film diodes. However such phenomenon is avoided in CdS nanowire diodes. The extracted high series resistance of CdS nanowire diodes may be attributed to the contact resistance between Au and AAO matrix. As a result, CdS nanowires significantly improves the diode properties without need to increase thickness of  $SnO_2$ .

Figure 5, (a): Current density ( $J$ ) versus voltage  $V$  characteristics (b):  $LnJ$  verse  $V$  characteristics of 200nm CdS nanowires/Au Schottky diodes on 100nm  $SnO_2$  substrate.

CdS nanowires with 200nm length is configured into a Schottky diode to investigate effect of nanowire length on diode properties. Figure 5 (a) and (b) show J-V and extracted  $ln(J)$ -V curves of 200nm CdS nanowires/Au diode on 100nm  $SnO_2$  substrate. Observed from Figure 4(a) and 5(a), nanowires with longer length shows higher current density and current density under illumination

1

2

3 and in the dark demonstrates larger difference than that of 100nm nanowire diodes. It can be

4 assumed that more electron-hole pairs are generated due to longer length of nanowires under

5 illumination. The difference between 100nm CdS nanowire and 200nm nanowire diodes is the

6 diode ideality factor, series and shunt resistance. The diode with longer length nanowires reduce

7 diode ideality factor to 2.2 and 2.6 in the dark and illumination, suggesting that longer nanowires

8 may be related with reduced interface states of junctions. Extracted series resistance is decreased

9 and extracted shunt resistance is simultaneously enhanced, which may be caused by spatial

10 inhomogeneities at the longer CdS nanowires and Au interface. As a consequence, the diodes

11 configured by CdS nanowires with 100nm length demonstrate the optimal diode behavior and

12 properties without need to increase length of nanowires and  $\text{SnO}_2$  thickness.

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

#### **2.4 Simulation of CdS nanowire and film Schottky Diode**

29

30 In order to understand carrier transport mechanisms which impact difference between the

31 nanowire and film diode behaviors, simulation of J-V characteristics of CdS nanowire and film

32 diodes in the light and dark were performed by SCAPS software [1]. By fitting simulated J-V with

33 measured J-V, numerical models of CdS nanowire and film diodes were established.

34

35

36

37

38

39

40

##### ***Simulation of CdS nanowires/Au Diode***

41 Table 2 show parameters to simulate the measured J-V curves of the 100nm nanowire CdS/Au

42 diodes. In this simulation, thickness of CdS nanowires is 100nm, and energy band gap is 3.5eV

43 and measured nanowire CdS absorption data was used to simulate CdS absorption spectrum.

44 Simulation found that shallow donor (doping) concentration of CdS nanowires affects diode

45 properties and mainly impacts diode current. Increase in shallow donor concentration considerably

46 increases current at applied bias. Acceptor traps compensate free carrier density and space charge

47

48

49

50

51

52

53

54

55

56

57

58

59

60

in CdS nanowires. Simulation demonstrates that due to its large energy bandgap, the acceptor traps in the CdS nanowires have non-significant influence on diode J-V characteristics. It is found that interface states are a key parameter which impact diode properties. It is acceptor type interface states rather than donor type interface states that play a role on diode behavior. Reducing acceptor interface states is found to improve reverse saturation current. Series resistance and shunt resistance are included into the simulation model, demonstrating strong influence on diode J-V curves, mainly on J-V curves under the reverse bias and the high forward bias.

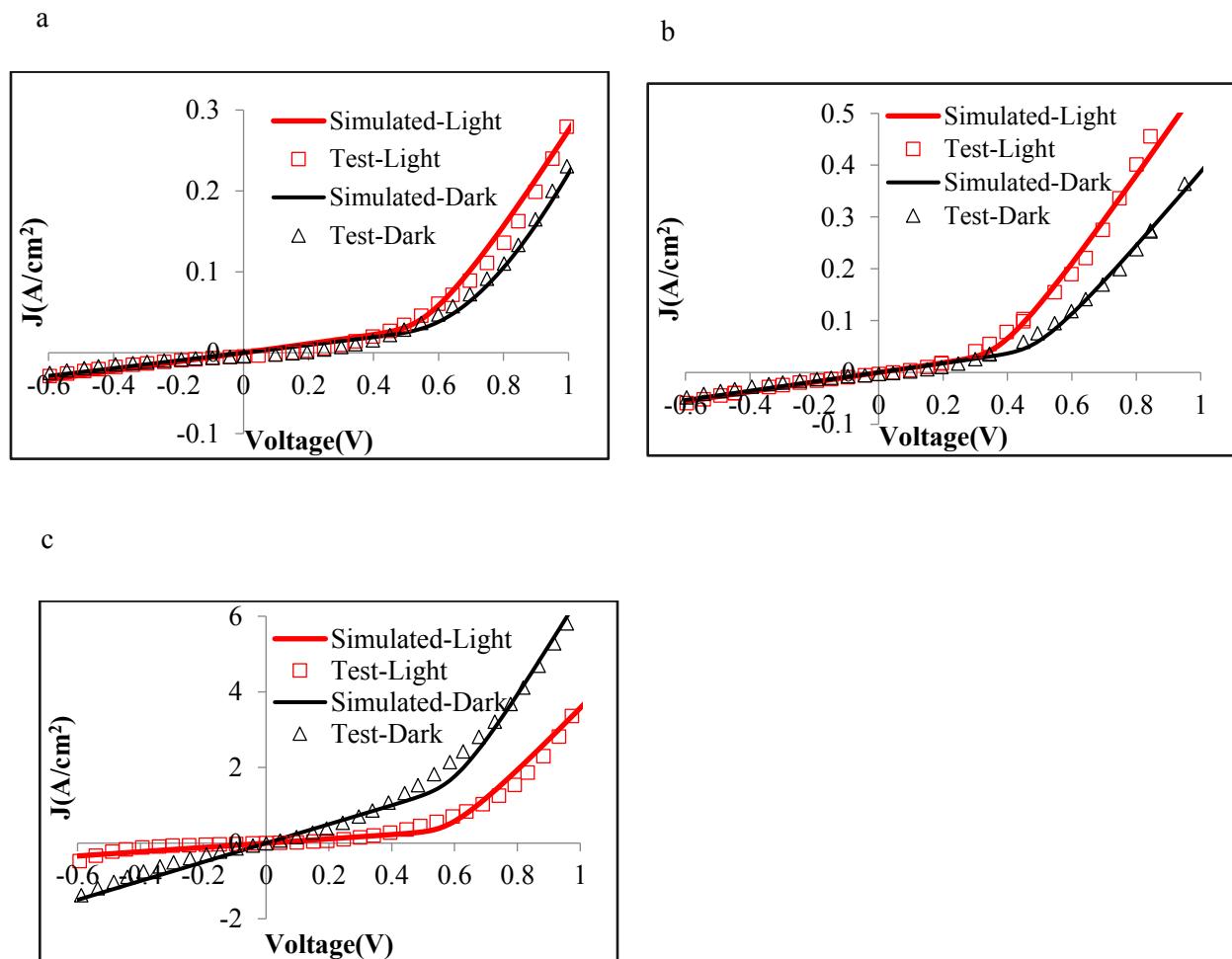

Figure 6, Light and dark simulated and measured current density ( $J$ ) versus voltage ( $V$ ) characteristics curves of (a): 100nm CdS nanowires/Au diode on 100nm  $\text{SnO}_2$  substrate (b): 200nm CdS nanowires/Au diode on 100nm  $\text{SnO}_2$  substrate. (c): 100nm CdS film/Au diode on 175 nm  $\text{SnO}_2$  substrate

In order to fit the J-V curve of 100nm CdS nanowire diodes in the dark, shallow donor concentration of CdS nanowires was adjusted to  $6.0 \times 10^{16} / \text{cm}^3$  and compensating acceptor type traps are located in the middle gap (1.75eV) of CdS nanowires and are introduced with density of  $5.5 \times 10^{15} / \text{cm}^3$ . To realize a better correspondence between the simulated and measured curves, acceptor interface trap density was tuned to  $5.0 \times 10^9 / \text{cm}^2$  where the acceptor interface traps are uniform distribution, located in the 1.5eV above valence band  $E_V$ . Low interface state density indicates interface recombination current isn't a dominated current transport mechanism in the nanowire diodes. Corresponding light J-V curve was simulated including slightly increased shallow donor concentration and slightly decreased acceptor type traps in CdS nanowires, which conform to data analysis above. In the simulation model, interface states and series and shunt resistances demonstrated similar values for simulated dark and light curves, suggesting that light has approximately negligible impact on interface recombination and shunt current.

Figure 6 (a) shows the simulated and measured J-V curves of 100nm CdS nanowire diodes in the dark and the light. In the figure, dotted lines are measured curves and solid lines are simulated curves. As shown in the Figure 6(a), simulated JV curve fits well with measured J-V curve. When voltage is less than 0.2V, simulated J-V curve slightly deviates from measured J-V curve. In the simulation model, a linear distribution of accept traps in the middle gap was assumed. However, these traps may not be linear distribution in the CdS nanowires. There is a slight difference when supply voltage is larger than 0.7V in the light curve. It is caused by series resistance. The nanowire diode samples have higher series resistance which is accord with data analysis above.

200nm nanowire CdS diodes were simulated and simulated J-V curves and parameters are shown in Figure 6 (b) and table 2 respectively. Shallow donor (doping) concentration of CdS nanowires was increased to  $4.0 \times 10^{17} / \text{cm}^3$  (dark) and  $6.0 \times 10^{17} / \text{cm}^3$  (light) in order to fit current

increase observed in the 200nm nanowire CdS diodes. The simulation model found that there are no obviously change of acceptor trap concentration. It can be deduced that nanowire length may have slight impact on defect recombination. Interface density between CdS nanowire/SnO<sub>2</sub> is increased and shunt resistance is obviously reduced in the model, which agree with experimental analysis above. Simulation shows that junction formation may be more challenging in longer nanowires.

Table 2: Simulated parameters used in CdS diodes

| Diode                                                         | Test Condition | Layer                                      | Shallow Donor Doping Density     | Trap Type and Trap Level                  | Trap Density                     | Series Resistance( $\Omega \cdot \text{cm}^2$ ) | Shunt Resistance ( $\Omega \cdot \text{cm}^2$ ) |

|---------------------------------------------------------------|----------------|--------------------------------------------|----------------------------------|-------------------------------------------|----------------------------------|-------------------------------------------------|-------------------------------------------------|

| <b>100nm CdS nanowires/ Au Diode on 100nm SnO<sub>2</sub></b> | Light          | CdS Nanowires                              | $7.0 \times 10^{16}/\text{cm}^3$ | Acceptor Middle Gap $E_i = 1.75\text{eV}$ | $4.5 \times 10^{15}/\text{cm}^3$ | $2.7 \times 10^{-3}$                            | $5.0 \times 10^{-2}$                            |

|                                                               |                | Interface between CdS and SnO <sub>2</sub> |                                  | Acceptor Above $E_v + 1.5\text{eV}$       | $5.0 \times 10^9/\text{cm}^2$    |                                                 |                                                 |

|                                                               | Dark           | CdS Nanowires                              | $6.0 \times 10^{16}/\text{cm}^3$ | Acceptor Middle Gap $E_i = 1.75\text{eV}$ | $5.5 \times 10^{15}/\text{cm}^3$ | $2.8 \times 10^{-3}$                            | $5.5 \times 10^{-2}$                            |

|                                                               |                | Interface between CdS and SnO <sub>2</sub> |                                  | Acceptor Above $E_v + 1.5\text{eV}$       | $5.0 \times 10^9/\text{cm}^2$    |                                                 |                                                 |

| <b>200nm CdS nanowires/ Au Diode on 100nm SnO<sub>2</sub></b> | Light          | CdS Nanowires                              | $6.0 \times 10^{17}/\text{cm}^3$ | Acceptor Middle Gap $E_i = 1.75\text{eV}$ | $5.0 \times 10^{15}/\text{cm}^3$ | $3.2 \times 10^{-3}$                            | $3 \times 10^{-2}$                              |

|                                                               |                | Interface between CdS and SnO <sub>2</sub> |                                  | Acceptor Above $E_v + 1.5\text{eV}$       | $5.5 \times 10^9/\text{cm}^3$    |                                                 |                                                 |

|                                                               | Dark           | CdS Nanowires                              | $4.0 \times 10^{17}/\text{cm}^3$ | Acceptor Middle Gap $E_i = 1.75\text{eV}$ | $6.0 \times 10^{15}/\text{cm}^3$ | $3.9 \times 10^{-3}$                            | $3 \times 10^{-2}$                              |

|                                                               |                | Interface between CdS and SnO <sub>2</sub> |                                  | Acceptor Above $E_v + 1.5\text{eV}$       | $5.5 \times 10^9/\text{cm}^3$    |                                                 |                                                 |

| <b>100nm CdS film/Au Diode on</b>                             | Light          | CdS film                                   | $6.0 \times 10^{19}/\text{cm}^3$ | Acceptor Middle Gap $E_i = 1.2\text{eV}$  | $1.0 \times 10^{18}/\text{cm}^3$ | $3.0 \times 10^{-4}$                            | $5.0 \times 10^{-3}$                            |

|                                          |                                          |          |                           |                                        |                           |               |               |

|------------------------------------------|------------------------------------------|----------|---------------------------|----------------------------------------|---------------------------|---------------|---------------|

| 175nm<br>$\text{SnO}_2$                  |                                          |          |                           | Neutral<br>0.6eV above $E_v$           | $1.0*10^{18}/\text{cm}^3$ |               |               |

|                                          | Interface between CdS and $\text{SnO}_2$ |          |                           | Acceptor<br>Above $E_v$<br>+1.2eV      | $6.0*10^{11}/\text{cm}^3$ |               |               |

|                                          | Dark                                     | CdS film | $4.0*10^{19}/\text{cm}^3$ | Acceptor<br>Middle Gap $E_i$<br>=1.2eV | $5.0*10^{18}/\text{cm}^3$ | $2.0*10^{-4}$ | $1.0*10^{-3}$ |

|                                          |                                          |          |                           | Neutral<br>0.6eV above $E_v$           | $1.0*10^{19}/\text{cm}^3$ |               |               |

| Interface between CdS and $\text{SnO}_2$ |                                          |          |                           | Acceptor<br>Above $E_v$<br>+1.2eV      | $8.0*10^{11}/\text{cm}^3$ |               |               |

## 2.5 Simulation of CdS film/Au Diodes

Simulation was conducted on 100nm CdS film/Au diodes on 175nm  $\text{SnO}_2$  substrate to understand difference between nanowire and film diodes. Figure 5(c) shows the simulated and measured J-V curves of 100nm CdS nanowire diode in the dark and the light. In the simulation, energy band gap of CdS film is 2.4eV, and shallow donor concentration of  $4.0*10^{19}/\text{cm}^3$  and  $6.0*10^{19}/\text{cm}^3$  are introduced in CdS film layer to fit I-V curves in the dark and light respectively. Compared with the nanowire diodes, significantly increased donor concentration accounts for higher current density in the CdS film diodes. Acceptor traps in CdS film are increased to  $1.0*10^{18}/\text{cm}^3$ , which reveals that deep-level defect recombination is obviously enhanced in the CdS film diodes. Another neutral type defects are added into the model and they are located in 0.6eV above valence band of CdS film and have liner concentration of  $1.0*10^{18}/\text{cm}^3$ . Furthermore, simulation shows that interface state density is increased to  $8.0*10^{11}/\text{cm}^2$ , significantly increased by two order of magnitude and shunt resistance is reduced by one order of magnitude. The simulation agrees that a great amount of interface states exist between CdS film and  $\text{SnO}_2$  and higher concentration of shunt paths occur in CdS films than CdS nanowires.

As shown in Figure 6 (c), simulated J-V curves fit with measured J-V curves and slight

1

2

3 difference between simulated and measure curves occur at the bias of 0.5-0.7 V. It is possible that

4 other traps exist in the CdS film. Simulation model indicates that deep-level combination, interface

5 recombination and shun paths that combine together to impact J-V characteristics of CdS film

6 diodes. It is considered the CdS layer has small energy bandgap like 2.4eV and form poor quality

7 film, hence acceptor traps and defects in the CdS layer significantly reduce diode properties.

8 However, high energy bandgap of CdS nanowires and nanowire features lead to reduced interface

9 and defect recombination and tunneling, contributing to improved diode behavior.

10

11

12

13

14

15

16

17

18

19

### 3. Conclusion:

20

21 CdS nanowires are fabricated by AAO assisted deposition method and configured to form

22 diode structure. Electronic characterization and simulation are conducted to investigate transport

23 mechanism and diode properties of CdS nanowire/Au diodes and film/Au diodes as comparison.

24 100nm CdS film/ Au on 100nm SnO<sub>2</sub> substrate demonstrates like-resistor characteristics and

25 indicate that shunt transport dominates current transport mechanism. Effect of SnO<sub>2</sub> on J-V

26 Characteristics of CdS film/Au diode properties is studied and increase in SnO<sub>2</sub> thickness corrects

27 resistor behavior and shows rectification behavior. However, the effective reverse saturation

28 current density and shunt resistance are significantly high and low respectively, implying that

29 interface/defect recombination and shunt issues are main current transport mechanism.

30 Furthermore, thickness of CdS film on J-V characteristics of the diodes is investigated. Increasing

31 CdS film thickness to 200nm improved the reverse saturation current density ( $J_0$ ) by one order of

32 magnitude and however shunt resistance is low and maintain similar values with increasing SnO<sub>2</sub>

33 method, suggesting poor quality and intrinsic issues of CdS film. 100nm CdS nanowire/Au diodes

34 reduce reverse saturation current density  $J_0$  by three orders of magnitude in the dark and two orders

35 of magnitude in the light respectively and their shunt resistance is significantly enhanced by 70

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

1

2

3 times times when comparing with those of the CdS film diodes. This widely difference of shunt

4 resistance can be attributed to the fact that CdS nanowires considerably reduces shunt paths,

5 contributing to high shunt resistance. However, CdS nanowire diodes have higher series resistance,

6 it may be attributed to reduced shunt recombination currents and the contact resistance between

7 Au and AAO matrix.

8

9

10 SCAPS simulation was conducted to establish defect impact on these diode properties. The

11 simulation models fit well with measured J-V of these diodes. In the simulation model of 100nm

12 CdS nanowire diodes, shallow donor concentration is adjusted to  $6.0 \times 10^{16} / \text{cm}^3$ , and compensating

13 acceptor type traps with a liner distribution of  $5.5 \times 10^{15} / \text{cm}^3$  was introduced in CdS nanowires. It

14 is acceptor type interface states that impact diode properties and interface state density is tuned to

15  $5.0 \times 10^9 / \text{cm}^2$ . Low interface state density indicates that interface recombination current isn't a

16 dominated current transport mechanism in the 100nm nanowire diodes. Compared with simulated

17 100nm nanowire diodes, shallow donor concentration is are slightly increased and there are no

18 obviously change of interface density and acceptor trap concentration in 200nm CdS nanowires.

19 Simulation is conducted for CdS film diodes and compared with the nanowire diodes, significantly

20 increased donor concentration accounts for higher current density in the CdS film diodes. Acceptor

21 traps are significantly increased by two order of magnitude, and another neutral type defects which

22 are located in 0.6eV above valence band and have liner concentration of  $1.0 \times 10^{18} / \text{cm}^3$  are added

23 into the model, revealing that deep-level defect recombination becomes dominated. The interface

24 state density is significantly increased by two order of magnitude and shunt resistance is reduced

25 by one order of magnitude, indicating that a great amount of interface states exist between CdS

26 film and SnO<sub>2</sub> and high concentration of shunt paths occur in CdS film. Simulation model indicates

27 that deep-level combination, interface recombination and shun paths that combine together to

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

negatively impact J-V characteristics of CdS film diodes. The high energy bandgap and nanowire features of CdS nanowires significantly reduce interface states, defect recombination and tunneling, contributing to improved diode properties.

## Acknowledgements

This work was supported by grants from the National Science Foundation CREST: Center for Nanotechnology Research and Education at UDC (Award 1914751) and NASA MUREP Institutional Research Opportunity Grant under Cooperative Agreement #80NSSC19M0196.

## References

- [1] Y. Zhu, J. Chen, L. Shao, X. Xia, Y. Liu, and L. Wang, "Oriented facet heterojunctions on CdS nanowires with high photoactivity and photostability for water splitting," *Applied Catalysis B: Environmental*, vol. 268, p. 118744, 2020.

- [2] H.-R. Kim, B.-G. An, Y. W. Chang, M.-J. Kang, J.-G. Park, and J.-C. Pyun, "Highly sensitive in situ-synthesized cadmium sulfide (CdS) nanowire photosensor for chemiluminescent immunoassays," *Enzyme and microbial technology*, vol. 133, p. 109457, 2020.

- [3] A. Aristizábal and M. Mikan, "Optical properties of CDS films by analysis of spectral transmittance," *IOSR Journal of Applied Physics*, vol. 8, no. 4, pp. 24-31, 2016.

- [4] L. Huang, Z. Wei, F. Zhang, and X. Wu, "Electronic and optical properties of CdS films deposited by evaporation," *Journal of Alloys and Compounds*, vol. 648, pp. 591-594, 2015.

- [5] S. Navale, A. Mane, M. Chougule, N. Shinde, J. Kim, and V. Patil, "Highly selective and sensitive CdS thin film sensors for detection of NO<sub>2</sub> gas," *RSC Advances*, vol. 4, no. 84, pp. 44547-44554, 2014.

- [6] A. Fernández-Pérez *et al.*, "Modification of the junction parameters via Al doping in Ag/CdS: Al thin-film Schottky diodes for microwave sensors," *Materials Research Express*, vol. 8, no. 1, p. 016408, 2021.

1

2

3 [7] Z. Li *et al.*, "Self-powered perovskite/CdS heterostructure photodetectors," *ACS applied*

4 *materials & interfaces*, vol. 11, no. 43, pp. 40204-40213, 2019.

5

6 [8] Y. L. Song *et al.*, "White electroluminescence from a prototypical light-emitting diode based on

7 CdS/Si heterojunctions," *Materials Letters*, vol. 196, pp. 8-11, 2017.

8

9 [9] M. R. Perez *et al.*, "Hybrid CMOS thin-film devices based on solution-processed CdS n-TFTs

10 and TIPS-Pentacene p-TFTs," *Organic Electronics*, vol. 13, no. 12, pp. 3045-3049, 2012.

11

12 [10] X. Wu, "High-efficiency polycrystalline CdTe thin-film solar cells," *Solar energy*, vol. 77, no. 6,

13 pp. 803-814, 2004.

14

15 [11] H. Dang, V. P. Singh, S. Guduru, and J. T. Hastings, "Embedded nanowire window layers for

16 enhanced quantum efficiency in window-absorber type solar cells like CdS/CdTe," *Solar Energy*

17 *Materials and Solar Cells*, vol. 144, pp. 641-651, 2016.

18

19 [12] N. Akcay, E. Zaretskaya, and S. Ozcelik, "Development of a CZTS solar cell with CdS buffer

20 layer deposited by RF magnetron sputtering," *Journal of Alloys and Compounds*, vol. 772, pp.

21 782-792, 2019.

22

23 [13] D.-B. Li *et al.*, "Stable and efficient CdS/Sb<sub>2</sub>Se<sub>3</sub> solar cells prepared by scalable close space

24 sublimation," *Nano Energy*, vol. 49, pp. 346-353, 2018.

25

26 [14] G. Kartopu *et al.*, "Effect of window layer composition in Cd<sub>1-x</sub>Zn<sub>x</sub>S/CdTe solar cells,"

27 *Progress in Photovoltaics: Research and Applications*, vol. 22, no. 1, pp. 18-23, 2014.

28

29 [15] S. Guo *et al.*, "Tunable optical loss and multi-band photodetection based on tin doped CdS

30 nanowire," *Journal of Alloys and Compounds*, vol. 835, p. 155330, 2020.

31

32 [16] Z. Bai, M. Fu, and Y. Zhang, "Vertically aligned and ordered ZnO/CdS nanowire arrays for self-

33 powered UV-visible photosensing," *Journal of Materials Science*, vol. 52, no. 3, pp. 1308-1317,

34 2017.

35

36 [17] W. Zhang *et al.*, "Flexible piezoelectric nanogenerators based on a CdS nanowall for self-

37 powered sensors," *Nanotechnology*, vol. 31, no. 38, p. 385401, 2020.

38

39

40

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

1

2

3 [18] D. Zheng *et al.*, "High-performance ferroelectric polymer side-gated CdS nanowire ultraviolet

4 photodetectors," *Advanced Functional Materials*, vol. 26, no. 42, pp. 7690-7696, 2016.

5

6 [19] R.-M. Ma, L. Dai, H.-B. Huo, W.-J. Xu, and G. Qin, "High-performance logic circuits

7 constructed on single CdS nanowires," *Nano letters*, vol. 7, no. 11, pp. 3300-3304, 2007.

8

9 [20] T.-Y. Wei *et al.*, "Large enhancement in photon detection sensitivity via Schottky-gated CdS

10 nanowire nanosensors," *Applied Physics Letters*, vol. 96, no. 1, p. 013508, 2010.

11

12 [21] S. Du *et al.*, "CoSe<sub>2</sub> modified Se-decorated CdS nanowire Schottky heterojunctions for highly

13 efficient photocatalytic hydrogen evolution," *Chemical Engineering Journal*, vol. 389, p. 124431,

14 2020.

15

16 [22] M. Peng *et al.*, "Enhancement-mode CdS nanobelts field effect transistors and phototransistors

17 with HfO<sub>2</sub> passivation," *Applied Physics Letters*, vol. 114, no. 11, p. 111103, 2019.

18

19 [23] M. B. Alex Niemegeers, Koen Decock, Stefaan Degraeve, Johan Verschraegen,

20

21 <http://scaps.elis.ugent.be/>.

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60