#### PAPER · OPEN ACCESS

## The Phase-I trigger readout electronics upgrade of the ATLAS Liquid Argon calorimeters

To cite this article: G. Aad et al 2022 JINST 17 P05024

View the article online for updates and enhancements.

#### You may also like

- LOCALIZATION AND BROADBAND FOLLOW-UP OF THE GRAVITATIONAL-WAVE TRANSIENT GW150914 B. P. Abbott, R. Abbott, T. D. Abbott et al.

- <u>A new calibration method for charm jet</u> <u>identification validated with proton-proton</u> <u>collision events at *s* = 13 TeV</u> The CMS collaboration, Armen Tumasyan, Wolfgang Adam et al.

- <u>SUPPLEMENT: "LOCALIZATION AND</u> <u>BROADBAND FOLLOW-UP OF THE</u> <u>GRAVITATIONAL-WAVE TRANSIENT</u> <u>GW150914" (2016, ApJL, 826, L13)</u> B. P. Abbott, R. Abbott, T. D. Abbott et al.

### IOP ebooks<sup>™</sup>

Bringing together innovative digital publishing with leading authors from the global scientific community.

Start exploring the collection-download the first chapter of every title for free.

RECEIVED: *February 21, 2022* Accepted: *March 21, 2022* Published: *May 16, 2022*

# The Phase-I trigger readout electronics upgrade of the ATLAS Liquid Argon calorimeters

G. Aad,<sup>23</sup> A.V. Akimov,<sup>6,26</sup> K. Al Khoury,<sup>7</sup> M. Aleksa,<sup>6</sup> T. Andeen,<sup>3</sup> C. Anelli,<sup>37</sup> N. Aranzabal,<sup>6</sup> C. Armijo,<sup>2</sup> A. Bagulia,<sup>26</sup> J. Ban,<sup>7</sup> T. Barillari,<sup>27</sup> F. Bellachia,<sup>1</sup> M. Benoit,<sup>5</sup> F. Bernon,<sup>23</sup> A. Berthold,<sup>10</sup> H. Bervas,<sup>32</sup> D. Besin,<sup>32</sup> A. Betti,<sup>9</sup> Y. Bianga,<sup>10</sup> M. Biaut,<sup>23</sup> D. Boline,<sup>33</sup> J. Boudreau,<sup>30</sup> T. Bouedo,<sup>1</sup> N. Braam,<sup>37</sup> M. Cano Bret,<sup>18</sup> G. Brooijmans,<sup>7</sup> H. Cai,<sup>30</sup> C. Camincher,<sup>6,37</sup> A. Camplani,<sup>16,39</sup> S. Cap,<sup>1</sup> A. Carbone,<sup>16</sup> J.W.S. Carter,<sup>35</sup> S.V. Chekulaev, <sup>36,26</sup> H. Chen,<sup>5</sup> K. Chen,<sup>5</sup> N. Chevillot,<sup>1</sup> M. Citterio,<sup>16</sup> B. Cleland,<sup>30,†</sup> M. Constable,<sup>36</sup> S. de Jong,<sup>37</sup> A.M. Deiana,<sup>9</sup> M. Delmastro,<sup>1</sup> B. Deng,<sup>9</sup> H. Deschamps,<sup>32</sup> C. Diaconu,<sup>23</sup> A. Dik,<sup>26</sup> B. Dinkespiler,<sup>23</sup> N. Dumont Dayot,<sup>1</sup> A. Emerman,<sup>7</sup> Y. Enari,<sup>34</sup> P.J. Falke,<sup>1,38</sup> J. Farrell,<sup>5</sup> W. Fielitz,<sup>5</sup> E. Fortin,<sup>23</sup> J. Fragnaud,<sup>1</sup> S. Franchino,<sup>14</sup> L. Gantel,<sup>1</sup> K. Gigliotti,<sup>2</sup> D. Gong,<sup>9</sup> A. Grabas,<sup>32</sup> P. Grohs,<sup>10</sup> N. Guettouche,<sup>23</sup> T. Guillemin,<sup>1</sup> D. Guo,<sup>9</sup> J. Guo,<sup>13</sup> L. Hasley,<sup>9</sup> C. Hayes,<sup>33,40</sup> R. Hentges,<sup>10</sup> L. Hervas,<sup>6</sup> M. Hils,<sup>10</sup> J. Hobbs,<sup>33</sup> A. Hoffman,<sup>5</sup> D. Hoffmann,<sup>23</sup> P. Horn,<sup>10</sup> T. Hryn'ova,<sup>1</sup> L. Iconomidou-Fayard,<sup>15</sup> R. Iguchi,<sup>34</sup> T. James,<sup>9</sup> J. Ye,<sup>9</sup> K. Johns,<sup>2</sup> T. Junkermann,<sup>14</sup> C. Kahra,<sup>22</sup> E.F. Kay,<sup>37</sup> R. Keeler,<sup>37</sup> S. Ketabchi Haghighat,<sup>35</sup> P. Kinget,<sup>8</sup> E. Knoops,<sup>23</sup> A. Kolbasin,<sup>26</sup> P. Krieger,<sup>35</sup> J. Kuppambatti,<sup>8</sup> L.L. Kurchaninov,<sup>36</sup> E. Ladygin,<sup>19</sup> S. Lafrasse,<sup>1</sup> M.P.J. Landon,<sup>21</sup> F. Lanni,<sup>5</sup> S. Latorre,<sup>16</sup> D. Laugier,<sup>23</sup> M. Lazzaroni,<sup>16,17</sup> X. Le,<sup>9</sup> P. Le Bourlout,<sup>32</sup> C.A. Lee,<sup>5</sup> M. Lefebvre,<sup>37</sup> M.A.L. Leite,<sup>20</sup> C. Leroy,<sup>25</sup> X. Li,<sup>9</sup> Z. Li,<sup>23,12</sup> F. Liang,<sup>9</sup> H. Liu,<sup>5</sup> C. Liu,<sup>9</sup> T. Liu,<sup>9</sup> H. Ma,<sup>5</sup> L.L. Ma,<sup>12</sup> D.J. Mahon,<sup>7</sup> U. Mallik,<sup>18</sup> B. Mansoulie,<sup>32</sup> A.L. Maslennikov,<sup>28,29</sup> N. Matsuzawa,<sup>34</sup> R.A. McPherson,<sup>37,a</sup> S. Menke,<sup>27</sup> A. Milic,<sup>35,6</sup> Y. Minami,<sup>34</sup> E. Molina,<sup>32</sup> E. Monnier,<sup>23</sup> N. Morange,<sup>15</sup> L. Morvaj,<sup>6,33</sup> J. Mueller,<sup>30</sup> C. Mwewa,<sup>5</sup> R. Narayan,<sup>9</sup> N. Nikiforou,<sup>3,6</sup> I. Ochoa,<sup>7,41</sup> R. Oishi,<sup>34</sup> D. Oliveira Damazio,<sup>5</sup> R.E. Owen,<sup>31</sup> C. Pancake,<sup>33</sup> D.K. Panchal,<sup>3</sup> G. Perrot,<sup>1</sup> M.-A. Pleier,<sup>5,\*</sup> P. Poffenberger,<sup>37,†</sup> R. Porter,<sup>37</sup> S. Quan,<sup>9</sup> J. Rabel,<sup>30</sup> A. Roy,<sup>3</sup> J.P. Rutherfoord,<sup>2</sup> F. Sabatini,<sup>16</sup> F. Salomon,<sup>23</sup> E. Sauvan,<sup>1</sup> A.C. Schaffer,<sup>15</sup> R.D. Schamberger, <sup>33</sup> Ph. Schwemling, <sup>32</sup> C. Secord, <sup>37</sup> L. Selem, <sup>1</sup> K. Sexton, <sup>5,†</sup> E. Shafto, <sup>33</sup> M.V. Silva Oliveira,<sup>6</sup> S. Simion,<sup>15</sup> S. Singh,<sup>35</sup> W. Sippach,<sup>7</sup> A.A. Snesarev,<sup>26</sup> S. Snyder,<sup>5</sup> M. Spalla,<sup>27</sup> S. Stärz,<sup>6,24</sup> A. Straessner,<sup>10</sup> P. Strizenec,<sup>4</sup> R. Stroynowski,<sup>9</sup> V.V. Sulin,<sup>26</sup> J. Tanaka,<sup>34</sup> S. Tang,<sup>5</sup> S. Tapprogge,<sup>22</sup> G.F. Tartarelli,<sup>16</sup> G. Tateno,<sup>34</sup> K. Terashi,<sup>34</sup> S. Tisserant,<sup>23</sup> D. Tompkins,<sup>2</sup> G. Unal,<sup>6</sup> M. Unal,<sup>3</sup> K. Uno,<sup>34</sup> A. Vallier,<sup>6,23</sup> S. Vieira de Souza,<sup>22</sup> R. Walker,<sup>2</sup> Q. Wang,<sup>7</sup> C. Wang,<sup>23,13</sup> R. Wang,<sup>22</sup> M. Wessels,<sup>14</sup> I. Wingerter-Seez,<sup>1</sup> K. Wolniewicz,<sup>5</sup> W. Wu,<sup>5,13</sup> Z. Xiandong,<sup>9</sup> R. Xu,<sup>3</sup> H. Xu,<sup>5</sup> S. Yamamoto,<sup>34</sup> Y. Yang,<sup>34</sup> H. Zaghia,  $^{32}$  J. Zang,  $^{34}$  T. Zhang,  $^{34}$  H.L. Zhu,  $^{5,11}$  V. Zhulanov,  $^{28,29}$  E. Zonca  $^{32,\dagger}$  and G. Zuk $^{30}$

<sup>†</sup>Deceased.

<sup>&</sup>lt;sup>a</sup>Also at Institute of Particle Physics (IPP); Canada.

<sup>\*</sup>Corresponding author.

<sup>© 2022</sup> CERN. Published by IOP Publishing Ltd on behalf of Sissa Medialab. Original content from this work may be used under the terms of the Creative Commons Attribution 4.0 licence. Any further distribution of this work must maintain attribution to the author(s) and the title of the work, journal citation and DOI.

- <sup>1</sup>LAPP, Univ. Savoie Mont Blanc, CNRS/IN2P3, Annecy, France <sup>2</sup>Department of Physics, University of Arizona, Tucson, AZ, United States of America <sup>3</sup>Department of Physics, University of Texas at Austin, Austin, TX, United States of America <sup>4</sup>Department of Subnuclear Physics, Institute of Experimental Physics of the Slovak Academy of Sciences, Kosice, Slovak Republic <sup>5</sup>Physics Department, Brookhaven National Laboratory, Upton, NY, United States of America <sup>6</sup>CERN, Geneva, Switzerland <sup>7</sup>Nevis Laboratory, Columbia University, Irvington, NY, United States of America <sup>8</sup>Department of Electrical Engineering, Columbia University, New York, NY, United States of America <sup>9</sup>Physics Department, Southern Methodist University, Dallas, TX, United States of America <sup>10</sup>Institut für Kern- und Teilchenphysik, Technische Universität Dresden, Dresden, Germany <sup>11</sup>Department of Modern Physics and State Key Laboratory of Particle Detection and Electronics, University of Science and Technology of China, Hefei, China <sup>12</sup>Institute of Frontier and Interdisciplinary Science and Key Laboratory of Particle Physics and Particle Irradiation (MOE), Shandong University, Qingdao, China <sup>13</sup>School of Physics and Astronomy, Shanghai Jiao Tong University, Key Laboratory for Particle Astrophysics and Cosmology (MOE), SKLPPC, Shanghai, China <sup>14</sup>Kirchhoff-Institut für Physik, Ruprecht-Karls-Universität Heidelberg, Heidelberg, Germany <sup>15</sup> IJCLab, Université Paris-Saclay, CNRS/IN2P3, 91405, Orsay, France <sup>16</sup>INFN Sezione di Milano, Milano, Italy <sup>17</sup>Dipartimento di Fisica, Università di Milano, Milano, Italy <sup>18</sup>University of Iowa, Iowa City, IA, United States of America <sup>19</sup>Joint Institute for Nuclear Research, Dubna, Russia <sup>20</sup>Instituto de Física, Universidade de São Paulo, São Paulo, Brazil <sup>21</sup>School of Physics and Astronomy, Queen Mary University of London, London, United Kingdom <sup>22</sup>Institut für Physik, Universität Mainz, Mainz, Germany <sup>23</sup>CPPM, Aix-Marseille Université, CNRS/IN2P3, Marseille, France <sup>24</sup>Department of Physics, McGill University, Montreal, QC, Canada <sup>25</sup>Group of Particle Physics, University of Montreal, Montreal, QC, Canada <sup>26</sup>P.N. Lebedev Physical Institute of the Russian Academy of Sciences, Moscow, Russia <sup>27</sup>Max-Planck-Institut für Physik (Werner-Heisenberg-Institut), München, Germany <sup>28</sup>Budker Institute of Nuclear Physics and NSU, SB RAS, Novosibirsk, Russia <sup>29</sup>Novosibirsk State University Novosibirsk, Russia <sup>30</sup>Department of Physics and Astronomy, University of Pittsburgh, Pittsburgh, PA, United States of America <sup>31</sup>Particle Physics Department, Rutherford Appleton Laboratory, Didcot, United Kingdom <sup>32</sup>IRFU, CEA, Université Paris-Saclav, Gif-sur-Yvette, France <sup>33</sup>Departments of Physics and Astronomy, Stony Brook University, Stony Brook, NY, United States of America <sup>34</sup>International Center for Elementary Particle Physics and Department of Physics, University of Tokyo, Tokyo, Japan <sup>35</sup>Department of Physics, University of Toronto, Toronto, ON, Canada

- <sup>36</sup>TRIUMF, Vancouver, BC, Canada

- <sup>37</sup>Department of Physics and Astronomy, University of Victoria, Victoria, BC, Canada

- <sup>38</sup>Physikalisches Institut, Universität Bonn, Bonn, Germany

- <sup>39</sup>Niels Bohr Institute, University of Copenhagen, Copenhagen, Denmark

<sup>40</sup>Department of Physics, University of Michigan, Ann Arbor, MI, United States of America

<sup>41</sup>Laboratório de Instrumentação e Física Experimental de Partículas — LIP, Lisboa, Portugal

*E-mail:* pleier@bnl.gov

ABSTRACT: The Phase-I trigger readout electronics upgrade of the ATLAS Liquid Argon calorimeters enhances the physics reach of the experiment during the upcoming operation at increasing Large Hadron Collider luminosities. The new system, installed during the second Large Hadron Collider Long Shutdown, increases the trigger readout granularity by up to a factor of ten as well as its precision and range. Consequently, the background rejection at trigger level is improved through enhanced filtering algorithms utilizing the additional information for topological discrimination of electromagnetic and hadronic shower shapes. This paper presents the final designs of the new electronic elements, their custom electronic devices, the procedures used to validate their proper functioning, and the performance achieved during the commissioning of this system.

KEYWORDS: Calorimeters; Electronic detector readout concepts (gas, liquid); Front-end electronics for detector readout; Radiation-hard electronics

ArXiv ePrint: 2202.07384

#### Contents

| 1 | Intr | oductio | on                                        | 1  |

|---|------|---------|-------------------------------------------|----|

| 2 | Ove  | rview o | f the LAr readout electronics             | 2  |

| 3 | New  | Front-  | -End electronics                          | 7  |

|   | 3.1  | Basep   | lanes                                     | 7  |

|   | 3.2  | Layer   | Sum Boards                                | 9  |

|   | 3.3  | LAr T   | rigger Digitizer Boards                   | 10 |

|   |      | 3.3.1   | Analog-to-Digital Converter               | 11 |

|   |      | 3.3.2   | Serializer and optical transmitter        | 13 |

|   |      | 3.3.3   | Motherboard                               | 15 |

|   |      | 3.3.4   | Power distribution board                  | 18 |

|   |      | 3.3.5   | Quality assurance and control             | 19 |

|   |      | 3.3.6   | Compatibility with Phase-II upgrade       | 21 |

| 4 | New  | 22      |                                           |    |

|   | 4.1  | LAr c   | arrier                                    | 22 |

|   | 4.2  | LAr tr  | rigger processing mezzanine               | 25 |

|   | 4.3  | Intelli | gent platform management controller       | 26 |

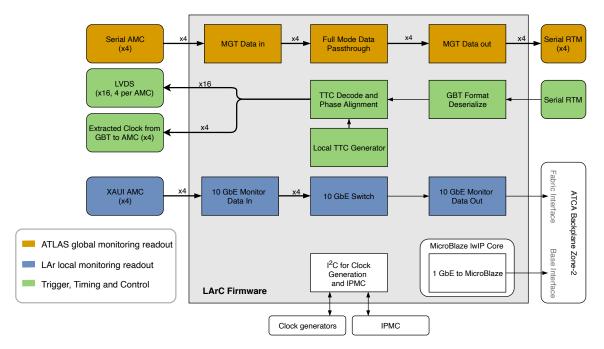

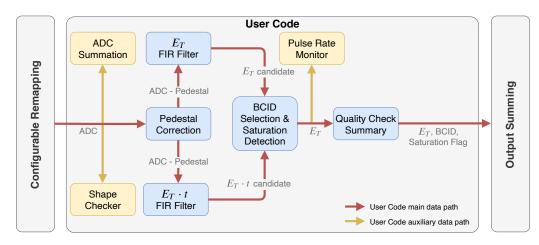

|   | 4.4  | Back-   | End firmware                              | 27 |

|   |      | 4.4.1   | LAr carrier firmware                      | 27 |

|   |      | 4.4.2   | LAr trigger processing mezzanine firmware | 30 |

| 5 | Inte | 37      |                                           |    |

|   | 5.1  | Front-  | End boards integration tests              | 37 |

|   | 5.2  | Back-   | End boards integration tests              | 38 |

|   | 5.3  | Full cl | hain tests                                | 41 |

|   | 5.4  | Syster  | n latency                                 | 45 |

| 6 | Con  | clusion | I                                         | 47 |

#### **1** Introduction

During the second Large Hadron Collider (LHC) Long Shutdown (LS2), the Liquid Argon (LAr) calorimeters of the ATLAS experiment have been equipped with new trigger readout electronics [1], which provides digital information to the ATLAS trigger system [2]. The purpose of this so-called Phase-I upgrade is to enhance the physics reach of the experiment during the upcoming operation at increasing LHC luminosities. ATLAS ran in the Run 2 data taking period (years 2015–2018) at a

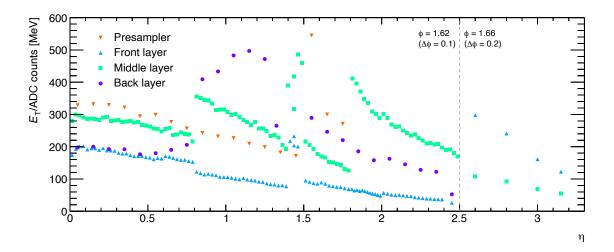

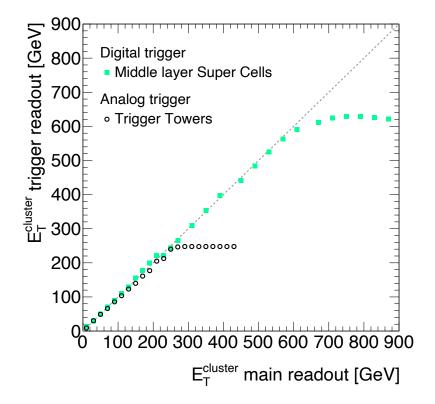

typical maximum instantaneous luminosity of  $1.9 \times 10^{34}$  cm<sup>-2</sup> s<sup>-1</sup> and with an average mean number of proton-proton interactions of  $\langle \mu \rangle = 33$  [3]. During Run 3 (years 2022–2025) the instantaneous luminosity was originally expected to increase to a peak value of  $3 \times 10^{34}$  cm<sup>-2</sup> s<sup>-1</sup>, with  $\langle \mu \rangle \approx 80$  [1]. The updated LHC plan for Run 3 targets a beam intensity increase of 50% compared to Run 2 with a luminosity leveled to  $2 \times 10^{34}$  cm<sup>-2</sup> s<sup>-1</sup> over periods up to 12 hours. The center-of-mass energy will also be raised from  $\sqrt{s} = 13$  TeV to 13.6 TeV. These changes will result in an overall detector occupancy increase, while the first level trigger (L1) bandwidth will remain at 100 kHz during Run 3. If the currently used LAr trigger readout system, referred to as *legacy* trigger readout in the following, were to remain unchanged, the transverse energy  $(E_T)$  trigger thresholds would need to be raised, degrading the physics performance. To avoid this efficiency loss and enhance the physics reach of the experiment in Run 3 and beyond, the new system installed during LS2 increases the readout granularity by up to a factor of ten: instead of summing the  $E_{\rm T}$  of calorimeter cells in areas as small as  $\Delta \eta \times \Delta \phi = 0.1 \times 0.1$  to form the so-called *Trigger Towers* of the legacy readout, additional lateral and longitudinal segmentation is introduced to form smaller clusters called Super Cells. Trigger Towers are typically split longitudinally into four layers, and some layers are split laterally along  $\eta$ into four strips each. One Super Cell can thus cover an area as small as  $\Delta \eta \times \Delta \phi = 0.025 \times 0.1$ , depending on which longitudinal layer it is located in. In addition, the precision and range of the  $E_{\rm T}$  measurement is also increased. Consequently, the background rejection at trigger level is improved due to better filtering algorithms being possible already at L1, based on topological discrimination between electromagnetic shower shapes and hadronic activity. In particular, the resulting electron, photon and tau lepton identification is more efficient. Furthermore, thanks to more advanced reconstruction algorithms and better pile-up subtraction techniques, the energy resolution for electromagnetic, jet and missing  $E_{\rm T}$  objects is improved, leading to a sharper rise of the per-event trigger efficiency toward its plateau value.

The Phase-I upgrade project is part of a broad upgrade program of the LAr calorimeters through the lifetime of the LHC and is fully compatible with the future Phase-II upgrade program of the ATLAS experiment planned for the third Long Shutdown (LS3) in 2026–2028.

This paper presents the new system, initially proposed in Reference [1] and installed during LS2, together with its performance. The final designs of the new electronic boards and their Application-Specific Integrated Circuits (ASICs) are described as well as the procedures used to validate their proper functioning. The basic performance achieved during the commissioning of this system is also presented. In section 2, the legacy readout electronics is briefly recapitulated and the new trigger readout electronics is introduced, as are the new data paths. The new electronics installed on the ATLAS detector (Front-End) and off the detector (Back-End) is described in sections 3 and 4, respectively. Finally, the integration tests performed to validate the full chain of this new readout electronics are reported in section 5 before the conclusions are presented in section 6.

#### 2 Overview of the LAr readout electronics

The readout electronics of the LAr calorimeters is designed to record energies approximately ranging from 50 MeV to 3 TeV, measured in 182418 calorimeter cells. The energy resolution of the calorimeter for electromagnetic showers can be written as  $\sigma_E/E = a/\sqrt{E} \oplus b \oplus c/E$ , with an intrinsic sampling term *a* that is typically 10–11%  $\sqrt{\text{GeV}}$  [4, 5], a constant term *b* that is 1–2% [6],

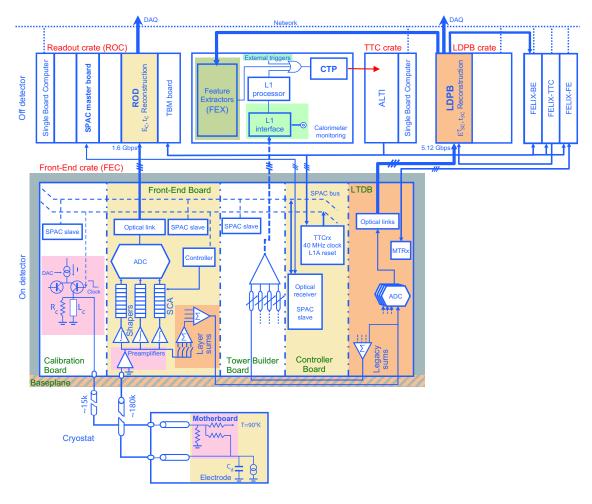

**Figure 1.** The ATLAS LAr calorimeter electronic architecture as of LHC Run 3. The new LAr boards are highlighted in orange. This diagram depicts the EM calorimeters; HEC and FCal electronics are slightly different.

and a noise term *c* that is 10–600 MeV without pile-up contribution [7] and is expected to be 30 MeV–3 GeV in Run 3 pile-up conditions [1], depending on the pseudorapidity region considered (up to  $|\eta| < 3.2$ ). The triangular pulse coming from the ionization in a LAr cell is shaped into a bipolar pulse that is sampled at 40 MHz. The digitized samples are read at the L1 trigger rate, that can go up to 100 kHz. The LAr calorimeter system is composed of four different components: the electromagnetic barrel (EMB) and end-caps (EMEC), both referred to as EM calorimeters; the hadronic end-cap (HEC); and the forward calorimeter (FCal). These components are divided in two sides, A and C, oriented respectively along the positive and negative *z*-axis of the experiment. The LAr readout electronics is divided into a Front-End and a Back-End system, both interconnected by cables and optical fibers as shown in figure 1.

The Front-End system is composed of 58 Front-End Crates (FECs), each hosting at most two baseplanes which interconnect the following legacy system boards:

**Front-End Boards (FEBs):** process typically 128 channels, each in a specific longitudinal layer of the calorimeter. They amplify, shape, sample and digitize the ionization signals and transmit

them to the Back-End readout. The analog sums needed for the trigger system are also prepared by the Linear Mixers and the Layer Sum Boards (LSBs), both hosted on the FEBs. The Linear Mixer electronics is part of the shaper chip located on the FEB motherboard, while the LSB is a plug-in card connected to the Linear Mixer.

- **Tower Builder Boards (TBBs):** form the legacy Trigger Towers from the analog sums provided by the LSBs over the FEC baseplanes. The Trigger Tower analog signals are sent to the L1 trigger system via copper cables. In the HEC and FCal no further sums need to be produced after the LSB. Therefore, Tower Driver Boards (TDBs) are used in place of TBBs.

- **Calibration Boards:** inject current calibration pulses whose shape is close to the pulse generated from the LAr ionization signal.

- **Controller Boards:** receive the configuration and monitoring commands from the Serial Protocol for Atlas Calorimeter [8] (SPAC) masters installed in the Back-End Readout Crates. Controller boards receive also the Timing Trigger and Control [9] (TTC) signals coming from the Back-End TTC crates. They distribute the SPAC and TTC commands to the other legacy boards in the FEC.

Some FECs also host monitor boards transmitting the information from the sensors measuring possible mechanical stresses of the detector and the LAr temperature and purity. Another function of some of the monitor boards is to measure the status of the FECs' low-voltage power supplies. Each electronic board in a FEC is conductively cooled using two aluminium plates placed on each side of the board. These aluminium plates are part of a leak-less water cooling system.

On the Back-End side, two legacy systems are present:

- **Readout Crates (ROCs):** Versa Module Eurocard (VME) crates hosting Readout Driver boards (RODs) that read the Analog-to-Digital Converter (ADC) data sent by the FEBs and compute energy ( $E_C$ ) and time ( $t_C$ ) for each cell signal at the L1 trigger rate. The ROCs also house the SPAC master boards and the Trigger Busy Modules (TBMs). The latter collect the busy signals from the RODs and distribute the TTC signals.

- **TTC crates:** VME crates containing the modules that receive the TTC commands from the ATLAS Central Trigger Processor (CTP) system or generate locally these commands and transmit them to the other LAr boards.

The LAr electronics upgrade extends the legacy system with new Front-End components, sending the Super Cells' digital data to new Back-End components, which compute and transmit the Super Cells'  $E_T$  to the new trigger system. The architecture as of Run 3 is illustrated in figure 1. This new LAr trigger readout system is composed of new Layer Sum Boards providing the analog sums for the higher trigger readout granularity; new baseplanes to route the increased number of analog signals and host the new LAr Trigger Digitizer Boards (LTDBs) that digitize the Super Cell analog signals at 40 MHz and provide the legacy sums for the TBBs; and new Back-End boards, the LAr Digital Processing Blades (LDPBs), that read the Super Cell ADC signals from the LTDBs, compute the Super Cells'  $E_T$  and send them to the new L1 trigger system. This new trigger system comprises a set of Feature EXtractors (FEX) with three subsystems targeting electromagnetic (eFEX), jet (jFEX) and

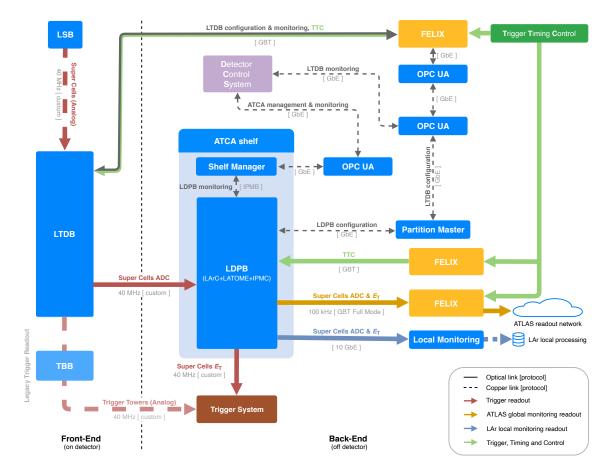

Figure 2. The ATLAS LAr calorimeter digital trigger readout system installed during the second LHC long shutdown.

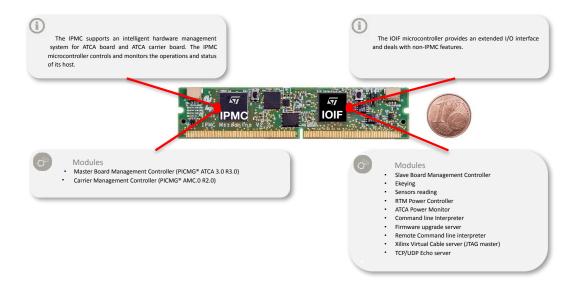

global (gFEX) features [10]. The choice to convert the Super Cells' energy to  $E_T$  at the LDPB level was made to simplify the LTDB design. The LDPB is built in Advanced Telecommunications Computing Architecture (ATCA) format and comprises one ATCA carrier blade named LAr Carrier (LArC) and up to four Advanced Mezzanine Cards (AMCs) called LAr Trigger processing MEzzanines (LATOMEs). The hardware control and monitoring of each blade proceeds via an Intelligent Platform Management Controller (IPMC) plugged into the LArC. In total, 124 LTDBs are installed on the 114 new baseplanes. Furthermore, 30 LDPBs corresponding to 30 LArCs and 116 LATOMEs, are installed in three ATCA shelves placed in one 19-inch rack. This new LAr system uses also three separate Front-End LInk eXchange (FELIX) [11] systems, comprising a total of 30 FELIX boards.

The new trigger readout path is illustrated in figure 2 with solid red arrows. In order to ease the new system commissioning and have a fallback solution in case of unforeseen issues, the legacy trigger readout is kept functional since the LTDB sends the re-summed analog signals to the TBB, which will remain in operation during at least the initial phase of the LHC Run 3. The legacy trigger readout path is illustrated in figure 2 with dashed red arrows.

Several other data paths are present in the system. A global monitoring path utilizes a Full Mode [11] data link between each LATOME and the FELIX system that connects to the ATLAS main data readout (path in orange arrows in figure 2). Its purpose is to verify that the  $E_T$  sent to

the trigger system is correct, by reading the Super Cell ADC data and the  $E_T$  values for all events selected by the first level trigger accept signal (L1A). Thus, this readout allows a recomputation of the calculation performed in the LATOME boards.

A similar monitoring path utilizes the 10 Gigabit Ethernet (GbE) interface of the ATCA shelf that hosts the LDPBs (blue arrow in figure 2). This readout is not connected to the ATLAS main readout but is used by a processing server specific to the LAr system. It enables a more flexible and localized monitoring to readout Super Cell ADC data and  $E_T$  at the L1A signal rate or optionally at any other rate, independently of the constraints present in the ATLAS main data readout in terms of bandwidth and event rate.

The whole system is synchronized with the TTC signals (green arrows in figure 2). These signals provide the 40 MHz LHC reference clock, the L1A, the Bunch Counter Reset (BCR), the Event Counter Reset (ECR) and the Trigger Type commands. The BCR corresponds to the LHC orbit frequency and enables the determination of the collision time of an event via its Bunch Crossing IDentifier (BCID). The ECR is used to compute an event identifier and the Trigger Type records which subsystem issued the L1A. The TTC signals are transmitted to LTDB and LDPB through FELIX systems with Gigabit Transceiver (GBT) [12, 13] links.

The configuration of the LTDB and LDPB hardware proceeds via a "Partition Master" PC. This computer is connected to LTDBs in three stages: two Open Platform Communications Unified Architecture (OPC UA) servers and a FELIX system, connected to LTDBs via GBT links. The first OPC UA server takes care of the LTDB configuration command generation, according to the run control commands received from the Partition Master. The second OPC UA server packs these specific commands to follow the GBT protocol. The Partition Master connection to the LDPB is made directly via a 1 GbE interface.

A Detector Control System [14] (DCS) handles the hardware monitoring: it ensures that the hardware is operated under safe conditions and provides basic safety mechanisms in case of failure. The connection to the LTDB is made with a part of the same OPC UA and FELIX chain used for the configuration. The LDPB is connected to the DCS via an OPC UA server and the ATCA shelf manager, interfaced to the IPMC on the LDPB via an Intelligent Platform Management Bus (IPMB).

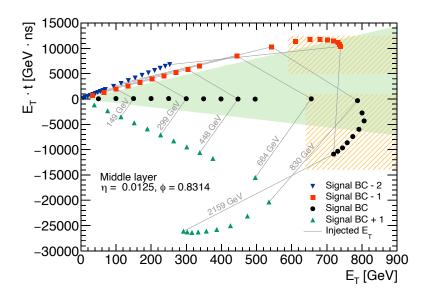

Some differences exist in the signal processing between the main and trigger readout systems: the analog signal processing in the main readout comprises pre-amplification followed by shaping performed in three different gain scales, such that three overlapping gains are obtained with a ratio of about 10. The bipolar shape is created with a time constant of 13 ns. The samples stored by the Switched Capacitor Array (SCA) analog pipeline chip are digitized by a 12-bit ADC and sent to the Back-End system via a 1.6 Gigabit per second (Gbps) optical link. In the trigger readout, the analog processing has a similar shaping with only one gain scale, but with a special conditioning described in section 3.3.3. The Super Cells' digital samples generated in the LTDBs are sent to the Back-End system with a 5.12 Gbps optical link. While in the main readout the RODs compute the cell energies and signal times at the L1A rate (up to 100 kHz), the LDPBs of the trigger readout compute the Super Cell transverse energies ( $E_{SC}^{T}$ ) and signal times ( $t_{SC}$ ) at the LHC collision rate (40 MHz).

The new trigger readout aims to have an Integral Non-Linearity (INL) for each Super Cell channel below 1% with a Super Cell energy computation precision below 250 MeV. Even under high pile-up data taking conditions, this computation must remain unbiased.

In the following, the new hardware, as well as the procedures carried out to validate its functionalities, are described in detail.

#### **3** New Front-End electronics

#### 3.1 Baseplanes

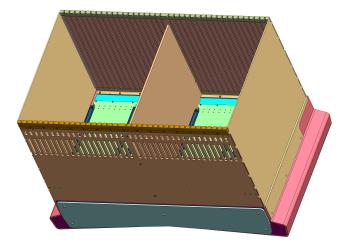

At each end of the barrel cryostat 32 calorimeter signal feedthroughs [15] are installed, distributed around the cylindrical periphery at nearly uniform angles. Each of the two end-cap cryostats has 25 signal feedthroughs distributed around the far end (from the collision point) of its periphery. Each feedthrough with cold and warm flanges connected via vacuum cables is made up of four pin carriers. Each pin carrier has either seven or eight connectors and each connector has 64 signal pins. A pedestal spans two adjacent feedthroughs and a FEC is mounted on each pedestal. Each FEC is divided into two halves with a baseplane installed in each half for almost all of the crates, see figure 3. For each connector in a pin carrier a flex ribbon cable carries 64 signals from the feedthrough to a connector on the back side of the baseplane. The pins in this connector extend through to the front side of the baseplane. A FEB has two 64-pin signal connectors on each FEB is a third 64-pin connector, which returns analog trigger signals to the baseplane where they are routed to trigger-handling boards, also plugged into the baseplane.

**Figure 3.** Perspective drawing of a FEC mounted on its pedestal. Simplified sketches of the two baseplanes can be seen mounted on the pedestal inside the crate.

For the Phase-I upgrade, new baseplanes are required (1) to accommodate the finer trigger segmentation, (2) to make room for the LTDBs (section 3.3), and (3) to maintain the legacy Level-1 trigger system. The new mezzanine LSBs (section 3.2), mounted on the existing FEBs, provide more analog signals than before onto the baseplanes, which are now routed to both the LTDBs and to the existing TBBs or TDBs requiring additional signal layers on the baseplane Printed Circuit Boards (PCBs). Because the LTDB baseplane connectors are wider than those for the other boards plugged into the baseplane, there is no space next to an LTDB for the Radio Frequency (RF) shields which protect the small-signal inputs to the FEBs from extraneous noise. This requires, in some cases, additional slots and/or significant re-arrangement of the baseplane slot assignments, as well as thicker baseplane PCBs, whose thickness is highly constrained by the existing size of the FEC and FEBs. Table 1 gives an overview of the physical dimensions of the various baseplane types.

| Table 1. Overview of the number of PCB layers, physical dimensions and numbers installed on the detector      |

|---------------------------------------------------------------------------------------------------------------|

| for the various baseplane types. Side A and side C are oriented along the positive and negative z-axis of the |

| experiment.                                                                                                   |

|                                                                                                               |

|                | EMB    | EMEC<br>Standard | EMEC<br>Special | HEC    | FCAL<br>side A | FCAL<br>side C |

|----------------|--------|------------------|-----------------|--------|----------------|----------------|

| PCB layers     | 12     | 12               | 14              | 12     | 16             | 16             |

| Length [mm]    | 388.00 | 388.00           | 522.73          | 260.00 | 450.60         | 490.00         |

| Width [mm]     | 415.00 | 415.00           | 415.04          | 415.00 | 406.40         | 406.40         |

| Thickness [mm] | 2.40   | 2.40             | 2.36            | 2.36   | 2.36           | 2.36           |

| # on detector  | 64     | 32               | 8               | 8      | 1              | 1              |

The new EMB baseplane has the same number of slots (19) as the original baseplane. Space for the single new LTDB comes from a previously unallocated slot at one end of the FEC. Some FEBs have been shifted by one slot to allow the LTDB to sit in the middle slot of the baseplane next to the TBB (see figure 4). The flex ribbon cable connections underneath the baseplane are then also shifted by the same amount.

**Figure 4.** Left: photograph of an EMB Baseplane. The slot with three wider baseplane connectors is for the LTDB. Just to the left of the LTDB is the slot for the TBB and to the right is the Controller board slot. The calibration board slot is on the far left and next to it is the monitor board slot. The gold-colored RF shields surrounding connectors in the top and bottom rows identify the FEB slots. Right: Close-up of an EMEC special baseplane showing the RF shields and the wider LTDB connectors.

The EMEC crates house two different types of baseplanes. The EMEC standard crate has baseplanes similar to the EMB but with one fewer FEB, leaving a slot for an additional monitor board. The EMEC special crate has one baseplane for the EMEC and another for the HEC. The

|                   | EMB | EMEC<br>Standard | EMEC<br>Special | HEC | FCAL |

|-------------------|-----|------------------|-----------------|-----|------|

| FEBs              | 14  | 13               | 17              | 6   | 14   |

| LTDBs             | 1   | 1                | 2               | 1   | 2    |

| TBBs              | 1   | 1                | 3               | 0   | 0    |

| TDBs              | 0   | 0                | 0               | 2   | 2    |

| Calibration       | 1   | 1                | 2               | 1   | 1    |

| Controller        | 1   | 1                | 1               | 1   | 1    |

| Monitor           | 1   | 2                | 0               | 0   | 1    |

| Low Voltage Power | 0   | 0                | 0               | 2   | 0    |

| Total             | 19  | 19               | 25              | 13  | 21   |

Table 2. Overview of the different board types which plug into each of the baseplane types.

EMEC special baseplane has two LTDBs and it extends well beyond the center of the crate. The HEC baseplane in the other side of the crate consequently has room for only 13 slots rather than the normal 19 slots of the EMB baseplanes and the EMEC standard baseplanes. An overview of the different boards which plug into the various baseplane types can be found in table 2.

The original FCal baseplanes had 19 slots, each fitting within one-half of a FEC. The other half was used for devices which monitor the status of the cryostats. The new FCal baseplanes each have two LTDBs and the baseplanes extend two (three) slots into the now unused other half crate for the A-end (C-end). Integrated into each new FCal baseplane are traces carrying pulses from the calibration board through attenuating injection resistors (surface mounted on the backside of the baseplane) to those pins on the baseplane connectors which carry FEB signals.

Prototype and production baseplanes were subjected to a series of tests. For those connector pins which are specified to be grounded, the impedance to ground was confirmed to be consistent with zero. Likewise, connector pins which are not specified to be grounded were also checked. The impedance of traces on the baseplanes was measured with a time-domain reflectometer. Continuity between trace ends was compared with the net lists. These mapping tests were then compared with independent LTDB mapping requirements. Signal integrity on the traces and cross-talk between near-by traces were measured with a pulser and oscilloscope to verify that they met specifications. In the case of the FCal baseplanes, the calibration injection resistors were all measured for correct values. All baseplanes were shown to meet the specifications.

#### 3.2 Layer Sum Boards

In the LAr trigger readout, the first level of summing is provided by the Linear Mixer, which sums over four channels in azimuth with different gains in different regions of  $\eta$ . The upgrade to the trigger branch begins with the ouput of this signal. The LSB is a plug-in card for the FEB that performs a second level of summing of the analog signals [16]. There are two LSBs mounted on each FEB. For the Phase-I upgrade, the new LSB output provides signals for the finer granularity

Super Cells in the front and middle layers, while retaining the signals needed for the legacy trigger path elsewhere. Six main types of new LSBs have been produced:

- **S2x8** The basic circuit on the board performs an analog sum of two input channels from the Linear Mixer. There are eight copies of this circuit on each LSB. There are 896 boards of this type required for the EMB and 192 for the EMEC, with 288 reused from the original construction.

- **S2x8D** S2x8 LSBs were already used in the back layer of the EM calorimeters. For Phase-I, this output signal must be sent to both the new LTDB and the legacy TBB. A simple splitter is added to the S2x8 in order to produce this dual output. There are 128 boards of this type required for the EMB and 160 for the EMEC.

- **S1x16LN** This LSB has no summing function and only serves as a line driver for the Linear Mixer signal. There are sixteen copies of this circuit on each LSB. There are 448 boards of this type required for the EMB and 544 for the EMEC.

- **S1x12+S6x2** For the front section of the EMEC in the range  $1.8 < |\eta| < 2.0$ , the output from the shapers covers the area  $\Delta \eta \times \Delta \phi = 0.0167 \times 0.1$ . These are sent individually to the LTDB, while sums of six inputs are sent to the TBB. There are 128 boards of this type required for the EMEC.

- **S2x6D+S1x4** At the end of the EM Barrel ( $|\eta| > 1.4$ ), each LSB must handle four signals originating from the middle layer and 12 signals from the back layer. The signals from the back layer are summed and handled with the same circuitry as the S2x8D and sent to the LTDB and TBB, while the four signals from the middle are just passed directly to the LTDB as in the S1x16LN circuit. There are 128 boards of this type required for the EMB.

- **FCal** All the LSBs above form an unweighted sum of cells in a narrow region of  $\eta$ , while in the FCal, one must perform a sum over a relatively wide range in pseudorapidity, over which the conversion factor from energy to transverse energy varies significantly. For this reason, the inputs to be summed on the FCal LSBs are weighted to perform the conversion to transverse energy before summing. This leads to a large variety of LSBs, which, within a given FCal module, differ only by the weighting resistor values. All 56 FCal LSBs were replaced by the new design.

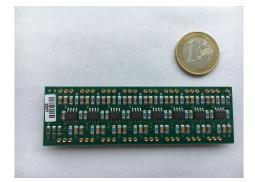

The technical specifications for all the boards are that the gain should not vary by more than 2% from nominal, the summing amplifier INL should be < 1%, and the Direct Current (DC) offset should be < 2% of the maximum output voltage. All boards were tested before and after a week-long burn-in. About 99% passed the specification and were delivered to CERN. As the replacement of the baseplanes required that all electronics in the FECs be disconnected and removed, all FEBs were brought to a surface laboratory. Here, the FEBs were "opened" (i.e. the cooling plates dismounted) and the LSBs replaced by the new boards. Figure 5 shows a photo of an example LSB.

#### 3.3 LAr Trigger Digitizer Boards

An LTDB processes and digitizes up to 320 Super Cell signals ("channels") and transmits them via optical links to the Back-End, while also providing summed analog legacy signals for the TBB via the new baseplanes. The following sections describe the key ASICs for digitization and optical transmission, the motherboard that houses them, the mezzanine card providing the power, quality assurance and control for the assembled system as well as considerations on compatibility with the Phase-II upgrade.

**Figure 5.** Photo of an S1x16LN LSB. Only one side is shown. Half of the components are on the other side. A one-euro coin is shown for scale.

#### 3.3.1 Analog-to-Digital Converter

A custom, quad-channel, pipeline ADC was designed to process the shaped analog signals from the LAr calorimeter Super Cells. These signals are continuously sampled and digitized at 40 Megasamples per second. To digitize the energy of the trigger signals, the ADC has a dynamic range of approximately 12 bits (after calibration) with a required precision of at least 10 bits [1]. Each ADC consumes 45 mW per channel and has a latency of less than 125 ns, meeting the power and latency budgets at the system level of less than 145 mW per channel and 200 ns, respectively.

Radiation tolerance is a key requirement for the ADC, as it is for all devices located on-detector and within the substantial radiation field. The device must operate reliably through the remaining LHC run, as well as the High Luminosity LHC (HL-LHC) runs, with a total expected integrated luminosity of  $3000 \text{ fb}^{-1}$ , possibly up to  $4000 \text{ fb}^{-1}$ . This places strict requirements on the ADC, particularly for the tolerance to total ionizing dose (TID) and single-event effects (SEE), which depend on the expected level of radiation at the readout electronics location [17]. The LAr on-detector ASICs are required to be radiation tolerant up to a total ionizing dose of 180 kRad, non-ionising energy loss doses of up to  $4.9 \times 10^{12} \text{ n eq/cm}^2$ , and be relatively insusceptible to (recoverable) SEEs for a total fluence of up to  $7.7 \times 10^{12}$  hadrons/cm<sup>2</sup> [18].

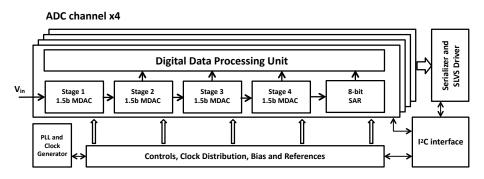

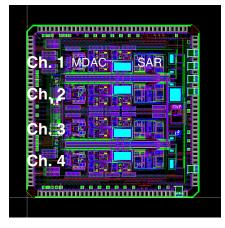

The ADC chip consists of four identical ADC channels and is implemented in CMOS 8RF 130 nm technology. Each channel consists of a multiplying digital-to-analog converter (MDAC) pipeline followed by a successive approximation (SAR) ADC, as shown in figure 6. The MDAC pipeline contains four 1.5-bit stages, each with a nominal gain of two. The additional half-bit overlap allows for a digital on-chip calibration to correct capacitor mismatch. These stages resolve the four most significant bits [19]. The remaining eight least significant bits are resolved by the SAR stage. An internal Phase Lock Loop (PLL) generates a 640 MHz clock from a 40 MHz input clock (provided by the LTDB), of which both edges are used for the SAR operation. The MDAC stages operate with a supply voltage of 2.5 V and a common-mode voltage of 1.25 V, while for the SAR a supply voltage of 1.2 V with a common-mode of 0.6 V is used [20]. A digital data processing unit (DDPU) applies the calibration, forming the digital output, and the data are serialized and sent off the chip over a Scalable Low-Voltage Signaling (SLVS) driver at 320 MHz. An Inter-Integrated Circuit (I<sup>2</sup>C) interface is used for chip control. An image of the chip layout is shown in figure 7.

Figure 6. ADC block diagram.

The 130 nm CMOS 8RF technology does not have sufficient fabrication accuracy to meet the 10 bit precision specification. Therefore, a digital calibration is performed to correct for capacitor mismatch in the MDAC stages. The algorithm measures the actual gain and compares it to the ideal MDAC gain of exactly two. The difference is then taken as a correction and applied to the digital output in the DDPU. By design, the gains are lower than two to avoid over-ranging the input to the following stage, which would lead to missing codes. This results in a reduction of up to 10% of the dynamic range of the chip with respect to the nominal 12 bits (or 4096 counts), within the margin of acceptable performance. The calibration constants are calculated off-line but stored on-chip and must be reloaded to the chip after power cycling.

**Figure 7.** Image of ADC layout  $(3.6 \times 3.6 \text{ mm})$ .

The radiation tolerance of the ADC chip has been studied in its different prototyping stages. The TID and SEE tests performed with a proton beam at the Francis H. Burr Proton Therapy Center at Massachusetts General Hospital with prototypes are described in references [19] and [21]. Radiation tolerance was established for a TID of up to 10 MRad and for non-ionising energy loss up to a fluence of the order of  $10^{14}$  n eq/cm<sup>2</sup>. Proton SEE cross-sections were measured to be of the order of  $10^{-12}$  cm<sup>2</sup> per ADC channel. In addition to the proton radiation tests, SEE cross-sections were measured using four different species of heavy ions at the Cyclotron Resource Centre at Louvain-la-Neuve, Belgium, targeting a larger range of deposited energies and complementing the existing studies with protons [20].

To equip the 124 LTDBs approximately 12000 fully functional ADC chips were required (80 chips per LTDB, plus spares). Allowing for yield factors 17200 chips were produced and packaged in molded QFN-72 packages. The individual ADCs were tested using a socketed test board which allowed for a sine wave input, low-jitter clock, power and readout via a Field Programmable Gate Array (FPGA). The functionality, dynamic range and precision, evaluated by the effective number of bits (ENOB), were measured. A total of 12838 chips were identified as having four channels with a dynamic range greater than 3600 counts and an ENOB larger than 9.9 bits (using the limited-precision socketed board) [20], and thus were qualified to be used for LTDB production.

#### 3.3.2 Serializer and optical transmitter

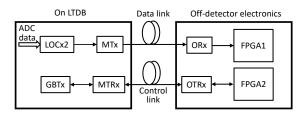

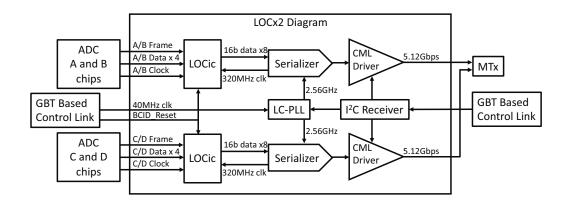

The digitized signals from up to 320 ADC channels per LTDB in the format of serial bit streams at 640 Mbps are prepared for uni-directional, high-speed serial-data transmission over fiber optics using the link-on-chip (LOC) serializer ASIC named LOCx2 [22]. Each LOCx2 can process the data from four ADC chips (a total of 16 ADC serial output channels) for transmission of the data via two 5.12 Gbps optical links to the Back-End. Five bi-directional 4.8 Gbps control links provide configuration, control and monitoring based on the GBT serializer-deserializer ASIC GBTx [23]. Consequently, each LTDB has up to 40 fibers for the data links and ten fibers for the control links, with all 124 LTDBs installed in ATLAS comprising a total of 5848 fibers and a throughput of more than 29 Tbps for the whole optical link system. The Miniature Transmitter (MTx) and Miniature Transceiver (MTRx) [24] are the optical transmitter and transceiver developed to fit between the LTDB PCB and the cooling plate with a clearance in thickness of six millimeters. The MTx is based on the LOCld [25] laser driver ASIC and an 850 nm Vertical Cavity Surface Emitting Laser (VCSEL). The MTRx uses the GBTIA [26] ASIC-loaded Receiver Optical Sub Assembly (ROSA) from CERN for the receiving channel. All ASICs and the optical components are tested to be radiation tolerant for applications in the LAr FECs [1, 17, 27]. The design of the two links, including the choice of the fiber, follows the guidelines of the Versatile Link collaboration [28]. Figure 8 shows a block diagram of the data and control links.

Figure 8. Block diagram of the LTDB optical links.

As the data link transmits information for the ATLAS Level-1 trigger, it is crucial that the transmission latency is fixed and is within the time budget of the ATLAS trigger system. This requirement, after subtracting the signal propagation in the optical fiber, translates to a maximum latency of 75 ns for LOCx2 [1].

The LOCx2 and LOCld ASICs are specifically designed for the LTDB and are based on commercial silicon-on-sapphire 250 nm CMOS technology. The two LOCx2 5.12 Gbps serializer channels share one high-speed clock system based on an inductor-capacitor (LC) oscillator PLL. They

use a low-overhead custom encoding and framing transmission protocol (LOCic [29]) developed to meet the requirement of transmission latency, and to achieve automatic link re-synchronization should the receiving end of the link fail to recognize the transmission frame due to single event upset (SEU) in the link Front-End. The encoding protocol can detect up to three consecutive SEU errors, enabling the link Back-End to discard data containing SEU errors. The LHC bunch-crossing ID is embedded in the protocol to save transmission bandwidth. The LOCic also scrambles the data to achieve DC balance in data transmission through fibers. The LOCId is the matching dual-channel VCSEL driver for the LOCx2. Figure 9 shows the block diagram of the LOCx2.

Figure 9. LOCx2 block diagram with connections to four ADCs (A,B,C and D), Control Link and MTx.

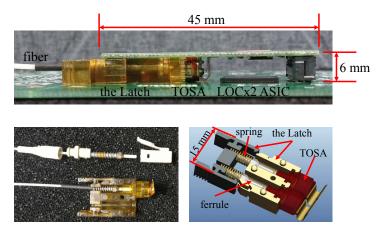

MTx and MTRx share the same mechanical design and electrical connector. A custom mechanical coupler (the "Latch") holds the fiber and the Transmitter Optical Subassembly (TOSA) or ROSA together. The fiber couples with the TOSA or ROSA through an industry standard ferrule. Figure 10 shows a photo of an MTx with the custom Latch to achieve the overall module height of 6 millimeters.

**Figure 10.** MTx and the Latch that couples the fiber with the TOSA or ROSA. Top: MTx on the LTDB with the LOCx2 under the module to save PCB space on the LTDB. Lower left: the LC ferrule taken from the industry standard LC fiber connector and the injection molded Latch. Lower right: a computer-aided design diagram of the Latch with the spring and ferrule to couple with the TOSA.

#### 3.3.3 Motherboard

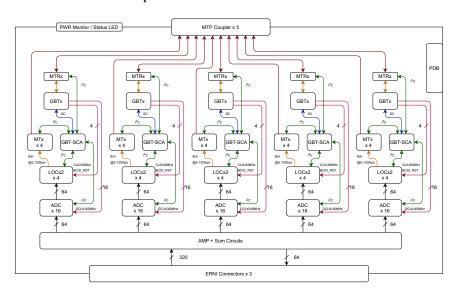

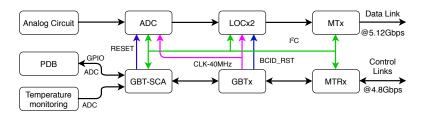

The LTDB motherboard digitizes the Super Cell signals from the FEBs, and sends the data to the Back-End electronics for trigger processing. Each LTDB is powered by a plug-in Power Distribution Board (PDB, see section 3.3.4) and can receive up to 320 Super Cell signals which are amplified by commercial amplifier chips and digitized by the custom ADCs. The digitized data are then packaged and serialized in the LOCx2, and sent out through 40 optical fibers, where each fiber transmits the data at 5.12 Gbps. For Super Cell signals from the front and the middle layers, four neighboring signals are summed up, and the resulting 64 summed signals on the LTDB are sent to the legacy TBB through the new baseplane. Each LTDB comprises five independent identical logical groups, every one capable of processing up to 64 Super Cell signals with 16 ADCs, four LOCx2 and four MTx. One GBTx set per group implements timing, control and monitoring. A block diagram of the LTDB is shown in figure 11, and the data flow and control links are shown in figure 12. While many elements of the LTDBs (such as powering) are common to all channels and consequently represent single points of failure for all channels, the independent logical groups enable normal operation of the other sections in case of a component failure in one section.

**Figure 11.** Block diagram of the LTDB: the board can be divided into five groups. Each group processes up to 64 Super Cell signals with 16 ADCs, four LOCx2 and four MTx. There is one GBTx set to implement timing, control and monitoring per group.

**Figure 12.** Block diagram of the LTDB data flow, showing the data link and the control link. The data link proceeds from the Super Cell signals injected into analog circuitry to ADC, LOCx2, and transmission through MTx. The control links send the clock and commands to GBTx, and collect monitoring information through MTRx.

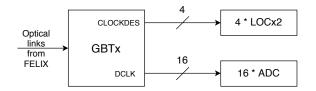

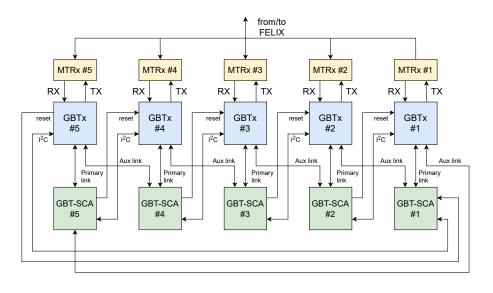

Timing, control, and monitoring are implemented through five GBTx links which operate at 4.8 Gbps in both directions to communicate with the FELIX system. The GBTx chips receive timing and control information through the down-link from the FELIX, then fan-out the clock signals to each ADC, and distribute the clock and BCR signals to each LOCx2 as illustrated in figure 13. The control commands are transferred to GBT-SCA (Slow Control Adapter) [30] chips, then to be used to configure the MTRx, MTx, ADC and LOCx2 ASICs through the I<sup>2</sup>C bus, and reset the ASICs through the General-Purpose Input/Output (GPIO) ports.

**Figure 13.** Block diagram of clock distribution on the LTDB. The DCLKs of the GBTx are used for the ADCs, and the CLOCKDES clocks of the GBTx are used for the LOCx2 chips.

The monitoring information, including voltages, currents, temperatures and power module status are transferred to the FELIX through the LTDB up-link. There are four input power rails drawn from the power bus of the FEC that are used to provide power to the LTDB. A shunt resistor installed in each power rail allows the monitoring of both current and voltage. There are also ten thermistors to measure the board temperature in different positions on the LTDB. All this monitoring information is collected through the ADC of the GBT-SCA. The power modules on the PDB have "Power-Good" signals that are used to indicate their operational status. These Power-Good signals are collected through the GPIO or the ADC of the GBT-SCA.

The LTDBs operate in a high-radiation environment, which may cause SEEs in the electronics during data taking periods. As some of the on-board devices will need a reset or power cycle to recover functionality, a redundant design of GBTx and GBT-SCA is implemented to mitigate this effect. Typically, the GBT-SCA ASIC connects via an electrical serial link (e-link) [13, 31] to the special purpose slow-control e-port of the GBTx ASIC. This dedicated e-port runs at 40 MHz Double Data Rate (DDR) mode, giving an effective data rate of 80 Mbps. It is also possible to connect the GBT-SCA ASIC to any of the other GBTx e-ports as long as its data transfer mode is properly configured for 40 MHz DDR operation. Thus, a possible redundancy scheme can be implemented by using both of these connections where only one of the GBTx e-ports is active at any moment. On the LTDB, a daisy-chain is designed to implement a redundancy scheme, as shown in figure 14. With this scheme, all the GBTx can be recovered by GBT-SCA even if only one GBTx is operational. The GBT-SCA in return can be reset through the GBTx.

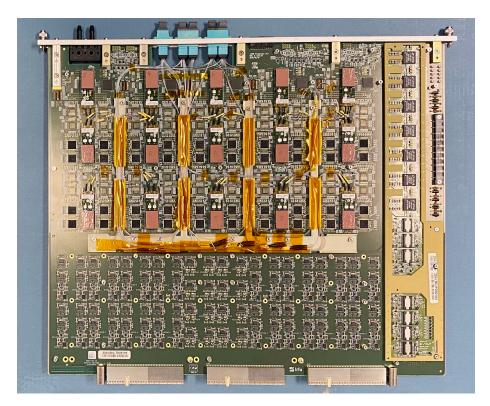

The LTDB PCB dimensions are 410.7 mm x 488.9 mm, with a thickness of 2.2 mm comprising 24 layers.<sup>1</sup> A picture of an assembled LTDB is shown in figure 15. The board design has been carefully considered to meet the low noise requirement. The analog amplifier circuits, which are located on the bottom half of the board, are separated from the digital circuits. The PDB is placed on the right side of the board, and separate regulators are used to provide power supplies for the analog circuitry. To minimize the trace length between the ADCs and LOCx2, four ADCs are placed

<sup>&</sup>lt;sup>1</sup>The manufacturer is TTM Technologies, 355 Turtle Creek Ct San Jose, CA 95125 U.S.A.

**Figure 14.** Redundancy design on the LTDB: the redundancy is implemented through the auxiliary port of the GBT-SCA. This full chain design can recover any GBTx if it gets stuck during data taking (when power cycling is not allowed), provided at minimum one GBTx is operating correctly. If all GBTx cannot work except GBTx #5, the GBTx #4 will be recovered through GBTx #5 and GBT-SCA #5, then the GBTx #3 will be recovered through GBTx #4 and GBT-SCA #4, etc.

around one LOCx2, where the data from four ADCs are organized and sent out through one MTx module with two fibers. The MTx module is placed over the LOCx2 chip to save space.

Special care is taken to adapt the analog signals at the input of the LTDB. The analog output dynamics of the Linear Mixer has to be matched to the input dynamics of the LTDB ADC. In addition, the single-ended signal coming from the LSBs located on the FEBs has to be converted to differential at the ADC input. This conversion and the dynamic range matching are done by a very low-power (1.14 mA/channel) fully-differential amplifier (THS4522), equipped with an appropriate passive network to set the gain and the pedestal at the ADC input.

In the case of the main readout, the current pulse coming from the cells is shaped by a CR-RC<sup>2</sup> filter. This filter is optimal in terms of signal over noise optimization. In the case of the trigger path, the cell signals are first summed in groups of up to four cells by the Linear Mixer, and shaped by a CR-RC active filter. A CR-RC filtering has been chosen to minimize the attenuation over the trigger path, and a passive RC stage with a time constant of 15 ns is implemented on the LTDB to get the same optimal CR-RC<sup>2</sup> as for the main readout. This passive RC stage also acts as an anti-aliasing low-pass filter in front of the LTDB ADC. Super Cell signals corresponding exactly to legacy analog trigger signals are configured as a high impedance pick up on the LTDB, since they are directly sent via the backplane to the legacy analog trigger boards (TBB and TDB), whose inputs are 50  $\Omega$  adapted. Super Cell signals that need further summing on the LTDB before being sent back to the backplane for the legacy analog trigger, are 50  $\Omega$  adapted on the LTDB.

The Linear Mixer is no longer in its linear dynamic range if its output amplitude goes above 3.3 V. This voltage threshold has to match the 2.4 V saturation voltage of the ADC differential input. Since each ADC has 3600 to 3800 available digital codes, the least significant bit of the LTDB ADC corresponds approximately to 1 mV at the Linear Mixer output everywhere on the detector.

Figure 15. Photograph of an assembled LTDB with PDB installed.

In addition, the pulses from the Super Cells do not all have the same shape, since the drift time of the charges produced by ionization of the Liquid Argon by the shower particles changes as a function of  $\eta$ . Because a bipolar shaping circuit is used, this translates into a change of the amplitude of the undershoot of the pulse. Since the undershoot has to be digitized and should not saturate the ADC, the gain and pedestal of each channel have been adjusted so that signals close to the Linear Mixer saturation amplitude use the full dynamics of the ADC input. Over the whole acceptance of the calorimeter, this leads to gain differences up to 30%.

#### 3.3.4 Power distribution board

Power distribution on the LTDB is provided by the PDB mezzanine card. The choice of developing a separate board for the generation of the supply voltages for the LTDB ensures forward compatibility in the future Phase-II upgrade, for which a different power distribution scheme for the Front-End electronics is planned. The use of a mezzanine board allows the re-design and replacement of only the PDB, without modifying the LTDB itself (as explained in section 3.3.6).

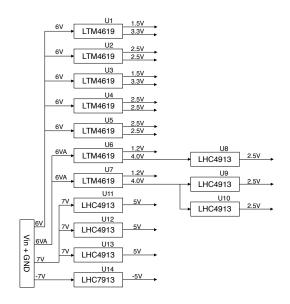

The PDB consists of digital and analog sections to power the corresponding sections of the LTDB. The block diagram of the power scheme is shown in figure 16. From the +6 V line taken from the FEC power bus, the following voltages are created for the digital part of the LTDB: +1.2 V, +1.5 V, +2.5 V and +3.3 V. This is achieved using LTM4619 DC-DC converters from Linear Technology Corporation (now Analog Devices, Inc.).

The analog voltages are generated as follows. From the +7 V (-7 V) of the FEC power bus, the +5 V (-5 V) is generated using the LHC4913 (LHC7913) Low-DropOut (LDO) linear voltage

**Figure 16.** Power scheme of the PDB. The board integrates LTM4619 DC/DC converters (U1-U7) and LHCx913 linear voltage regulators (U8-U14) to produce the voltages needed by the LTDB (the number of devices has been established based on the budget of the output currents). From the two +6 V lines available on the input power bus, one (labelled "6V") is used to generate the digital voltages and the other one ("6VA") is used to generate the analog voltages (see text).

regulators from STMicroelectronics. The LHC4913 is also used to generate the analog +2.5 V, starting from the +6 V of the power bus (with an intermediate step down at +4 V, using an LTM4619, to avoid a large voltage drop in the LDO).

The PDB is radiation tolerant [32–34] and able to operate in presence of the maximum magnetic field expected in the LTDB positions (lower than 0.1 T) [35]. The radiation tolerance requirements for the PDB are less stringent than for the rest of the LTDB components (see section 3.3.1) since the board will have to operate only for the LHC Run 3 and will be replaced before the start of the HL-LHC.

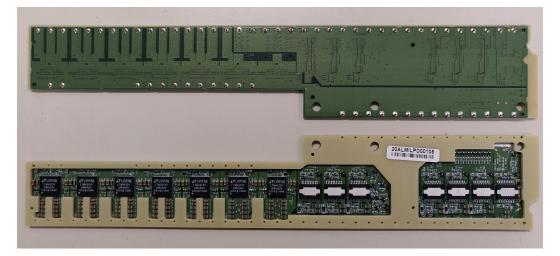

The board is manufactured as a ten-layer PCB of 1.6 mm thickness,<sup>2</sup> reinforced with a fiberglass (G10) frame glued on the top side. When mounted on the LTDB motherboard, the total maximum vertical height is about 5.4 mm, which fits just below the LTDB cooling plate, mounted at 6 mm from the motherboard surface. A picture of one production PDB is shown in figure 17. An automated set-up has been developed to test the correctness of all output voltages of the PDBs at full load before they were shipped to the LTDB assembly sites.

#### 3.3.5 Quality assurance and control

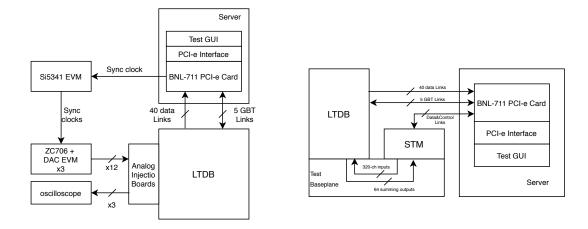

The LTDB quality assurance and control (QA/QC) involves the testing of three main components: the cooling interface is tested for leaks, the PDBs are tested to meet the requirements on voltage and current of the outputs, and each LTDB with a qualified PDB installed is subjected to functionality testing and — integrated with the test stand — to performance testing as detailed below.

Each PDB module is tested with a standalone test stand to verify basic functionality before it is cleared to be installed on an LTDB motherboard. The input and output voltages and current

<sup>&</sup>lt;sup>2</sup>The PDBs have been produced by ARTEL S.r.l. - 52041 Pieve Al Toppo (AR) - Italy

**Figure 17.** Picture of a PDB as seen from the bottom and top. All components are mounted on the top side. On the same side, the G10 reinforcement frame is also visible.

are measured to obtain efficiency information. All test data and analysis results are examined and logged into a database. A PDB module is accepted if it passes the following requirements: the output voltage is within  $\pm 2.5\%$  of the nominal value; the output voltage ripple is within 10 mV peak-to-peak; and the efficiency is better than 70% at nominal load.

The PDBs passing the tests above are then subjected to a Highly Accelerated Stress Screening (HASS) test, where the PDBs are placed in a chamber and undergo ten thermal cycles between  $0 \degree C$  and  $60 \degree C$  for about 12 hours. The goal of the HASS test is to find any failures due to component infant mortality, cold solder joints, etc. After HASS testing, each PDB is installed on an LTDB for re-testing, where the voltage of all outputs is measured, control and monitoring signals are tested, and the power rail ramp-up time (from 10% to 90% of the rising edge) for the GBTx is measured as well. If the PDB passes this re-testing, it can be used on the LTDB for integration testing.

Each LTDB motherboard is initially tested with a standalone test stand to verify basic functionality. If it passes this test, a HASS test as described for the PDBs above is performed as well. After the HASS test, the PDB, MTx, MTRx and fibers are installed on the LTDB. Then, digital functionality and power distribution as well as analog performance are verified, followed by an integration test, all performed using the integration test stand (see section 5.1), before the LTDB is qualified to be installed on the detector.

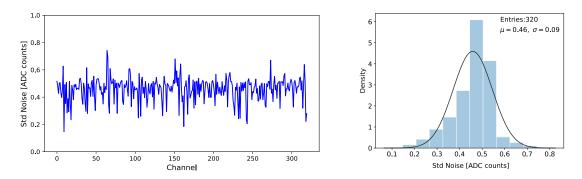

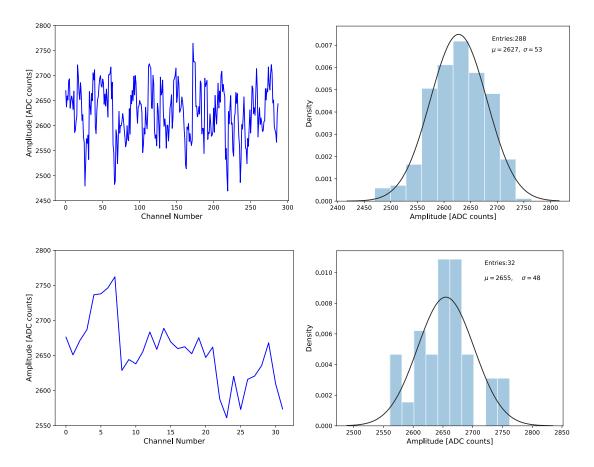

Initially, the control links through GBTx as well as the digital readout chain through LOCx2 are verified. Each ASIC, including GBT-SCA, MTRx, MTx, ADC and LOCx2, is configured and checked through the GBT link to verify the control links. The readout chain is verified through ADC test patterns before analog signal injection is exercised. To pass these digital functionality tests, an LTDB must meet the following requirements: slow control, configuration and remote monitoring logic are functioning properly; pedestal tests of the digital readout chains are functioning correctly for all 320 channels; and monitoring information is correct, with the temperature of the digital part at  $20 \pm 5$  °C, the temperature of the analog part at  $30 \pm 5$  °C, and the voltages at their nominal values  $\pm 10\%$ .

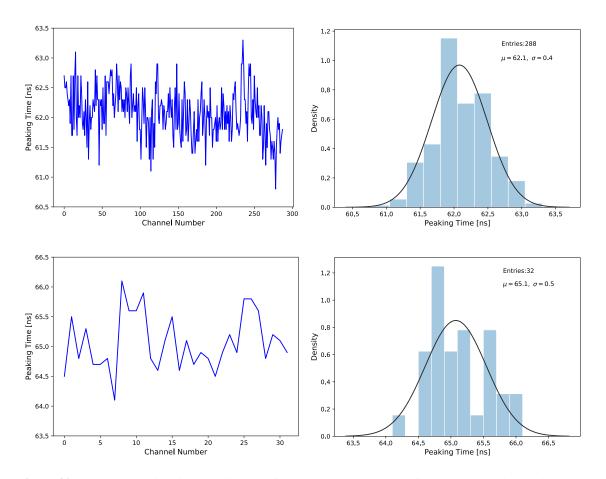

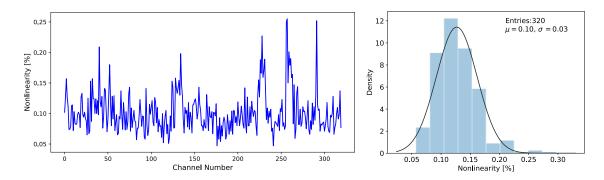

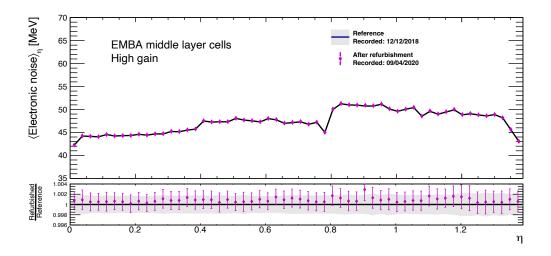

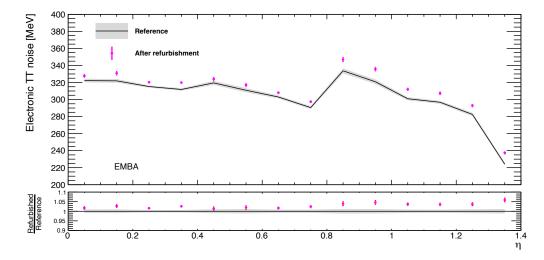

The analog performance integration focuses on the detailed characterization of the full board. Both pedestal tests and pulse tests are performed on the board, as well as tests to measure the signal amplitude and peaking time. Additional testing enables assessment of the INL of each channel while summing testing verifies the summing output and measures the non-linearity of each summing output. All test data and analysis results are examined and logged into a database. To pass these analog functionality tests, an LTDB must meet the following requirements: pedestal tests of analog readout chains are functioning correctly for all 320 channels, with a noise level better than 0.85 of the least significant bit; pulse tests of both analog and digital readout chains are functioning correctly for all 320 channels are functioning correctly for all 320 channels are functioning correctly; and the power consumption of the whole board is within 95.0  $\pm$  4.5 W.

After the above tests are passed, the cooling interface is installed. Each cooling interface including the cooling blocks and cooling plates is leak-checked in a dedicated test station prior to assembly on the LTDB, and again after installation on the LTDB. If no leak is observed, the boards passing above performance tests are shipped to CERN, where another leak check with pressurized gas is performed in a dedicated test station before installation. Only the boards passing this additional leak check are finally installed on the detector.

#### 3.3.6 Compatibility with Phase-II upgrade

After the Phase-I upgrade and data taking in Run 3, the LTDB boards will still be used in the Phase-II upgrade for Run 4 and beyond as part of a level-0 trigger system [36]. To fully exploit the functionalities of the LTDB in the Phase-II configuration of the LAr trigger and readout system, some design work is needed on the side of the future FEBs. Correct matching between the analog dynamic range of the differential trigger sums that will be provided by the Front-End preamplifier/shaper ASICs and the single-ended analog dynamic range of the LTDB inputs has to be ensured. These design aspects will not be covered here, since the Phase-II FEBs are currently under development and the details of how to ensure compatibility are not yet fully defined.

On the LTDB side, it is critical to ensure easy adaptation to the configuration of the LAr Front-End system during Phase-II. Seen from the LTDB side, the main differences between Phase-I and Phase-II configurations are:

- In Phase-II, the legacy analog trigger system, based on the analog TBB, will have been decommissioned. The consequence for the LTDB is that the adders that are present to sum groups of four channels will no longer be needed. On the LTDB, these adders build the analog layer sum signals needed by the TBB from the Super Cell signals.

- The PDB will have to be redesigned to adapt to the Phase-II power rail configuration which will provide only one single positive voltage; negative power supply rails will no longer be available. The absence of negative voltages means that it will not be possible anymore to power the (then no longer needed) legacy analog adders. Appropriate measures have been taken so that this situation does not degrade the performance on the Super Cell signal path.

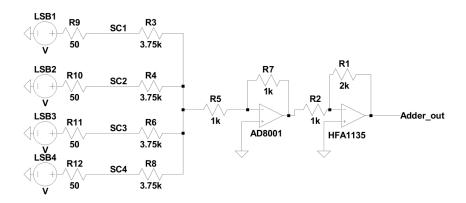

Figure 18 shows a simplified schematic of the LTDB analog adder circuitry. The Super Cell signals are modelled as a voltage source in series with a 50  $\Omega$  resistor. It can be seen that each of the four Super Cells (SC1 to SC4 in figure 18) that are summed by the legacy adders are connected through a 3.75 k $\Omega$  resistor to the inverting input of the first of the two inverting amplifiers (AD8001) that make up the complete adder. As long as this amplifier is powered on, its negative input is a

virtual ground, and there is no induced crosstalk between Super Cells. On the other hand, once the amplifier is powered off, the Super Cells that are summed together are connected through a resistive network that introduces some resistive crosstalk. Consequently, the resistor values have been chosen high enough to keep the crosstalk below 0.2%. Taking into account the actual resistor values used, the crosstalk between any two Super Cells connected to the same adder is equal to 0.17%. This number has been checked on a test board that has been built for this purpose, featuring a group of four Super Cells and their adder, with the possibility to power off specifically the adder circuit. This shows that the crosstalk induced during Phase-II by the absence of the negative power rail is acceptable.

Figure 18. Simplified schematic of the adder implemented on the LTDB for compatibility with the legacy analog trigger system.

#### 4 New Back-End electronics

#### 4.1 LAr carrier

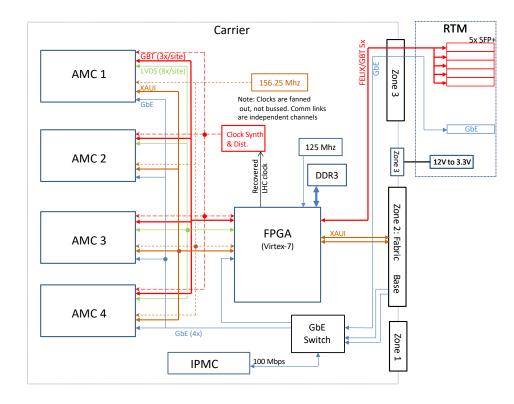

The LAr carrier (LArC) is an ATCA standard cut-out blade with a Rear Transition Module (RTM). The LArC hosts the LATOME processor daughtercards (section 4.2), sends and receives data from the read out system, and distributes clocks and trigger signals synchronized to the LHC beam clock. Data connectivity includes the ATLAS Trigger and Data Acquisition (TDAQ) system for the global monitoring and standard Ethernet 1 GbE and 10 GbE links. The latter are based on the 10 Gigabit Attachment Unit Interface (XAUI). A photograph of the LArC is shown in figure 19.

Data are received and/or transmitted on the LArC using five paths: (1) serial Multi-Gigabit Transceiver (MGT) connections of 9.6 Gbps between the LArC and LATOME cards for readout of data on L1A (TDAQ path), (2) readout of 10 Gbps local monitoring data between the LArC and LATOME cards upon user request (local monitoring path), (3) Low Voltage Differential Signaling (LVDS) connections between the carrier and LATOME cards used for clock and trigger distribution, (4) serial transceiver links to optical fibers connected to Small Form-factor Pluggable (SFP+) modules<sup>3</sup> on the RTM which provide the external connection for the TDAQ path and (5) serial transceiver links between the carrier and other ATCA boards using the ATCA shelf backplane which provide the external connection for the local monitoring path. The master clock signal and trigger

<sup>&</sup>lt;sup>3</sup>SFP+ modules are an industry standard hot-swappable electro-optical converter module.

Figure 19. A photograph of the LArC and RTM, with the LArC side panels removed for clarity and testing cards in the AMC sites.

data are recovered from a dedicated link of the TDAQ data path from the ATLAS trigger distribution system to the LArC and distributed to all of the LATOMEs.

A block diagram of the carrier data and clock connectivity is shown in figure 20, The main component on the board is a Xilinx<sup>®</sup> Virtex<sup>®</sup>-7 FPGA, part number XC7VX550T-FFG1927-2-E, through which all of the TDAQ and local monitoring data passes. The FPGA boots from onboard flash and has 256 MB of external DDR3 memory. There are four clock domains on the LArC for the TDAQ path, the local monitoring path, the 1 GbE path and a system clock. The TDAQ clock is recovered from the LHC master clock and provides all trigger-related timing.

Along with the dedicated purpose TDAQ and local monitoring links, the carrier provides GbE connections. All GbE links are routed through a BROADCOM switch on the LArC. The GbE links are connected from the switch to the LArC FPGA, each of the 4 LATOME sites, the IPMC module (at 100 Mbps), an SFP cage on the RTM and 2 GbE connections to the ATCA shelf backplane. The redundant backplane connections are required by the ATCA standard.

The LArC uses an ATLAS standard IPMC (section 4.3) to provide all board power and sensor management functions. The ATCA standard also specifies electrostatic shielding and status Light Emitting Diodes (LEDs) all of which are included in the carrier. The FPGA can be rebooted without a LArC or shelf power cycle by using dedicated commands sent to the IPMC over the 1 GbE network.

The RTM is used to provide connectivity for 5 TDAQ channels via SFP+ modules. It also has Joint Test Action Group (JTAG) connectors on the back panel providing access to the onboard JTAG chain and an IPMC JTAG interface. An insertion indicator switch is integrated into the

**Figure 20.** A block diagram of the data and clock connections on the LArC. The GbE connectivity is provided using a BROADCOM BCM5396. The switch is automatically initialized at power on without programming. The switch to the AMC, switch to FPGA and switch to RTM SFP connections are standard 1000Base-X connections. The connections between the switch and the Zone 2 base layer are 1000Base-TX as required by the ATCA standard, and the connections between the switch and the IPMC are 100 Mbps PHY-based links. All XAUI and TDAQ connections are routed through the FPGA. I<sup>2</sup>C based monitoring and configuration connections are not shown.

RTM insertion/removal handle, and by sensing the switch, RTM power is controlled by user code in the IPMC. This allows hot swapping control of the RTM DC-to-DC converter. The RTM data connection to the carrier is a standard ATCA connector located in carrier zone 3. A second zone 3 connector provides 3.3 V management power and 12 V payload power to the RTM.

The production LArC's and RTM's undergo multistep testing. The first step involves checking the power systems, including a simple resistance test before initial powering on. The second step then tests the infrastructure including JTAG, I2C, IPMC, DDR3, clock generation, and the 1 GbE infrastructure. The next step is testing of all transceiver TDAQ and local monitoring links to  $10^{14}$  and  $10^{12}$  bits respectively, using the industry standard PRBS31 (PseudoRandom Binary Sequence of length  $2^{31} - 1$ ). The LVDS links are also tested at 160 MHz using PRBS31. The tests for the links which connect to LATOME's use special passive loopback cards inserted in the AMC slots during this check. In the final step a boot flash memory is programmed with low-level board management code, and the one-time-programmable FPGA identification eFuse is set. At this point all components and functionality are verified, and the carriers are ready to have LATOMEs installed.

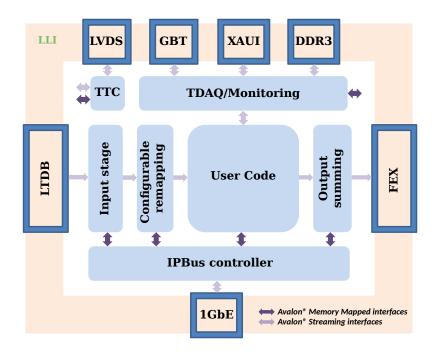

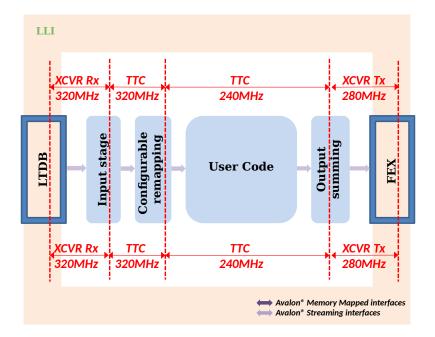

#### 4.2 LAr trigger processing mezzanine

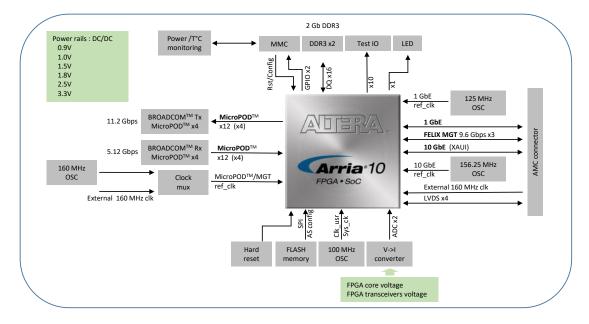

The LATOME board reads incoming data from 48 optical links, processes these data in a highperformance FPGA and sends the results to 48 optical links. The board is also interlinked to the standard Ethernet networks (1 GbE and 10 GbE) and the specific ATLAS network (TDAQ) for monitoring and control purposes. This board fulfills the AMC standard and is plugged into the LArC which provides connectivity as discussed above. Figure 21 shows the LATOME equipped with optical fibers: the black front panel connectors gather the 48 transmitting fibers and the blue ones the 48 receiving fibers. The FPGA and the optical transceivers are cooled down with large copper heatsinks.

Figure 21. LATOME board equipped with optical fibers.

The board receives LTDB data at 5.12 Gbps and transmits new FEX system data at 11.2 Gbps through four twelve-channel BROADCOM MicroPOD<sup>TM</sup> receivers and four twelve-channel BROAD-COM MicroPOD<sup>TM</sup> transmitters. These MicroPOD<sup>TM</sup> modules make the optical to electrical and the electrical to optical conversion for the 2×48 FPGA high speed links. All these links can be synchronized either by a local oscillator with a fixed frequency of 160.316 MHz or by the external clock provided by the LArC. The links to the standard Ethernet (1 GbE and 10 GbE) and the TDAQ (9.6 Gbps) networks are routed through the AMC connector. This connector carries also the common TTC commands over four LVDS links.

On the board, the main component is the Intel<sup>®</sup> Arria<sup>®</sup> 10 FPGA, part number 10AX115R3F40E2SG (figure 22). Four DC/DC converters provide the different voltage supplies to this FPGA. They are enabled by a sequencer chip in order to generate the power on and off sequence required by the Arria<sup>®</sup> 10. This sequence is triggered by the Modular Management Controller (MMC) chip which manages the AMC hotswap, the onboard sensors (temperature, voltage and current) and the IPMC connection (see section 4.3 for the IPMC description).

The FPGA firmware boots from a 1 Gb serial flash memory. Two 2 Gb DDR3 external memories are also available to exchange data with the FPGA. Four oscillators (125/156.25/160.316 and 100 MHz) provide all the clocks needed to synchronize the internal FPGA logic.

The LTDB and FEX optical cables are plugged into the LATOME front panel through high density Multi-fiber Push On (MPO) optical connectors. On this front panel there is also access to the FPGA JTAG and test outputs and the MMC JTAG port with external connectors. A reset push button and status LEDs are available as well.

There are two types of LATOME according to the combination of input channels on the MPO connectors and pigtail fibers to the MicroPOD<sup>TM</sup> modules. The standard LATOME has four MPO connectors of 12 channels (MPO12) while the special LATOME has two MPO connectors of 24 channels (MPO24) and one MPO12 for data reception (Rx). Both LATOME types have one MPO connector of 48 channels for data transmission (Tx).

Figure 22. Block diagram of the LATOME board.

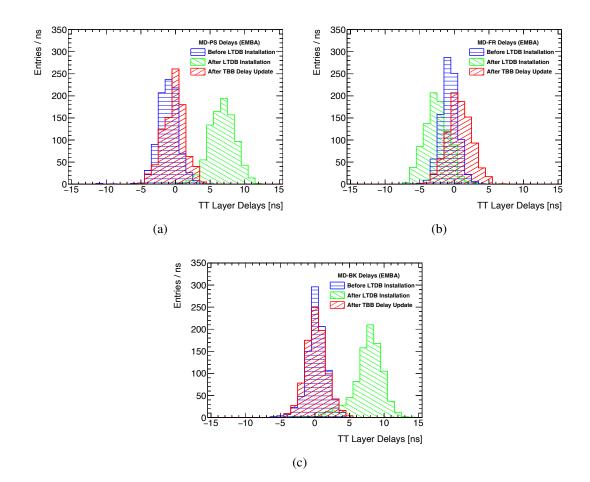

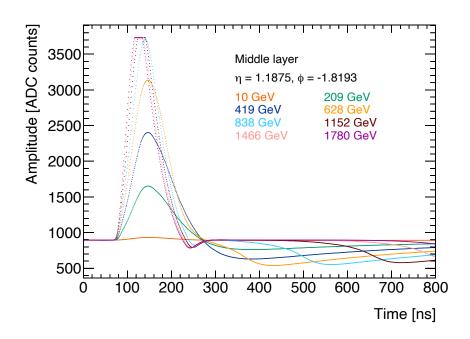

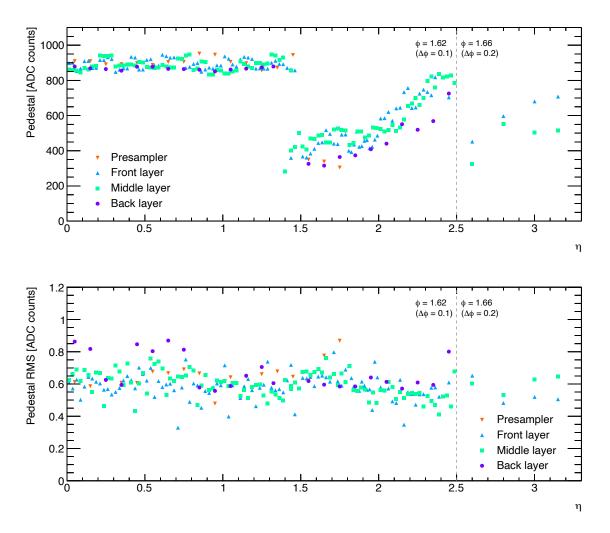

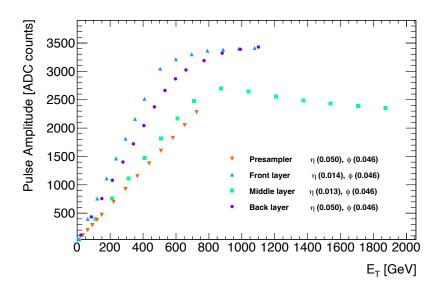

The LATOME boards were validated after their production in several stages. Once the LATOME is received from the assembly house, the board is stamped with its unique identifier by setting a ten-bit vector with pull down resistors connected to the FPGA input pins. This identifier is used to track the board all along the process. The first stage of validation consists of checking the powering sequence. The board is powered on and the power-up sequence and the DC/DC converters' voltage values are checked. Then the FPGA JTAG connection is verified and all the ports and components interlinked to the FPGA are sequentially tested: oscillators, DDR3, flash memory and ATCA carrier links up to 10<sup>13</sup> bits with PRBS31 vectors.