# Multi-Element Thermal Modeling of Interconnects Derived from a Projection-based Learning Algorithm

Ming-C. Cheng\* and Wangkun Jia

Dept. of Electrical and Computer Engineering, Clarkson University, Potsdam, NY 133699-5720, USA

\*mcheng@clarkson.edu

**Abstract**—An approach combining domain decomposition and model order reduction enabled by a data-driving learning algorithm is developed for thermal simulation of interconnects. The approach accounts for variations of heat sources, boundary conditions (BCs) and material properties. This approach is applied to construct the thermal model of a generic element for a group of interconnects that are used to wire FinFET standard cells. The interconnect structure in a FinFET IC is then partitioned into several elements, each modeled by the generic element model. The developed multi-element thermal simulation of the interconnects is demonstrated and its accuracy is examined in terms of the metal/via routings and BCs.

**Keywords**—Thermal simulation, interconnects, data science, model order reduction, domain decomposition, FinFETs

## I. INTRODUCTION

Interconnect thermal prediction has been a very important TCAD simulation issue due to the thermal impacts on performance and reliability of semiconductor devices and integrated circuits (ICs) [1-4]. The common approaches to predict the thermal profiles in devices and ICs, including interconnects, have been usually based on either compact models [5-8] or direct numerical simulations (DNSs) [9-11]. The former derived from *RC* thermal circuits or analytical methods, although efficient, require major approximations/assumptions and do not offer fine enough resolution to locate high thermal gradient or hot spots. The latter, although accurate with high resolution, demand extensive computational time and resources.

An innovative approach combining domain decomposition and a model order reduction technique based on proper orthogonal decomposition (POD) [12-14], a data-driving learning algorithm, was proposed in a previous study [15] to overcome all the aforementioned problems. It has been shown that the POD approach is as efficient as the *RC* thermal circuits and as accurate as the DNSs, and it offers a spatial resolution as fine as that of the DNSs. It has been demonstrated [15] that the POD approach applied to 3D thermal simulations of ICs offers a reduction in the numerical degrees of freedom (DoF) by 5 orders of magnitude and improves the computational time by more than 3 orders when a fine resolution is needed.

The proposed approach partitions the simulation domain into smaller subdomains (or called elements). Each element is projected onto a functional space represented by a finite set of POD basis functions (or POD modes). These elements are then glued together to construct the whole domain. To develop a POD model for each element, thermal data of each subdomain obtained from the heat transfer equation influenced by spatial

and temporal parametric variations are needed to extract (or *train*) the POD modes. Using this multi-element approach, POD modes  $\varphi_i$  of each element instead of the entire domain can be generated more efficiently. The POD modes studied previously only account for variations of heat sources and boundary conditions (BCs) [15-19]. In this study of interconnect thermal modeling, property variations (PVs) of materials is also implemented in the POD mode training to adopt variations of thermal properties between the metal and dielectric. The proposed PV-POD approach is demonstrated in a group of interconnects that are used to wire FinFET standard cells, such as a small FinFET IC shown in Fig. 1(a). To the best of our knowledge, this is the first study implementing PV in POD.

## II. BACKGROUND OF POD THERMAL SIMULATION

POD generates a set of modes from thermal data accounting for parametric variations by solving the Fredholm equation [12, 13],

$$\int_{\vec{x}'} \langle T(\vec{r}, t) \otimes T(\vec{r}', t) \rangle \bar{\varphi}(\vec{r}') d\vec{r}' = \lambda \bar{\varphi}(\vec{r}) \quad (1)$$

where  $\lambda$  is the eigenvalue representing the mean squared temperature captured by its mode  $\bar{\varphi}$ . Once the modes are found, temperature can be described by a linear combination of  $\varphi_i$

$$T(\vec{x}, t) = \sum_{i=1}^M a_i(t) \varphi_i(\vec{x}), \quad (2)$$

where  $M$  is the selected DoF for the solution and  $a_i$  is the time dependent coefficient for each mode. To predict  $T(\vec{r}, t)$  in (2) in each element, a set of equations for  $a_j$  is derived by projecting the heat transfer equation onto an eigenspace. Several POD elements can then be assembled together to construct a POD model for a large structure. In the structure, all the identical elements can be described by their generic POD element.

### A. Multi-Element POD Approach

Projection of the heat transfer equation onto a POD space for an element neighbored by others based on the Galerkin projection gives rise to [20, 21]

$$\int_{\Omega} \left( \varphi \frac{\partial \rho C T}{\partial t} + \nabla \varphi \cdot k \nabla T \right) d\Omega - k \int_{\Gamma} (\llbracket T \rrbracket \cdot \nabla \varphi + \nabla T \cdot \llbracket \varphi \rrbracket) d\Gamma + k \int_{\Gamma} \mu \llbracket T \rrbracket \cdot \llbracket \varphi \rrbracket d\Gamma = \int_{\Omega} \varphi P_d(x, t) d\Omega, \quad (3)$$

where  $k$  is the thermal conductivity,  $P_d$  the power density,  $\rho$  the density,  $C$  the specific heat,  $\Gamma$  the boundary surface,  $\mu$  a penalty constant defined as  $N_{\mu}/dx$  ( $dx$  is the local element size and  $N_{\mu}$  as the penalty number), and  $\{\cdot\}$  and  $\llbracket \cdot \rrbracket$  the average and

This work is supported by National Science Foundation under Grant No. ECCS-2003307.

difference across the interface, respectively [15, 20, 21]. The surface integrals in (3) are adopted from the interior penalty discontinuous Galerkin method [20, 21] to enforce thermal continuity at the interface. Power density in metal induced by Joule heating is given as

$$P_{dm} = \vec{J} \cdot \vec{E} = J^2 / \sigma, \quad (4)$$

where  $\vec{J}$  is the current density,  $\vec{E}$  the electric field, and  $\sigma$  the copper metal conductivity.

For a domain consisting of  $N$  projected elements, (3) reduces to an  $N$ -element POD model given as

$$\begin{bmatrix} \mathbf{C}_{1,1} & \mathbf{C}_{1,2} & \cdots & \mathbf{C}_{1,N} \\ \mathbf{C}_{2,1} & \mathbf{C}_{2,2} & \cdots & \mathbf{C}_{2,N} \\ \vdots & \vdots & \ddots & \vdots \\ \mathbf{C}_{N,1} & \mathbf{C}_{N,2} & \cdots & \mathbf{C}_{N,N} \end{bmatrix} \frac{d}{dt} \begin{bmatrix} \vec{a}_1 \\ \vec{a}_2 \\ \vdots \\ \vec{a}_N \end{bmatrix} + \begin{bmatrix} \mathbf{G}_1 + \sum_{q=2}^N \mathbf{G}_{1,B_{1,q}} & \mathbf{G}_{1,2} & \cdots & \mathbf{G}_{1,N} \\ \mathbf{G}_{2,1} & \mathbf{G}_2 + \sum_{q=1, q \neq 2}^N \mathbf{G}_{2,B_{2,q}} & \cdots & \mathbf{G}_{2,N} \\ \vdots & \vdots & \ddots & \vdots \\ \mathbf{G}_{N,1} & \mathbf{G}_{N,2} & \cdots & \mathbf{G}_N + \sum_{q=1}^{N-1} \mathbf{G}_{N,B_{N,q}} \end{bmatrix} \begin{bmatrix} \vec{a}_1 \\ \vec{a}_2 \\ \vdots \\ \vec{a}_N \end{bmatrix} = \begin{bmatrix} \vec{P}_1 \\ \vec{P}_2 \\ \vdots \\ \vec{P}_N \end{bmatrix}, \quad (5)$$

where the elements of the thermal capacitance and conductance matrices of each element in the POD space are detailed in [15].

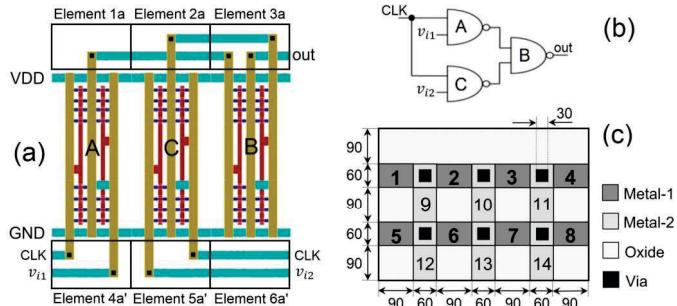

Fig. 1. (a) IC layout of a 3-NAND2 circuit with M1 in blue, M2 in yellow, poly in red and vias in black. (b) 3-NAND2 circuit. (c) Genetic interconnect element with metal/via labeled in nm, thicknesses of M1 and M2 equal to 60nm and dielectric thickness of 100nm between M1 and M2. Metal segments in (c) are numbered. All NAND2 structures (A, B and C) are identical.

### B. POD Accounting for MaterialProperty Variations

In this study, we extend the POD thermal simulation approach to account for the PVs between metal and dielectric for a particular group of interconnects given in Elements 1a-3a and 4a'-6a' of Fig 1(a). These elements are used to wire the standard cells, as shown in Fig. 1(a) whose circuit is given in Fig. 1(b). Each interconnect element includes 2 metal layers with interlayer dielectrics and the substrate. Thus, a generic element given in Fig. 1(c) and its mirror symmetric element can be used to cover all possible metal/via routings for this group. However, for different-size standard cells, a different generic element will be needed. Thermal data collected from ANSYS DNSs of several elements of this group to account for effects of metal-dielectric variations are needed to train the POD modes.

Using the collected thermal data, the method of snapshots [15, 22] are applied to (1) to extract the POD modes.

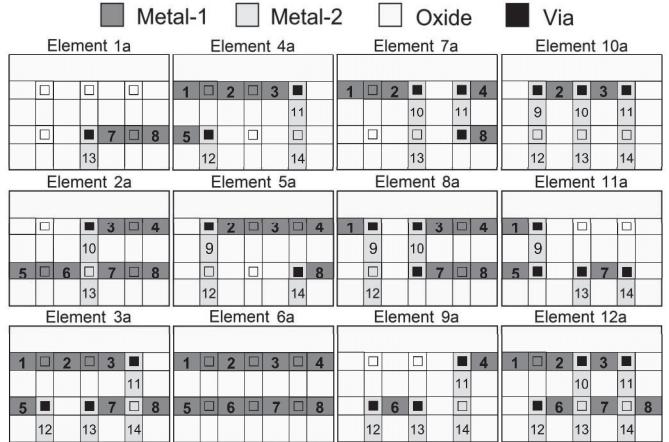

Fig. 2. Twelve interconnect elements for thermal data collection. Elements 1a-6a or their symmetric ones are those shown in Fig. 1.

In previous POD studies [15-19], if a material changes in any location of the structure, a different set of POD modes is needed. In the PV-POD approach for interconnects with unified metal dimensions/pitches, a set of selected elements with different metal/via routings is performed in DNSs to embed effects of PVs in the POD modes. Therefore, only one set of POD modes is required to cover the effects of material changes in the selected group of interconnect elements.

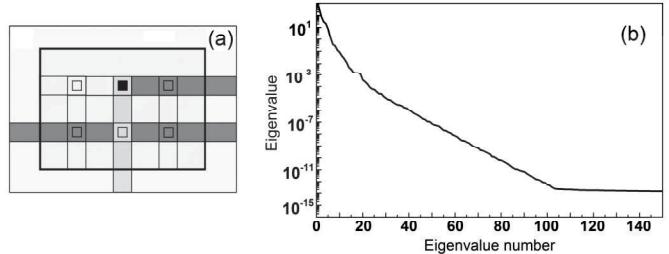

Fig. 3. (a) Element 2a placed in a larger dielectric domain for thermal data collection in DNSs. (b) Eigenvalue of the collected data from the 12 elements.

## III. APPLICATION OF PV-POD IN INTERCONNECTS

Dimensions and material properties of the NAND and IC structures in Fig. 1 are adopted from [15]. The generic element given in Fig. 1(c) is used in this work to illustrate the application of the multi-element POD thermal simulation approach.

### A. Data Collection – POD Mode Training

To generate robust POD modes for the generic element in Fig. 1(c), in addition to Elements 1a-6a given in Fig. 2, Elements 7a-12a with different metal/via routings in Fig. 2 are also included in ANSYS DNSs to collect thermal data. These elements offer a large number of metal/via routings to ensure each metal/via segment in Fig. 1(c) appears at least once. DNS of each element in Fig.2 is performed to collect temporal and spatial thermal data, subjected to joule heating in metal and BCs. To account for BCs , each element is embedded in a larger simulation domain, as shown in Fig. 3(a) for Element 2a. This BC setting however does not account for some BCs in the

multi-element demonstration in Sec. III.B and is partially responsible for the error in the demonstration.

### B. Demonstration in an Integrated Circuit

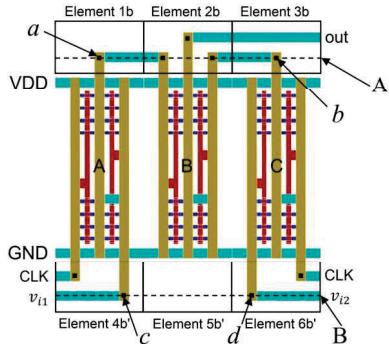

The multi-element PV-POD approach is implemented in a FinFET IC of Fig. 4 for the same circuit in Fig. 1(b) with Gates B and C swapped in the layout. The POD modes for the generic element and its mirror symmetric element are applied to all the six interconnect elements in Fig. 4. POD simulation of the entire IC structure also includes three NAND2 elements described by one set of POD modes developed in [15]. The nine-element POD simulation is thus performed with only these 2 sets of POD modes. Different random voltages are applied to  $v_{i1}$  and  $v_{i2}$  in Spice simulation at a 4 GHz voltage clock to estimate the power densities at device junctions and along each metal lines for both the POD simulations and DNSs in ANSYS.

Fig. 4. Layout for the circuit given in Fig. 1 in the multi-element demonstration.

Elements 2b, 3b and 5b' in Fig. 4 are different from any of the trained elements in Fig. 2. Although Elements 1b, 4b and 6b in Fig. 4 are identical to Elements 1a, 4a and 5a in Fig. 2, respectively, the BCs induced by the neighboring elements shown in Fig. 4 are very different from those in the training. In addition, there was no adiabatic boundary in the trained elements but at least one adiabatic boundary appears on the dielectric surface of each interconnect element in Fig. 4. Also, each interconnect element in Fig. 4 is neighbored by a parallel VDD or GND M1 line. The M1 lines impose entirely different BCs from those in the training. Similar to the previous study [15],  $N_\mu = 20$  is used in this demonstration. Only the solution derived from the PV-POD interconnect models are presented below, compared against the DNS in ANSYS. Thermal distributions in the FinFETs can be found in [15].

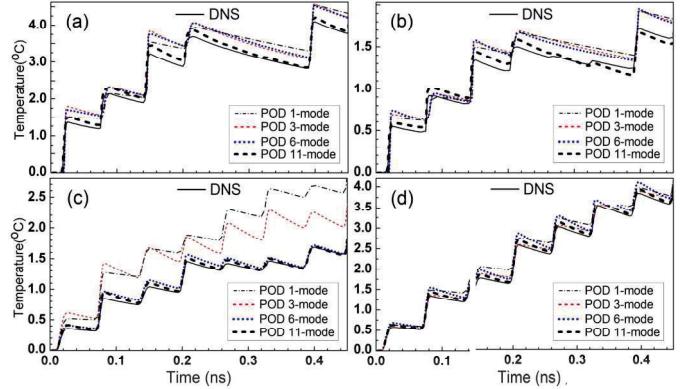

Dynamic temperatures at Points  $a$ ,  $b$ ,  $c$  and  $d$  in M1 labeled in Fig. 4 are illustrated in Fig. 5. Even with Points  $a$ ,  $c$  and  $d$  located in the elements identical to some trained elements, the error at Point  $a$  with 6 modes is still relatively large; it actually needs 10 or 11 modes to reach a good accuracy at Point  $a$ . It is however interesting to find in Fig. 5 very accurate solution with just 3 POD modes at Point  $d$  but poor accuracy at other locations. Also, better accuracy is observed for the 6-mode model at Points  $c$  and  $d$  than at Points  $a$  and  $b$ .

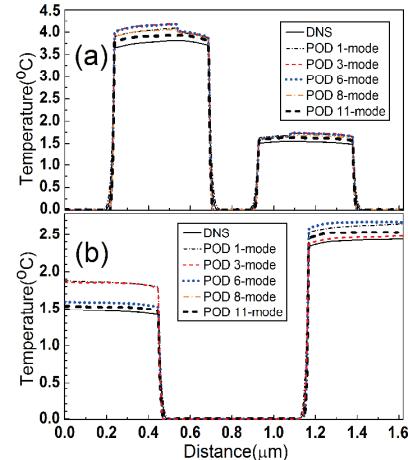

The temperature distributions at 0.215ns along Lines A and B (see Fig. 4) are illustrated in Figs. 6(a) and 6(b). Overall, the PV-POD model with more modes offers a higher accuracy. However, it is interesting to observe that the 3-mode model actually leads to a better accuracy than the 11 mode model in

Element 6b' along Line B, as shown in Fig. 6(b) and at Point  $d$  in Fig. 5. It should be noted that the POD only optimizes the LS error over the entire simulation time and domain instead of minimizing the local errors. The LS error for the multi-element POD simulation reduces substantially with more POD modes included, as displayed in Table I. An error of 2.67% can be reached with 12 POD modes included in each element.

Fig. 5. Dynamic temperatures at Points (a)  $a$ , (b)  $b$ , (c)  $c$  and (d)  $d$  in Fig. 5.

Fig. 6. Temperature profiles at 0.215 ns along (a) Line A and (b) Line B shown in Fig. 4.

TABLE I. LEAST SQUARE ERROR

| No. of modes | 1    | 3    | 6    | 8    | 10   | 11   | 12   |

|--------------|------|------|------|------|------|------|------|

| LS error (%) | 10.4 | 7.87 | 4.95 | 4.28 | 3.23 | 3.02 | 2.67 |

Although the errors presented in Fig. 6 and Table I for 11 modes and beyond are reasonably small, the accuracy is not as good as that of the thermal distribution in the FinFETs derived from the multi-element POD thermal simulation presented in [15], where the LS error below 1% can be achieved with 6 modes in each element. The reasons for the less accurate multi-element interconnect POD model presented in Figs. 5 and 6 are twofold. First, even with the discontinuous Galerkin method applied to the projection in (3), evident boundary discontinuities across the element interfaces are observed due to the truncation of the solution given in (2). Fig. 6(a) shows clear temperature discontinuities across element interfaces along Line A. Second, as discussed above, the BCs

implemented in the training of the POD modes for each element illustrated in Fig. 3 are clearly very different from those encountered by each element in the demonstration shown in Fig. 4. Even being trained by very different BCs, the POD approach is still able to offer a reasonably good accuracy. Future study will focus on more rigorous training of the POD modes and minimizing the boundary discontinuities.

In the nine-element POD simulation, a fine resolution is needed to capture nanometer-size hot spots in device junctions. With 10 modes in each interconnect element and 8 modes in each NAND2 element, a reduction in numerical DoF by more than 4 orders of magnitude can be achieved, compared to DNS, which amounts to a 3-order reduction in computational time.

#### IV. CONCLUSION

The concept of PVs is proposed in POD to capture material property variations due to metal/via routings in a dielectric structure. The developed PV-POD approach is applied to a group of interconnects that are used to wire FinFET standard cells. A generic element representing the interconnect group is projected onto the POD modes that are trained to capture the effects of variations for material properties, power sources and BCs. A nine-element thermal simulation of a small FinFET NAND2 IC is performed using two sets of POD modes that include one set for the generic interconnect element developed in this work and the other for the generic NAND2 element. A reasonably good accuracy is achieved even though the BCs implemented in the training are clearly different from those applied in the demonstration. In addition to the insufficient BCs for training the POD modes, the error also attributes to the large boundary discontinuities.

To the best of our knowledge, this study presents the first approach implementing the material PVs in POD. The PV-POD concept increases the flexibility for the POD simulation method. Typically, a different set of POD modes is needed for a structure when a material changes in a location. With the proposed PV-POD method, it is possible to generate a single set of POD modes to represent a structure with variations of material properties.

#### REFERENCES

- [1] T.Y. Chiang, B. Shieh, K. C. Saraswat, "Impact of Joule heating on scaling of deep sub-micron Cu/low-k interconnects," *Symp. VLSI Technol. Dig. Tech. Papers*, 2002, pp. 38–39.

- [2] K.-D. Lee *et al.*, "Effect of Joule Heating on electromigration in dual-damascene copper low-k interconnects," *2017 IEEE Int. Reliability Physics Symp. (IRPS)*, Monterey, CA, 2017, pp. 6B-6.1–6B-6.5.

- [3] S. Rzepka, K. Banerjee, E. Meusel, Chenming Hu, "Characterization of self-heating in advanced VLSI interconnect lines based on thermal finite element simulation," *IEEE Trans. Comp., Pack, Manufact. Tech.: Part A*, vol. 21, pp. 406–411, 1998.

- [4] A. Kim, B. Li, B. Linder, "Transient self-heating modeling and simulations of back-end-of-line interconnects," *2018 IEEE Int. Reliability Phys. Symp. (IRPS)*, Burlingame, CA, 2018, pp. P-MR.2-1-P-MR.2-5.

- [5] A. Bansal, *et al.*, "Compact thermal models for estimation of temperature-dependent power/performance in FinFET technology," *Asia & South Pacific Conf. Design Automation, 2006*, Yokohama, Japan, 2006, pp. 24–27.

- [6] K. Zhang, M. C. Cheng, "Thermal Circuit for SOI Structure Accounting for Non-Isothermal effect," *IEEE Trans. Electron Devices*, Vol 57, pp. 2838–2847, November 2010.

- [7] F. Yu, M. C. Cheng, "Electrothermal Simulation of SOI CMOS Analog Integrated Circuits," *Solid-State Electronics*, vol. 51, pp. 691–702, 2007.

- [8] M.C. Cheng, J. A. Smith, W. Jia, R. Coleman, "An Effective Thermal Model for FinFET Structure," *IEEE Trans. Electron Devices*, Vol. 61, No. 1, pp. 202–206, 2014.

- [9] R. Sabelka, C. Harlander, S. Selberherr, "The state of the art in interconnect simulation," *2000 Int. Conf. Simulation Semiconductor Processes & Devices (SISPAD 2000)*, Seattle, WA, 2000, pp. 6–11.

- [10] G. Kumar, M. Singh, A. Bulusu, G. Trivedi, "A Parallel Device Simulator Based on Finite Element Method," in *2015 International Conference on Computational Science and Computational Intelligence (CSCI)*, Las Vegas, 2015.

- [11] D. Chen, E. Li, E. Rosenbaum, S. M. Kang, "Interconect thermalmodeling for accurate simulation of circuit timing and reliability," *IEEE Trans. Computer-Aided Design*, vol. 19, pp. 197–205, 2000.

- [12] J. L. Lumley, *Atmospheric Turbulence and Wave Propagation*, Moscow, Russia, Nauka publisher, 166 (1967).

- [13] J. L. Lumley, *Stochastic Tools in Turbulence*, Academic, New York, 1970; reprint, Dover publisher 2007.

- [14] Y. Maday, E. M. Rønquist, "A reduced-basis element method," *Comptes Rendus Math.*, 335, pp. 195–200, 2002.

- [15] W. Jia, B. T. Helenbrook, M.C. Cheng, "Fast Thermal Simulation of FinFET Circuits Based on a Multiblock Reduced-Order Model," *IEEE Trans. CAD ICs. Syst*, vol. 35, pp. 1114–1124, 2016.

- [16] W. Jia, B. T. Helenbrook, M.C. Cheng, "Thermal modeling of multi-fin field effect transistor structure using proper orthogonal decomposition," *IEEE Trans. Electron Devices*, vol. 61, pp. 2752–2759, 2014.

- [17] W. Jia, B. Helenbrook, M.C. Cheng, "Thermal modeling of multi-gate field effect transistors based on a reduced order model," *Proc. IEEE Annu. Semicond. Therm. Meas. Manage. Symp.*, San Jose, CA, 2014, pp. 230–235.

- [18] D. S. Meyer, B. T. Helenbrook, M.-C. Cheng, "Proper orthogonal decomposition-based reduced basis element thermal modeling of integrated circuits," *Int. J. Numer. Meth. Engng.*, 112, pp. 479–500, 2017.

- [19] R. Venters, B. T. Helenbrook, K. Zhang, M.C. Cheng, "Proper-orthogonal-decomposition based thermal modeling of semiconductor structures," *IEEE Trans. Electron Devices*, vol. 59, pp. 2924–2931, 2012.

- [20] D. N. Arnold, F. Brezzi, B. Cockburn, D. Marini, *Discontinuous Galerkin methods for Elliptic Problems* (Lecture Notes in Computational Sci. & Eng.), vol. 11. Berlin, Germany: Springer, 2000, pp. 89–101.

- [21] D. N. Arnold, F. Brezzi, B. Cockburn, L. Donatella Marini, "Unified analysis of discontinuous Galerkin methods for elliptic problems," *SIAM J. Numer. Anal.*, vol. 39, pp. 1749–1779, 2002.

- [22] L. Sirovich, "Turbulence and the dynamics of coherent structures. I–Coherent structures. II–Symmetries and transformations. III–Dynamics and scaling," *Quart. Appl. Math.*, vol. 45, pp. 561–571 and 573–590, Oct. 1987.