Nidhin Kurian Kalarickal<sup>®</sup>, Zhanbo Xia<sup>®</sup>, *Member, IEEE*, Hsien-Lien Huang, Wyatt Moore, Yumo Liu, Mark Brenner, Jinwoo Hwang, and Siddharth Rajan

Abstract—Maintaining high average fields between the gate and drain is imperative in achieving near theoretical performance in ultra-wide band gap semiconductors like  $\beta$ -Ga<sub>2</sub>O<sub>3</sub>. In this letter we report on a field management strategy to reduce the peak electric field at the drain side corner of the gate by using a composite dielectric layer consisting of an extreme permittivity dielectric like BaTiO<sub>3</sub> and a low- $\kappa$  dielectric like SiO<sub>2</sub> overlapped over the gate electrode. Using this strategy in  $\beta$ -(Al<sub>0.18</sub>Ga<sub>0.82</sub>)<sub>2</sub>O<sub>3</sub>/Ga<sub>2</sub>O<sub>3</sub> double heterojunction field effect transistor, we achieved a record average breakdown field of 5.5 MV/cm at a gate-drain spacing of 1.15  $\mu$ m along with an improved power figure of merit of 408 MW/cm<sup>2</sup>. The reported works shows the effectiveness of integrating extreme dielectric materials with ultra-wide band gap semiconductors in significantly improving breakdown performance.

*Index Terms*—Gallium oxide, perovskite oxide, barium titanate, power figure of merit, breakdown.

# I. INTRODUCTION

ULTRA-WIDE bandgap semiconductors like  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> and AlGaN offer the next avenue for improved performance in power switching devices [1]–[3]. The promise in these materials stem from the much larger breakdown field strength [4]–[6], offering improved theoretical performance in power devices as described by the Baliga's figure of merit  $(V_{br}^2/R_{ON})$  [7]. Among the ultra-wide band gap materials,  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> stands out mainly due to the availability of bulk substrates that can be grown from melt [8]–[13]. Therefore, if the theoretical breakdown field and transport properties can

Manuscript received March 17, 2021; revised April 2, 2021; accepted April 4, 2021. Date of publication April 9, 2021; date of current version May 21, 2021. This work was supported in part by the Air Force Office of Scientific Research (Program Manager: Dr. Ali Sayir) under Award FA9550-18-1-0479 and in part by the National Science Foundation Program under Grant NSF ECCS-1809682. The review of this letter was arranged by Editor G. Han. (*Corresponding author: Nidhin Kurian Kalarickal.*)

Nidhin Kurian Kalarickal, Zhanbo Xia, Wyatt Moore, and Mark Brenner are with the Department of Electrical and Computer Engineering, The Ohio State University, Columbus, OH 43210 USA (e-mail: kalarickal.1@osu.edu).

Hsien-Lien Huang, Yumo Liu, and Jinwoo Hwang are with the Department of Material Science and Engineering, The Ohio State University, Columbus, OH 43210 USA.

Siddharth Rajan is with the Department of Electrical and Computer Engineering, The Ohio State University, Columbus, OH 43210 USA, and also with the Department of Material Science and Engineering, The Ohio State University, Columbus, OH 43210 USA.

Color versions of one or more figures in this letter are available at https://doi.org/10.1109/LED.2021.3072052.

Digital Object Identifier 10.1109/LED.2021.3072052

be achieved,  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> power switching devices with better performance will be available at lower cost.

The absence of p type doping and availability of dielectrics that can sustain electric field significantly higher than 8 MV/cm makes achieving the theoretical breakdown field strength challenging. Integration of extreme- $\kappa$  ( $\epsilon > 100$ ) gate dielectrics with ultra-wide band gap materials is one approach to solving this problem especially in lateral field effect transistors, [6], [14] where the presence of extreme- $\kappa$ gate dielectric has been shown to result in improved uniformity in the electric field profile [15]. The large dielectric constant also ensures that the vertical component of the electric field seen at the gate is significantly reduced. But, as will be shown in section II, the lateral component of the electric field still leads to a significant peak electric field at the gate corner.

In this letter, we show using 2D device simulation followed by experimental demonstration, a field management strategy utilizing a composite extreme- $\kappa$ /low- $\kappa$  dielectric overlapping the gate, to reduce the peak electric field at the gate corner, resulting in improved breakdown performance.

#### II. DEVICE DESIGN AND FABRICATION

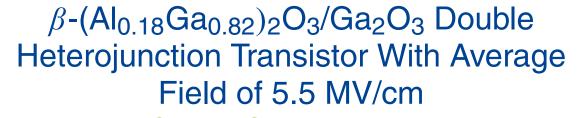

Consider the  $\beta$ -(AlGa)<sub>2</sub>O<sub>3</sub>/Ga<sub>2</sub>O<sub>3</sub> thin spacer (1 nm) modulation doped double heterojunction transistor with a 2D electron gas density of  $1 \times 10^{13}$  cm<sup>-2</sup> as shown in Fig.1 (a) (transistor A) [16], [17]. Transistor A has a bilayer gate dielectric stack consisting of a low- $\kappa$  dielectric (dielectric 1-Al<sub>2</sub>O<sub>3</sub>) and an extreme- $\kappa$  dielectric (BaTiO<sub>3</sub>,  $\epsilon_b = 203$ ) of thickness  $t_{b1}$ . Fig.1 (c) shows the 2-D distribution of electric field between the gate and drain terminals of transistor A at a reverse bias of 800 V (average field = 4 MV/cm). The plot in Fig.1 (c) shows the electric field profile along the cutline A-A'. We see that the presence of extreme- $\kappa$  dielectric leads to significant uniformity of electric field within the gate-drain region as has been reported earlier [18], but at the gate corner this uniformity is lost resulting in a high peak field of  $\sim$ 9 MV/cm. The large dielectric discontinuity present in the y direction results in partial screening of the negative charges on the gate. But due to absence of polarization charges along the vertical edge of the gate (Fig.1 (a)), the negative charges are not fully screened, resulting in a significant peak electric field at the corner. This is detrimental since most of the extreme- $\kappa$  dielectrics like BaTiO<sub>3</sub> and SrTiO<sub>3</sub> have breakdown fields similar to  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> [19].

Fig. 1 (b) shows a transistor design (transistor B) with a field management structure that consists of an extreme- $\kappa$ /low- $\kappa$  composite dielectric deposited over the gate electrode of

0741-3106 © 2021 IEEE. Personal use is permitted, but republication/redistribution requires IEEE permission. See https://www.ieee.org/publications/rights/index.html for more information.

Fig. 1. (a) Transistor design A (gate-drain region). (b) Transistor design B (gate-drain region). (c) Simulated electric field contour profile in transistor A at a reverse bias of 800 V. (d) simulated electric field contour profile in transistor B at a reverse bias of 800 V. The plots in (c) and (d) show the electric field profile along the cutline A-A' as shown.

transistor A. This provides an extreme dielectric discontinuity in both x and y directions. Fig. 1 (d) shows the electric field distribution between the gate and drain terminals of transistor B at the same reverse bias of 800 V. Due to the presence of the extreme dielectric discontinuity in both directions, the polarization charges formed in the extreme- $\kappa$ dielectric completely screens the negative charges on the gate (Fig.1 (b)), reducing the overall peak field at the gate corner. The plot in Fig.1 (d) quantifies this reduction in peak field to below 6 MV/cm. Usage of a low- $\kappa$  overlap dielectric with a large breakdown field like SiO<sub>2</sub>, would ensure that transistor B has a much higher breakdown voltage compared to transistor A. The low- $\kappa$  overlap dielectric is required since in its absence, the peak field is at the air/extreme- $\kappa$  interface which is detrimental.

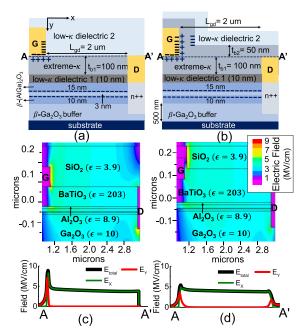

We fabricated lateral field effect transistors similar to transistor B using  $\beta$ -(Al<sub>0.18</sub>Ga<sub>0.82</sub>)<sub>2</sub>O<sub>3</sub>/ Ga<sub>2</sub>O<sub>3</sub> modulation doped double heterojunction, epitaxially grown using molecular beam epitaxy (MBE) as shown in Fig. 2 (a) and (c). Fe delta doping was carried out at the substrate-epilayer growth interface to prevent formation of unintentional parasitic channel due to Si impurity. Further details on the MBE growth of the epilayer and doping may be found in references [16], [17], [20].

Ohmic contacts were laid down using MBE regrowth technique [21] followed by ohmic metallization using Ti/Au/Ni (40/50/50 nm) stack annealed at 470 °C in N<sub>2</sub> ambient. Device isolation was carried out by etching a 180 nm deep mesa structure using BCl<sub>3</sub>/Ar based dry etch [22]. 12.5 nm of Al<sub>2</sub>O<sub>3</sub> dielectric (10 nm intended) was then deposited using atomic layer deposition (ALD). The Al<sub>2</sub>O<sub>3</sub>serves as a protective layer preventing damage to semiconductor surface during the subsequent radio frequency sputtering (670 °C) of BaTiO<sub>3</sub> gate dielectric (95 nm). Further details on sputtering

Fig. 2. (a) Epitaxial and final device structure. (b) Comparison of the capacitance-voltage measurements performed pre and post deposition of gate dielectric layers. (c) Cross sectional STEM image of BaTiO<sub>3</sub>/ $\beta$ -Ga<sub>2</sub>O<sub>3</sub> DHFET ( $L_g = 0.9\mu$ m) showing the BaTiO<sub>3</sub>/SiO<sub>2</sub> field management structure and the epilayer and dielectric stack. The vertical protrusions on both sides of the gate are unintentional lift off edges. (d) Schematic band diagram of SiO<sub>2</sub>/BaTiO<sub>3</sub>/ $\beta$ -Ga<sub>2</sub>O<sub>3</sub> DHFET including the positive fixed charges at the Al<sub>2</sub>O<sub>3</sub>/ $\beta$ -(Al<sub>0.18</sub>Ga<sub>0.82</sub>)<sub>2</sub>O<sub>3</sub> interface (e) Charge diagram showing the distribution of charges in the device.

of BaTiO<sub>3</sub> may be found in [18]. The extreme- $\kappa$  gate dielectric is intentionally made thick since this improves the uniformity of electric field profile between the gate and drain [18]. Cr/Pt (5/100 nm) metal stack was then deposited to form the Schottky gate. Cr layer was added to improve adhesion of Pt with BaTiO<sub>3</sub>. Following the deposition of gate, 50 nm of BaTiO<sub>3</sub> (RF sputtering) and 150 nm of SiO<sub>2</sub> (plasma enhanced chemical vapor deposition at 250 °C) is deposited to form the overlap field management structure as shown in Fig.2 (a) and (c).

## **III. RESULTS AND DISCUSSION**

Hall effect measurements were carried out on the epilayer before and after the deposition of gate dielectric layers  $(Al_2O_3 + BaTiO_3)$  giving a mobility of 85 cm<sup>2</sup>/V-s and a charge density of  $9.4 \times 10^{12}$  cm<sup>-2</sup>. Transfer length measurements (TLM) showed a total contact resistance of 5.5  $\Omega$ ·mm in these devices pre deposition of BaTiO<sub>3</sub>. The specific contact resistance between the metal and regrown layer  $(R_{sh} \sim 250 \ \Omega/sq)$  was found to be  $10^{-6}\Omega \cdot cm^2$ . Fig.2 (b) compares the capacitance-voltage (C-V, 200 µm pads) measurements performed on the devices before and after the deposition of gate dielectric layers (Al<sub>2</sub>O<sub>3</sub>+BaTiO<sub>3</sub>). Negligible frequency dispersion is observed below 100 kHz, whereas significant dispersion is observed at 1 MHz. Since the dispersion is present before and after the deposition of gate dielectrics, the traps responsible must be inherent to the epitaxial structure and not from the dielectrics. As shown in Fig.2 (a), intentional Fe doping was carried out at the epilayer/substrate interface to compensate parasitic channel formation due to remnant

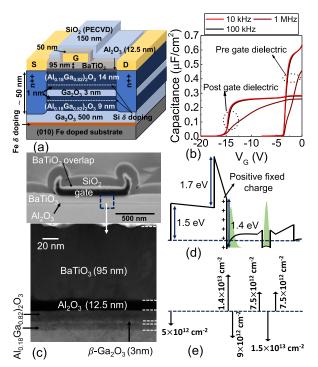

Fig. 3. (a) Output characteristics of BaTiO<sub>3</sub>/ $\beta$ -Ga<sub>2</sub>O<sub>3</sub> DHFET ( $L_g = 0.9 \text{ um}, L_{sd} = 2.6 \mu \text{m}$ ). (b) Transfer characteristics of BaTiO<sub>3</sub>/ $\beta$ -Ga<sub>2</sub>O<sub>3</sub> DHFET ( $L_g = 0.9 \text{ um}, L_{sd} = 2.6 \mu \text{m}$ ). (c) Pulsed I-V characteristics of BaTiO<sub>3</sub>/ $\beta$ -Ga<sub>2</sub>O<sub>3</sub> DHFET ( $L_g = 1.2 \mu \text{m}, L_{sd} = 4 \mu \text{m}$ ). (d) Measured breakdown voltage and average breakdown field vs  $L_{gd}$ . (e) Reverse leakage current as a function of gate-drain bias for different values of  $L_{gd}$ . (f)  $V_{br} - R_{ON}$  benchmark plot for  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> lateral transistors [25]–[32].

Si impurities. This results in a significantly longer Fe tail  $(\sim 500 \text{ nm})$  deep into the buffer [16] which was previously shown to cause trapping and dispersion issues [23]. Increasing the buffer thickness such that the Fe tail is kept at least 400 nm away from the channel was previously found to reduce Fe related dispersion issues [23]. By comparing the 2DEG capacitance value measured before ( $V_g = -1$  V) and after deposition ( $V_g = -7.2$  V) of gate dielectrics, a dielectric constant of 203 for the BaTiO<sub>3</sub> layer is estimated ( $\epsilon_{Al_2O_3}$  of 8.9 is assumed [24]). Channel charge density  $(n_s)$  of  $1.1 \times 10^{13}$  cm<sup>-2</sup> is obtained in devices before the deposition of gate dielectrics, whereas  $n_s$  of  $2.4 \times 10^{13}$  cm<sup>-2</sup> is observed in devices after the deposition of gate dielectric layers (100 kHz). This increase in  $n_s$  is likely due to the presence of positive fixed charges at the Al<sub>2</sub>O<sub>3</sub>/ $\beta$ -(Al<sub>0.18</sub>Ga<sub>0.82</sub>)<sub>2</sub>O<sub>3</sub> interface resulting in the formation of a parasitic channel. Fig.2 (d), (f) shows the band diagram and charge diagram of the device considering this positive fixed charge density  $(1.4 \times 10^{13} \text{ cm}^{-2})$  at the Al<sub>2</sub>O<sub>3</sub>/ $\beta$ -(Al<sub>0.18</sub>Ga<sub>0.82</sub>)<sub>2</sub>O<sub>3</sub> interface assuming a schottky barrier height of 1.5 eV to BaTiO<sub>3</sub> and band offsets given in [6].

Fig.3 (a) shows the measured output characteristics of the BaTiO<sub>3</sub>/ $\beta$ -Ga<sub>2</sub>O<sub>3</sub> DHFET with a source-drain ( $L_{sd}$ ) spacing (gate length and gate-drain spacing) of 2.6  $\mu$ m (0.9  $\mu$ m and 1.15  $\mu$ m). The device shows an on-resistance ( $R_{ON}$ ) of 28.6  $\Omega$ -mm and a max drain current of 220 mA/mm at a gate bias of 2 V. As is clear from Fig.3 (a), the parasitic 2DEG at

the Al<sub>2</sub>O<sub>3</sub>/ $\beta$ -(Al<sub>0.18</sub>Ga<sub>0.82</sub>)<sub>2</sub>O<sub>3</sub> interface being a low mobility channel leads to only a minimal increase in drain current (or reduction in  $R_{ON}$ ) above a gate voltage of -4 V. The measured  $R_{ON}$  increases from 28.6  $\Omega$ ·mm at  $L_{sd}$  of 2.6  $\mu$ m to 59  $\Omega$ ·mm at  $L_{sd}$  of 6.8  $\mu$ m. Fig.3 (b) shows the transfer characteristics of the same device showing an on-off ratio of roughly 10<sup>7</sup>.

Fig.3 (c) shows the pulsed I-V characteristics of a representative device with  $L_g = 1.2 \ \mu m$  an  $L_{sd} = 4 \ \mu m$ . Pulse width was set to a value of 5  $\mu$ s with a duty cycle of 0.1%. A significant increase in  $R_{ON}$  from 41  $\Omega$ ·mm to 125  $\Omega$ ·mm is observed when comparing the DC and pulsed (V<sub>GQ</sub> = -19 V, V<sub>DQ</sub> = 20 V) measurements. Similar to the dispersion observed in the C-V measurements (Fig.2 (b)), the intentional Fe doping at the epilayer/substrate interface and the resulting long Fe tail deep into the buffer was found to cause trapping, resulting in current collapse [23]. Increasing the buffer layer thickness ensuring sufficient (>400 nm) separation between the channel and the Fe tail would ensure significantly improved pulsed I-V characteristics in future devices.

Two terminal breakdown (gate-drain) measurements were carried out on the devices to assess the effectiveness of the field management structure. Fig.3 (d) and (e) shows the breakdown characteristics of the devices as the gate-drain spacing is increased from 1.15  $\mu$ m to 5.15  $\mu$ m. The device dimensions reported were confirmed using cross sectional STEM imaging. The measured breakdown voltage (averaged value at a given  $L_{gd}$ ) increases from 636 V (5.5 MV/cm) to 1095 V (2.1 MV/cm) as the gate-drain spacing  $(L_{gd})$  is increased from 1.15  $\mu$ m to 5.15  $\mu$ m, with the best device at  $L_{gd} = 1.15 \ \mu m \ (L_{sd} = 2.6 \ \mu m)$  showing a breakdown voltage of 660 V (5.7 MV/cm). The average field ( $F_{av}$ ) of 5.7 MV/cm is the highest reported in any  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> transistor device showing the effectiveness of the field management strategy used in this study. At larger gate-drain spacing the field-management is less effective due to the large  $n_s(2.4 \times 10^{13} \text{ cm}^{-2})$  being modulated [18].

The power figure of merit for these devices  $(V_{br}^2/R_{ON})$  can be estimated by normalizing  $R_{ON}$  to the active area of the transistor,  $L_{sd} + 2L_T$ , where  $L_T$  corresponds to the transfer length between the metal and the regrown layer  $(2L_T =$  $1.3 \ \mu\text{m})$ . Record high PFOM of 408 MW/cm<sup>2</sup> (558 MW/cm<sup>2</sup> without  $L_T$ ) at an  $L_{sd}$  of 3.5  $\ \mu\text{m}$  ( $R_{ON} =$  1.72 m $\Omega \cdot \text{cm}^2$ ,  $V_{br} =$  840 V) and 390 MW/cm<sup>2</sup> (586 MW/cm<sup>2</sup> without  $L_T$ ) at an  $L_{sd}$  of 2.6  $\ \mu\text{m}$  ( $R_{ON} =$  1.11 m $\Omega \cdot \text{cm}^2$ ,  $V_{br} =$  660 V) are obtained as shown in Fig. 3 (f). We note that the high PFOM was achieved despite the parasitic channel which did not contribute to conduction.

### IV. CONCLUSION

In conclusion, we demonstrate a field management strategy to reduce the peak electric field at the drain side corner of the gate by using an extreme- $\kappa$  /low- $\kappa$  composite dielectric overlapped over the gate electrode. Utilizing this method in BaTiO<sub>3</sub>/ $\beta$ -Ga<sub>2</sub>O<sub>3</sub> double heterojunction transistor enabled a record average electric field of 5.5 MV/cm and a PFOM of 408 MW/cm<sup>2</sup> at a source-drain spacing of 3.5  $\mu$ m.

#### ACKNOWLEDGMENT

Electron microscopy was performed at the Center for Electron Microscopy and Analysis at The Ohio State University.

## REFERENCES

- J. Y. Tsao, S. Chowdhury, M. A. Hollis, D. Jena, N. M. Johnson, K. A. Jones, R. J. Kaplar, S. Rajan, C. G. Van de Walle, E. Bellotti, C. L. Chua, R. Collazo, M. E. Coltrin, J. A. Cooper, K. R. Evans, S. Graham, T. A. Grotjohn, E. R. Heller, M. Higashiwaki, M. S. Islam, P. W. Juodawlkis, M. A. Khan, A. D. Koehler, J. H. Leach, U. K. Mishra, R. J. Nemanich, R. C. N. Pilawa-Podgurski, J. B. Shealy, Z. Sitar, M. J. Tadjer, A. F. Witulski, M. Wraback, and J. A. Simmons, "Ultrawide-bandgap semiconductors: Research opportunities and challenges," *Adv. Electron. Mater.*, vol. 4, no. 1, Jan. 2018, Art. no. 1600501, doi: 10.1002/aelm.201600501.

- [2] R. J. Kaplar, A. A. Allerman, A. M. Armstrong, M. H. Crawford, J. R. Dickerson, A. J. Fischer, A. G. Baca, and E. A. Douglas, "Review—Ultra-wide-bandgap AlGaN power electronic devices," *ECS J. Solid State Sci. Technol.*, vol. 6, no. 2, pp. Q3061–Q3066, Dec. 2016, doi: 10.1149/2.0111702jss.

- [3] A. Raman, S. Dasgupta, S. Rajan, J. S. Speck, and U. K. Mishra, "AlGaN channel high electron mobility transistors: Device performance and power-switching figure of merit," *Jpn. J. Appl. Phys.*, vol. 47, no. 5R, p. 3359, May 2008, doi: 10.1143/JJAP.47.3359.

- [4] X. Yan, I. S. Esqueda, J. Ma, J. Tice, and H. Wang, "High breakdown electric field in β – Ga<sub>2</sub>O<sub>3</sub>/graphene vertical barristor heterostructure," *Appl. Phys. Lett.*, vol. 112, no. 3, Jan. 2018, Art. no. 032101, doi: 10.1063/1.5002138.

- [5] T. Razzak, H. Chandrasekar, K. Hussain, C. H. Lee, A. Mamun, H. Xue, Z. Xia, S. H. Sohel, M. W. Rahman, S. Bajaj, C. Wang, W. Lu, A. Khan, and S. Rajan, "BaTiO<sub>3</sub>/Al<sub>0.58</sub>Ga<sub>0.42</sub>N lateral heterojunction diodes with breakdown field exceeding 8 MV/cm," *Appl. Phys. Lett.*, vol. 116, no. 2, Jan. 2020, Art. no. 023507, doi: 10.1063/1.5130590.

- [6] Z. Xia, H. Chandrasekar, W. Moore, C. Wang, A. J. Lee, J. McGlone, N. K. Kalarickal, A. Arehart, S. Ringel, F. Yang, and S. Rajan, "Metal/BaTiO<sub>3</sub>/β – Ga<sub>2</sub>O<sub>3</sub> dielectric heterojunction diode with 5.7 MV/cm breakdown field," *Appl. Phys. Lett.*, vol. 115, no. 25, Dec. 2019, Art. no. 252104, doi: 10.1063/1.5130669.

- [7] B. J. Baliga, "Power semiconductor device figure of merit for high-frequency applications," *IEEE Electron Device Lett.*, vol. 10, no. 10, pp. 455–457, Oct. 1989, doi: 10.1109/55.43098.

- [8] H. Aida, K. Nishiguchi, H. Takeda, N. Aota, K. Sunakawa, and Y. Yaguchi, "Growth of β – Ga<sub>2</sub>O<sub>3</sub> single crystals by the edge-defined, film fed growth method," *Jpn. J. Appl. Phys.*, vol. 47, no. 11R, p. 8506, Nov. 2008, doi: 10.1143/JJAP.47.8506.

- [9] A. Kuramata, K. Koshi, S. Watanabe, Y. Yamaoka, T. Masui, and S. Yamakoshi, "High-quality β – Ga<sub>2</sub>O<sub>3</sub> single crystals grown by edgedefined film-fed growth," Jpn. J. Appl. Phys., vol. 55, no. 12, Nov. 2016, Art. no. 1202A2, doi: 10.7567/JJAP.55.1202A2.

- [10] T. Oishi, Y. Koga, K. Harada, and M. Kasu, "High-mobility  $\beta Ga_2 O_3()$  single crystals grown by edge-defined film-fed growth method and their Schottky barrier diodes with Ni contact," *Appl. Phys. Exp.*, vol. 8, no. 3, Feb. 2015, Art. no. 031101, doi: 10.7567/APEX.8.031101.

- [11] Z. Galazka, R. Uecker, D. Klimm, K. Irmscher, M. Naumann, M. Pietsch, A. Kwasniewski, R. Bertram, S. Ganschow, and M. Bickermann, "Scaling-up of bulk  $\beta Ga_2O_3$  single crystals by the czochralski method," *ECS J. Solid State Sci. Technol.*, vol. 6, no. 2, pp. Q3007–Q3011, 2017, doi: 10.1149/2.0021702jss.

- [12] Z. Galazka, R. Uecker, K. Irmscher, M. Albrecht, D. Klimm, M. Pietsch, M. Brützam, R. Bertram, S. Ganschow, and R. Fornari, "Czochralski growth and characterization of  $\beta Ga_2O_3$  single crystals," *Crystal Res. Technol.*, vol. 45, no. 12, pp. 1229–1236, Dec. 2010, doi: 10.1002/crat.201000341.

- [13] Y. Tomm, P. Reiche, D. Klimm, and T. Fukuda, "Czochralski grown Ga<sub>2</sub>O<sub>3</sub> crystals," *J. Cryst. Growth*, vol. 220, no. 4, pp. 510–514, Dec. 2000, doi: 10.1016/S0022-0248(00)00851-4.

- [14] V. D. Wheeler, D. I. Shahin, M. J. Tadjer, and C. R. Eddy, "Band alignments of atomic layer deposited ZrO<sub>2</sub> and HfO<sub>2</sub> high-K dielectrics with (-201)  $\beta$  *Ga*<sub>2</sub>*O*<sub>3</sub>," *ECS J. Solid State Sci. Technol.*, vol. 6, no. 2, pp. Q3052–Q3055, Dec. 2016, doi: 10.1149/2.0131702jss.

- [15] Z. Xia, C. Wang, N. K. Kalarickal, S. Stemmer, and S. Rajan, "Design of transistors using high-permittivity materials," *IEEE Trans. Electron Devices*, vol. 66, no. 2, pp. 896–900, Feb. 2019, doi: 10.1109/TED. 2018.2888834.

- [16] N. K. Kalarickal, Z. Xia, J. F. McGlone, Y. Liu, W. Moore, A. R. Arehart, S. A. Ringel, and S. Rajan, "High electron density  $\beta$ -(Al<sub>0.17</sub>Ga<sub>0.83</sub>)<sub>2</sub>O<sub>3</sub>/Ga<sub>2</sub>O<sub>3</sub> modulation doping using an ultra-thin (1 nm) spacer layer," *J. Appl. Phys.*, vol. 127, no. 21, Jun. 2020, Art. no. 215706, doi: 10.1063/5.0005531.

- [17] Y. Zhang, C. Joishi, Z. Xia, M. Brenner, S. Lodha, and S. Rajan, "Demonstration of  $\beta$ -(AlxGa<sub>1-x</sub>)<sub>2</sub>O<sub>3</sub>/Ga<sub>2</sub>OO<sub>3</sub> double heterostructure field effect transistors," *Appl. Phys. Lett.*, vol. 112, no. 23, Jun. 2018, Art. no. 233503, doi: 10.1063/1.5037095.

- [18] N. K. Kalarickal, Z. Feng, A. F. M. A. U. Bhuiyan, Z. Xia, W. Moore, J. F. McGlone, A. R. Arehart, S. A. Ringel, H. Zhao, and S. Rajan, "Electrostatic engineering using extreme permittivity materials for ultra-wide bandgap semiconductor transistors," *IEEE Trans. Electron Devices*, vol. 68, no. 1, pp. 29–35, Jan. 2021, doi: 10.1109/TED.2020. 3037271.

- [19] J. F. Scott, Ferroelectric Memories. Berlin, Germany: Springer, 2000, p. 59.

- [20] N. K. Kalarickal, Z. Xia, J. McGlone, S. Krishnamoorthy, W. Moore, M. Brenner, A. R. Arehart, S. A. Ringel, and S. Rajan, "Mechanism of Si doping in plasma assisted MBE growth of β – Ga<sub>2</sub>O<sub>3</sub>," *Appl. Phys. Lett.*, vol. 115, no. 15, Oct. 2019, Art. no. 152106, doi: 10.1063/1.5123149.

- [21] Z. Xia, C. Joishi, S. Krishnamoorthy, S. Bajaj, Y. Zhang, M. Brenner, S. Lodha, and S. Rajan, "Delta doped  $\beta Ga_2O_3$  field effect transistors with regrown ohmic contacts," *IEEE Electron Device Lett.*, vol. 39, no. 4, pp. 568–571, Apr. 2018, doi: 10.1109/LED.2018. 2805785.

- [22] Z. Xia, H. Xue, C. Joishi, J. McGlone, N. Kalarickal, S. Sohel, M. Brenner, A. Arehart, S. Ringel, S. Lodha, W. Lu, and S. Rajan, " $\beta - Ga_2O_3$  delta-doped field effect transistors with current gain cutoff frequency of 27 GHz," *IEEE Electron Device Lett.*, vol. 40, no. 7, pp. 1052–1055, Jun. 2019, doi: 10.1109/LED.2019. 2920366.

- [23] C. Joishi, Z. Xia, J. McGlone, Y. Zhang, A. R. Arehart, S. Ringel, S. Lodha, and S. Rajan, "Effect of buffer iron doping on delta-doped  $\beta - Ga_2O_3$  metal semiconductor field effect transistors," *Appl. Phys. Lett.*, vol. 113, no. 12, Sep. 2018, Art. no. 123501, doi: 10.1063/1.5039502.

- [24] T. Kamimura, D. Krishnamurthy, A. Kuramata, S. Yamakoshi, and M. Higashiwaki, "Epitaxially grown crystalline Al<sub>2</sub>O<sub>3</sub> interlayer on  $\beta Ga_2O_3(010)$  and its suppressed interface state density," *Jpn. J. Appl. Phys.*, vol. 55, no. 12, Oct. 2016, Art. no. 1202B5, doi: 10.7567/JJAP.55.1202B5.

- [25] Y. Lv, H. Liu, X. Zhou, Y. Wang, X. Song, Y. Cai, Q. Yan, C. Wang, S. Liang, J. Zhang, Z. Feng, H. Zhou, S. Cai, and Y. Hao, "Lateral  $\beta Ga_2O_3$  MOSFETs with high power figure of merit of 277 MW/cm<sup>2</sup>," *IEEE Electron Device Lett.*, vol. 41, no. 4, pp. 537–540, Apr. 2020, doi: 10.1109/LED.2020.2974515.

- [26] K. Tetzner, E. B. Treidel, O. Hilt, A. Popp, S. B. Anooz, G. Wagner, A. Thies, K. Ickert, H. Gargouri, and J. Würfl, "Lateral 1.8 kV β-Ga<sub>2</sub>O<sub>3</sub> MOSFET with 155 MW/cm<sup>2</sup> power figure of merit," *IEEE Electron Device Lett.*, vol. 40, no. 9, pp. 1503–1506, Sep. 2019, doi: 10.1109/LED.2019.2930189.

- [27] Y. Lv, X. Zhou, S. Long, X. Song, Y. Wang, S. Liang, Z. He, T. Han, X. Tan, Z. Feng, H. Dong, X. Zhou, Y. Yu, S. Cai, and M. Liu, "Sourcefield-plated β – Ga<sub>2</sub>O<sub>3</sub> MOSFET with record power figure of merit of 50.4 MW/cm<sup>2</sup>," *IEEE Electron Device Lett.*, vol. 40, no. 1, pp. 83–86, Jan. 2019, doi: 10.1109/LED.2018.2881274.

- [28] C. Joishi, Y. Zhang, Z. Xia, W. Sun, A. R. Arehart, S. Ringel, S. Lodha, and S. Rajan, "Breakdown characteristics of β-(Al<sub>0.22</sub>Ga<sub>0.78</sub>)<sub>2</sub>O<sub>3</sub>/Ga<sub>2</sub>O<sub>3</sub> field-plated modulation-doped field-effect transistors," *IEEE Electron Device Lett.*, vol. 40, no. 8, pp. 1241–1244, Aug. 2019, doi: 10.1109/LED.2019.2921116.

- [29] K. Zeng, A. Vaidya, and U. Singisetti, "1.85 kV breakdown voltage in lateral field-plated Ga<sub>2</sub>O<sub>3</sub> MOSFETs," *IEEE Electron Device Lett.*, vol. 39, no. 9, pp. 1385–1388, Sep. 2018, doi: 10.1109/LED.2018. 2859049.

- [30] J. K. Mun, K. Cho, W. Chang, H.-W. Jung, and J. Do, "Editors' choice— 2.32 kV breakdown voltage lateral β – Ga<sub>2</sub>O<sub>3</sub> MOSFETs with sourceconnected field plate," ECS J. Solid State Sci. Technol., vol. 8, no. 7, pp. Q3079–Q3082, Feb. 2019, doi: 10.1149/2.0151907jss.

- [31] K. Zeng, A. Vaidya, and U. Singisetti, "A field-plated Ga<sub>2</sub>O<sub>3</sub> MOSFET with near 2-kV breakdown voltage and 520 m $\Omega$  cm<sup>2</sup> on-resistance," *Appl. Phys. Exp.*, vol. 12, no. 8, Jul. 2019, Art. no. 081003, doi: 10. 7567/1882-0786/ab2e86.

- [32] S. Sharma, K. Zeng, S. Saha, and U. Singisetti, "Field-plated lateral Ga<sub>2</sub>O<sub>3</sub> MOSFETs with polymer passivation and 8.03 kV breakdown voltage," *IEEE Electron Device Lett.*, vol. 41, no. 6, pp. 836–839, Jun. 2020, doi: 10.1109/LED.2020.2991146.