# Bottom-up Nanoscale Patterning and Selective Deposition on Silicon Nanowires

Amar T. Mohabir,<sup>\*</sup> Daniel Aziz,<sup>\*</sup> Amy C. Brummer,<sup>†</sup> Kathleen E. Taylor,<sup>\*</sup> Eric M. Vogel<sup>†</sup>, Michael A. Filler<sup>\*,†</sup>

Georgia Institute of Technology

School of Chemical & Biomolecular Engineering<sup>\*</sup>

School of Materials Science & Engineering<sup>†</sup>

30332, Georgia, United States

## ABSTRACT

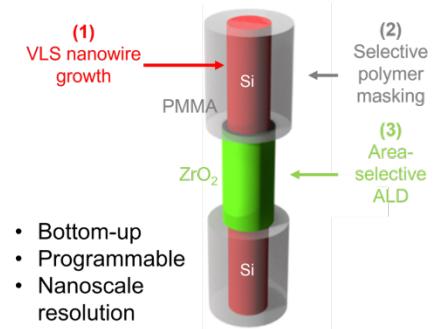

We demonstrate a bottom-up process for programming the deposition of coaxial thin films aligned to the underlying dopant profile of semiconductor nanowires. Our process synergistically combines three distinct methods – vapor-liquid-solid (VLS) nanowire growth, selective coaxial lithography via etching of surfaces (SCALES), and area-selective atomic layer deposition (AS-ALD) – into a cohesive whole. Here, we study  $ZrO_2$  on Si nanowires as a model system. Si nanowires are first grown with an axially modulated n-Si/i-Si dopant profile. SCALES then yields coaxial poly(methyl methacrylate) (PMMA) masks on the n-Si regions. Subsequent AS-ALD of  $ZrO_2$  occurs on the exposed i-Si regions and not on those masked by PMMA. We show the spatial relationship between nanowire dopant profile, PMMA masks, and  $ZrO_2$  films, confirming the programmability of the process. The nanoscale resolution of our process coupled with the plethora of available AS-ALD chemistries promises a range of future opportunities to generate structurally complex nanoscale materials and electronic devices using entirely bottom-up methods.

## INTRODUCTION

The bottom-up synthesis of complex nanoscale materials and functional devices requires new patterning techniques that are not only compatible with the structure and dimensionality of the object to be patterned, but also offer a suitable marriage of resolution and programmability. Nanoscale patterning methods commonly deployed for 2-dimensional (2-D) surfaces, such as photo or e-beam lithography, are user-definable and offer excellent resolution.<sup>1-4</sup> However, the patterning of 3-dimensional (3-D) nanoscale objects introduces additional challenges. Techniques must be compatible with objects oriented in most any direction and exhibiting local curvature, in addition to offering programmability and nanoscale resolution.

Several examples highlight recent progress toward a robust ability to pattern 3-D nanoscale objects, and to leverage that pattern to direct subsequent deposition. Ozel *et al* demonstrated the fabrication of complex nanostructures in anodized alumina oxide (AAO) membranes using a combination of electrochemical deposition and selective etching.<sup>5</sup> The technique is amenable to any material that can be electrodeposited, including semiconductors (e.g., CdSe), metals (e.g., Au), or oxides (e.g., MnO<sub>2</sub>). The resulting nanostructures are programmable in the axial direction by controlling the sequencing and deposition time of each segment. Phase separation of polymer-coated nanostructures can also be used to impart nanoscale patterns.<sup>6, 7</sup> Wang *et al* show that thermal treatment of polystyrene-block-poly(acrylic acid)-coated Au nanorod dispersions can result in a variety of surface structures that serve as masks for subsequent metal (e.g., Ag, Pd) deposition.<sup>8</sup> The mask structure is tunable through the polymer's structure and interactions with the underlying nanorod. To date, no similarly powerful techniques exist for nanopatterning the single crystalline, high mobility semiconductors that are the basis of high performance nanoelectronic devices.

Here, we demonstrate a bottom-up process for programming the deposition of nanoscale thin films on semiconductor nanowires. As illustrated in Figure 1, our approach combines bottom-up vapor-liquid-solid (VLS) nanowire growth,<sup>9-14</sup> selective coaxial lithography via etching of surfaces (SCALES),<sup>15</sup> and area-selective atomic layer deposition (AS-ALD). The resulting structure is that of a Si “proto-transistor,” containing a source, channel, and drain as well as a model ZrO<sub>2</sub> gate dielectric aligned to the channel. Detailed experimental methods are available in the Supporting Information. We begin with the VLS synthesis of Si nanowires that alternate between nominally intrinsic (i-Si) and phosphorous-doped (n-Si) segments. Segment, and ultimately coaxial mask and thin film, dimensions are programmable via Si nanowire growth time and conditions. We next use SCALES<sup>15</sup> to create coaxial poly(methyl methacrylate) (PMMA) masks on the n-Si regions. A blanket poly(methyl methacrylate) (PMMA) brush is initially grown from the entire Si nanowire surface using atom transfer radical polymerization (ATRP)<sup>16-18</sup> (Supporting Information, Figure S1). We then selectively remove the polymer from i-Si regions but not n-Si regions using aqueous potassium hydroxide (KOH).<sup>10, 19-22</sup> In this step, KOH diffuses through the PMMA mask and selectively etches the underlying i-Si segments, which releases the tethered PMMA chains into solution. Notably, relative to our initial work on Si/Ge nanowires,<sup>15</sup> the n-Si/i-Si nanowires require distinct strategies for attaching the polymerization initiator and selectively etching the nanowire. We then use the SCALES mask to direct the AS-ALD of ZrO<sub>2</sub> onto i-Si segments.

**Figure 1. Overall process flow.** (a) VLS growth of Si nanowires with axially programmed phosphorus dopant profiles, (b) surface-initiated polymerization of PMMA from both i-Si and n-Si segments, (c) selective etching to remove PMMA from the i-Si segments, (d) AS-ALD of  $ZrO_2$  on exposed i-Si segments. (e) Selective etching mechanism (transition from step b to c)

Our approach enables the axial programming of patterns with nanoscale resolution on semiconductor nanowires. The single-crystallinity of VLS-grown semiconductor nanowires,<sup>23, 24</sup> in addition to the alignment of the coaxial masks and thin films to the nanowire dopant profile, promises to be useful for the fully bottom-up construction of nanoelectronic devices, such as field effect transistors. The availability of myriad VLS-grown nanowires<sup>25-27</sup> and AS-ALD chemistries<sup>28-30</sup> also offers versatility and extensibility. Moreover, the bottom-up nature of all process steps – VLS nanowire growth, SCALES, and selective deposition – also ensures compatibility with the 3-D nature of the nanowires themselves as well as any scalable nanowire manufacturing technique with which they may be produced (e.g., Geode Process,<sup>31</sup> Aerotaxy<sup>32</sup>).

## RESULTS AND DISCUSSION

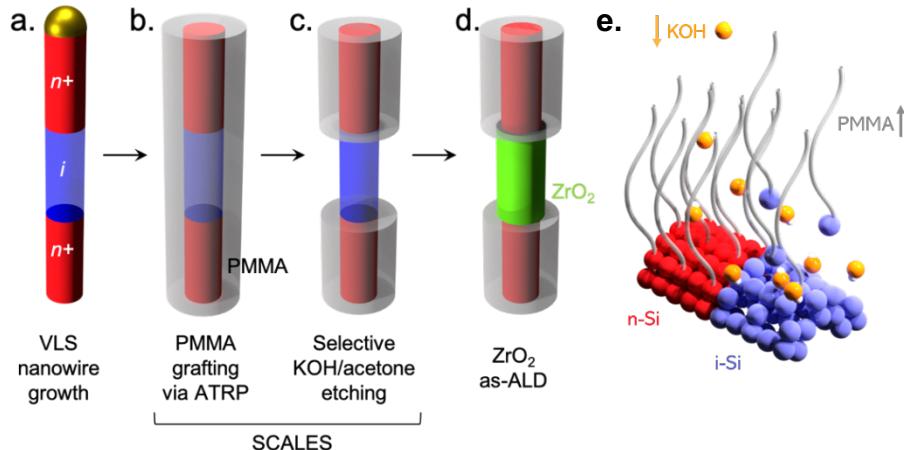

The entire sequence of VLS growth, SCALES patterning, and AS-ALD is shown in Figure 2. Si nanowires are grown with n-Si segments of a fixed length (~200 nm) and i-Si segments of different lengths (~200 and ~500 nm). Figure 2(a) shows a representative as-grown Si nanowire following a short KOH etch, confirming these segment lengths. Figure 2(b) shows a blanket PMMA film (false-colored in yellow) on an as-grown Si nanowire after ATRP. The PMMA thickness depends on the type of segment to which it is attached: i-Si and n-Si regions exhibit a thickness of ~20 and ~30 nm, respectively. Since the subsequent selective etching process relies on the diffusion of the etchant through the PMMA, the polymer film thickness was intentionally kept low. X-ray photoelectron spectroscopy (XPS) spectra of such a film on a Si wafer are consistent with PMMA (Supporting Information, Figure S2).

**Figure 2. Demonstration of complete VLS growth, SCALES, and AS-ALD sequence.** (a) VLS-grown Si nanowire following a brief KOH etch to reveal the phosphorus dopant profile. (b) As-grown Si nanowire with a blanket coating of PMMA following ATRP. PMMA is false colored in yellow for clarity. (c) SCALES-patterned Si nanowire following cyclic etching with KOH/acetone to remove PMMA from the i-Si segments. (d) SCALES-patterned Si nanowire after a final KOH rinse to remove residual PMMA on the i-Si segments. (e) Si nanowire after AS-ALD of  $ZrO_2$  onto the exposed i-Si segments. The magnification of all images is the same.

Next, we apply a cyclic etch procedure, switching between aqueous KOH solution and acetone, to selectively remove PMMA from the i-Si segments. Figure 2(c) shows the resulting PMMA mask after 3 KOH/acetone cycles. We find that continuous KOH etching does not selectively remove the PMMA, even with a final acetone rinse. We suspect this behavior results because water is a poor solvent for PMMA<sup>33</sup> and the addition of acetone helps solvate both tethered and released PMMA chains, thereby facilitating etching. Notably, the n-Si segments also show some PMMA loss, albeit less than that on the i-Si segments. A final KOH rinse (without acetone) removes remaining PMMA on the i-Si segments, as displayed in Figure 2(d), without additional removal of PMMA on the n-Si segments.

The SCALES-patterned nanowires are then used as substrates for AS-ALD. AS-ALD is extensively used to direct thin film deposition on 2-D substrates, where selectively attached or top-down patterned self-assembled monolayers or polymers are the deposition-directing agents.<sup>34-37</sup> Figure 2(e) shows  $ZrO_2$  thin films solely on the i-Si segments (also see Supporting Information, Figure S3). The  $ZrO_2$  appears bright due to its large atomic number (40) relative to Si (14) or C (6). Despite modest removal of PMMA from the n-Si segments, the remaining film is still able to

resist  $\text{ZrO}_2$  ALD. This result is consistent with previous studies, which show that the steric hinderance of the tetrakis groups of the Zr precursor minimizes interactions with PMMA.<sup>38</sup>

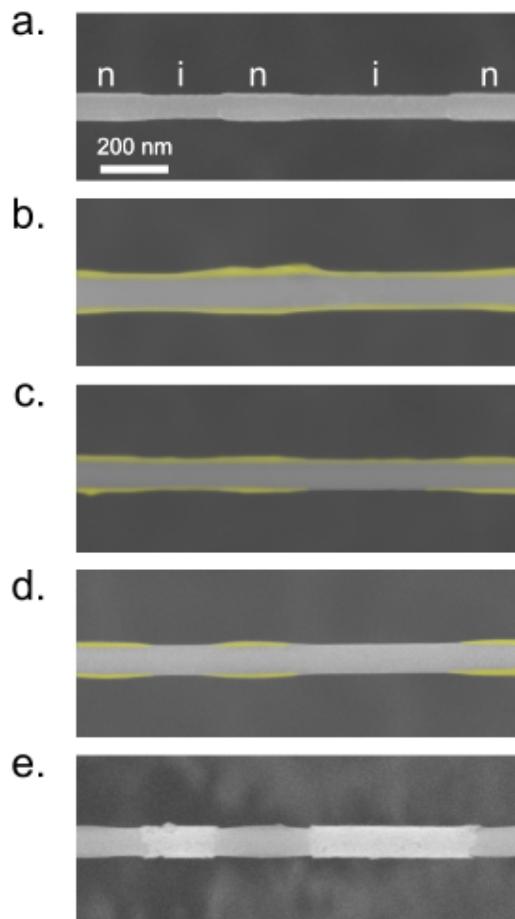

We now investigate the resulting coaxial thin films in more detail, confirming the programmability of our process and presence of  $\text{ZrO}_2$ . Figure 3(a) shows SEM images of Si nanowires with constant and different length i-Si segments following KOH etching without PMMA to reveal the i-Si and n-Si segments. The presence of a bright film following AS-ALD  $\text{ZrO}_2$  only on the i-Si segments in Figure 3(b), as expected from the underlying dopant encoding shows the intended programmability.  $\text{Zr}(\text{L}\alpha)$  and  $\text{O}(\text{K}\alpha)$  energy dispersive X-ray (EDX) spectroscopy maps in Figure 3(c) and 3(d), respectively, confirm the presence of both Zr and O, which is consistent with the presence of  $\text{ZrO}_2$ . While Zr is only observable above the noise on the i-Si segments, O is observed on both the i-Si and n-Si segments. We attribute this observation to the presence of some native oxide on the n-Si surface. Despite demonstrating the programmability of our process, there is clearly room to improve the morphology, continuity, and edge abruptness of the coaxial thin films. We expect that this will be possible with a combination of increasingly abrupt dopant profiles in the Si nanowires, more complete PMMA removal upon KOH etching, and pre-ALD surface cleaning. These improvements will also facilitate the clean semiconductor-thin film interfaces needed for high performance nanoelectronic devices<sup>39, 40</sup>.

**Figure 3. Demonstration of pattern programming and EDX analysis of AS-ALD thin film.** (a) SEM images of as-grown Si nanowires following KOH etch to confirm dopant profile. (b) SEM images of Si nanowires following SCALES patterning and 180 cycles of  $ZrO_2$  ALD. (c) EDX map of  $Zr(L\alpha)$  showing the presence of Zr, as expected for  $ZrO_2$ , on the i-Si segments. Zr cannot be observed above the noise on the n-Si segments. (d) EDX map of  $O(K\alpha)$  showing a higher concentration of O on the i-Si, as expected for  $ZrO_2$ . The presence of some O on n-Si segments is attributed to native oxide. The magnification of all images is the same.

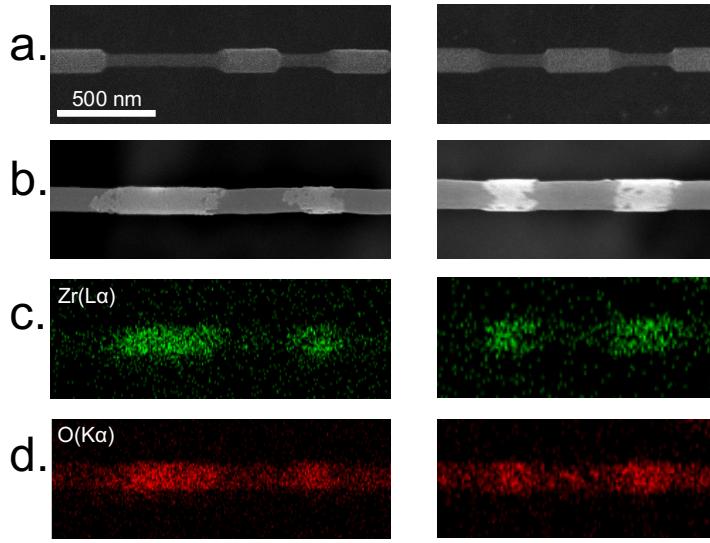

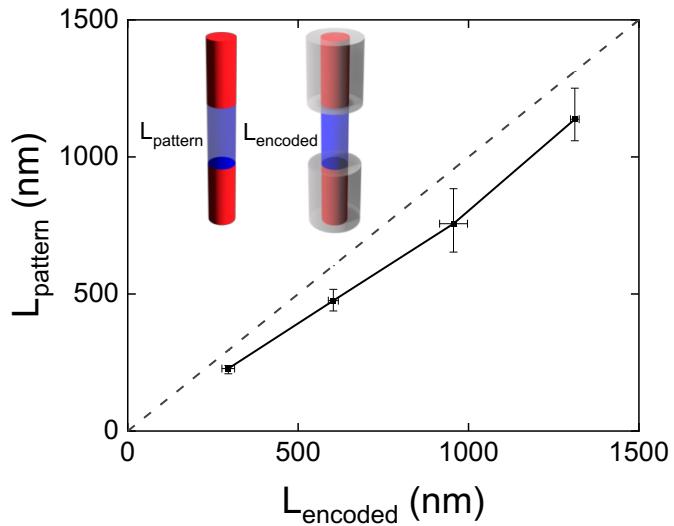

The ultimate resolution of our patterning and deposition approach will depend on multiple factors, including abruptness of nanowire dopant profile, etch selectivity, and PMMA thickness. We begin to understand these factors, as shown in Figure 4, by comparing the length of as-grown i-Si segments after KOH etching,  $L_{encoded}$ , relative to the length of the regions exposed following PMMA removal,  $L_{pattern}$ . An ideal process would result in an  $L_{encoded} = L_{pattern}$  line, as indicated by the dotted line. However, we find that PMMA removal is always less than the as-grown i-Si

segment length determined via selective KOH etching. We hypothesize that the finite thickness of the polymer means that chains near the i-Si/n-Si interface can collapse onto the i-Si regions and block AS-ALD.<sup>41, 42</sup>

**Figure 4.** Comparison of as-grown i-Si segment length ( $L_{\text{encoded}}$ ) and length of segment exposed following PMMA removal ( $L_{\text{pattern}}$ ).

## CONCLUSION

In summary, we demonstrate a process to apply coaxial thin films to Si nanowires using a combination of VLS growth, SCALES patterning, and AS-ALD. Our approach offers nanoscale resolution and is programmable via doping during VLS growth. It is versatile and extensible due to the variety of available VLS growth, selective etch, and AS-ALD chemistries. While feature sizes of ~200 nm are demonstrated, we expect that feature sizes of tens of nanometers are likely with careful control of nanowire growth, polymer chemistry, and polymer thickness. We use KOH to selectively remove PMMA from i-Si segments but note that an inverse process using HF to selectively remove PMMA from n-Si segments may also be possible. On-going work in our

laboratory is focused on understanding the intimate interplay between nanowire growth, nanowire surface structure and chemistry, polymer chemistry and thickness, selective etching, and AS-ALD. Finally, this work is an important step toward the entirely bottom-up fabrication of nanoelectronic devices.

## **ACKNOWLEDGEMENTS**

The authors would like to thank the National Science Foundation (CMMI-1916953) and the Defense Advanced Research Projects Agency (W911NF2110298) for their financial support. A.C.B. is also supported by the Department of Defense (DOD) through a National Defense Science & Engineering Graduate (NDSEG) Fellowship. This work was performed in part at the Georgia Tech Institute for Electronics and Nanotechnology, a member of the National Nanotechnology Coordinated Infrastructure (NNCI), which is supported by the National Science Foundation (ECCS-2025462). We thank the staff of the IEN for supporting the operation of our CVD system.

## **CONFLICT OF INTEREST**

The authors declare no conflict of interest.

## **ORCID IDs**

|                    |                                                                                           |

|--------------------|-------------------------------------------------------------------------------------------|

| Amar T. Mohabir    | <a href="https://orcid.org/0000-0001-5445-0734">https://orcid.org/0000-0001-5445-0734</a> |

| Daniel Aziz        | <a href="https://orcid.org/0000-0003-2185-1587">https://orcid.org/0000-0003-2185-1587</a> |

| Amy C. Brummer     | <a href="https://orcid.org/0000-0001-6734-2265">https://orcid.org/0000-0001-6734-2265</a> |

| Kathleen E. Taylor | <a href="https://orcid.org/0000-0002-9731-0704">https://orcid.org/0000-0002-9731-0704</a> |

| Eric M. Vogel      | <a href="https://orcid.org/0000-0002-6110-1361">https://orcid.org/0000-0002-6110-1361</a> |

| Michael A. Filler  | <a href="https://orcid.org/0000-0003-4239-8558">https://orcid.org/0000-0003-4239-8558</a> |

## **SUPPORTING INFORMATION DESCRIPTION**

Supporting information is available online at the Nanotechnology publications website. The following additional figures and details are available as referenced in the main text: experimental methods, figures S1-S3.

## REFERENCES

1. Mack, C. A., Fifty Years of Moore's Law. *IEEE Trans. Semicond. Manuf.* **2011**, *24* (2), 202-207.

2. Pease, R. F.; Chou, S. Y., Lithography and other patterning techniques for future electronics. *Proc. IEEE* **2008**, *96* (2), 248-270.

3. Murr, L. E., Photolithography Applied to Integrated Circuit (IC) Microfabrication. In *Handbook of Materials Structures, Properties, Processing and Performance*, Springer International Publishing: Cham, 2016; pp 1-7.

4. Craven, D., *Photolithography challenges for the micromachining industry*. SPIE: 1996; Vol. 2884.

5. Borissov, D.; Isik-Uppenkamp, S.; Rohwerder, M., Fabrication of Iron Nanowire Arrays by Electrodeposition into Porous Alumina. *The Journal of Physical Chemistry C* **2009**, *113* (8), 3133-3138.

6. Tao, H.; Chen, L.; Galati, E.; Manion, J. G.; Seferos, D. S.; Zhulina, E. B.; Kumacheva, E., Helicoidal Patterning of Gold Nanorods by Phase Separation in Mixed Polymer Brushes. *Langmuir* **2019**, *35* (48), 15872-15879.

7. Choueiri, R. M.; Galati, E.; Therien-Aubin, H.; Klinkova, A.; Larin, E. M.; Querejeta-Fernandez, A.; Han, L. L.; Xin, H. L.; Gang, O.; Zhulina, E. B.; Rubinstein, M.; Kumacheva, E., Surface patterning of nanoparticles with polymer patches. *Nature* **2016**, *538* (7623), 79-83.

8. Wang, Z.; He, B.; Xu, G.; Wang, G.; Wang, J.; Feng, Y.; Su, D.; Chen, B.; Li, H.; Wu, Z.; Zhang, H.; Shao, L.; Chen, H., Transformable masks for colloidal nanosynthesis. *Nature Communications* **2018**, *9* (1) 563.

9. Christesen, J. D.; Pinion, C. W.; Grumstrup, E. M.; Papanikolas, J. M.; Cahoon, J. F., Synthetically Encoding 10 nm Morphology in Silicon Nanowires. *Nano Letters* **2013**, *13* (12), 6281-6286.

10. Christesen, J. D.; Pinion, C. W.; Zhang, X.; McBride, J. R.; Cahoon, J. F., Encoding Abrupt and Uniform Dopant Profiles in Vapor–Liquid–Solid Nanowires by Suppressing the Reservoir Effect of the Liquid Catalyst. *ACS Nano* **2014**, *8* (11), 11790-11798.

11. Hill, D. J.; Teitsworth, T. S.; Kim, S.; Christesen, J. D.; Cahoon, J. F., Encoding Highly Nonequilibrium Boron Concentrations and Abrupt Morphology in p-Type/n-Type Silicon Nanowire Superlattices. *ACS Applied Materials & Interfaces* **2017**, *9* (42), 37105-37111.

12. Kodambaka, S.; Tersoff, J.; Reuter, M. C.; Ross, F. M., Germanium nanowire growth below the eutectic temperature. *Science* **2007**, *316* (5825), 729-732.

13. Radovanovic, P. V.; Barrelet, C. J.; Gradečak, S.; Qian, F.; Lieber, C. M., General Synthesis of Manganese-Doped II–VI and III–V Semiconductor Nanowires. *Nano Letters* **2005**, *5* (7), 1407-1411.

14. Xie, T.; Schmidt, V.; Pippel, E.; Senz, S.; Gösele, U., Gold-Enhanced Low-Temperature Oxidation of Silicon Nanowires. *Small* **2008**, *4* (1), 64-68.

15. Mohabir, A. T.; Tutuncuoglu, G.; Weiss, T.; Vogel, E. M.; Filler, M. A., Bottom-Up Masking of Si/Ge Surfaces and Nanowire Heterostructures via Surface-Initiated Polymerization and Selective Etching. *ACS Nano* **2020**, *14* (1), 282-288.

16. Matyjaszewski, K., Atom Transfer Radical Polymerization (ATRP): Current Status and Future Perspectives. *Macromolecules* **2012**, *45* (10), 4015-4039.

17. Matyjaszewski, K.; Patten, T. E.; Xia, J. H., Controlled/"living" radical polymerization. Kinetics of the homogeneous atom transfer radical polymerization of styrene. *J. Am. Chem. Soc.* **1997**, *119* (4), 674-680.

18. Zhang, H.; Jiang, Y.; Yu, Q., Grafting Polymer Brushes from Glass Fibers by Surface-Initiated ATRP. *Macromolecular Reaction Engineering* **2010**, *4* (3-4), 251-256.

19. Palik, E. D.; Bermudez, V. M.; Glembocki, O. J., Ellipsometric Study of Orientation-Dependent Etching of Silicon in Aqueous KOH. *Journal of The Electrochemical Society* **1985**, *132* (4), 871-884.

20. Palik, E. D.; Faust, J. W.; Gray, H. F.; Greene, R. F., Study of the Etch-Stop Mechanism in Silicon. *Journal of The Electrochemical Society* **1982**, *129* (9), 2051-2059.

21. Palik, E. D.; Glembocki, O. J.; Jr., I. H.; Burno, P. S.; Tenerz, L., Etching roughness for (100) silicon surfaces in aqueous KOH. *Journal of Applied Physics* **1991**, *70* (6), 3291-3300.

22. Palik, E. D.; Gray, H. F.; Klein, P. B., A Raman Study of Etching Silicon in Aqueous KOH. *Journal of The Electrochemical Society* **1983**, *130* (4), 956-959.

23. Zhang, B.-C.; Wang, H.; He, L.; Zheng, C.-J.; Jie, J.-S.; Lifshitz, Y.; Lee, S.-T.; Zhang, X.-H., Centimeter-Long Single-Crystalline Si Nanowires. *Nano Letters* **2017**, *17* (12), 7323-7329.

24. Cui, Y.; Lauhon, L. J.; Gudiksen, M. S.; Wang, J.; Lieber, C. M., Diameter-controlled synthesis of single-crystal silicon nanowires. *Applied Physics Letters* **2001**, *78* (15), 2214-2216.

25. Chen, C.-C.; Yeh, C.-C.; Chen, C.-H.; Yu, M.-Y.; Liu, H.-L.; Wu, J.-J.; Chen, K.-H.; Chen, L.-C.; Peng, J.-Y.; Chen, Y.-F., Catalytic Growth and Characterization of Gallium Nitride Nanowires. *J. Am. Chem. Soc.* **2001**, *123* (12), 2791-2798.

26. Wu, Y.; Yan, H.; Huang, M.; Messer, B.; Song, J. H.; Yang, P., Inorganic Semiconductor Nanowires: Rational Growth, Assembly, and Novel Properties. *Chemistry - A European Journal* **2002**, *8* (6), 1260-1268.

27. Yang, P. D.; Yan, H. Q.; Mao, S.; Russo, R.; Johnson, J.; Saykally, R.; Morris, N.; Pham, J.; He, R. R.; Choi, H. J., Controlled growth of ZnO nanowires and their optical properties. *Adv. Funct. Mater.* **2002**, *12* (5), 323-331.

28. Miikkulainen, V.; Leskela, M.; Ritala, M.; Puurunen, R. L., Crystallinity of inorganic films grown by atomic layer deposition: Overview and general trends. *Journal of Applied Physics* **2013**, *113* (2) 021301.

29. George, S. M., Atomic Layer Deposition: An Overview. *Chemical Reviews* **2010**, *110* (1), 111-131.

30. Johnson, R. W.; Hultqvist, A.; Bent, S. F., A brief review of atomic layer deposition: from fundamentals to applications. *Mater. Today* **2014**, *17* (5), 236-246.

31. Mujica, M.; Tutuncuoglu, G.; Shetty, P. P.; Mohabir, A. T.; Woods, E. V.; Breedveld, V.; Behrens, S. H.; Filler, M. A., The Geode Process: Hollow Silica Microcapsules as a High Surface Area Substrate for Semiconductor Nanowire Growth. *ACS Applied Nano Materials* **2020**, *3* (1), 905-913.

32. Sivakumar, S.; Persson, A. R.; Metaferia, W.; Heurlin, M.; Wallenberg, R.; Samuelson, L.; Deppert, K.; Johansson, J.; Magnusson, M. H., Aerotaxy: gas-phase epitaxy of quasi 1D nanostructures. *Nanotechnology* **2021**, *32* (2).

33. Moh, L. C. H.; Losego, M. D.; Braun, P. V., Solvent Quality Effects on Scaling Behavior of Poly(methyl methacrylate) Brushes in the Moderate- and High-Density Regimes. *Langmuir* **2011**, *27* (7), 3698-3702.

34. Mackus, A. J. M.; Merkx, M. J. M.; Kessels, W. M. M., From the Bottom-Up: Toward Area-Selective Atomic Layer Deposition with High Selectivity. *Chemistry of Materials* **2019**, *31* (1), 2-12.

35. Merkx, M. J. M.; Vlaanderen, S.; Faraz, T.; Verheijen, M. A.; Kessels, W. M. M.; Mackus, A. J. M., Area-Selective Atomic Layer Deposition of TiN Using Aromatic Inhibitor Molecules for Metal/Dielectric Selectivity. *Chemistry of Materials* **2020**, *32* (18), 7788-7795.

36. Parsons, G. N.; Clark, R. D., Area-Selective Deposition: Fundamentals, Applications, and Future Outlook. *Chemistry of Materials* **2020**, *32* (12), 4920-4953.

37. Puurunen, R. L.; Vandervorst, W.; Besling, W. F. A.; Richard, O.; Bender, H.; Conard, T.; Zhao, C.; Delabie, A.; Caymax, M.; De Gendt, S.; Heyns, M.; Viitanen, M. M.; de Ridder, M.; Brongersma, H. H.; Tamminga, Y.; Dao, T.; de Win, T.; Verheijen, M.; Kaiser, M.; Tuominen, M., Island growth in the atomic layer deposition of zirconium oxide and aluminum oxide on hydrogen-terminated silicon: Growth mode modeling and transmission electron microscopy. *Journal of Applied Physics* **2004**, *96* (9), 4878-4889.

38. Haider, A.; Yilmaz, M.; Deminskyi, P.; Eren, H.; Biyikli, N., Nanoscale selective area atomic layer deposition of TiO<sub>2</sub> using e-beam patterned polymers. *RSC Advances* **2016**, *6* (108), 106109-106119.

39. Zhang, W.; Wang, D.; Zheng, W. T., A semiconductor-electrochemistry model for design of high-rate Li ion battery. *J Energy Chem* **2020**, *41*, 100-106.

40. Louie, S. G.; Cohen, M. L., Electronic-Structure of a Metal-Semiconductor Interface. *Phys Rev B* **1976**, *13* (6), 2461-2469.

41. Chen, J.-K.; Hsieh, C.-Y.; Huang, C.-F.; Li, P.-m., Characterization of patterned poly(methyl methacrylate) brushes under various structures upon solvent immersion. *Journal of Colloid and Interface Science* **2009**, *338* (2), 428-434.

42. Chen, W.-L.; Menzel, M.; Prucker, O.; Wang, E.; Ober, C. K.; Rühe, J., Morphology of Nanostructured Polymer Brushes Dependent on Production and Treatment. *Macromolecules* **2017**, *50* (12), 4715-4724.

## SYNOPSIS TOC