# Schottky diode characteristics on high-growth rate LPCVD $\beta$ -Ga<sub>2</sub>O<sub>3</sub> films on (010) and (001) Ga<sub>2</sub>O<sub>3</sub> substrates

Sudipto Saha<sup>1,a)</sup>, Lingyu Meng<sup>2</sup>, Zixuan Feng<sup>2</sup>, A F M Anhar Uddin Bhuiyan<sup>2</sup>, Hongping Zhao<sup>2,3</sup>, and Uttam Singisetti<sup>1, b)</sup>

<sup>1</sup>*Electrical Engineering Department, University at Buffalo, Buffalo, NY, 14260, USA.*

<sup>2</sup> *Department of Electrical and Computer Engineering, The Ohio State University, Columbus, Ohio, USA 43016.*

<sup>3</sup> *Department of Materials Science and Engineering, The Ohio State University, Columbus, Ohio, USA 43016.*

High crystalline quality thick  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> drift layers are essential for multi-kV vertical power devices. Low-pressure chemical vapor deposition (LPCVD) is a suitable technique to achieve high growth rates. This paper presents a systematic study of the Schottky barrier diodes fabricated on four different Si-doped homoepitaxial  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> thin films grown on Sn-doped (010) and (001)  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> substrates by LPCVD with fast growth rate varying from 13  $\mu\text{m/h}$  to 21  $\mu\text{m/h}$ . A higher temperature growth results in the highest reported growth rates to date. Room temperature current density-voltage data for different Schottky diodes is presented and diode characteristics such as ideality factor, barrier height, specific on-resistance, and breakdown voltage are studied. Temperature dependence (25  $^{\circ}\text{C}$ -250  $^{\circ}\text{C}$ ) of the ideality factor, barrier height, and specific on-resistance is also analyzed from the  $J$ - $V$ - $T$  characteristics of the fabricated Schottky diodes. The reported work shows the promise of the LPCVD growth technique with a high growth rate to grow  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> on native substrates for vertical power devices with thick active layers.

---

<sup>a)</sup> Email: [sudiptos@buffalo.edu](mailto:sudiptos@buffalo.edu), Tel: 701-793-7192

<sup>b)</sup> Email: [uttamsin@buffalo.edu](mailto:uttamsin@buffalo.edu), Tel: 716-645-1536

Recently, there has been a growing interest in developing power electronics technology based on ultra-wide bandgap (UWBG) semiconductors because of the potential for significantly higher switching efficiency and higher power conversion densities <sup>1-5</sup>. These technologies could potentially surpass the performance of the current commercialized WBG technologies of Silicon Carbide (SiC) and Gallium Nitride (GaN). UWBGs with their high Baliga's figure of merit (BFOM=  $\epsilon \cdot \mu \cdot E_c^3$ , where  $\epsilon$ ,  $\mu$ , and  $E_c$  are the dielectric constant, carrier mobility, and critical breakdown field strength, respectively) can provide more efficient performance such as high breakdown voltage, small size, low on-state resistance, and low switching losses <sup>6-11</sup>. Monoclinic beta-phase gallium oxide ( $\beta$ -Ga<sub>2</sub>O<sub>3</sub>, referred to hereinafter as Ga<sub>2</sub>O<sub>3</sub>) has recently attracted tremendous interest as a high-performing and economically viable UWBG power device technology. It has an ultrawide-bandgap 4.8 eV, predicted breakdown field of  $\sim$  8MV/cm, n-doping control over a larger range, and most importantly, a unique advantage of free-standing native substrates synthesis technology by low-cost methods <sup>12-17</sup>. The large experimentally measured field strengths also make it attractive for multi-kV ( $>10$  kV) devices for medium voltage grid applications. High-quality epitaxy layers with low compensating defects and heterostructures have been demonstrated <sup>18</sup>. Taking advantage of these properties, several groups have demonstrated high voltage breakdown devices and high-frequency RF devices <sup>6,19-24</sup> further confirming its potential for power and RF technology.

Vertical devices are generally preferred over lateral geometries for power electronics applications due to the absence of surface effects. For beyond-10kV devices, this requires high quality low-doped thick (10 -100  $\mu$ m) drift layers with low-compensation doping ruling out slow rate methods such as molecular beam epitaxy (MBE). While other techniques such as low-pressure chemical vapor deposition (LPCVD) <sup>25,26</sup>, metal-organic chemical vapor deposition

(MOCVD)<sup>27,28</sup>, pulsed laser deposition (PLD)<sup>29</sup>, and halide vapor phase epitaxy (HVPE)<sup>30–33</sup> can provide higher growth rates. HVPE films with a growth rate of 5  $\mu\text{m}/\text{h}$  on (001)<sup>30</sup> and LPCVD with a growth rate of  $\sim$ 2  $\mu\text{m}/\text{h}$  on (010) substrates<sup>25</sup> have been reported. LPCVD in particular has demonstrated high-quality  $\text{Ga}_2\text{O}_3$  homo-epitaxy with controllable doping<sup>34</sup>, characterized by the high room-temperature and low-temperature mobility and commensurate low compensating acceptor impurity concentration. Additionally, the lower cost of LPCVD makes it a preferred growth technique for multi-kV vertical  $\text{Ga}_2\text{O}_3$  power devices.

In this work, we investigated the LPCVD growth of Si-doped n-type  $\text{Ga}_2\text{O}_3$  homoepitaxial drift layers on both (010) and (001) Sn-doped  $\text{Ga}_2\text{O}_3$  substrates. The growth rates of  $\geq$  13  $\mu\text{m}/\text{h}$  is achieved using LPCVD on both (010) and (001) substrates, highest reported homoepitaxial growth rate for  $\text{Ga}_2\text{O}_3$ . The surface morphology and crystal quality of the grown films were characterized by atomic force microscopy (AFM), and X-ray diffraction (XRD), revealing promising crystalline quality. We report a detailed study on the electrical behavior, both at room temperature and as a function of elevated temperature, of four LPCVD grown  $\text{Ga}_2\text{O}_3$  Schottky diode samples of different surface smoothness and substrate crystal orientations. The films on (001) grown with a growth rate of 13  $\mu\text{m}/\text{h}$  show the best device performance in terms of ON/OFF ratio, on-resistance, and breakdown showing the potential of this growth method for future  $\text{Ga}_2\text{O}_3$  technology.

Four  $\text{Ga}_2\text{O}_3$  films were grown via high-temperature (1050 °C) low-pressure chemical vapor deposition (HT-LPCVD)<sup>25,26,34–37</sup> on Sn-doped (001) and (010) oriented  $\text{Ga}_2\text{O}_3$  substrates (commercially acquired from Novel Crystal Technology, Inc.), labeled as S1, S2, S3, and S4. The substrates were first cleaned with isopropanol, rinsed with de-ionized water, and dried with nitrogen flow prior to loading to the growth system. High-purity metallic Ga (Alfa Aesar, 99.999

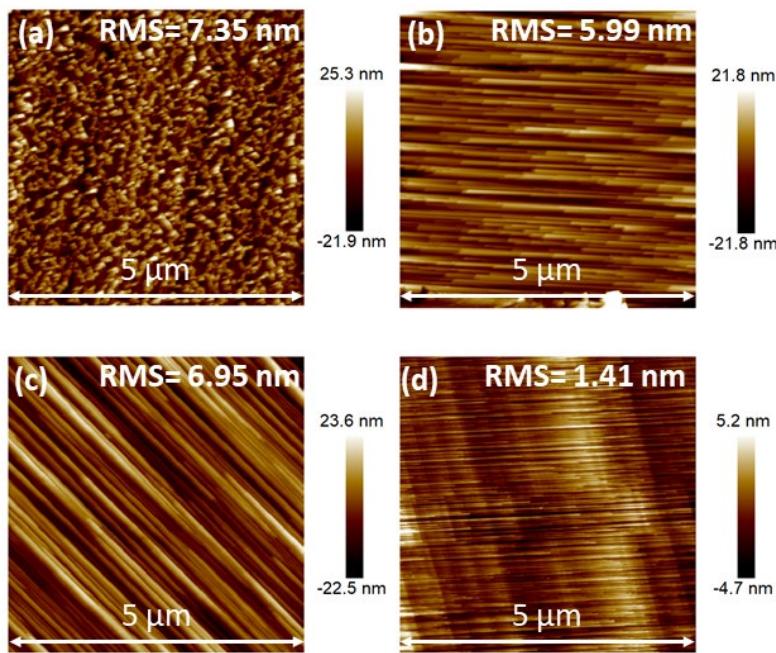

99%) was used as the Ga precursor, which was placed in a quartz crucible the upstream of the substrates. High-purity O<sub>2</sub> gas was used as the O precursor. In this study, a fixed flow rate of O<sub>2</sub> at 30 standard cubic centimeters per minute (sccm) was used. Argon (Ar) was used as a carrier gas with a flow rate of 200 sccm. Diluted silicon tetrachloride (SiCl<sub>4</sub>) was used as an n-type dopant source. The growth temperature was set at 1050 °C, and the growth pressure was fixed at ~2.8 Torr, the growth duration was 50-60 min. Under this growth condition, the growth rates of 13, 15.6, 21, and 19 μm/h were obtained for S1, S2, S3, and S4 respectively. The detailed growth conditions of Ga<sub>2</sub>O<sub>3</sub> films on Sn-doped Ga<sub>2</sub>O<sub>3</sub> substrates are listed in Table I. As specified in the Table, there is macro-scale roughness observed in these films (see Supplementary Materials). The surface morphology of the films in the smooth area was characterized by atomic force microscopy (AFM). Fig. 1 shows the AFM images of the 5 × 5 μm<sup>2</sup> scan for the homoepitaxial thin films surfaces. The RMS values for the S1, S2, S3, and S4 homoepitaxial thin films were 7.35 nm, 6.95 nm, 5.99 nm, and 1.41 nm respectively. The film morphology for S1 is different from other samples. The RMS roughness values for S1, S2, and S3 were higher than previously reported thin films grown by LPCVD (~3-4 nm)<sup>35,38</sup>. This was due to the much faster growth rate of the films grown in this study compared to the ones grown previously. Although in micron-scale (for 5 × 5 μm<sup>2</sup> scan), S1 seems to have the roughest surface out of the four samples surfaces, this sample contains the most area with smooth surface compared to the other three samples (see Supplementary Materials).

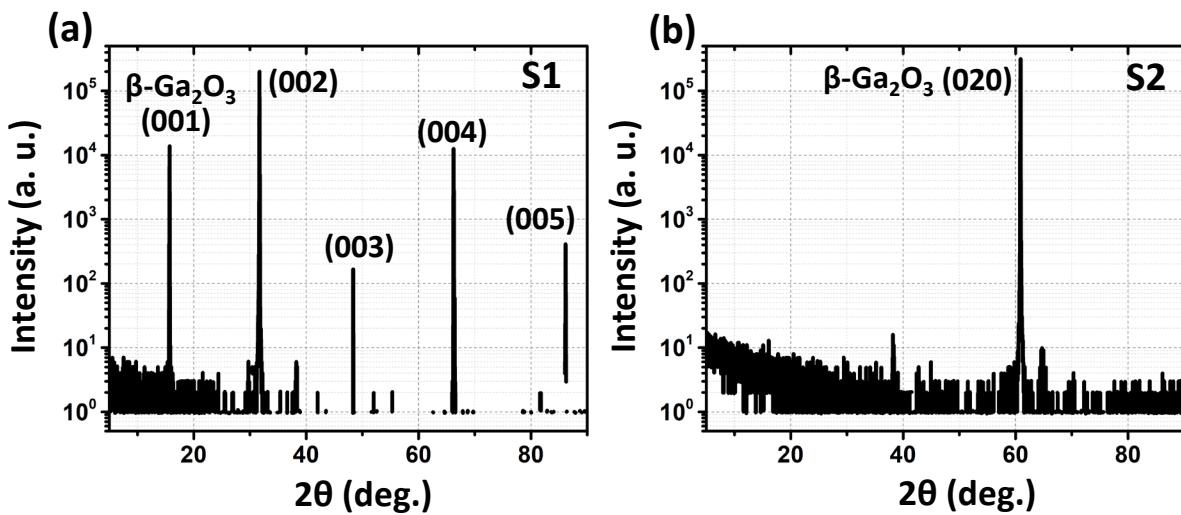

The LPCVD β-Ga<sub>2</sub>O<sub>3</sub> films crystalline quality was characterized by Bruker D8 Discover XRD. Figure 2(a) and 2(b) show the XRD ω-2θ scan of (010) and (001) β-Ga<sub>2</sub>O<sub>3</sub> homoepitaxial films grown on (010) and (001) β-Ga<sub>2</sub>O<sub>3</sub> substrates, respectively. Even at the high growth temperatures where other phases of Ga<sub>2</sub>O<sub>3</sub> are known to be stable<sup>39-41</sup>, no peaks associated with α, γ, δ, and ε

phases of  $\text{Ga}_2\text{O}_3$  were detected, which indicates the high-quality  $\beta$ - $\text{Ga}_2\text{O}_3$  homoepitaxial thin films on (010) and (001)  $\beta$ - $\text{Ga}_2\text{O}_3$  substrates.

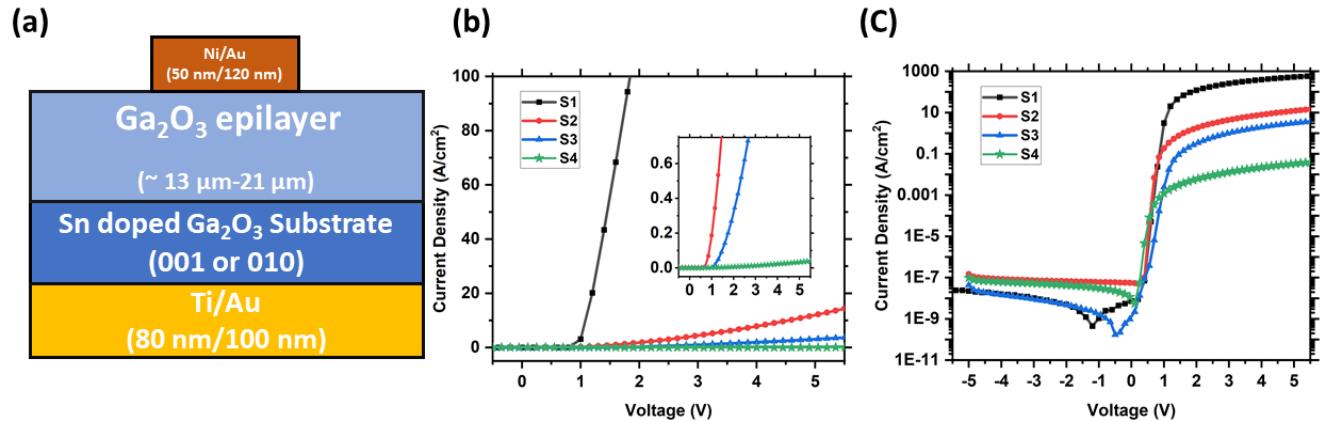

Schottky diodes are used to further verify the electrical characteristics of these films. A schematic cross-section of the Schottky diode structures fabricated is shown in Fig. 3(a). The device fabrication commenced with  $\text{BCl}_3$ -based reactive-ion etching (RIE) of the backside, a total of 1  $\mu\text{m}$  thick  $\text{Ga}_2\text{O}_3$  was etched in this step. A Ti/Au Ohmic metal stack was deposited by electron beam evaporation followed by rapid thermal annealing (RTA) in  $\text{N}_2$  ambient at 470  $^{\circ}\text{C}$  for 1 minute. Finally, the top Ni/Au Schottky contacts were defined by electron beam lithography. After device fabrication, current density-voltage ( $J$ - $V$ ) measurements were performed using HP 4155B semiconductor parameter analyzer. Schottky barrier height ( $\Phi_B$ ), ideality factor ( $\eta$ ), and specific on-resistance ( $R_{\text{on,sp}}$ ) for each sample was calculated using the method of Cheung *et al.*<sup>42</sup>. The measurements were repeated for elevated temperatures up to 250  $^{\circ}\text{C}$ . A room temperature reverse breakdown measurement was also performed.

As seen in Fig. 3(b), all the samples show rectifying behavior. In the semi-log Fig. 3(c), at low bias voltage ( $V < 1 \text{ V}$ ), the current varies linearly. At high bias voltage ( $V > 1 \text{ V}$ ), the linearity is deviated with increasing bias voltage due to the series resistance for all four samples. The measured forward bias  $I$ - $V$  characteristics were analyzed using the ideal thermionic emission (TE) model<sup>43,44</sup>

$$J = J_S \left( e^{\frac{qV}{\eta kT}} - 1 \right), \quad (1)$$

Where  $J_S = A^* T^2 \left( e^{\frac{q\Phi_B^J V}{\eta(T) kT}} \right)$  (2)

Here,  $J_s$  is the saturation current density,  $\eta$  is the ideality factor,  $V$  is the forward bias voltage,  $T$  is the absolute temperature,  $q$  is the electron charge,  $k$  is the Boltzmann constant,  $\Phi_B^{JV}$  is the apparent Schottky barrier height,  $A$  is the effective diode area, and  $A^*$  is the effective Richardson constant, calculated to be  $41.04 \text{ Acm}^{-2}\text{T}^{-2}$ <sup>45</sup>. The electrical properties extracted from the  $J-V$  measurements are shown in Table II. The accuracy of  $\Phi_B$  obtained from Eqn. (2) depends on the corresponding value of the ideality factor. The measured Schottky barrier height from Eqn. (2) is closer to the actual value if the ideality factor is close to 1, as described by Wagner *et al.*<sup>46</sup>. As the ideality factor is  $>1$  in our case, the corrected Schottky barrier height,  $\Phi_B$  is obtained using the following equation<sup>46</sup>

$$\Phi_B = \left[ \Phi_B^{JV} - \left( \frac{\eta-1}{\eta} \frac{kT}{q} \ln \frac{N_C}{N_D} \right) \right] \eta \quad (3)$$

Where  $N_C$  is the conduction density of states for  $\text{Ga}_2\text{O}_3$  calculated using electron effective mass of  $0.34 \text{ m}_0$  with all other constants at their standard values<sup>47,48</sup>.  $N_D$  is the donor concentration of the  $\text{Ga}_2\text{O}_3$ .

As seen in Table II, S1 has excellent rectifying behavior with the highest forward current densities ( $527.5 \text{ A/cm}^2$  at 5 V), lowest specific on-resistance, lowest reverse leakage current ( $2.24 \times 10^8 \text{ A/cm}^2$  at -5 V), and highest ON-OFF ratio ( $>10^{10}$ ). The ideality factor ( $\eta$ ) for S1 is 1.37 which could be attributed to the roughness seen in AFM. While the ideality factor values of S1 and S2 are closer to unity, S3 and S4 have higher ideality factors representing the dominance of non-ideal effects such as spatial inhomogeneity of the Schottky barriers. Inhomogeneous Schottky barriers are believed to result from surface roughness at the metal-semiconductor interfaces. The highest ideality factor was observed for S3 which has the highest growth rate, the larger value of  $\eta$  represents the dominance of non-ideal effects such as thermionic field emission,

and/or trap-assisted tunneling currents, metal adhesion quality, and interface quality. The calculated Schottky barrier heights for S2, S3, and S4 agree with the values reported in the literature<sup>49,50</sup>. For S1, the obtained Schottky barrier height is 0.99 eV, which is at the lower end but within the range of previously reported values<sup>49,51</sup>. However, for the S1 diode, the values of specific on-resistance,  $R_{on,sp}$  was found to be 4.29 mΩ-cm<sup>2</sup>, which is the lowest among the four samples. The maximum value of  $R_{on,sp}$  has been found for S4, as seen in Table II. The macroscale roughness and growth rate seem to correlate with the  $R_{on,sp}$  as with the increase of surface roughness, increased of  $R_{on,sp}$  is observed.

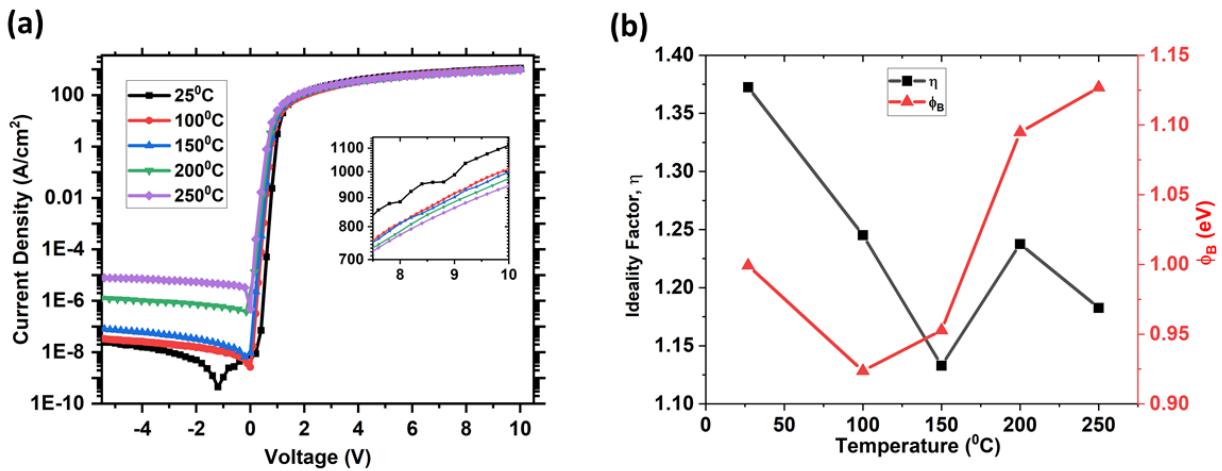

Fig. 4(a) shows the temperature dependence of semi-logarithmic of  $J$ - $V$  characteristics of the S1 sample (see Supplementary Materials for other samples). The forward  $J$ - $V$  curves of all the samples show that in low bias voltage, the turn-on voltage shifts gradually toward the lower bias side with increasing temperature representing an increase of the thermal contribution of electron transport. At higher bias voltages, the linearity has deviated with the increase of bias voltage due to the increase of the series resistance for all four structures. The series resistance component dominates the transport and increases with the increase of temperature. The reverse  $J$ - $V$  characteristics show that with an increase in temperature the leakage current densities increase almost monotonically for all four samples. This is because electrons gain higher energies at elevated temperatures to climb over the metal-semiconductor barrier which attributes leakage. As a result, ON-OFF current ratios reduce by two to four orders of magnitude due to an increase of reverse current densities with temperature.

Fig. 4(b) shows a plot of the temperature dependence of ideality factor,  $\eta$ , and the barrier height,  $\Phi_B$  of S1(see Supplementary Materials for other samples). The ideality factor,  $\eta$  was found to decrease linearly from 1.37 to 1.13 when room temperature increases to 150°C. Beyond this

temperature,  $\eta$  starts increasing with temperature. The reduction in the values of  $\eta$  with an increase of temperature up to a certain temperature is observed when there is marginal improvement in the pure thermionic emission current part over thermionic field emission current transport mechanism in the device. However, the increase of  $\eta$  with temperature beyond that certain temperature has often been accredited to the current transport mechanism not following the ideal thermionic emission theory. Schottky barrier inhomogeneities in the transport current due to different interface qualities can be the cause of this nonideal dependence. Pure thermionic emission barrier height reduces with the elevation of temperature <sup>52</sup>.  $\Phi_B$  decreases from 1 eV to 0.92 eV when temperature increases from room temperature to 100<sup>0</sup>C which indicates they are corresponding to thermionic emission. Interestingly, a gradual increase in  $\Phi_B$  from 0.92 eV to 1.13 eV has been observed when temperature increases from 100<sup>0</sup>C to 250<sup>0</sup>C. The slight increase of  $\Phi_B$  beyond 100<sup>0</sup>C is due to the deviation of the dominant conduction mechanism, from thermionic emission current to thermionic field emission or field mission. An almost similar trend of dependency of  $\eta$  and  $\Phi_B$  on the temperature is observed for the other three samples as well. Such non-monotonic behavior for  $\eta$  and  $\Phi_B$  has also been observed in previous studies <sup>48</sup>.

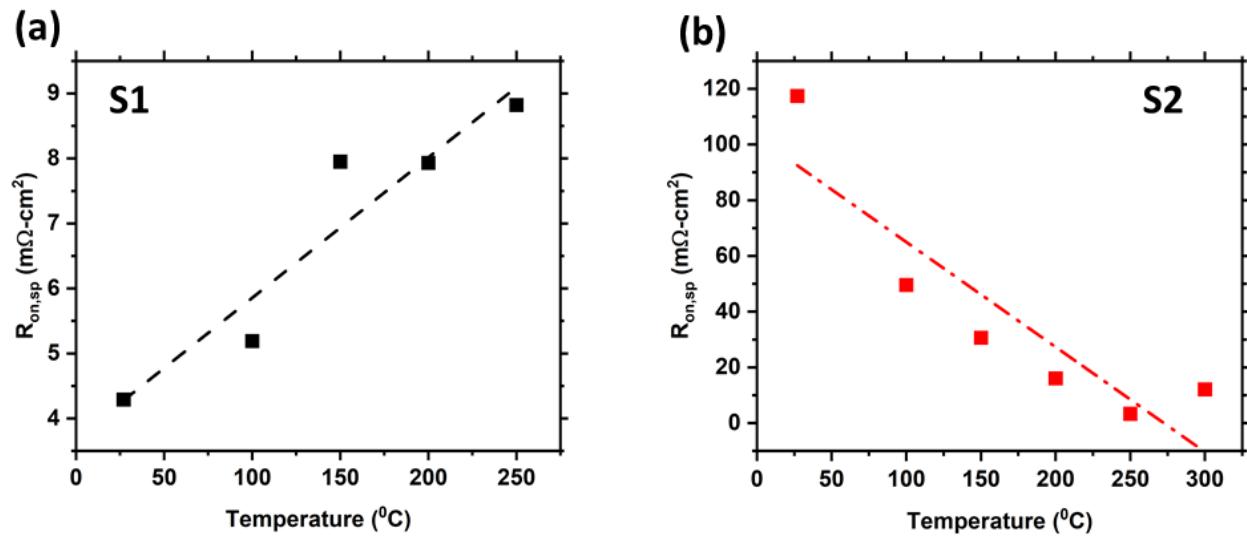

Fig. 5 shows a plot of specific on-resistance,  $R_{on,sp}$  as a function of temperature. As seen in Fig. 5(a),  $R_{on,sp}$  was found to increase linearly from a value of 4.29 mΩ-cm<sup>2</sup> to 8.82 mΩ-cm<sup>2</sup> for S1 when temperature increases from room temperature to 250<sup>0</sup>C. On the contrary,  $R_{on,sp}$  decreases linearly from 117.38 mΩ-cm<sup>2</sup> to 12.08 mΩ-cm<sup>2</sup> for S2 as temperature increases from room temperature to 250<sup>0</sup>C, as seen in Fig. 5(b). S3 and S4 also follow the same trend as S2.  $R_{on,sp}$  is a combined result of contact and bulk resistance values. Bulk resistance increases with increasing temperature due to the decrease in mobility with the elevation of temperature. The contact

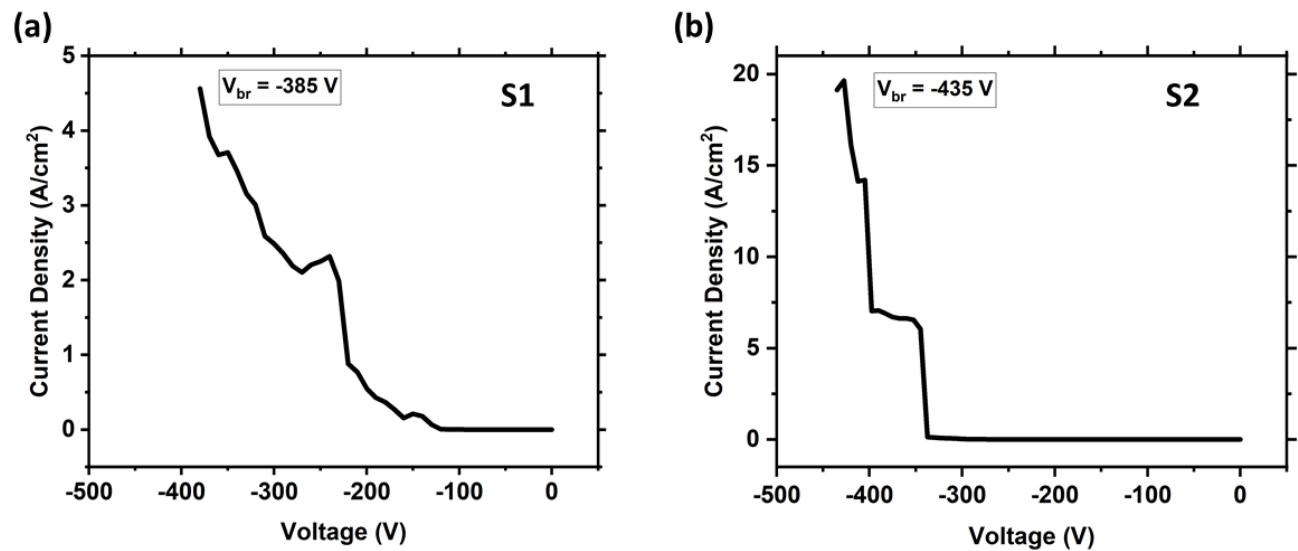

resistance decreases with increasing temperature in  $\text{Ga}_2\text{O}_3$  due to the reduction of the barrier height<sup>53</sup>. In the case of S1, bulk resistance dominates whereas contact resistance dominates over the bulk resistance for S2, S3, and S4. However, any other explanations for the S2, S3, and S4 remain plausible. Future work will investigate such discrepancies for Ni/Au Schottky contacts for LPCVD  $\text{Ga}_2\text{O}_3$  material. The reverse  $J$ - $V$  characteristics of S1 and S2 diodes are shown in Fig. 6. A destructive breakdown is observed for S1 with a breakdown voltage ( $V_{br}$ ) of -385 V and S2 with  $V_{br} = -435$  V. The moderate breakdown voltage is limited by the lower barrier height, high surface roughness of the samples, and edge effects of the anode. Using field-plates, trench MOS diodes, and electric field engineering will improve the breakdown voltage. Improving surface smoothness through chemical mechanical polishing is also expected to significantly improve reverse characteristics. Nevertheless, the modest breakdown voltages show that LPCVD films can be used for high-voltage devices. The samples S1 and S2 with growth rates of 13 and 15.6  $\mu\text{m}/\text{h}$  show reliable device characteristics, while films with growth rates  $>19$   $\mu\text{m}/\text{h}$  show high resistances.

In conclusion, four different Si-doped homoepitaxial  $\text{Ga}_2\text{O}_3$  thin films were grown on Sn-doped (010) and (001)  $\text{Ga}_2\text{O}_3$  substrates via LPCVD with fast growth rates varying from 13  $\mu\text{m}/\text{h}$  to 21  $\mu\text{m}/\text{h}$ . (001) and (010) homoepitaxial  $\text{Ga}_2\text{O}_3$  thin films with RMS surface roughness varying from 1.41 nm to 7.35 nm were obtained. Though the RMS value is highest, Si-doped homoepitaxial  $\text{Ga}_2\text{O}_3$  thin films on (001) Sn-doped  $\text{Ga}_2\text{O}_3$  substrate grown at 13  $\mu\text{m}/\text{h}$  growth rate turns out to be the best among the four samples as it contains less macro-scale roughness, offering the maximum amount of smooth surface for device fabrication. We also demonstrated Schottky diodes using the four LPCVD-grown homoepitaxial  $\text{Ga}_2\text{O}_3$  films. Schottky diodes fabricated on (001) Sn-doped  $\text{Ga}_2\text{O}_3$  substrate followed by Si-doped homoepitaxial  $\text{Ga}_2\text{O}_3$  thin

films exhibits the highest forward current densities ( $527.56 \text{ A/cm}^2$  at 5 V), lowest leakage current ( $2.24 \times 10^8 \text{ A/cm}^2$  at -5 V), highest ON-OFF ratio ( $>10^{10}$ ), lowest specific On-resistance ( $4.29 \text{ m}\Omega\text{cm}^{-2}$ ), and breakdown voltage of -385 V indicating the viability of LPCVD as a growth technique for vertical power electronic devices. The specific On-resistance of this sample also increases with increasing temperature, from  $4.29 \text{ m}\Omega\text{-cm}^2$  at room temperature to  $8.82 \text{ m}\Omega\text{-cm}^2$  at  $250^{\circ}\text{C}$ . For all the samples, ideality factor and barrier height decrease first with temperature elevation and increase with temperature increase beyond a certain temperature. Overall, the growth rate of  $13\text{-}15.6 \mu\text{m/h}$  turns out to be optimum for fabricating vertical devices on LPCVD grown  $\beta$ -  $\text{Ga}_2\text{O}_3$  samples in terms of surface morphology and reliable device characteristics. The reported work shows the promise of the LPCVD growth technique with a high growth rate to grow  $\beta$ -  $\text{Ga}_2\text{O}_3$  on native substrates for fabricating vertical power devices with thick active layers.

## Acknowledgments

The authors acknowledge the Air Force Office of Scientific Research FA9550-18-1-0479 (AFOSR, Dr. Ali Sayir) for financial support. The authors also acknowledge the National Science Foundation (ECCS 2019753, 2019749) and Semiconductor Research Corporation (SRC) under the Task ID GRC 3007.001 for partial support, and II-VI Foundation Block Gift Program. This work used the electron beam lithography system acquired through NSF MRI award ECCS 1919798.

## REFERENCES

<sup>1</sup> M. Higashiwaki, A. Kuramata, H. Murakami, and Y. Kumagai, *J. Phys. D. Appl. Phys.* **50**,

333002 (2017).

<sup>2</sup> J. Yang, C. Fares, R. Elhassani, M. Xian, F. Ren, S.J. Pearton, M. Tadjer, and A. Kuramata, ECS J. Solid State Sci. Technol. **8**, Q3159 (2019).

<sup>3</sup> H. Amano, Y. Baines, E. Beam, M. Borga, T. Bouchet, P.R. Chalker, M. Charles, K.J. Chen, N. Chowdhury, and R. Chu, J. Phys. D. Appl. Phys. **51**, 163001 (2018).

<sup>4</sup> T.J. Flack, B.N. Pushpakaran, and S.B. Bayne, J. Electron. Mater. **45**, 2673 (2016).

<sup>5</sup> J.Y. Tsao, S. Chowdhury, M.A. Hollis, D. Jena, N.M. Johnson, K.A. Jones, R.J. Kaplar, S. Rajan, C.G. Van de Walle, and E. Bellotti, Adv. Electron. Mater. **4**, 1600501 (2018).

<sup>6</sup> K. Konishi, K. Goto, H. Murakami, Y. Kumagai, A. Kuramata, S. Yamakoshi, and M. Higashiwaki, Appl. Phys. Lett. **110**, 103506 (2017).

<sup>7</sup> N. Allen, M. Xiao, X. Yan, K. Sasaki, M.J. Tadjer, J. Ma, R. Zhang, H. Wang, and Y. Zhang, IEEE Electron Device Lett. **40**, 1399 (2019).

<sup>8</sup> S.J. Pearton, F. Ren, M. Tadjer, and J. Kim, J. Appl. Phys. **124**, 220901 (2018).

<sup>9</sup> S.J. Bader, H. Lee, R. Chaudhuri, S. Huang, A. Hickman, A. Molnar, H.G. Xing, D. Jena, H.W. Then, and N. Chowdhury, IEEE Trans. Electron Devices **67**, 4010 (2020).

<sup>10</sup> M. Higashiwaki, K. Sasaki, H. Murakami, Y. Kumagai, A. Koukitu, A. Kuramata, T. Masui, and S. Yamakoshi, Semicond. Sci. Technol. **31**, 34001 (2016).

<sup>11</sup> S. Fujita, Jpn. J. Appl. Phys. **54**, 30101 (2015).

<sup>12</sup> W. Li, Z. Hu, K. Nomoto, Z. Zhang, J.-Y. Hsu, Q.T. Thieu, K. Sasaki, A. Kuramata, D. Jena, and H.G. Xing, Appl. Phys. Lett. **113**, 202101 (2018).

<sup>13</sup> W. Li, K. Nomoto, Z. Hu, D. Jena, and H.G. Xing, IEEE Electron Device Lett. **41**, 107 (2019).

<sup>14</sup> Y. Yao, R.F. Davis, and L.M. Porter, J. Electron. Mater. **46**, 2053 (2017).

<sup>15</sup> M. Higashiwaki, K. Sasaki, T. Kamimura, M.H. Wong, and D. Krishnamurthy, Appl. Phys.

Lett. **103**, 123511 (2013).

<sup>16</sup> M.H. Wong, K. Sasaki, A. Kuramata, S. Yamakoshi, and M. Higashiwaki, (2015).

<sup>17</sup> Z. Zhang, E. Farzana, A.R. Arehart, and S.A. Ringel, Appl. Phys. Lett. **108**, 52105 (2016).

<sup>18</sup> E. Farzana, F. Alema, W.Y. Ho, A. Mauze, T. Itoh, A. Osinsky, and J.S. Speck, Appl. Phys. Lett. **118**, 162109 (2021).

<sup>19</sup> C. Joishi, Y. Zhang, Z. Xia, W. Sun, A.R. Arehart, S. Ringel, S. Lodha, and S. Rajan, IEEE Electron Device Lett. **40**, 1241 (2019).

<sup>20</sup> Y. Lv, X. Zhou, S. Long, X. Song, Y. Wang, S. Liang, Z. He, T. Han, X. Tan, and Z. Feng, IEEE Electron Device Lett. **40**, 83 (2018).

<sup>21</sup> S. Sharma, K. Zeng, A. Vaidya, and U. Singisetti, in *2019 Device Res. Conf.* (IEEE, 2019), pp. 151–152.

<sup>22</sup> K. Zeng, A. Vaidya, and U. Singisetti, IEEE Electron Device Lett. **39**, 1385 (2018).

<sup>23</sup> J.K. Mun, K. Cho, W. Chang, H.-W. Jung, and J. Do, ECS J. Solid State Sci. Technol. **8**, Q3079 (2019).

<sup>24</sup> S. Sharma, K. Zeng, S. Saha, and U. Singisetti, IEEE Electron Device Lett. **41**, 836 (2020).

<sup>25</sup> S. Rafique, L. Han, M.J. Tadjer, J.A. Freitas Jr, N.A. Mahadik, and H. Zhao, Appl. Phys. Lett. **108**, 182105 (2016).

<sup>26</sup> S. Rafique, L. Han, and H. Zhao, Phys. Status Solidi **213**, 1002 (2016).

<sup>27</sup> X. Du, W. Mi, C. Luan, Z. Li, C. Xia, and J. Ma, J. Cryst. Growth **404**, 75 (2014).

<sup>28</sup> N.M. Sbrockey, T. Salagaj, E. Coleman, G.S. Tompa, Y. Moon, and M.S. Kim, J. Electron. Mater. **44**, 1357 (2015).

<sup>29</sup> A. Petitmangin, B. Gallas, C. Hebert, J. Perriere, L. Binet, P. Barboux, and X. Portier, Appl. Surf. Sci. **278**, 153 (2013).

<sup>30</sup> H. Murakami, K. Nomura, K. Goto, K. Sasaki, K. Kawara, Q.T. Thieu, R. Togashi, Y.

Kumagai, M. Higashiwaki, and A. Kuramata, *Appl. Phys. Express* **8**, 15503 (2014).

<sup>31</sup> V.I. Nikolaev, A.I. Pechnikov, S.I. Stepanov, I.P. Nikitina, A.N. Smirnov, A. V Chikiryaka, S.S. Sharofidinov, V.E. Bougrov, and A.E. Romanov, *Mater. Sci. Semicond. Process.* **47**, 16 (2016).

<sup>32</sup> K. Nomura, K. Goto, R. Togashi, H. Murakami, Y. Kumagai, A. Kuramata, S. Yamakoshi, and A. Koukitu, *J. Cryst. Growth* **405**, 19 (2014).

<sup>33</sup> Y. Oshima, E.G. Víllora, and K. Shimamura, *J. Cryst. Growth* **410**, 53 (2015).

<sup>34</sup> S. Rafique, L. Han, A.T. Neal, S. Mou, J. Boeckl, and H. Zhao, *Phys. Status Solidi* **215**, 1700467 (2018).

<sup>35</sup> S. Rafique, M.R. Karim, J.M. Johnson, J. Hwang, and H. Zhao, *Appl. Phys. Lett.* **112**, 52104 (2018).

<sup>36</sup> Y. Zhang, Z. Feng, M.R. Karim, and H. Zhao, *J. Vac. Sci. Technol. A Vacuum, Surfaces, Film.* **38**, 50806 (2020).

<sup>37</sup> S. Rafique, L. Han, A.T. Neal, S. Mou, M.J. Tadjer, R.H. French, and H. Zhao, *Appl. Phys. Lett.* **109**, 132103 (2016).

<sup>38</sup> C. Joishi, S. Rafique, Z. Xia, L. Han, S. Krishnamoorthy, Y. Zhang, S. Lodha, H. Zhao, and S. Rajan, *Appl. Phys. Express* **11**, 31101 (2018).

<sup>39</sup> J. Lee, H. Kim, L. Gautam, and M. Razeghi, *Crystals* **11**, 446 (2021).

<sup>40</sup> A.F.M.A.U. Bhuiyan, Z. Feng, H.-L. Huang, L. Meng, J. Hwang, and H. Zhao, *APL Mater.* **9**, 101109 (2021).

<sup>41</sup> V.D. Wheeler, N. Nepal, D.R. Boris, S.B. Qadri, L.O. Nyakiti, A. Lang, A. Koehler, G. Foster, S.G. Walton, and C.R. Eddy Jr, *Chem. Mater.* **32**, 1140 (2020).

<sup>42</sup> S.K. Cheung and N.W. Cheung, *Appl. Phys. Lett.* **49**, 85 (1986).

<sup>43</sup> Y. Zhou, D. Wang, C. Ahyi, C.-C. Tin, J. Williams, M. Park, N.M. Williams, A. Hanser, and E.A. Preble, *J. Appl. Phys.* **101**, 24506 (2007).

<sup>44</sup> S.M. Sze, Y. Li, and K.K. Ng, *Physics of Semiconductor Devices* (John Wiley & Sons, 2021).

<sup>45</sup> A. Jayawardena, A.C. Ahyi, and S. Dhar, *Semicond. Sci. Technol.* **31**, 115002 (2016).

<sup>46</sup> L.F. Wagner, R.W. Young, and A. Sugerman, *IEEE Electron Device Lett.* **4**, 320 (1983).

<sup>47</sup> I. Lee, A. Kumar, K. Zeng, U. Singisetti, and X. Yao, in *2017 IEEE 5th Work. Wide Bandgap Power Devices Appl.* (IEEE, 2017), pp. 185–189.

<sup>48</sup> A. Vaidya, K. Sasaki, A. Kuramata, T. Masui, and U. Singisetti, *ArXiv Prepr. ArXiv1803.07504* (2018).

<sup>49</sup> Y. Yao, R. Gangireddy, J. Kim, K.K. Das, R.F. Davis, and L.M. Porter, *J. Vac. Sci. Technol. B, Nanotechnol. Microelectron. Mater. Process. Meas. Phenom.* **35**, 03D113 (2017).

<sup>50</sup> E. Farzana, Z. Zhang, P.K. Paul, A.R. Arehart, and S.A. Ringel, *Appl. Phys. Lett.* **110**, 202102 (2017).

<sup>51</sup> S. Oh, G. Yang, and J. Kim, *ECS J. Solid State Sci. Technol.* **6**, Q3022 (2016).

<sup>52</sup> J.H. Werner and H.H. Güttler, *J. Appl. Phys.* **73**, 1315 (1993).

<sup>53</sup> K. Zeng and U. Singisetti, in *2017 75th Annu. Device Res. Conf.* (IEEE, 2017), pp. 1–2.

### Table Captions:

**Table I.** HT-LPCVD growth conditions of  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> films on Sn-doped  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> substrate with

1050  $^{\circ}\text{C}$  temperature and 0.5 sccm diluted  $\text{SiCl}_4$  flow

**Table II.** Extracted electrical properties at room temperature from  $J$ - $V$ , and  $J$ - $V$ - $T$  measurements for S1, S2, S3, and S4

**Figure Captions:**

Fig. 1. AFM images of HT-LPCVD grown  $\beta$ - $\text{Ga}_2\text{O}_3$  films on (a) (001) Sn-doped  $\beta$ - $\text{Ga}_2\text{O}_3$  substrate, film thickness~13 $\mu\text{m}$  (sample S1); (b) (001) Sn-doped  $\beta$ - $\text{Ga}_2\text{O}_3$  substrate, film thickness~21 $\mu\text{m}$  (sample S3); (c) (010) Sn-doped  $\beta$ - $\text{Ga}_2\text{O}_3$  substrate, film thickness~13 $\mu\text{m}$  (sample S2); (d) (010) Sn-doped  $\beta$ - $\text{Ga}_2\text{O}_3$  substrate, film thickness~16 $\mu\text{m}$  (sample S4).

Fig. 2. XRD  $\omega$ -2 $\theta$  scan of (a) (001); and (b) (010)  $\beta$ - $\text{Ga}_2\text{O}_3$  homoepitaxial films grown on (001) and (010)  $\beta$ - $\text{Ga}_2\text{O}_3$  substrates, respectively. Prominent characteristic diffraction peaks from (a) (020) plane; and (b) (00l) planes from the wide scan range.

Fig. 3. (a) Schematic cross-section of the vertical Schottky diode structures fabricated on LPCVD (010 and 001)  $\beta$ - $\text{Ga}_2\text{O}_3$  substrates. (b) Room temperature forward current density ( $J$ ) vs Voltage ( $V$ ) characteristics for S1, S2. S3, and S4 Schottky barrier diodes. Inset shows forward characteristics of S2, S3, and S4. (c) Room temperature semilogarithmic current density ( $J$ ) vs Voltage ( $V$ ) characteristics for S1, S2. S3, and S4 Schottky barrier diodes.

Fig. 4. (a) Semi-logarithmic current density ( $J$ ) vs Voltage ( $V$ ) characteristics at different temperatures showing variation in forward and reverse current densities with temperature for S1. Inset shows the forward  $J$ - $V$  characteristics in the high-bias region. (b) The temperature dependence of ideality factor,  $\eta$ , and the barrier height,  $\Phi_B$  of S1 Schottky diode.

Fig. 5. The temperature dependence of specific On-resistance,  $R_{on,sp}$  of (a) S1 (b) S2 Schottky diodes.

Fig. 6. (a) Reverse  $J-V$  characteristics of S1  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> Schottky diode, where the destructive breakdown was observed at  $V_{br} = -385$  V. (b) Reverse  $J-V$  characteristics of S2  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> Schottky diode, where the destructive breakdown was observed at  $V_{br} = -435$  V.

### Tables:

Table I.

| Sample No | Substrate Orientation | Estimated Doping     | Growth Duration | Estimated Thickness <sup>b</sup> ( $\mu\text{m}$ ) | Growth Rate ( $\mu\text{m}/\text{h}$ ) | % Smooth area of overall sample | Backside Growth |

|-----------|-----------------------|----------------------|-----------------|----------------------------------------------------|----------------------------------------|---------------------------------|-----------------|

| S1        | (001)                 | $1.0 \times 10^{16}$ | 1 h.            | 13                                                 | 13                                     | 75                              | Less            |

| S2        | (010)                 | $1.2 \times 10^{16}$ | 50 min.         | 13                                                 | 15.6                                   | 60                              | Medium          |

| S3        | (001)                 | $1.5 \times 10^{16}$ | 1 h.            | 21                                                 | 21                                     | 40                              | More            |

| S4        | (010)                 | $2 \times 10^{16}$   | 50 min.         | 16                                                 | 19                                     | 45                              | Medium          |

a Estimated doping is measured from co-loaded c-sapphire samples

b Estimated thickness is measured from co-loaded Fe-doped substrates with AlGaO buffer

Table II.

| Sample No | Ideality Factor, $\eta$ | $\Phi_B$ (eV) | $R_{on,sp}$ ( $\text{m}\Omega\text{cm}^2$ ) | Leakage current @ -5V ( $\text{A}/\text{cm}^2$ ) |

|-----------|-------------------------|---------------|---------------------------------------------|--------------------------------------------------|

| S1        | 1.37                    | 1.0           | 4.29                                        | $2.24 \times 10^{-8}$                            |

| S2        | 1.28                    | 1.5           | 117.38                                      | $1.464 \times 10^{-7}$                           |

| S3        | 2.36                    | 1.58          | 528.65                                      | $4.374 \times 10^{-7}$                           |

| S4        | 1.63                    | 1.53          | 62550                                       | $9.745 \times 10^{-8}$                           |

### Figures:

Fig. 1.

Fig. 2.

Fig. 3.

Fig. 4.

Fig. 5.

Fig. 6.