### **β-Gallium oxide power electronics 9**

Cite as: APL Mater. 10, 029201 (2022); https://doi.org/10.1063/5.0060327

Submitted: 17 June 2021 • Accepted: 14 December 2021 • Published Online: 07 February 2022

🔟 Andrew J. Green, James Speck, Grace Xing, et al.

### **COLLECTIONS**

This paper was selected as Featured

#### **ARTICLES YOU MAY BE INTERESTED IN**

Recent progress on the electronic structure, defect, and doping properties of Ga<sub>2</sub>O<sub>3</sub> APL Materials 8, 020906 (2020); https://doi.org/10.1063/1.5142999

Gallium oxide (Ga<sub>2</sub>O<sub>3</sub>) metal-semiconductor field-effect transistors on single-crystal  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> (010) substrates

Applied Physics Letters 100, 013504 (2012); https://doi.org/10.1063/1.3674287

Perspective: Ga<sub>2</sub>O<sub>3</sub> for ultra-high power rectifiers and MOSFETS

Journal of Applied Physics 124, 220901 (2018); https://doi.org/10.1063/1.5062841

### **β**-Gallium oxide power electronics

Cite as: APL Mater. **10**, 029201 (2022); doi: 10.1063/5.0060327 Submitted: 17 June 2021 • Accepted: 14 December 2021 •

Vlew Online

Published Online: 7 February 2022

Andrew J. Green, Andrea Arias-Purdue, Andrea Arias-Purdue, Sivek Mehrotra, Akito Kuramata, Kohei Sasaki, Shinya Watanabe, Kimiyoshi Koshi, Andrea Arias-Purdue, Sivek Mehrotra, Akito Kuramata, Kohei Sasaki, Shinya Watanabe, Kimiyoshi Koshi, Andrea Arias-Purdue, Sivek Mehrotra, Akito Kuramata, Kohei Sasaki, Shinya Watanabe, Kimiyoshi Koshi, Andrea Arias-Purdue, Sivek Mehrotra, Akito Kuramata, Kohei Sasaki, Shinya Watanabe, Kimiyoshi Koshi, Andrea Arias-Purdue, Shinya Watanabe, Siriam Krishnamoorthy, Andrea Arias-Purdue, Shinya Watanabe, Kimiyoshi Koshi, Andrea Arias-Purdue, Shinya Watanabe, Siriam Krishnamoorthy, Andrea Arias-Purdue, Shinya Watanabe, Andrea Arias-Purdue, Andrea Arias-Purdue, Shinya Watanabe, Andrea Arias-Purdue, Andrea Arias

For affiliations, please see the end of the Reference section

#### **ABSTRACT**

Gallium Oxide has undergone rapid technological maturation over the last decade, pushing it to the forefront of ultra-wide band gap semiconductor technologies. Maximizing the potential for a new semiconductor system requires a concerted effort by the community to address

technical barriers which limit performance. Due to the favorable intrinsic material properties of gallium oxide, namely, critical field strength,

widely tunable conductivity, mobility, and melt-based bulk growth, the major targeted application space is power electronics where high performance is expected at low cost. This Roadmap presents the current state-of-the-art and future challenges in 15 different topics identified

by a large number of people active within the gallium oxide research community. Addressing these challenges will enhance the state-ofthe-art device performance and allow us to design efficient, high-power, commercially scalable microelectronic systems using the newest

semiconductor platform.

© 2022 Author(s). All article content, except where otherwise noted, is licensed under a Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/). https://doi.org/10.1063/5.0060327

#### TABLE OF CONTENTS 1. Gate driver requirements . . . . . . . . . Topology and controls considerations . . 2 INTRODUCTION ...... 3. Projected β-Ga2O3 switch performance AN OUTLOOK TO THE COMMERCIAL MAR-KET OPPORTUNITIES OF **\$-**Ga<sub>2</sub>O<sub>3</sub> BASED POWER 4. Projected β-Ga2O3 switch performance DEVICES ..... and comparison to GaN devices...... 8 Next generation power systems . . . . . . 4 Current and future challenges . . . . . . . . . . Low thermal conductivity . . . . . . . . 5 1. IV. Lack of a p-type . . . . . . . . . . . . . . . . 2 Status of the area $\dots \dots \dots \dots \dots$ The lack of p-type may also be a problem Current and future challenges in this area . . . . for junction termination design ......5 4. Wafer size limitation . . . . . . . . . . . . 5 Epitaxial wafers . . . . . . . . . . . . . . . . Several poly-types . . . . . . . . . . . . . . . 5 5. 6. E-mode device design . . . . . . . . . 6 Lack of reliability data . . . . . . . . . . . 6 Concluding remarks . . . . . . . . . . . . . . . . 6 Czochralski (CZ)......11 DEFENSE BASED POWER CONVERTER APPLICA-III. 2. Edge defined film fed growth (EFG)......11 6 3. Current and future challenges . . . . . . . . . . 6

|       | B.  | Conclusion                                                                | 12 |

|-------|-----|---------------------------------------------------------------------------|----|

| VI.   | MO  | LECULAR BEAM EPITAXY                                                      | 12 |

|       | A.  | Status                                                                    |    |

|       | B.  | Current and future challenges                                             |    |

|       |     | 1. MBE: Growth rate                                                       |    |

|       |     | 2. MBE: Electrical quality doping, purity, and                            |    |

|       |     | point defects                                                             | 13 |

|       |     | 3. Epitaxy: Crystallinity and extended defects                            | 15 |

|       |     | 4. Epitaxy: Surface and interface morphology                              | 15 |

|       |     | 5. Epitaxy: Alloys and heterostructures                                   | 15 |

|       | C.  | Concluding remarks                                                        |    |

| VII.  | ME  | TALORGANIC VAPOR PHASE EPITAXY                                            |    |

| , 11. | A.  | Status                                                                    |    |

|       | В.  | Current and future challenges                                             |    |

|       | ъ.  | Substrate orientation and growth window                                   | 16 |

|       |     | Material purity                                                           | 16 |

|       |     | 3. Dopants and defects                                                    | 16 |

|       |     | 4. Alloys and heterostructures                                            | 17 |

|       | C.  | Concluding remarks                                                        | 17 |

| 37111 |     | HER GROWTH METHODS: HALIDE VAPOR                                          | 1, |

| VIII. |     |                                                                           |    |

|       |     | ASE EPITAXY, LOW PRESSURE CHEMICAL NAPOR                                  |    |

|       |     | POR DEPOSITION, MIST CHEMICAL VAPOR POSITION, AND PULSED LASER DEPOSITION | 17 |

|       | A.  | Status                                                                    |    |

|       | В.  | Current and future challenges                                             |    |

|       | ъ.  | Halide vapor phase epitaxy                                                | 17 |

|       |     | <ol> <li>Low pressure chemical vapor deposition .</li> </ol>              | 18 |

|       |     | 3. Mist chemical vapor deposition                                         | 18 |

|       |     | 4. Pulsed laser deposition                                                | 18 |

|       | C.  | Concluding remarks                                                        | 19 |

| IV    |     | _                                                                         |    |

| IX.   | ØH. | RACTERIZATION                                                             |    |

|       | A.  | Status                                                                    | 19 |

|       | В.  | Current and future challenges                                             | 20 |

|       | C.  | Concluding remarks                                                        | 21 |

| Χ.    |     | DAMENTAL MATERIALS AND TRANSPORT                                          |    |

|       |     | OPERTIES                                                                  |    |

|       | Α.  | Status of the area                                                        |    |

|       | В.  | Status of the area                                                        |    |

|       |     | 1. 2DEG transport properties                                              |    |

|       |     | 2. AlGaO properties                                                       |    |

|       | G   | 3. Impact ionization parameters                                           |    |

|       | C.  | Concluding remarks                                                        |    |

| XI.   |     | IOTTKY BARRIER DIODES                                                     |    |

|       | A.  | Status of the area                                                        |    |

|       | В.  | Current and future challenge                                              |    |

|       |     | 1. On-resistance limit                                                    | 24 |

|       |     | 2. Strategies for Ron, SBD optimization                                   | 24 |

|       |     | 3. Edge termination                                                       | 25 |

|       |     | 4. Barrier height control                                                 |    |

|       |     | 5. Thermal management                                                     |    |

|       | C.  | Concluding remarks                                                        | 26 |

| XII.  | VER | RTICAL DEVICES                                                            | 26 |

|       | A.  | Status of the area                                                        |    |

|       | B.  | Current and future challenges in this area                                | 27 |

|       |     | <ol> <li>Design similarities between a trench SBD</li> </ol>              |    |

|       |     | and a FinFET                                                              | 27 |

|       |      | 2.    | Threshold vo     | oltage control an                            | d stability    | 27 |

|-------|------|-------|------------------|----------------------------------------------|----------------|----|

|       |      | 3.    | Reliability of   | of MIS structure                             | s for reaching |    |

|       |      |       | high fields ir   | n <b>β-</b> Ga2O3                            | -              | 27 |

|       |      | 4.    | Current          |                                              | employing      |    |

|       |      |       | semi-insulat     | ing <b>β</b> -Ga <sub>2</sub> O <sub>3</sub> |                | 27 |

|       |      | 5.    |                  |                                              |                |    |

|       | C.   | Con   |                  |                                              |                |    |

| XIII. | LAT  | ERAL  | DEVICES          |                                              |                | 28 |

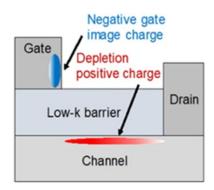

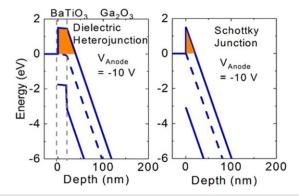

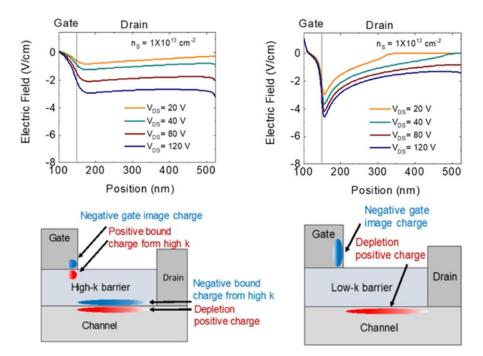

|       | A.   | Cur   | rent and future  | challenges in th                             | is area        | 28 |

| XIV.  | DIEI | LECTE | RIC ENGINEE      | RING                                         |                | 30 |

|       | A.   | Chal  | llenges          |                                              |                | 30 |

|       | B.   |       |                  |                                              |                |    |

| XV.   | ULT  | RA-H  | IGH k DIELEC     | CTRICS                                       |                | 32 |

|       | A.   | Chal  | llenges          |                                              |                | 32 |

|       | B.   | Con   | cluding remarl   | ζs                                           |                | 33 |

| XVI.  | THE  | RMAI  | L MANAGEM        | ENT                                          |                | 33 |

|       | A.   | The   | rmal character   | zation                                       |                | 34 |

|       | B.   | Dev   | rice-level therm | al management                                |                | 34 |

|       | C.   |       |                  |                                              |                |    |

|       | D.   | Con   | cluding remark   | ζs                                           |                | 35 |

| KVII. | CLO  | SING  | REMARKS          |                                              |                | 35 |

|       | AUT  | HOR   | DECLARATIO       | ONS                                          |                | 36 |

|       | DAT  | AAV   | AILABILITY       |                                              |                | 36 |

|       | REF  | ERENC | CES              |                                              |                | 36 |

|       |      |       |                  |                                              |                |    |

#### I. INTRODUCTION

#### Andrew J. Green, James Speck, Grace Xing

With extreme rarity, a materials result has the power to rally the research community around a new semiconductor technology. There are many reasons for this, but first and foremost, potential leap-ahead performance must be present from multiple rare intrinsic material properties. Second, a materials supply chain must often be created and sustained by multiple long-term government investments (semiconductor research tends to be cost prohibitive). Finally, the research community must break through technical barriers that inhibit performance and commercialization. For the first time in decades, a research community has risen in support of a new technology.  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> has the technical and programmatic momentum not seen in decades since the rise of SiC and GaN research in the

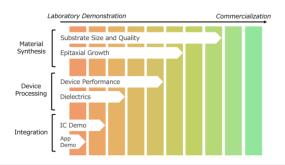

$\beta$ -Ga<sub>2</sub>O<sub>3</sub> is unique. The material has a collection of properties that, until recently, has not been observed in one system.  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> has an ultra-wide bandgap of nearly 5 eV. The material can not only conduct electrons but also maintain extremely high fields. Most importantly, it has a large, scalable low-cost substrate. These properties existing together have enabled one of the most exciting fields to explode. The availability of substrates is greater now than it ever has been, and with new companies developing substrates for commercialization in the near future, the pace of progress is expected to grow. Figure 1 shows commercialization progress for various sectors in the  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> semiconductor development chain. As expected, materials synthesis has made the most progress toward large scale production as high-quality materials are almost a prerequisite for advanced device development. While

FIG. 1. A top-level view of the technology progress for various sectors toward commercialization of  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> applications as of October 2021.

many device demonstrations have taken place, many design optimizations still need to be explored. The relatively new opportunity to purchase 2-in. diameter substrates will enable large-scale experiments. The large bandgap and field strength have created a new set of problems for materials and device researchers. To this date, avalanche breakdown has not been measured in  $\beta$ -Ga<sub>2</sub>O<sub>3</sub>. Every device breakdown to date has resulted from catastrophic dielectric failure. Until avalanche breakdown is observed, the true potential of this technology will not be known. Finally, integration and application demonstrations have still yet to be realized. The availability of large-scale substrates should be a significant enabling factor for the circuit and application demonstrations. One major step forward requires the community needs to reach up to application engineers to probe for requirements that  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> can address. Overall, the maturation of this material has progressed with incredible pace.

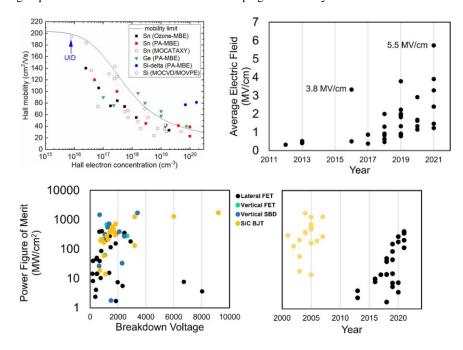

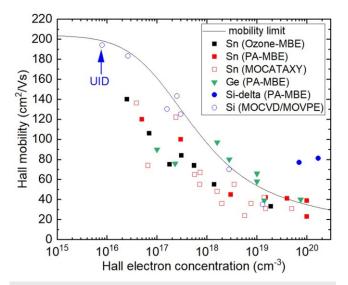

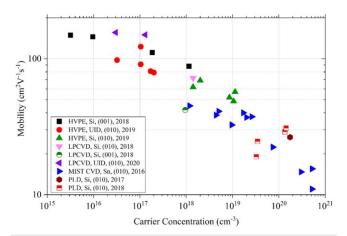

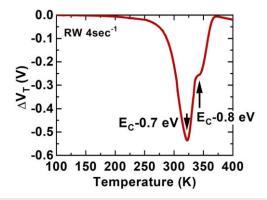

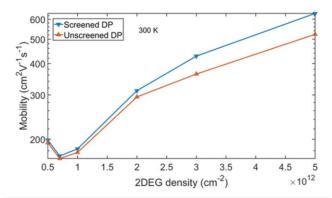

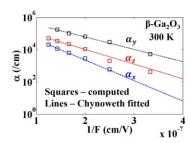

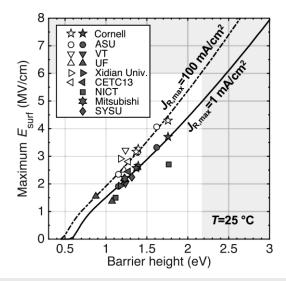

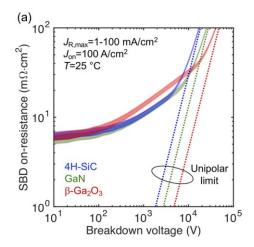

Per Baliga's Figure of Merit, mobility and field strength are the main predictors of conduction losses and therefore performance for a power device. As seen in Fig. 2 (left), multiple groups have been able to demonstrate bulk doping for a variety of concentrations. This enabled the device community to make quick strides in fabricating high performance devices. Figure 2 (right) shows a collection of  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> lateral device results. Until 2016, no device in any material had measured a greater average critical field strength than SiC. (2.5 MV/cm). Since then,  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> has repeatedly pushed the boundaries for high field devices.

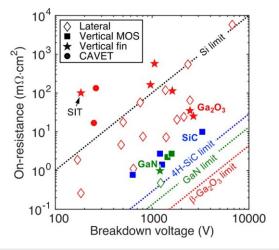

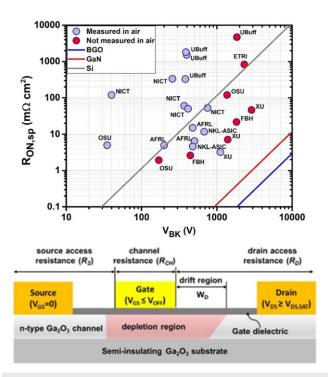

The large breadth of the device that results over the past decade is a testament to the materials quality and availability. Figure 3 shows the Power Figure of Merit (PFOM) as a function of device breakdown voltage (BV) for multiple device topologies. There are major gaps which have yet to be demonstrated. Surprisingly, voltages >3 kV have been rare in  $\beta$ -Ga<sub>2</sub>O<sub>3</sub>. This is expected to change over in the next five years as field management issues are addressed. On the right-hand side of Fig. 3, historical progress of lateral  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> device PFOMs is compared to SiC bipolar junction transistors (BJTs). Incredibly, the  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> PFOM has improved exponentially over the past decade approaching that of the BJT from the middle to late 2000s. For continued improvement, parasitic removal and field management will need to be achieved.

There has been incredible progress over the past decade, but there is still work to be done. This document serves to identify the main challenges that currently limit  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> from reaching the full performance potential. For each chapter in this Roadmap, the state of the art is described briefly followed by an analysis of the most important technical barriers in each respective section. This serves as a call to action, for if the community can address these barriers, it will enable  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> to be the next commercialized semiconductor.  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> is at a critical point in the development cycle. The materials supply chain is healthy. Device results are swift and encouraging. The technology readiness level is improving, but the community must establish application pull to attract serious investment further motivating development. This guide will help inform future research directions and help propel  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> to the world's next great commercial semiconductor technology.

**FIG. 2.** (Left) Hall mobility is plotted as a function of electron concentration. A wide range of bulk doping is available for  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> from the contact regime to the high blocking voltage regime. (Right) Average field (V<sub>BK</sub>/L<sub>GD</sub>) is plotted as a function of time for lateral  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> FETs.

**FIG. 3.** (Left) The Power Figure of Merit (PFOM) is shown for multiple  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> topologies (black: lateral FET, teal: vertical FET, and blue: vertical SBD) as well as the SiC BJT (yellow). (Right) PFOM is plotted as a function of time for SiC BJTs and  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> lateral FETs. Initial exponential growth is observed in  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> due to the rapidity of materials and device optimization.

II. AN OUTLOOK TO THE COMMERCIAL MARKET OPPORTUNITIES OF  $\pmb{\beta}\text{-}\text{Ga}_2\text{O}_3$  BASED POWER DEVICES

### Peter Moens, Fredrik Allerstam, Krister Gumaelius, Thomas Neyer

#### A. Status of the area

For many decades, Si-based devices dominated the field of power electronic devices. Substantial progress and device improvement was achieved by the commercialization of the HEXFET® transistor in the 1980s, the insulated gate bipolar transistor (IGBT) in the 1990s, and the superjunction transistor in the 2000s. Each major improvement was due to clever junction engineering using Si as the base substrate. However, since 2010, devices based on other material systems entered the market and the focus shifted from junction engineering to materials engineering. SiC diodes were introduced around 2010 and junction field-effect transistors (JFETs) and MOSFETs followed soon after. Steady and continuous improvement in SiC material quality, increase in wafer size (up to 200 mm today), and better process control have resulted in lower cost substrates. In 2019, SiC devices took up  $\sim$ 3% of the total power device market (including modules) growing to exceed 12% in 2025.1 Recently, GaN-based vertical power devices are available from several suppliers (JFETs and MOSFETs). These devices are built on native GaN bulk substrates, similar to SiC. The wafer size is limited to 100 mm. Another emerging class of devices are based on AlGaN/GaN high-electron-mobility transistors (HEMTs), which can be built on low-cost 200 mm Si wafers on which a thin ( $\sim$  few  $\mu$ m) GaN-based layer is grown by metal organic chemical vapor deposition (MOCVD).<sup>2</sup> Although their market share is small, it is expected to grow substantially over the next few years, serving applications below 900 V. This is a similar technology to what is used for RF devices for mm wave applications. First successful attempts to grow GaN-on-Si on 300 mm have been published.<sup>3</sup>

Looking toward the future, a number of other wide-bandgap materials are currently being explored in research. The most studied is **diamond** that is considered to be the "ultimate material." However, technological obstacles (lack of efficient n-type doping, conductive surface channels, lack of substrates, and difficulties to make ohmic contacts) have for a long time blocked the demonstration of performant devices. Unless spectacular progress is made on these issues, no real-world implementations are expected in the foreseeable future. AIN is probably the most interesting wide bandgap material because it combines high thermal conductivity with a very large bandgap of 6.2 eV. The bandgap is even higher than that of diamond (5.5 eV). Currently, a few AIN bulk substrate suppliers exist and the substrates are 2 in. in diameter or below.

Gallium oxide is the only wide bandgap material that can be grown from a melt and as such is potentially a low-cost material. It can be n-type doped by several elements with good control over a wide range. Doping from a melt results in resistivity down to 10 mΩ cm. Halide vapor phase epitaxy (HVPE) grown epi can be controlled corresponding to doping concentrations  $\sim 10^{19}$  and mid  $10^{15}$  cm<sup>-3</sup>, respectively. By Si implantation, resistivity can be as low as 1 mΩ cm. Ohmic and Schottky contacts can be made by

using standard metals (Ti, Al, and Ni) and relatively low annealing temperatures.<sup>5</sup> Wafering and lapping can be done using standard production tools. Different dielectrics [e.g., atomic layer deposition (ALD) deposited Al<sub>2</sub>O<sub>3</sub>] can be used as a gate dielectric. Recently, a number of publications reported on promising device characteristics and performance.<sup>6–9</sup>

#### B. Current and future challenges

$\beta$ -Ga<sub>2</sub>O<sub>3</sub> is a material system with a high critical electric field and a relatively low mobility, which allows devices with improved performance compared to SiC and even GaN. Equally important, the material can be grown from a melt and can thus be produced with a very high crystalline quality at low cost when compared to (bulk) GaN, SiC, AlN, and diamond. The crystal growth techniques used today allow scaling from 100 to 150 mm.

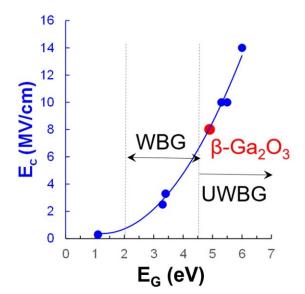

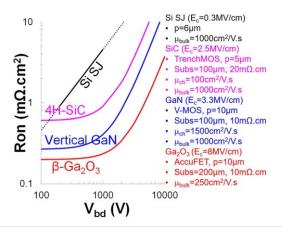

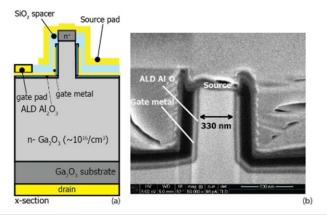

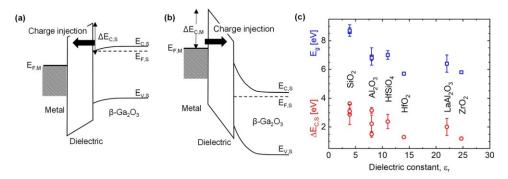

Figure 4 depicts the estimated critical electric field  $E_c$  vs the bandgap energy  $E_g$  for different material systems which are attractive to power semiconductor applications. Only homo-epitaxial material systems are included, which are the ones of interest for making vertical devices.  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> is well positioned in terms of  $E_c$  and has an estimated substantial lower material cost than any other ultra wide bandgap material. Figure 5 shows the predicted device performance (on-state resistance Ron vs blocking voltage capability  $V_{bd}$ ), with the assumptions on substrate thickness and resistivity, bulk and inversion layer mobility, device pitch, etc., as calculated from basic device physics. Figure 5 clearly shows the potential to reach lower Ron for a given breakdown voltage  $V_{bd}$  (e.g., for a 1.2 kV device, a typical breakdown is around 1.5 kV).

Besides on-resistance ( $\hat{R}_{ON}$ ) and breakdown voltage ( $\hat{V}_{BK}$ ), also switching capacitance, output capacitance, charge, and energy are important. Based on the physics equations that relate the output

**FIG. 4.** Estimated critical electric field  $E_c$  vs the bandgap energy  $E_g$  for the different material systems that are attractive to power semiconductor applications. Bulk materials only, so no hetero-epitaxy (e.g., for HEMTs).

**FIG. 5.** Calculated theoretical performance ( $R_{ON}$  vs  $V_{BK}$ ) for vertical power devices. Assumptions used in the calculation are listed on the right. The model takes into account the contact, channel, drift, and substrate resistances; p denotes the cell-pitch.

capacitance (Coss), charge (Qoss), and energy (Eoss) to the expansion on the depletion width,  $R_{ON}$  \*  $Q_{OSS}$  and  $R_{ON}$  \*  $E_{OSS}$  can be calculated using the same assumptions as shown in Fig. 5. Table I shows the calculated values for a 1.2 kV rated device (with an assumed  $V_{bd}=1.5$  kV). The prime transistor figures of merit  $R_{ON}$  \*  $Q_{OSS}$  and  $R_{ON}$  \*  $E_{OSS}$  are  $\sim\!3\times$  better than for 4H–SiC and  $\sim\!20\%$  better than for bulk GaN. Figure 5 and Table I show the great promise of  $\beta\text{-}Ga_2O_3$  as a material for power switching devices.

There are, however, some important obstacles and areas of research which need to be overcome to make  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> based power devices economically viable and a reality in real-life power switching applications.

#### 1. Low thermal conductivity

With a value of  $\sim 0.2$  W/cm K,  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> has a thermal conductivity which is 8× lower than bulk GaN and  $\sim 30\times$  lower than SiC. Efficient heat transfer is a must for power devices. This is especially true for transistors with a small overall die area. As can be deduced from Table I, for a device with the same voltage and current (or on-resistance) rating, a  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> die will be  $10\times$  smaller than a

corresponding SiC die. Therefore, die thinning ( $<50~\mu m$ ) is a must, and technologies to transfer thin die directly to the lead frame need to be explored. The possibility to easily cleave the  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> may pose a way forward to produce very thin die. In addition, heat removal from the top surface needs to be studied through innovative assembly technologies. Demonstrations of heat removal techniques <sup>10,11</sup> are expected to be a major research area as devices begin to be distributed throughout the community in the next five years. This will have major ramifications with respect to application space (i.e., power rating and duty cycle).

#### 2. Lack of a p-type

To date, there is no p-type doping in  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> since acceptor states are deep in the bandgap, >1 eV from the valence band. The valance band is also theorized to be flat resulting in negligible hole transport. This means that no avalanching p—n junction can be made. The lack of an avalanching junction is a concern for applications that are used in regions with noisy power grids or need to take over large inductive loads rapidly, like UPS systems.

### 3. The lack of p-type may also be a problem for junction termination design

Management of the electric fields at the die edge is an important device design focus point, as it impacts the voltage rating of the transistor or diode as well as its reliability. For termination structures, the lack of p-type can perhaps be mitigated by the integration of p-type oxides, such as sputtered NiO. Also beveled terminations are under investigation.

#### 4. Wafer size limitation

Today, the maximum wafer size that is commercially available is 100 mm. From a practical commercial point-of-view, the minimum wafer size should be 150 mm, with a roadmap to 200 mm. Larger wafer size does not only reduce the product cost but also allows the device processing in more advanced fabrication lines, which result in better process control, lower defect densities, etc.

#### 5. Several poly-types

Ga<sub>2</sub>O<sub>3</sub> has many poly-types, among which the  $\alpha$ -phase and  $\beta$ -phase are the most investigated.  $\alpha$ -Ga<sub>2</sub>O<sub>3</sub> is rhombohedral, has a high E<sub>c</sub> ~ 10 MV/cm, but is only thermally stable up to ~600 to 700 °C. Since Al<sub>2</sub>O<sub>3</sub> and epitaxial In<sub>2</sub>O<sub>3</sub> have the same  $\alpha$ -structure,

**TABLE I.** Calculated prime transistor parameters for a 1.2 kV rated vertical power transistor. Assumptions for the calculation are listed in Fig. 5. The prime transistor figures of merit  $R_{ON} \cdot Q_{OSS}$  and  $R_{ON} \cdot E_{OSS}$  are  $\sim 3 \times$  better than for 4H–SiC and  $\sim 20\%$  better than for bulk GaN.

| $V_{RATING} = 1200 \text{ V}$ |                          |       |       |        |          |                                         |  |  |

|-------------------------------|--------------------------|-------|-------|--------|----------|-----------------------------------------|--|--|

| Parameter                     | Unit                     | Si    | Si SJ | 4H–SiC | Bulk GaN | $\beta$ -Ga <sub>2</sub> O <sub>3</sub> |  |  |

| R <sub>ON</sub>               | $(m\Omega \text{ cm}^2)$ | 227   | 6.84  | 1.8    | 0.589    | 0.189                                   |  |  |

| Qoss                          | $(nC/cm^2)$              | 313   | 6260  | 2150   | 2710     | 7080                                    |  |  |

| Eoss                          | $(\mu J/cm^2)$           | 125   | 250.4 | 857    | 1082     | 2829                                    |  |  |

| $R_{ON} \cdot Q_{OSS}$        | $(m\Omega nC)$           | 71051 | 42818 | 3870   | 1596     | 1338                                    |  |  |

| $R_{ON} \cdot E_{OSS}$        | $(m\Omega \mu J)$        | 28375 | 1713  | 1543   | 637      | 535                                     |  |  |

it paves the way to hetero-structures in a similar way as is done for the AlN/GaN/InN material system. P-type would be possible through combination with  $\alpha$ -Ir<sub>2</sub>O<sub>3</sub> and  $\alpha$ -Rh<sub>2</sub>O<sub>3</sub>, which are p-type oxides. These hetero-structures are, however, lateral device types.  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> is monoclinic, can be grown from a melt, and is thermo-mechanically stable until 1700 °C. From a research perspective, the multitude of different phases is interesting, but from a commercialization point of view, it would be preferred if the development effort could be focused on the  $\beta$  phase due to the maturity of the sample supply chain.

#### 6. E-mode device design

The lack of p-type also puts restrictions on how to make e-mode transistors. First results using fin field-effect transistors (FINFET) type of accumulation FETs are promising but require tight process control and advanced processing equipment. It remains to be seen if this is a viable option. Another option is to use a depletion mode transistor cascoded with a Si (or other) low voltage MOSFET. Market adoption for cascaded SiC JFETs or AlGaN/GaN HEMTs is limited due to the fact that the internal node cannot be controlled during switching.

#### 7. Lack of reliability data

Reliability on any type of  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> device (diode or transistor) is still in its infancy.

#### C. Concluding remarks

From a power device manufacturer's perspective, β-Ga<sub>2</sub>O<sub>3</sub> is the preferred ultra wide bandgap material because it can be grown from a melt and has a high crystalline quality and a relatively low cost. There is a roadmap to 150 mm. The lack of p-type is a serious drawback for transistors. On the plus side, most of the fundamental process modules for making  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> Schottky diodes are available: standard Ohmic and Schottky metallization's, good control of the n-type doping of the epi, and low resistivity substrates. Termination structures for the diodes will have to be optimized and further developed. A good market entry point for these diodes could be the 600 V and 1. 2 kV voltage classes, where they will compete with SiC diodes, e.g., for high-end power supplies used in server farms or in boost stages of energy efficient power converters. These devices could potentially offer better than SiC performance at reduced cost. According to Ref. 1, this market alone will amount to 100 M\$ by 2025 and is driven by efficiency standards mandated by governments. β-Ga<sub>2</sub>O<sub>3</sub> diodes will potentially enable a further improvement step from "80 plus" titanium (currently the highest certification level for power supply efficiency) with efficiencies exceeding >95% at full load. If by that time  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> diodes can prove reliability at good cost and they can be sourced easily on the power electronic market, they could take significant share of the TAM

At higher voltage classes (e.g., 1.7 kV and beyond), doping control has to be proven to be reproducible and stable for production. In addition, the larger surface fields will create additional challenges with the passivation layers on top of the termination. Below 600 V, there will be competition also with lateral devices that are not limited to bulk properties.

### III. DEFENSE BASED POWER CONVERTER APPLICATIONS

#### Andrea Arias-Purdue, Vivek Mehrotra

Much of the traditional military system's power conversion needs have been fulfilled by sub-assemblies that have continuously leveraged improvements in commercial semiconductors and integrated circuits, such as state-of-the-art MOSFETs, drivers, and controllers. For applications ranging from low-voltage to kV power converters, switched-mode power supplies have become the dominant approach due to their efficiency benefits. For example, switching regulators (such as buck converters) offer typical efficiencies of 70%-95%, up to switching frequencies in tens of megahertz for commercial parts<sup>12,13</sup> and up to hundreds of megahertz in research. 14-16 This remarkable progress is also complemented by research efforts such as DARPA's Microscale Power Conversion (MPC) program, <sup>17,18</sup> where DARPA requested a ~1 GHz switching GaN-based power converter to enable very high bandwidth and efficiency supply modulators for power amplifiers. Significant challenges surfaced during the MPC effort. The switches and gate drivers developed needed to have at least an order of magnitude less total gate charge and power dissipated, respectively, for efficient 1 GHz switching converters (28 m $\Omega$  nC<sup>19</sup> is the lowest R<sub>ON</sub> × Q<sub>G</sub> demonstrated under MPC). It also became apparent that the co-design of the power amplifier and the switch modulator would result in the most efficient system design.

As new wider bandgap semiconductor materials have matured and have become widely available (i.e., SiC and GaN devices), state-of-the-art modules with progressively improved performance have followed-improvements in size, weight, efficiency, operational temperature range, and cost. In addition, several DoD systems require ruggedness at high ambient temperature: for this reason, ultra wide bandgap (UWBG) materials, such as β-Ga<sub>2</sub>O<sub>3</sub>, are excellent candidates for maximizing performance even under these extreme environmental conditions. While several circuit techniques can be employed to effectively switch a power circuit at a frequency higher than its individual branches, we note that the maximum performance benefit is often achieved when the power commutation path is monolithically (or perhaps 3D) integrated using the least number of components, thus operating at the maximum feasible switching frequency as allowed by the device's dynamic losses and as permitted by the intrinsic losses of the wiring closing the critical power commutation path.

#### A. Current and future challenges

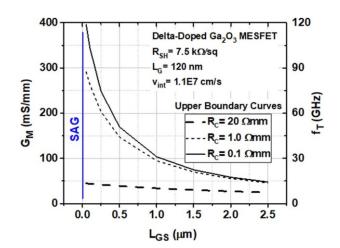

Switching power converters operating at >1 GHz remain a challenge due to the stringent  $R_{ON} \times Q_G$  requirements imposed on the main switch, a necessary condition to achieve high efficiency. Owing to its ultra-high Baliga figure of merit,  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> MOSFETs with over 3.8 and 5.3 MV/cm of mean peak breakdown field strengths<sup>20</sup> have been demonstrated, constituting the highest field of any lateral FET measured to date. The key requirements for next-generation  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> power devices and ICs are low loss power devices for high frequency operation: low conduction ( $R_{ON}$ ) and switching losses ( $Q_G$ ) and low turn-on and turn-off energy. We estimate that a sheet

charge density  $N_{SH}$  of  $9.6\times10^{12}$  cm $^{-2}$  and a state-of-the-art mobility of  $200~\text{cm}^2/\text{V}$  s along with a contact resistance of  $0.1~\Omega$  mm and submicrometer access regions will enable  $\beta\text{-Ga}_2\text{O}_3$  devices with a total gate charge  $Q_G\sim0.8~\text{pC/mm}$  for a >100~V breakdown voltage lateral device, a  $>5\times$  improvement with respect to state-of-the-art GaN switches.

One of the key advantages of UWBG materials is their ability to withstand high ambient temperature, as demonstrated in Ref. 21, where  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> MOSFETs showing stable operation up to 300  $^{\circ}$ C were reported. In addition, packaging to enable high reliability in harsh environments will be required, taking into account coefficient of thermal expansion (CTE) matching and incorporating heat spreading, given the low coefficient of thermal conductivity for β-Ga<sub>2</sub>O<sub>3</sub>. It is likely that the development of new encapsulation compounds will be needed, simultaneously requiring low signal-loss and considering the device thermal budget. These challenges will need to be addressed at the multi-chip package level. Monolithic integration of power devices, gate drivers, and passives for lower parasitic beyond a certain critical frequency (~1 GHz) becomes necessary, since stray inductance and capacitance can completely negate the benefits of high frequency switching. Currently, magnetics are available which address switching frequencies at 1 GHz. Advanced 3D integration that can enable approximately tens of micrometers pitch between different chips is also a viable option.

High switching frequency (>1 GHz) enables size reduction of magnetics and capacitors as well as high bandwidth control for special applications, such as transient loads and envelope tracking (ET). For example, for ET, the output of the converter may be a pulse-width modulated signal with a control bandwidth that needs to be 10× faster than the signal bandwidth. Reduced volume magnetics are especially relevant for size-constrained platforms, such as Unmanned Aerial Vehicle (UAV) power systems and phased array power distribution, which necessitate both high efficiency due to limited heatsinking and small components due to the constrained area available in arrays operating at mm-wave frequencies. The magnetics required to support 1 GHz converters will have negligible hysteresis and Eddy current losses, with enough magnetic permeability and saturation flux density up to  $\sim 10$  GHz. We note that to materialize high speed converters, these passive components will have to be developed alongside emerging  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> devices. Novel materials such as FeSi-based magnetic compounds are possible candidates.<sup>22</sup>

#### 1. Gate driver requirements

Gate drivers are key to the implementation of the converter: they are essentially pulse amplifiers. The input pulse train from a control circuit defines the interval during which the main power switch should be on and off. The function of the gate driver circuit is to supply and remove charge from the gate of the main switch rapidly so that its state reflects the desired condition. The rate at which this charge is delivered and taken away is a major factor in determining how fast the main device switches. To maintain a square gate pulse, power delivery to each switch gate containing up to several harmonics of 1 GHz carrier fundamental is required to preserve high efficiency. In addition, realizing high efficiency, the gate driver output stage capacitances must be considerably less than those of the power device. To minimize switching losses, the gate driver must be able to turn the switch on and off at least additional 10× faster

(10% of the period), leading to an extremely challenging 20 ps rise and fall time requirement of the converter's pulse width modulated (PWM) output waveform, for a 1 GHz carrier converter. We note that the current state-of-the-art commercial gate drivers exhibit ~350 ps of rise and fall times,<sup>23</sup> while research gate drivers have been demonstrated to switch at 1 GHz carrier while exhibiting 106 ps/122 ps transitions and consuming 3 W of power,<sup>24</sup> not yet adequate for 1 GHz converters—since ~5× faster transitions are required. Therefore, to enable 1 GHz β-Ga<sub>2</sub>O<sub>3</sub> converters, a new class of ultra-short transition and low power consumption gate drivers must be developed, and critically, they must be integrated alongside the main switch power commutation loop so that stray inductance does not significantly lower the system efficiency. While highly scaled GaN could potentially be used if a suitable complementary technology was developed, it is possible that the most efficient gate driver solution would come from specifically tailored highly scaled β-Ga<sub>2</sub>O<sub>3</sub> MOSFETs.

#### 2. Topology and controls considerations

For Pulse Width Modulated (PWM) converters, the switch rise and fall times must be negligible as compared to both carrier frequency and minimum duty cycle—this is important to maintain low switching losses. Both the power switch and the control elements' bandwidth must be at least 20× greater than the fundamental switching frequency for negligible dynamic losses. In addition to switching frequency, control rise/fall time can be optimized to better leverage the  $\beta\text{-Ga}_2\text{O}_3$  device's low gate charge by generating very high device slew rates, thus minimizing dynamic losses. An application where this feature can offer a critical advantage is direct AC to AC conversion.

For many applications, a synchronous converter topology can be chosen to maximize efficiency: this is expected to also apply to  $\sim 1 \, \text{GHz}$  switching converters.

We note that for power distribution systems, an intermediate bus structure and Point of Load (PoL) regulators provide flexibility and maximize efficiency, and coupled with their high frequency and smaller footprint,  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> converters will provide the necessary degrees of freedom for high performance power system design.

# 3. Projected $\beta$ -Ga $_2$ O $_3$ switch performance and comparison to GaN devices

For Pulse Width Modulated (PWM) converters, the switch rise and fall times must be negligible as compared to both carrier frequency and minimum duty cycle—this is important to maintain low switching losses. Both the power switch and the control elements' bandwidth must be at least 20× greater than the fundamental switching frequency for negligible dynamic losses. In addition to switching frequency, control rise/fall time can be optimized to better leverage the  $\beta\text{-Ga}_2\text{O}_3$  device's low gate charge by generating very high device slew rates, thus minimizing dynamic losses. An application where this feature can offer a critical advantage is direct AC to AC conversion.

For many applications, a synchronous converter topology can be chosen to maximize efficiency: this is expected to also apply to  $\sim 1 \, \text{GHz}$  switching converters.

We note that for power distribution systems, an intermediate bus structure and Point of Load (PoL) regulators provide flexibility and maximize efficiency, and coupled with their high frequency

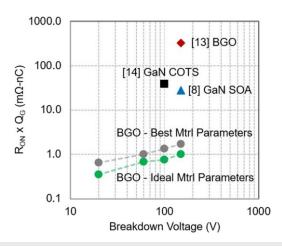

**FIG. 6.** Comparison of GaN,  $\beta$ -Ga<sub>2</sub>O<sub>3</sub>, and projected  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> performance. <sup>19,21</sup>

and smaller footprint,  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> converters will provide the necessary degrees of freedom for high performance power system design.

## 4. Projected **β**-Ga<sub>2</sub>O<sub>3</sub> switch performance and comparison to GaN devices

$\beta$ -Ga<sub>2</sub>O<sub>3</sub> and GaN switch performance is compared in Fig. 6. The projected  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> curves correspond to aggressively scaled devices (50 nm of gate length with sub-micrometer drain to source spacing assuming 383 and 500 V/ $\mu$ m of breakdown voltage for the best material parameters and ideal material parameters curves, respectively). The assumed material and calculated device parameters are included in Table II. We note that even based on the best  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> material parameters reported to date, our projected  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> device has a considerably lower RoN × Q<sub>G</sub> product as compared to both COTS and SOA GaN HEMTs of similar voltage rating.

#### 5. Next generation power systems

Future DoD needs include next generation phased array power distribution: high efficiency will require point of load (PoL) power conversion at the element/tile array level while also leveraging high bandwidth adaptive supplies to maximize the transmitter efficiency. It will be important to leverage high control bandwidths and ultralow size and weight in mm-wave arrays (very compact platforms due to the lambda/2 spacing requirement) to fulfill the need for high efficiency. UAV applications, typically also requiring lower voltage, will

consist of similar needs—ultra-size, optimized PoL converters. We envision a modular library of PoL  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> power devices that can fulfill these needs for a host of power conversion ratios—both boost and down converters—and power levels.

#### B. Concluding remarks

Reduced size, high efficiency converters for emerging applications, such as mm-wave digitally steered arrays and next generation UAVs, will necessitate fundamentally advanced power switches.  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> is poised to enable next generation power systems due to its superior material properties that enable its potential for significantly lower dynamic power losses as compared to Si and GaN, as well as its ability to withstand harsher environmental conditions, in part, due to its wider bandgap.

While it might not be advantageous to increase the converter switching frequency for high power applications (>100 W), the control bandwidth can be increased, thereby resulting in significant system efficiency improvements. To better understand these practical limitations, the intrinsic material-driven losses (wiring stray capacitance and inductance) must be considered within the converter design space to establish a fundamental switching frequency vs power loss trend for the wiring environments (including filter components) available to the power electronics designer.

#### IV. ECONOMIC MODEL

### Akito Kuramata, Kohei Sasaki, Shinya Watanabe, Kimiyoshi Koshi

#### A. Status of the area

The most important index affecting the economic model of  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> for power-device applications is the device price per unit current. The index is determined by the wafer price and the current density of devices. It is expected that  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> wafers will be able to be manufactured at low cost because  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> is suitable for melt growth, has medium hardness, and can be easily processed. This expectation is in contrast to the situation of other new power device materials, such as SiC or GaN, which suffer from high wafer manufacturing costs due to difficulties in bulk growth and wafer processing. Furthermore, since Baliga's figure of merit for  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> is larger than that of SiC or GaN, it is expected that the on-resistance of diodes or transistors can be reduced, and as a result, the current

**TABLE II.** State-of-the-art and ideal material parameters for  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> devices.

| Device                          | $N_{SH}$ (cm <sup>-2</sup> ) | Mobility | $R_{SH}$ $(\Omega/sq)$ | BV<br>(V/ <b>µ</b> m) | $\begin{array}{c} R_{C} \\ (\Omega \ mm) \end{array}$ | v_e<br>(cm/s)        | WG<br>(cm) | _     | Q <sub>G</sub><br>(C)  | $R_{ON}(\Omega)$<br>BV = 20 V | $R_{ON}(\Omega)$<br>BV = 60 V | $R_{ON}(\Omega)$<br>BV = 100 V | $R_{ON}(\Omega)$<br>BV = 150 V |

|---------------------------------|------------------------------|----------|------------------------|-----------------------|-------------------------------------------------------|----------------------|------------|-------|------------------------|-------------------------------|-------------------------------|--------------------------------|--------------------------------|

| Best mtrl.                      | $9.60 \times 10^{12}$        | 150      | 4340                   | 383                   | 0.20                                                  | $1.00 \times 10^6$   | 0.10       | 0.154 | $7.68 \times 10^{-13}$ | 0.853                         | 1.307                         | 1.760                          | 2.213                          |

| param.<br>Ideal mtrl.<br>param. | $9.60 \times 10^{12}$        | 200      | 3255                   | 500                   | 0.10                                                  | $2.00 \times 10^{6}$ | 0.10       | 0.307 | $7.68 \times 10^{-13}$ | 0.460                         | 0.880                         | 0.981                          | 1.307                          |

density can be made large.<sup>27</sup> Low-cost production will be enabled by filling the technological gaps in terms of the two factors mentioned above. In this chapter, we describe the challenges to reducing the wafer price of  $\beta$ -Ga<sub>2</sub>O<sub>3</sub>. See the discussion in Chaps. II, III, XI, XII, and XIII for challenges involved with improving device performance.

The present commercialization status of  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> substrates and epitaxial wafers are as follows: Currently, substrates made by the edge-defined film-fed growth (EFG) method in wafer sizes up to 4 in. are commercially available. In addition, 6-in. EFG substrates have been fabricated<sup>5</sup> and 2-in. substrates made by the Czochralski (CZ) method are expected to be commercially available in 2021.<sup>28</sup> Growth of 2-in. bulk crystals by using the vertical Bridgman (VB) method has been reported.<sup>29</sup> As for  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> epitaxial wafers, 4-in. wafers grown by halide vapor phase epitaxy (HVPE)<sup>30</sup> and 1-in. wafers grown by molecular beam epitaxy (MBE) are commercially available.<sup>31</sup> Metal organic chemical vapor deposition (MOCVD) epitaxial growth with excellent electrical properties has been reported.<sup>32</sup>  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> epitaxial wafers are still more expensive than SiC epitaxial wafers of the same size because  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> devices have not been commercialized yet and few wafers have been produced.

#### B. Current and future challenges in this area

The challenges of low-priced wafer production are described below.

#### 1. Substrates

The biggest challenge to lowering the manufacturing cost of bulk  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> crystal is that some of the expensive precious metal crucibles are lost during crystal growth or by recasting. In the EFG method and CZ method, Ir, which has a high melting point and can be used only in a low-concentration oxygen atmosphere, is used as a crucible material. Galazka et al. pointed out that a small amount of Ga exists in an equilibrium state of the gallium oxide melt above the melting point, and when it reacts with Ir, part of the crucible is lost.33 This problem becomes more serious as the size of the substrate increases. In the case of the EFG method, the lifespan of the crucible is about 6 months in the production of 2-in. bulk crystals, whereas during trial production of 6-in. bulk crystals, some holes opened at the bottom corner of the crucible after a considerably shorter period. In the case of 6-in. bulk crystals, the amount of Ga increases as the amount of Ga<sub>2</sub>O<sub>3</sub> melt increases, and the temperature difference inside the crucible increases, resulting in increased reaction in the high-temperature part of the crucible. These phenomena are presumed to shorten the lifespan of the crucible. As far as the EFG method and CZ method go, it is possible to solve this problem by reducing the size of the crucible. In the VB method, the temperature distribution in the furnace can be narrowed and the maximum temperature can be lowered, which expands the choice of metal materials. On the other hand, the method requires an atmosphere with a high oxygen concentration. Under such conditions, Pt-Rh alloy is a suitable crucible material.<sup>29</sup> The VB method can reduce the amount of precious metal lost in one growth, but it is necessary to recast the crucible after each growth. Therefore, the amount of precious metal wear cannot be reduced by more than an order of magnitude. The floating zone (FZ) method enables crystal growth without using precious metals, but the diameter of the reported

crystals is as small, about 1 cm, and there are no reports of large crystals having been successfully grown.

The challenge regarding the wafer fabrication process is to increase the number of substrates taken from one bulk. To meet it, the thickness of the substrate should be reduced. β-Ga<sub>2</sub>O<sub>3</sub> has the property of being easily cleaved on the (100) and (001) planes. In order to suppress cracking of the wafer due to cleavage, bevel processing has to be performed with high accuracy. Since gallium oxide has a crystal structure of a monoclinic system with low symmetry, the ease of scraping and cracking of the crystals differs depending on the position of the outer peripheral portion of the wafer. As such, a fine processing technique is required, such as by changing the processing conditions according to the position of the outer periphery of the wafer. The crystallographic planes of β-Ga<sub>2</sub>O<sub>3</sub> substrates commercially available at present are the (100), (010), and (001) because epitaxial layers with good crystalline quality can be grown on these planes. Other intrinsic material properties of interest are transport (which is thought to be isotropic), thermal conductivity, and field strength (which is thought to be anisotropic). Manufactures have chosen to prioritize yield and growth quality when producing wafers, although other orientations may be of interest. Process optimization should be done in different ways appropriate for each plane. It is also necessary to take measures to reduce the amount of scraping in the polishing process. The related steps are the slicing step, grinding step, polishing step, and Chemical Mechanical Polishing (CMP) step, but in each step, it is necessary to remove a region thicker than the damaged layer generated in the previous step. To reduce the total amount of scraping as much as possible, a processing method that causes less damage has to be developed. To date, a detailed methodology above has not been published. Optimization of this process may have significant impact on the future of  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> manufacturing cost.

#### 2. Epitaxial wafers

HVPE or MOCVD is a candidate of the epitaxial growth method for vertical power devices that require a thick film, while MOCVD or MBE is a candidate for lateral power devices that require a film with a flat surface. Regardless of which epitaxial growth method is chosen, the cost challenge is the same, which is to increase the number of wafers to be manufactured per unit equipment per unit time.

One solution is to use multi-wafer equipment. However, at present, there is no multi-wafer equipment capable of mass production in HVPE or MOCVD. It is expected that with increased investment into the technology, multi-wafer equipment will be offered by tool manufacturers. The current HVPE apparatus has a hot-walltype configuration with a reactor made of quartz, since GaCl is used as a raw material. The reactor made of quartz makes it difficult to build large, reproducible manufacturing equipment. In particular, the gas flow changes because of the low dimensional accuracy of the quartz parts. If the HVPE method is to be used in the future, a mass production furnace with high dimensional accuracy has to be developed. HVPE systems have not been commercially available but have been originally designed. We are planning to develop an advanced HVPE system to increase the production volume. The system will be developed by 2023 which will produce  $7 \times 150 \text{ mm}^2$  epitaxial wafers per run. On the other hand, the barrier to realizing multiple-wafer growth in MOCVD is low because it usually uses a stainless-steel

reactor. However, the MOCVD has another problem: the Ga metal organic raw material it uses is expensive.

Another solution is to increase the rate of epitaxial growth. The current growth rate is about 10  $\mu$ m/h in the HVPE method and about 1  $\mu$ m/h in the MOCVD method (while maintaining high mobility). The HVPE method is desired to be several times faster, whereas MOCVD is desired to be one order of magnitude faster. In addition, countermeasures to shorten the interval between growths, such as by using a maintenance-free furnace or high-temperature transportation system, would affect a cost reduction.

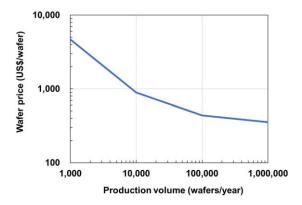

Figure 7 shows the expected  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> wafer price against production volume. The values were calculated by considering the progress level of  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> crystal growth and epi-film formation technology which will be available in 2027 for 150 mm wafer size. The  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> wafer price is anticipated to decrease drastically with increasing production volume due to several factors as explained earlier in this section. These low-priced wafers will offer substantial cost-competitive merits in the discrete market sector.

#### C. Concluding remarks

In this chapter, we described the technical challenges to reducing the wafer price of  $\beta$ -Ga<sub>2</sub>O<sub>3</sub>. If the challenges described here can be resolved and the number of wafers manufactured increased to mass production scale through commercialization of β-Ga<sub>2</sub>O<sub>3</sub> power devices, the price of β-Ga<sub>2</sub>O<sub>3</sub> epitaxial wafers may be reduced to less than one-third those of SiC epitaxial wafers. If devices with low electrical resistance and low thermal resistance per unit area are developed owing to advances in device design and fabrication technology, the device price per unit current is presumed to fall even further. If they are achieved, it is expected that the manufacturing of β-Ga<sub>2</sub>O<sub>3</sub> power devices will proceed and capture a large market, especially in the high voltage and high current applications. Performance at a cost reduction is quite possibly the most attractive trait of \(\beta\)-Ga2O3 due to the rampant competition in the semiconductor sector. Although continuous improvement of SiC material quality and scaling in wafer size up to 150 mm have resulted in low-cost substrates, the  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> substrate quality has also been improving in line with expanding in diameter at a rate more than twice of SiC since 2004. With time, 150 and 200 mm β-Ga<sub>2</sub>O<sub>3</sub> wafers are expected to be commonplace which will offer significant

**FIG. 7.** Expected  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> wafer price in 2027 as a function of production volume.

cost competitive advantages for vertical FETs and Schottky barrier diodes (SBDs).

#### V. BULK GROWTH

#### **John Blevins**

In this section, we examine the techniques used for growth of bulk  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> single crystals. Gallium oxide is known to form five crystalline polymorphs. The  $\beta$  phase is the only stable polymorph at growth temperatures above 1800 °C and 1 atm pressure. The application of melt-based growth techniques provides significant manufacturing, cost, and scalability advantages compared to vapor transport processes used for other wide bandgap single crystals, such as SiC, GaN, and AlN. \(\beta\)-Ga2O3 is the only wide bandgap semiconductor capable of crystallization from a melt utilizing industrial scale manufacturing techniques, such as Vertical Bridgman (VB),<sup>34</sup> Czochralski (CZ),35 Edge-Defined Film-fed Growth (EFG),36 and Float Zone (FZ).<sup>37</sup> The majority of  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> bulk growth research and development to date has focused on the CZ and EFG techniques. Presently, Novel Crystal Technology (NCT, Japan) is the only commercial provider of bulk β-Ga<sub>2</sub>O<sub>3</sub> substrates utilizing the EFG technique. High quality β-Ga<sub>2</sub>O<sub>3</sub> substrates of differing orientations and doping are commercially available in sizes ranging from  $25 \times 25 \text{ mm}^2$  for (010) and 100-mm for (201).<sup>26</sup> Kuramata et al. showed the growth of (201) oriented crystals up to 150-mm by the EFG method.<sup>38</sup> The Leibniz Institute for Crystal Growth (IKZ Germany) is a leading research institute for CZ β-Ga<sub>2</sub>O<sub>3</sub>, having made numerous contributions to understanding the scalability of β-Ga<sub>2</sub>O<sub>3</sub> single crystals.<sup>33</sup> Their research clearly demonstrated the necessity of increasing the O2 concentration in the growth atmosphere with increased crystal diameter. IKZ has grown 50-mm diameter single crystals exceeding 50-mm in length weighing up to 1 kg and are the largest grown by any method. In the U.S., Northrop-Grumman SYNOPTICS has been developing both 25 and 50 mm semi-insulating (010) CZ β-Ga<sub>2</sub>O<sub>3</sub> substrates (Fig. 8) that have recently become commercially available. Typical x-ray rocking curves are <75 arc sec with surface roughness <1 nm. The prospect for growing large diameter, low cost β-Ga<sub>2</sub>O<sub>3</sub> bulk crystals provides an added incentive for development of this promising next generation semiconductor material.

**FIG. 8.** SYNOPTICS 50 mm (010) Fe-doped  $\beta$ -Ga $_2$ O $_3$  as-grown boule and 50 mm substrate

#### A. Key challenges

Impressive device results and early demonstration of large diameter single crystals has stimulated interest in this promising next generation semiconductor. The maturation of any semiconductor device technology can be accelerated by the availability and/or promise of large diameter, high quality, and low-cost native substrates. Wide bandgap semiconductors, namely, SiC, faced significant commercialization challenges due to monumental sublimation growth technology barriers. It took Cree (Wolfspeed) 20 years from the company founding to the commercial release of 100 mm substrates. Approximately 16 years transpired between the commercial availability of 25 and 100 mm SiC substrates. 43 Today, 100 and 150 mm SiC substrates are manufactured at a cost, quantity, and quality never thought possible. The wide bandgap semiconductor manufacturing infrastructure has evolved such that a minimum of 100 mm diameter substrates will be required to access large scale, compound semiconductor manufacturing facilities. A 2019 National Renewable Energy Laboratory (NREL) study estimated a  $3 \times$  cost advantage of  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> compared to SiC substrates leading to 2× lower cost power electronic devices. 44 This study alluded to the relative ease of scaling and potential for low-cost manufacturing of β-Ga<sub>2</sub>O<sub>3</sub> substrates, providing a solid foundation for rapid commercialization. Despite rapid progress with CZ and EFG growth process development, it should be recognized that specific "bulk" material requirements remain largely undefined beyond a preference for Ntype or semi-insulating. Significant work remains with epitaxial and device process development before bulk crystalline requirements, such as dopant, defect density, and resistivity, are clearly understood. Semiconductor manufactures tend to be growth technology agnostic rather focusing on a combination of technical, manufacturing, and cost factors for selecting a substrate.

Fabrication and polishing of  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> merits discussion. Processing of boules and ribbons present differing challenges. The presence of two strong cleavage planes parallel to the (100) and (001) planes complicate boule fabrication and polishing. These crystal planes are highly susceptible to mechanical stress and can easily form cleaves and/or crack during fabrication (coring, grinding, and wire sawing) and polishing. EFG ribbons are typically not subjected to these mechanical processes. As such, fabricating substrates from ribbons are less susceptible to damage. However, ribbons are not the preferred method of manufacturing semiconductor substrates.

Regardless of the crystal growth technique utilized, standards for substrate parameters, such as flats, orientation, thickness, flatness, surface roughness, total thickness variation, and associated tolerances, will be required. Additionally, electrical (resistivity, doping levels) and crystalline (dislocation density and x-ray rocking curves) requirements will evolve as the device fabrication process matures. Substrates that are round and flat (bow/warp <20  $\mu$ m) with FWHM <50 arc sec and "epi-ready" surfaces should be the immediate focus of the industry. Near term availability of 50 mm substrates will broaden research and development interest, but production will likely demand 100 mm or larger substrates. Both CZ and EFG appear to be well positioned to address near term substrate requirements. Regardless of the advantages melt-based crystal growth processes provide, bulk growth of  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> is not without significant technical hurdles which are further highlighted below.

#### 1. Czochralski (CZ)

Czochralski (CZ) is the de facto standard method for manufacturing a variety of large diameter single crystal boules, such as silicon, sapphire, germanium, and gallium arsenide. CZ's primary attributes are its scalability, manufacturability, and low cost. Due to the high growth temperature (>1800 °C) of β-Ga<sub>2</sub>O<sub>3</sub>, crucible options are presently limited to iridium due to the high growth temperature and oxidizing environment. The use of iridium introduces significant cost and manufacturing challenges due to susceptibility to oxidation in atmospheres of only a few percent oxygen and decomposition of the melt forming metallic gallium further reacting with the iridium crucible forming eutectic or intermetallic phases.<sup>40</sup> Increasing the oxygen partial pressure can suppress the decomposition of the melt but will subject the iridium crucible to further oxidation. Galazka et al. showed that undoped layers have been shown to be insulating scale-up of  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> crystal size is strongly affected by the formation of metallic gallium in the melt and that scale-up to 100 mm diameter crystals may require oxygen containing atmosphere up to 100%.33 SYNOPTICS has shown that an atmosphere of 91% CO<sub>2</sub> and 9% O<sub>2</sub> is sufficient for growth of (010) Fe-doped single crystals up to 60 mm in diameter, but crucible lifetime remains an ongoing concern.<sup>28</sup>

- a. Current/future challenges.

- Management of growth atmosphere and melt decomposition.

- Iridium crucible cost and maintainability.

- Diameter scalability to 100 mm and larger.

- Defect identification and mitigation.

- Uniform dimensional, crystalline and electrical parameters.

- Boule and substrate yield.

#### 2. Edge defined film fed growth (EFG)

Edge Defined Film Fed Growth (EFG) was originally developed by LaBelle and Mylavski for growth of sapphire ribbons. EFG remains the technology of choice for growth of large sapphire windows and complex geometries. It is not the preferred approach for large scale manufacturing of semiconductor substrates. EFG's primary attributes are its high growth rates exceeding 10 mm/h, scalability, and manufacturability of large single or multiple ribbons. Iridium crucibles are still required but are less susceptible to oxidation and melt volatilization due to the reduced area of the exposed melt surface. NCT has successfully commercialized EFG for a variety of sizes, orientations, and dopants and demonstrated scalability of (201) substrates up to 150 mm.<sup>38</sup>

- a. Current/future challenges.

- Scalability of (010) oriented substrates beyond 25 mm.

- Manufacturing throughput and cost.

- Defect mitigation.

- Uniform dimensional, crystalline, and electrical parameters.

#### 3. Float zone

a. Optical floating zone (OFZ). The float zone method is a melt-based technique most commonly used to manufacture high resistivity silicon single crystals up to 200 mm diameter. The OFZ

method is a variation of the float zone method used to grow  $\beta$ -Ga<sub>2</sub>O<sub>3</sub>. Single crystals of  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> are grown without a crucible, enabling the use of high oxygen atmosphere. A uniform polycrystalline rod is required and is readily available for silicon but not for  $\beta$ -Ga<sub>2</sub>O<sub>3</sub>. High purity  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> powders must be combined with preferred dopant and compacted and sintered to form a suitable rod. The use of an RF heat source is not an option due to the low conductivity of  $\beta$ -Ga<sub>2</sub>O<sub>3</sub>. Rather halogen lamps provide the heat source. Víllora *et al.* was the first to demonstrate growth of 25 mm in diameter crystals with three differing crystallographic orientations: (100), (010), and (001).<sup>37</sup>  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> single crystals were grown in the [010] direction at a growth rate of 6 mm/h. The OFZ method is not easily scalable beyond 25 mm and as such is not competitive with other melt-based techniques.

#### b. Current/future challenges.

- Diameter scaling severely limited by halogen lamp heat source.

- Doping techniques.

- Industrial research and development commitment.

- Defect identification and mitigation.

- Uniform dimensional, crystalline and electrical parameters.

#### 4. Vertical Bridgman

Vertical Bridgman and/or its variants (vertical gradient freeze) are common techniques used in manufacturing III-V single crystals up to 150 mm in diameter. This technique involves the directional solidification of the melt from the hot zone to the cold zone by controlling the movement of the crucible or hot zone. Single crystals can be grown with or without seed utilizing a Pt-Rh alloy crucible, enabling the use of high oxygen atmosphere without risk of crucible oxidation. Diameter control is unnecessary because the diameter is determined by the inner diameter of the crucible. The first application of the vertical Bridgman (VB) method to β-Ga<sub>2</sub>O<sub>3</sub> was demonstrated by Hoshikawa et al., and they reported growth of 25 mm diameter (100) single crystals without a seed in ambient air, with no adhesion of the crystals to the crucible wall.<sup>34</sup> Recent efforts demonstrated 50 mm diameter Sn-doped β-Ga<sub>2</sub>O<sub>3</sub> crystals with growth orientation perpendicular to the (001) plane utilizing a resistance heating furnace with platinum-rhodium alloy crucibles in ambient air.25

#### a. Current/future challenges.

- Scalability of the growth process.

- Industrial research and development commitment.

- Use of a Pt–Rh alloy crucible.

- Defect identification and mitigation.

- Uniform dimensional, crystalline and electrical parameters.

#### B. Conclusion

$\beta$ -Ga<sub>2</sub>O<sub>3</sub> is a novel ultra-wide bandgap semiconductor that combines high theoretical figure of merits with growth of single crystals with proven manufacturing techniques such as CZ and EFG. While a variety of growth techniques have been utilized to grow  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> single crystals, it is too early in the development cycle to suggest that one technique is superior to competing approaches.

Until such a time that a volume application emerges, it is conceivable for multiple techniques to co-exist. Generally speaking, near term (1–3 years) availability of 50 mm  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> substrates with desired surface orientation, N<sup>+</sup> or semi-insulating (>10<sup>8</sup>  $\Omega$  cm), good crystallinity (FWHM <50 arc sec), and low defect density (<10<sup>4</sup> cm<sup>-2</sup>) should be a goal for the industry going forward. The availability of such substrates should sustain development for several years to follow. Ultimately, a minimum of 100 mm will be required for access and subsequent transition to commercial compound semiconductor foundries. Presently, both CZ and EFG techniques appear to be best positioned to address near term substrate requirements. The extent of research and development of these techniques exceeds other approaches. EFG substrates produced by NCT have been commercially available for several years. CZ substrates from SYNOPTICS have become commercially available in 2021. EFG is not the preferred approach for semiconductor substrate manufacturing, but it could address  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> requirements for non-(010) oriented substrates. CZ has a long history of scalability and low-cost manufacturing; there will always be a preference for CZ. However, CZ faces unique challenges not faced with other techniques. Galazka et al. showed that CZ scalability will be dictated by the ability to control the growth environment such that melt decomposition and crucible oxidation are mitigated, enabling a cost-effective manufacturing process. The recent market spike in iridium prices could impact development and manufacturing. Vertical Bridgman remains an attractive approach notwithstanding the lack of a stronger industrial developmental commitment as well as addressing the added cost Pt-Rh alloy crucibles. The commercial availability of native larger diameter β-Ga<sub>2</sub>O<sub>3</sub> substrates are critical to the long-term development of this novel ultra-wide bandgap semiconductor technology.

#### VI. MOLECULAR BEAM EPITAXY

#### Oliver Bierwagen

#### A. Status

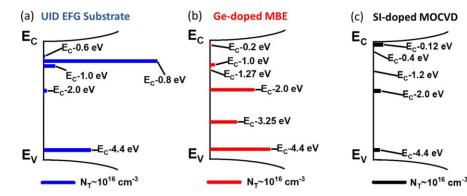

Close to a decade ago, the research field of β-Ga<sub>2</sub>O<sub>3</sub>-based power electronics got started by the seminal work of Higashiwaki et al., 27 describing the theoretical potential of  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> coupled with the demonstration of a MESFET device with high breakdown voltage. This demonstrator device was based on a homoepitaxial, Sn-doped layer grown by molecular beam epitaxy (MBE) on a (010)-oriented, semi-insulating, Fe-doped β-Ga<sub>2</sub>O<sub>3</sub> substrate. It has to be stressed that the availability of the  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> substrate from bulk growth enables the homoepitaxial growth of functional layers by MBE and other film growth techniques with highest structural quality. Living up to its pioneering role by realizing high quality layers with simpler growth chemistry than metal organic vapor phase epitaxy (MOVPE)/MOCVD, the MBE growth of  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> has evolved rapidly in the past years: homoepitaxy has been demonstrated with growth rates up to few nm/min on the available orientations [(100), (010), (001), and (201)]. 45,46 Undoped layers have been shown to be insulating,<sup>47</sup> and the n-type conductivity has been controlled by donor doping with Sn, 31,48 Ge,49 and Si<sup>50</sup> up

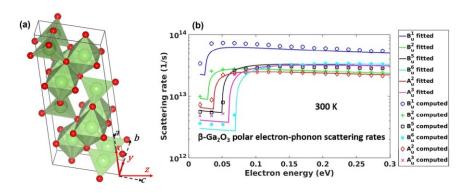

to electron concentrations of  $10^{20}$  cm<sup>-3</sup>. Widening the bandgap<sup>51</sup> by alloying with Al<sub>2</sub>O<sub>3</sub><sup>52</sup> enabled the MBE-growth of modulation-doped (Al,Ga)<sub>2</sub>O<sub>3</sub>/Ga<sub>2</sub>O<sub>3</sub> single<sup>53</sup> and double<sup>54</sup> heterostructures that confine a two-dimensional electron gas (2DEG). With average breakdown fields of ~3 MV/cm, these high-electron-mobility transistor (HEMT) structures are promising candidates for high frequency and high-power device applications.

Despite these advances, a number of challenges need to be addressed for MBE-grown layers to be used in competitive power electronics devices. Some of these challenges are specific to MBE, whereas others are universally observed.

#### B. Current and future challenges