# Analysis of Hybrid Modular Multilevel Rectifier Operated at Non-Unity Power Factor for HVDC Applications

Jian Liu, *Student Member, IEEE*, Di Zhang, *Senior Member, IEEE*, and Dong Dong, *Senior Member, IEEE*

**Abstract-** Hybrid modular multilevel converter (HMMR) is a type of unidirectional modular voltage source converter (VSC) that has been proposed for high-voltage (HV) dc transmission applications. Compared to the modular multilevel converter (MMC), up to 50% of the submodules (SMs) and capacitors can be replaced by the simple HV line-frequency diode stacks. Non-unity power factor operation is favored for rectifier station to support the grid, but additional SM mitigates the benefit of HMMR. Therefore, this paper proposes two new current commutation methods for HMMR to reduce the required SM number at non-unity power factor. It can be further reduced by the use of third harmonic injection. In addition, an average model is given to reveal the inherent power flow relationship of HMMR. It is found that part of active power is delivered from ac to dc side through diode directly, which reduces the energy storage requirement. The performance of HMMR is evaluated and compared with MMC under variable power factor conditions. The feasibility of the proposed converter is verified by the simulation results of a 200 kV HVDC model. Finally, a scale-down HMMR experiment prototype is developed to validate its effectiveness, operating principles, and control scheme.

**Index Terms-** Hybrid modular multilevel rectifier (HMMR), HVdc system, non-unity power factor, current commutation, power flow.

## I. INTRODUCTION

Modular Multilevel Converter (MMC) has emerged as one of the most attractive topologies for the medium-voltage (MV) and high-voltage direct current (HVDC) applications due to its flexibility, modular structure, excellent power quality and fault tolerant operation capability [1-3]. However, MMC based HVDC (MMC-HVDC) systems still confront some limitations. First, the number of IGBTs is doubled with the half-bridge (HB) submodule (SM) and quadrupled with full-bridge (FB) SM compared with the classic two-level voltage source converter (VSC). The use of low-voltage rating IGBTs in SM results in higher conduction losses. Second, the SM capacitors occupy more than 50% of the weight and size of MMC [4], hence resulting in the bulky volume and higher construction cost. This also hinders MMC for the weight or space sensitive applications, such as the offshore wind power platform.

Compared to the MMC-HVDC, line-commutated converter based HVDC system (LCC-HVDC) reduces the cost, volume and power conversion losses [5]. Nevertheless, LCC-HVDC also suffers from some critical

drawbacks, including the large reactive power consumption, large amount of harmonic currents and limited voltage regulation range [6], [7]. The commutation process involves interactions with the grid, leading to the commutation failure or reduced power capacity under a weak-grid condition.

Given that the power flow of MV/HV DC power delivery systems is often unidirectional, the diode rectifier based HVDC (DR-HVDC) systems have recently received notable interest [8-10]. By replacing the MMC rectifier station with DR, the volume, weight and cost could be decreased significantly. For example, a technical feasibility study on the use of DR for the connection of offshore wind power plants was presented in [11]. Besides, the DR based low frequency ac transmission (LFAC) has been proposed in [12], which gives a competitive solution for offshore wind farm integration. Notwithstanding the advantages of smaller size and lower cost, the passive device used in DR brings some limitations as well. First, DR cannot provide reactive power, so the reactive power of the ac grid connected to DR must be compensated by other equipment. Second, DR will inject harmonic currents into the ac system, implying the need for active compensation or bulky passive filters. Third, the ac voltage magnitude has to vary in order to regulate the active power transmission.

In order to address these issues, various hybrid topologies have been proposed. In [13] a hybrid converter composed with DRs and a series connected two level VSC was proposed. The VSC can compensate the reactive power and harmonics generated by the DR. Reference [14] proposed to connect a MMC in parallel with LCC or diode rectifier (DR) on ac sides to optimize the power distribution between two HVDC links. However, the parallel connection needs the VSC to tolerate full nominal HVDC voltage and additional full-rating ac transformer with tertiary windings. In [15], a HV cascaded FB branch are connected to the MMC dc side to reduce MMC SM number. But a large LC filter is required to constrain the high-frequency circulating current. In [16], a low power FB-MMC is connected in series with DR on dc side, while their ac sides are in parallel through transformer. The FB-MMC can control the dc voltage and regulate partial power. However, the FB-MMC may work as inverter mode to

control DR power and this circulating power will reduce the efficiency.

Different from the combination of converter level MMC and DR, another type of hybrid MMC structure is derived from device level. Various “hybrid multilevel converters” have evolved recently [17], which are created with the concept of combining the thyristors (or series-connected IGBTs) and chain-links (CLs). A groups of converters, including alternate arm converter (AAC) [18-20], parallel hybrid converter (PHC) [21], [22], series bridge converter (SBC) [23] have been proposed. They can address one or more issues of MMC. But the series connected active device is still quite challenging. Therefore, [24] proposed a hybrid modular multilevel rectifier (HMMR), which replaces the HV insulated-gate bipolar transistor (IGBT) stack in hybrid MMC [25-27] with series diode. In this way, the key benefits of MMC are kept, and the SM number could be reduced at the same time. Particularly at unity power factor (PF), HMMR can reduce the SM numbers by 50% due to the utilization of HV diode. Thus, both the volume and construction cost could be reduced substantially compared with MMC.

Non-unity power factor operation is also important for rectifier station in HVdc system to support the grid. To realize the current commutation during the leading or lagging time of ac current, some additional FB SMs should be added [24]. As an extension, the main contribution of this paper is:

1) A new current commutation method is proposed to operate HMMR at non-unity PF. This method requires only HB SM and possesses better modularity.

2) The third harmonic is injected to help reduce the FB number used in [24]. And the analysis of two methods covers the cases of leading and lagging PF.

3) The average model is established to reveal the inherent power flow relationship between ac and dc sides. It is found HMMR has a lower capacitance requirement because partial active power is delivered from ac to dc side through the diode directly.

4) The performance is evaluated and compared between traditional MMC and HMMR with two methods, in terms of device number, arm capacitance as well as semiconductor losses.

This paper is organized as follows. The non-unity PF operation of HMMR with two methods are proposed in Section II. The average model is also given to understand power low in HMMR. In Section III, the performance is compared between the traditional HB MMC and HMMR at different PF. The control strategy and simulation results are assessed in Section IV, and the experimental results of a scale down prototype are provided to validate proposed method in Section V. Finally, Section VI draws conclusions.

## II. SYSTEM OVERVIEW AND OPERATION PRINCIPLE

### A. System Topology

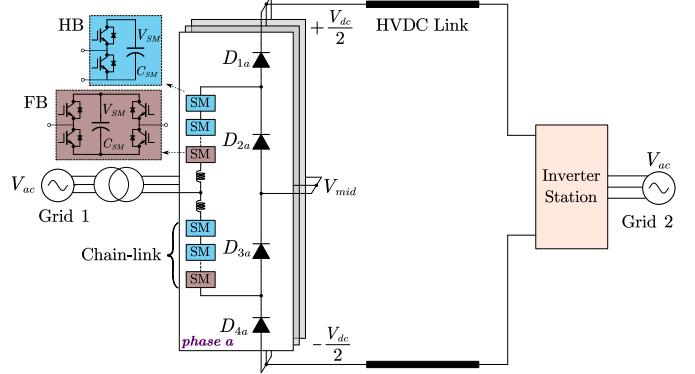

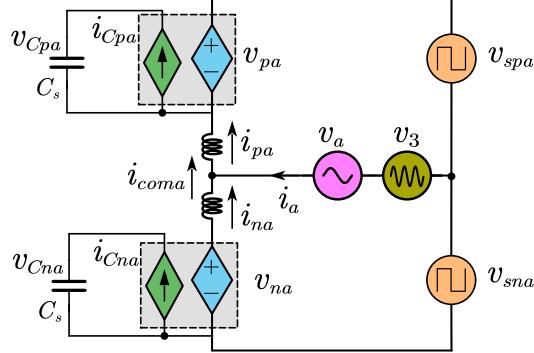

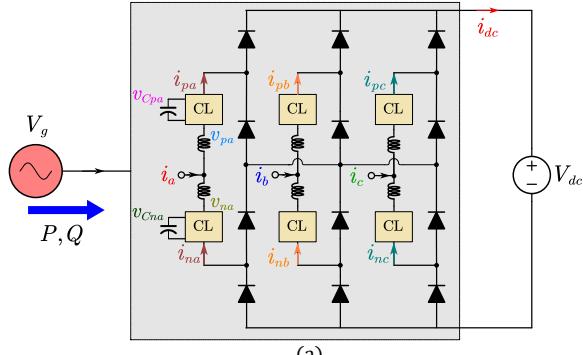

Fig. 1 depicts the topology of three-phase HMMR derived from [24]. Each phase-leg consists of the upper and lower CLs, which are connected between four HV diode stacks ( $D_1 - D_4$ ). The midpoints of three-phase diode stacks are connected together, thereby providing a freedom to reshape the CL voltage. In this type of HMMR, each CL contains  $N$  series SMs, including  $N_h$  HB SMs and  $N_f$  FB SMs. Each of them has a floating capacitor  $C_{sm}$  at the voltage of  $V_{sm}$ .

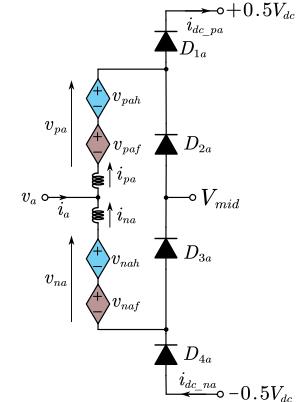

For the sake of simplicity, one phase (phase  $a$ ) is used as an example for illustration. Fig. 2 shows the simplified model of HMMR, where the cascaded HB and FB SMs in each arm

Fig.1 Structure of HMMR.

Fig.2 Single phase simplified model of HMMR.

can be regarded as the controlled voltage sources.  $V_{dc}$  and  $V_a$  are the rated dc-side and ac-side voltages, respectively.  $V_{mid}$  is the midpoint voltage, which should be controlled to be zero.  $v_{pah}$ ,  $v_{paf}$ ,  $v_{nah}$  and  $v_{naf}$  represent the voltages modulated by the HB and FB SMs in the upper and lower CLs, respectively. Their sum voltages are denoted as  $v_{pa}$  and  $v_{na}$ . While  $i_{pa}$  and  $i_{na}$  are referred to the corresponding CL currents, respectively.

The ac side variables are defined as,

$$v_a = V_{ac} \sin(\omega t - \varphi), \quad i_a = I_{ac} \sin(\omega t) \quad (1)$$

where  $V_{ac}$  and  $I_{ac}$  represent the amplitude of ac voltage and current, respectively. The angular frequency is denoted as  $\omega$ , whereas the phase angle difference between current and voltage is given by  $\varphi$ , which determines the PF.

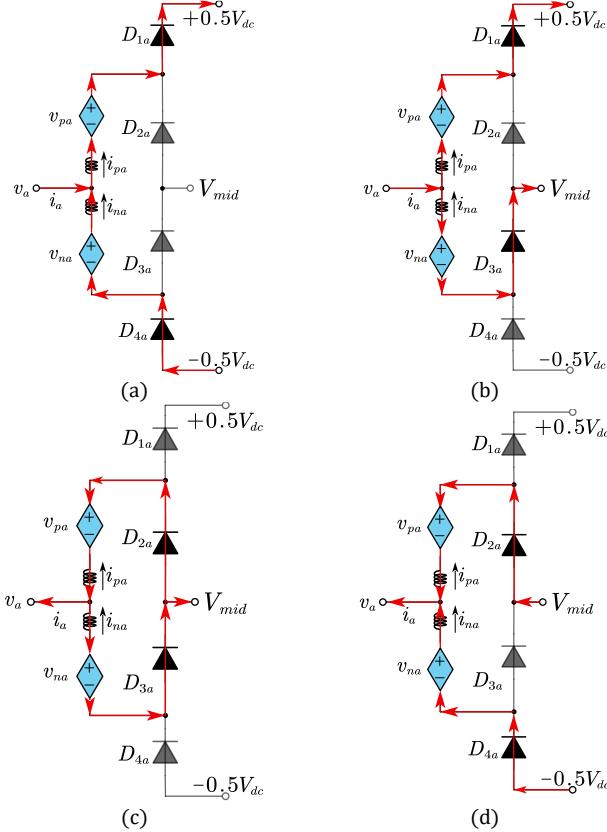

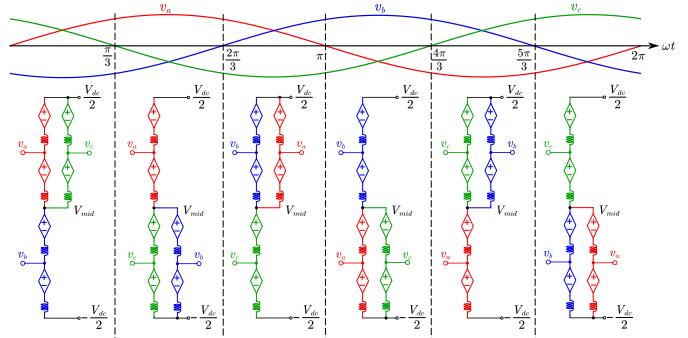

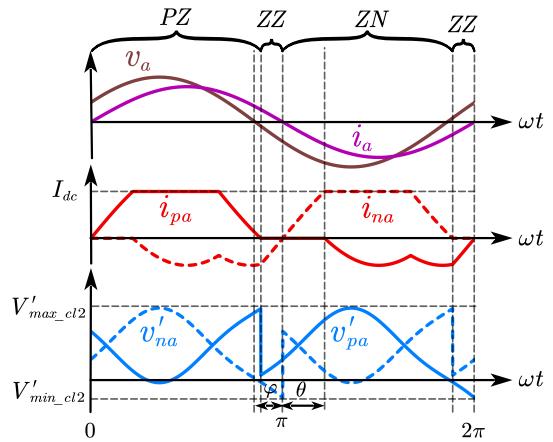

Since diode is a passive device, the polarity of  $i_{pa}$  directly determines whether  $D_{1a}$  or  $D_{2a}$  is turned on. Similarly, the polarity of  $i_{na}$  determines the conduction of  $D_{3a}$  or  $D_{4a}$ . As a result, there are four working states and connection methods for the single-phase HMMR: *PN* (positive-negative), *PZ* (positive-zero), *ZZ* (zero-zero), *ZN* (zero-negative) states as shown in Fig. 3. Accordingly, the upper and lower CL voltages could be calculated as below if neglecting the inductor voltage,

$$\begin{aligned} v_{pa}^* &= 0.5V_{dc} - v_a, \quad v_{na}^* = 0.5V_{dc} + v_a \quad (i_{pa} > 0, i_{na} > 0, PN) \\ v_{pa}^* &= 0.5V_{dc} - v_a, \quad v_{na}^* = v_a - V_{mid} \quad (i_{pa} > 0, i_{na} < 0, PZ) \\ v_{pa}^* &= V_{mid} - v_a, \quad v_{na}^* = v_a - V_{mid} \quad (i_{pa} < 0, i_{na} < 0, ZZ) \\ v_{pa}^* &= V_{mid} - v_a, \quad v_{na}^* = 0.5V_{dc} + v_a \quad (i_{pa} < 0, i_{na} > 0, ZN) \end{aligned} \quad (2)$$

Fig. 3 Four working states of single phase HMMR, (a) *PN* state, (b) *PZ* state, (c) *ZZ* state, (d) *ZN* state.

Fig. 4 Sing-phase CL current and voltage waveforms at unity PF.

But regardless the working state, there is always a constraint for two CL currents in (3).

$$i_a = i_{pa} - i_{na} \quad (3)$$

### B. Three-phase configuration and Current Distribution

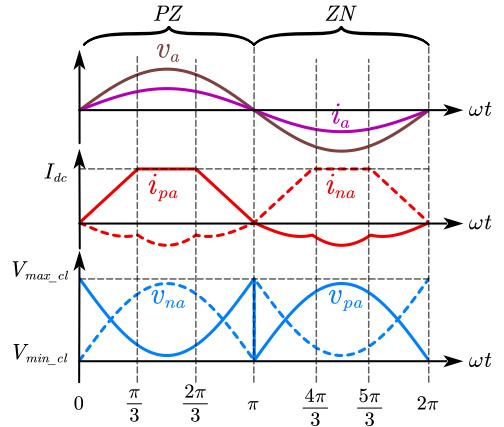

The original unity PF operation has already been discussed in [24]. The trapezoidal current allocation method as shown in Fig. 4 can switch the CL current polarity and working state naturally at the ac voltage zero-crossing point. Besides, the rotation between the *PZ* and *ZN* states can help achieve a minimum CL voltage stress and reduce 50% of SM number compared to the traditional HB-MMC of same voltage rating.

Fig. 5 Three-phase configuration of HMMR at unity PF.

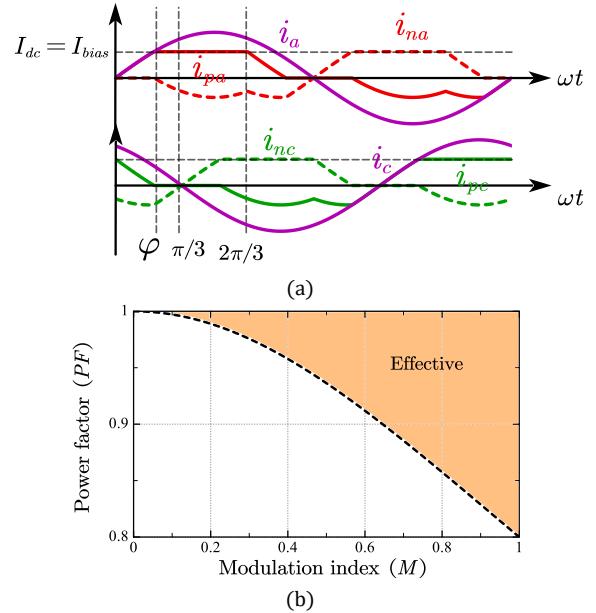

Furthermore, it can be proven that this scheme is feasible at any modulation index  $M$ . Taking the positive half cycle  $\omega t$  (0,  $\pi$ ) as an example,  $i_{pa} > 0$  and  $i_{na} < 0$  should be met to operate in *PZ* state. Since  $i_{pa}$  is trapezoidal, and  $i_{na}$  is the subtraction of ac sinusoidal wave from  $i_{pa}$ . As long as value of  $i_{na}$  at  $\pi/3$  or  $2\pi/3$  is negative as in (4), it will be negative during whole (0,  $\pi$ ).

$$I_{dc} - I_{ac} \sin(\omega t) < 0, \quad \omega t = \pi/3 \quad (4)$$

If  $M$  is defined as  $M = 2V_{ac}/V_{dc}$ , the input and output current relationship should be,

$$\left. \begin{aligned} V_{dc} I_{dc} &= 3 \cdot \frac{V_{ac} I_{ac} \cos \varphi}{2} \\ I_{dc} &< \frac{\sqrt{3}}{2} I_{ac} \end{aligned} \right\} \Rightarrow M < \frac{2}{\sqrt{3}} \cos \varphi \quad (5)$$

Since the maximum  $M$  is 1.15 with the third harmonic injection, (4) and (5) always hold at unity PF.

Considering the symmetry of three-phase structure, the working states of other two phases can be derived by considering the  $2\pi/3$  shift of CL currents. In this way, the three-phase connection of HMMR during one-line cycle could be divided into six segments and depicted in Fig. 5. It can be observed that during each segment, two phases are connected in parallel to the positive (or negative) terminal to share the dc bus current. And the third phase is connected to another terminal and needs to support the whole dc current. Therefore, the trapezoidal current allocation can keep the dc bus current constant during the overlap period of two phases parallel connection.

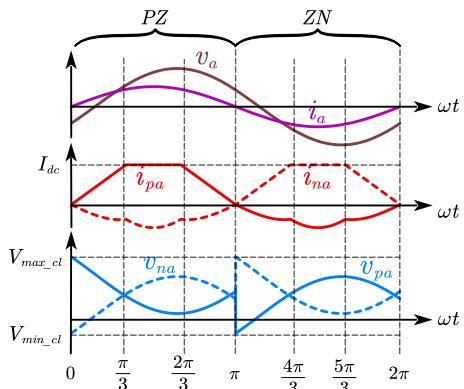

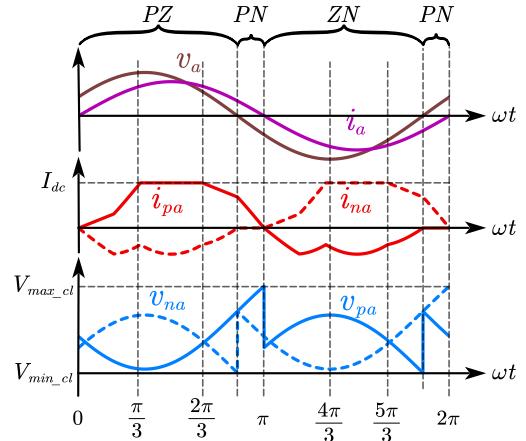

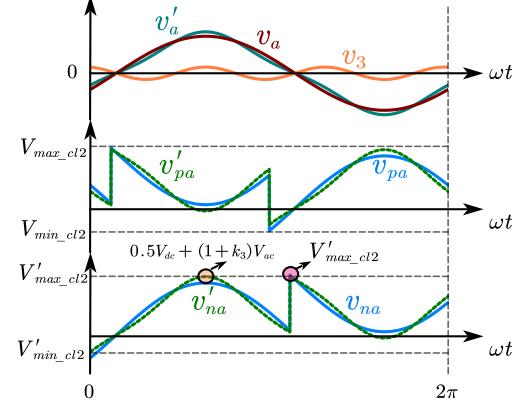

Besides the unity PF operation, non-unity PF operation is also important for the rectifier in applications like HVDC to deliver some amount of reactive power and support the grid during the low-voltage transient and weak grid conditions. As shown in Fig. 6, the intuitive way is to keep the same trapezoidal current allocation aligning with the ac current, and change the CL voltages accordingly. This trapezoidal current is feasible as long as  $M$  and PF meet the condition of (5). As a result, the minimum and maximum CL voltage stresses will change to

$$\begin{aligned} V_{max\_cl} &= 0.5V_{dc} + V_{ac} \sin \varphi \\ V_{min\_cl} &= -V_{ac} \sin \varphi \end{aligned} \quad (6)$$

Fig. 6 Single-phase CL waveforms using previous method at leading PF.

Fig. 7 Single-phase CL waveforms using method 1 at leading PF.

Obviously, extra FB SMs must be inserted to generate the negative voltage, and the total number of required SM is,

$$N_{FB} = \frac{V_{ac} \sin \varphi}{V_{SM}}, \quad N_{HB} = \frac{0.5V_{dc}}{V_{SM}} \quad (7)$$

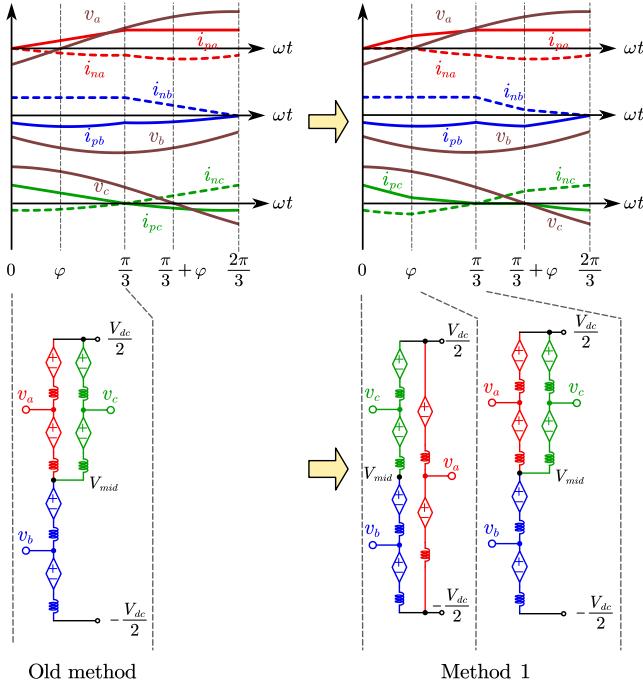

However, the additional FB SMs bring higher cost, volume as well as power losses, which mitigates the benefit of HMMR. In this regard, it is desired to find other solutions to reduce the SM requirement at non-unity PF operation. In fact, besides  $PZ$  and  $ZN$  states,  $PN$  and  $ZZ$  states could also be utilized for the current commutation during the leading or lagging time of ac current. They represent two methods proposed in this paper, and the detailed transient analysis and reduced CL voltage stress will be explained below.

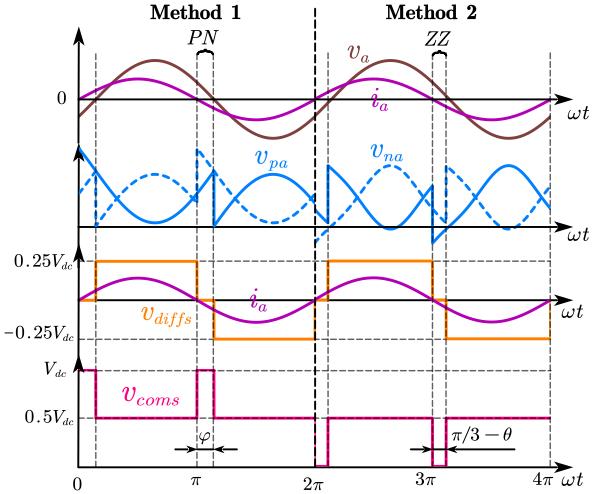

#### B. Method 1 of HMMR in Non-unity PF Operation

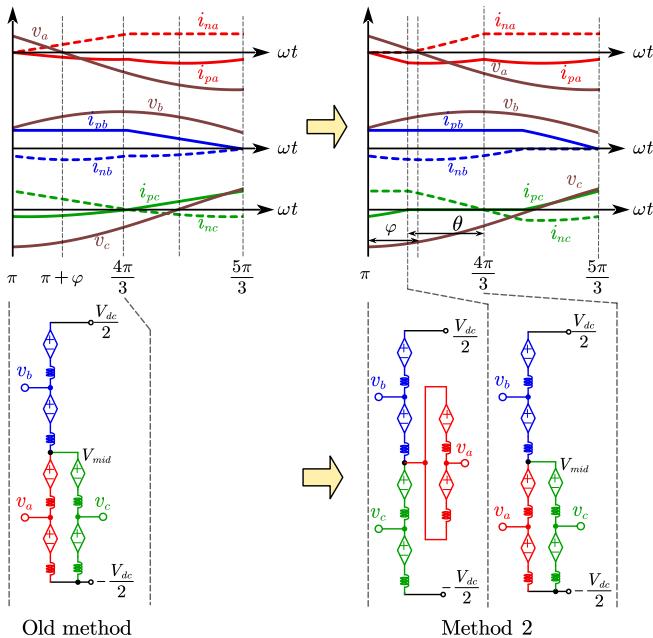

Method 1 employs the  $PN$  state to reduce the CL voltage stress. The single-phase CL waveforms at leading PF are presented in Fig. 7, and three-phase connection is shown in Fig. 8. Since six segments are symmetrical, two segments between  $(0, 2\pi/3)$  are taken for illustration. When  $\omega t$  is in the range of  $(0, \varphi)$ , the polarities of ac voltage and current are opposite. The CL currents are designed as below to make phase  $a$  work in  $PN$  state.

$$i_{pa} = i_a > 0, \quad i_{na} \approx 0, \quad \omega t \in (0, \varphi) \quad (8)$$

In this way, the minimum CL voltage is reduced to 0, leading to the employment of only HB SMs. And the CL voltage stresses of method 1 become,

$$V_{max\_cl1} = 0.5V_{dc} + V_{ac} \sin \varphi, \quad V_{min\_cl1} = 0 \quad (9)$$

Fig. 8 Three-phase CL waveforms and transition of method 1 at leading PF.

According to the three-phase connection in Fig. 8, both positive and negative dc bus currents are shared by two phases. Once phase  $a$  current is determined, the CL currents of phase  $b$  and  $c$  could be derived easily in (10) based on the ac current constraint.

$$\begin{cases} i_{pc} = i_{dc} - i_{pa}, i_{nc} = i_{pc} - i_c, \omega t \in (0, \varphi) \\ i_{nb} = i_{dc} + i_{na}, i_{pb} = i_{nb} + i_b \end{cases} \quad (10)$$

Then during  $(\varphi, \pi)$ , phase  $a$  switches to  $PZ$  state as shown in Fig. 7. Similarly,  $i_{pa}$  is designed as a plateau of  $I_{dc}$  between  $\pi/3$  and  $2\pi/3$ . Then a ramp current shape in (11) is designed for  $i_{pa}$  during the transition of  $(\varphi, \pi/3)$ .  $I_{bias}$  refers to the ending value of  $i_{pa}$  between  $(0, \varphi)$ , and is the initial value in next stage as well.

$$i_{pa} = \frac{(\omega t - \varphi)}{2\pi/3 - \varphi} \cdot (I_{dc} - I_{bias}) + I_{bias}, I_{bias} = I_{ac} \sin \varphi \quad (11)$$

$$i_{na} = i_{pa} - i_a, \omega t \in (\varphi, \pi/3)$$

The CL currents of phase  $b$  and  $c$  could be calculated accordingly. And a similar procedure is applied during  $(\pi/3, 2\pi/3)$  as shown in Fig. 8. However, it should be noted that the designed CL current of phase  $a$  does not always hold to meet the requirement of  $PZ$  state. When PF becomes larger,  $I_{bias}$  becomes closer to  $I_{dc}$ , and finally reaches the boundary as shown in Fig. 9 (a). When  $i_{pa}$  is larger than  $I_{dc}$ ,  $i_{pc}$  which equals  $I_{dc} - i_{pa}$ , will become negative and phase  $c$  enters  $ZZ$  state. This case should be avoided and poses the limitation of (12) for method 1.

$$I_{bias} = I_{ac} \sin \varphi < I_{dc} \quad (12)$$

Substituting (5) into (12) yields,

Fig. 9 (a) The boundary operation of method 1, (b) effective region for modulation index  $M$  and PF of method 1.

Fig. 10 Single-phase CL waveforms using method 1 at lagging PF.

$$\begin{aligned} \frac{3M \cos \varphi}{4} - \sin \varphi &> 0, \varphi > 0 \\ \Rightarrow \frac{3M \cdot PF}{4} - \sqrt{1 - PF^2} &> 0 \end{aligned} \quad (13)$$

Therefore, the possible region for method 1 could be plotted in Fig. 9(b). It can be seen that the PF range is  $[0.8, 1]$ , and the higher modulation index corresponds to larger PF range. As for the lagging PF, the  $PN$  state is also employed as shown in Fig. 10. Compared to the old method, method 1 uses only HB SM and behaves better in terms of the efficiency and modularity.

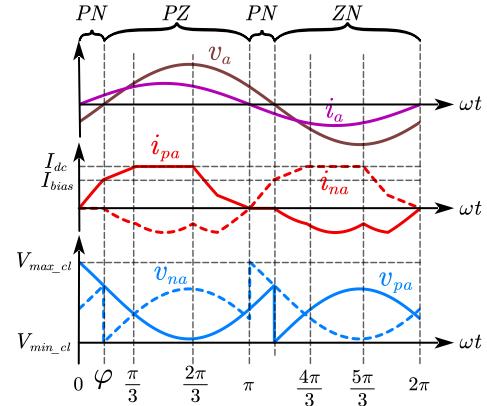

### C. Method 2 of HMMR in Non-unity PF Operation

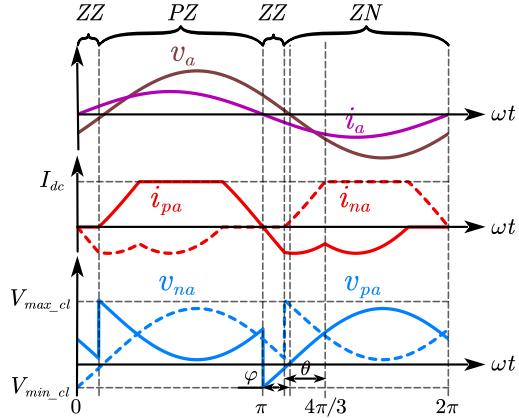

Different from method 1, method 2 utilizes the  $ZZ$  state to reshape the CL voltage. The single-phase CL waveforms of leading PF are presented in Fig. 11, and the three-phase connection is depicted in Fig. 12.

Similarly, two segments between  $(\pi, 5\pi/3)$  are taken as an example. When  $\omega t$  is in the range of  $(\pi, \pi+\varphi)$ , the polarities of

Fig. 11 Single-phase CL waveforms using method 2 at leading PF.

Fig. 12 Three-phase CL waveforms and transition of method 2 at leading PF.

ac voltage and current are opposite. Firstly, it is intended for phase  $a$  work to  $ZZ$  state during the whole range of  $(\pi, \pi+\varphi)$  as the designed current below.

$$i_{pa} = i_a < 0, i_{na} \approx 0, \omega t \in (\pi, \pi+\varphi) \quad (14)$$

According to the three-phase connection in Fig. 12, both positive and negative dc bus currents are supported by only single phase. Therefore, the CL currents of phase  $b$  and  $c$  could be derived easily in (15) based on the ac current constraint.

$$\begin{cases} i_{pb} = I_{dc} > 0, i_{nb} = I_{dc} - i_b < 0 \\ i_{nc} = I_{dc} > 0, i_{pc} = I_{dc} + i_c < 0 \end{cases} \quad (15)$$

$$\Rightarrow \pi/3 + \theta < \omega t < 4\pi/3 - \theta, \theta = \arcsin(I_{dc}/I_{ac})$$

Eq. (15) gives the second constraint for negative  $i_{pc}$  during  $ZZ$  state of phase  $a$  to be  $(\theta+\pi/3, 4\pi/3-\theta)$ . Once  $4\pi/3-\theta < \pi+\varphi$ , the  $ZZ$  state duration of phase  $a$  should be shortened to  $(\pi, 4\pi/3-\theta)$  to avoid the case of positive  $i_{pc}$ . Then during  $(4\pi/3-\theta, 2\pi)$ ,

Fig. 13 Method 2 CL voltage after injecting third-order harmonic.

Fig. 14 Single-phase CL waveforms using method 2 at lagging PF.

$4\pi/3)$ , phase  $a$  switches to the  $ZN$  state and parallels with phase  $c$  to share the dc current. A ramp current shape in (16) is designed for this transition.

$$i_{na} = \frac{\omega t - (4\pi/3 - \theta)}{\theta} \cdot I_{dc} > 0 \quad (16)$$

$$i_{pa} = i_{na} + i_a < 0, \omega t \in (4\pi/3 - \theta, 4\pi/3)$$

In this way, the CL voltage stress of method 2 becomes,

$$V_{max\_cl2} = 0.5V_{dc} + V_{ac}\sin(\gamma), \gamma = \theta + \varphi - \frac{\pi}{3} \quad (17)$$

$$V_{min\_cl2} = -V_{ac}\sin\varphi$$

where  $\gamma$  is the difference between  $\theta+\varphi$  and  $\pi/3$ . Furthermore, this CL voltage rating can be further reduced by injecting a specific third harmonic voltage  $v_3$ . Eq. (18) gives its expression, where the coefficient  $k_3$  represents its magnitude normalized to the ac voltage.

$$v_3 = k_3 \cdot V_{ac}\sin(3\omega t - 3\varphi) \quad (18)$$

$$v'_a = v_a - v_3$$

Subtracting the third-order voltage has flattened the region of the zero crossing of the new ac voltage  $v_a'$  and accentuated the peak voltage. This is the opposite effect with the normally used third harmonic injection to flatten the peak voltage. As shown in Fig. 13, this injection has the benefits of lowering the voltage rating of the CLs, thus reducing the number of

Fig. 15 Simplified average model of HMMR phase  $a$ .

TABLE I

Comparison of CL voltage stress with three methods

| Method   | Maximum CL stress                                               | Minimum CL stress                                  |

|----------|-----------------------------------------------------------------|----------------------------------------------------|

| Original | $0.5V_{dc} + V_{ac} \sin \varphi$                               | $-V_{ac} \sin \varphi$                             |

| Method 1 | $0.5V_{dc} + V_{ac} \sin \varphi$                               | 0                                                  |

| Method 2 | $0.5V_{dc} + V_{ac} \sin \gamma$<br>$-k_3 V_{ac} \sin(3\gamma)$ | $-V_{ac} \sin \varphi + k_3 V_{ac} \sin(3\varphi)$ |

SMs required. In this way, the new maximum CL voltage stress  $V_{\max\_cl2}'$  and minimum stress  $V_{\min\_cl2}'$  become,

$$V'_{\max\_cl2} = 0.5V_{dc} + V_{ac} \sin \gamma - k_3 V_{ac} \sin(3\gamma), \quad (19)$$

$$V'_{\min\_cl2} = -V_{ac} \sin \varphi + k_3 V_{ac} \sin(3\varphi)$$

$k_3$  should be designed to make sure the accentuated peak voltage does not exceed  $V_{\max\_cl2}'$ .

$$0.5V_{dc} + (1 + k_3)V_{ac} \leq V'_{\max\_cl2} \quad (20)$$

The  $k_3$  meeting the equation of (20) has the best effect. As for the negative  $\varphi$ , a similar current allocation and third harmonic injection are designed as shown in Fig. 14. The summary of CL maximum and minimum voltage stresses with three methods are listed in Table I. It can be seen that method 1 reduces the minimum CL stress to 0, while method 2 reduces both values successfully.

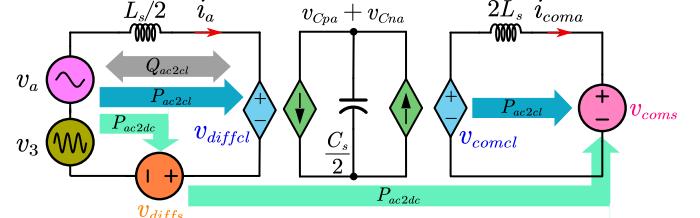

#### D. Power Flow Analysis of Two Methods

The power flow analysis is important to reveal the inherent power relationship between ac, dc and HMMR inner side, and help give the energy ripple tendency of two methods at different PFs. After neglecting the midpoint voltage and integrating the voltage source with HV diode, the average model could be derived as shown in Fig. 15.  $v_{spa}$  and  $v_{sna}$  refer to the equivalent top and bottom voltage sources in dc bus, respectively. Whereas the upper and lower CL dc-link capacitor voltages are denoted as  $v_{Cpa}$  and  $v_{Cna}$ . And the new capacitance  $C_s$  can be calculated as  $C_{sm}/N$ . The common mode voltage  $v_3$  is also given for clarification.

Similar to the traditional MMC, the Kirchhoff's voltage law (KVL) could be applied to the upper and lower CLs as below.

$$v_{spa} - v_{pa} + L_s \frac{di_{pa}}{dt} = v_a + v_3 \quad (21)$$

$$-v_{sna} + v_{na} - L_s \frac{di_{na}}{dt} = v_a + v_3$$

Fig. 16 Decoupling average model and power flow of HMMR phase  $a$ .

Fig. 17 Waveforms of voltage source with two different methods.

The addition and subtraction of two equations in (21) decompose two CL variables in the format of differential mode and common mode as in (22).

$$\frac{(v_{na} - v_{pa})}{2} + \frac{(v_{spa} - v_{sna})}{2} + \frac{L_s}{2} \frac{d(i_{pa} - i_{na})}{dt} = v_a + v_3 \quad (22)$$

$$(v_{pa} + v_{na}) - (v_{sna} + v_{spa}) = L_s \frac{d(i_{pa} + i_{na})}{dt}$$

The differential and common mode variables are defined as,

$$v_{diffs} = (v_{sna} - v_{spa})/2, \quad v_{coms} = v_{spa} + v_{sna}$$

$$v_{diffcl} = (v_{na} - v_{pa})/2, \quad v_{comcl} = v_{pa} + v_{na} \quad (23)$$

$$i_a = i_{pa} - i_{na}, \quad i_{com} = (i_{pa} + i_{na})/2$$

Then the new decoupling model could be depicted as Fig. 16. It can be observed that a new voltage source  $v_{diffcl}$  is connected in series with CL voltage  $v_{diffs}$  to follow the input ac voltage  $v_a + v_3$ . While the dc side voltage source  $v_{coms}$  should be the sum of  $v_{pa}$  and  $v_{na}$ . Since the CL voltages have already been derived according to current allocation,

the equivalent source  $v_{\text{diffs}}$  and  $v_{\text{coms}}$  could be calculated easily.

$$v_{\text{diffs}} = (v_a + v_3) - v_{\text{diffa}}, v_{\text{coms}} = v_{\text{coma}} \quad (24)$$

Therefore, the source waveforms of  $v_{\text{diffs}}$  and  $v_{\text{coms}}$  with method 1 and 2 could be plotted in Fig. 17. It is interesting to find that the three-level wave of  $v_{\text{diffs}}$  aligns with the ac current  $i_a$ , and the duration of zero voltage in  $v_{\text{diffs}}$  equals to the lasting time of PN (or ZZ) state in method 1 (or 2). This implies that part of active power is delivered from the ac side to dc side directly, whose average value is denoted as  $P_{\text{dc2ac}}$ . And this power of method 1 could be obtained through integral in (25).

TABLE II

Specifications of HMMR based HVDC converter

| Description           | Symbol                   | Value          |

|-----------------------|--------------------------|----------------|

| Ac Line-voltage (RMS) | $V_{LL,\text{rms}}$ (kV) | 115            |

| Ac frequency          | $f_a$ (Hz)               | 60             |

| Output DC bus voltage | $V_{dc}$ (kV)            | 200            |

| Rated power           | $S$ (MVA)                | 200            |

| PF                    | $PF$                     | 0.9~1          |

| SM capacitor voltage  | $V_{SM}^*$ (kV)          | 2.3            |

| SM capacitor ripple   | $\epsilon$               | 10%            |

| SM IGBT               | FZ825R33HE4D             | 3.3 kV / 825 A |

| HV diode              | W0880LC720               | 7.2 kV / 880A  |

$$P_{\text{dc2ac\_m1}} = \int_0^{2\pi} i_a v_{\text{diffs}} d(\omega t) = \frac{(1 + \cos \varphi) I_{ac} V_{dc}}{4\pi} \cdot \frac{V_{dc} I_{dc}}{3} \cdot \frac{1 + \cos \varphi}{\pi M \cos \varphi} \quad (25)$$

The remaining active power is delivered via CL named as  $P_{\text{dc2cl}}$ , while the reactive power  $Q_{\text{ac2cl}}$  is circulated between ac side and CL. At the unity PF and M of 1, it can be calculated that  $P_{\text{ac2dc}}$  about 63.7% ( $2/\pi$ ) of total power. While the dc-link capacitor energy ripple of the CL  $E_{\text{cl}}$  could be calculated as,

$$E_{\text{cl}} = \int p_{\text{cl}} dt. \quad (26)$$

The reduction of average active power indicates that the CL energy fluctuation of HMMR  $\Delta E_{\text{cl}}$  could be reduced compared to MMC. It is worth mentioning that the amplitude of  $\Delta E_{\text{cl}}$  is not proportional to the average active power  $P_{\text{dc2cl}}$ , and the reactive power also involves at the non-unity PF. Therefore, the quantitative equation of  $\Delta E_{\text{cl}}$  related to PF is not given here. But the results obtained from the numerical calculation will be shown in next section. As for method 2, the power term  $P_{\text{dc2ac}}$  is,

$$P_{\text{dc2ac\_m2}} = \frac{[1 + \cos(\pi/3 - \theta)] I_{ac} V_{dc}}{4\pi}. \quad (26)$$

Therefore, method 2 should have lower energy ripple than MMC, too.

### III. COMPARISON BETWEEN MMC AND HMMR

As claimed earlier, the biggest advantage of HMMR is reduced devices and capacitors. In order to perform a fair comparison between two methods at non-unity PF, designing the converters at different operating conditions is necessary. A HVDC case is performed and the electrical

parameters are listed in Table II. In this case, the modulation index is fixed at 0.94, and the PF range is 0.9~1 which satisfies the effective region of method 1 in Fig. 9(b).

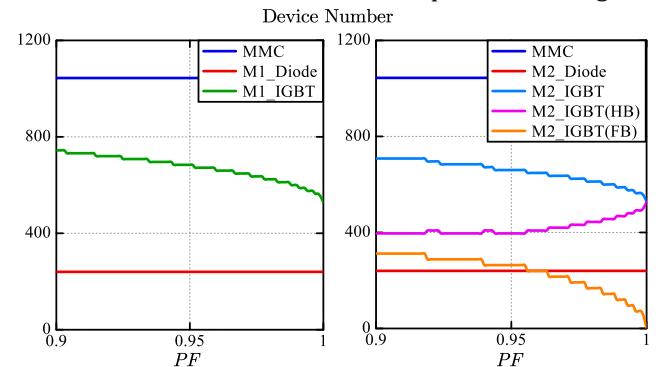

#### A. Device Number

In this paper, the Infineon 3.3 kV 825A IGBT module (FZ825R33HE4D) [28] is used for the SM. And 7.2 kV 880A press-pack diode W0880LC720 [29] from IXYS is selected for the diode stack due to less device number. The device number used in HMMR is directly related to the CL voltage stress.

The number of SMs in each CL is selected so that the dc link capacitor voltage  $V_{SM}^*$  does not exceed 2.3 kV, and the FB SM number should be sufficient to provide the negative

Fig. 18 Device number used in MMC and HMMR with two methods.

Fig. 19 CL Waveforms of MMC and HMMR with two methods at 0.9 PF.

voltage. Following Table I, the required SM number could be calculated as in (28).

$$\begin{aligned}

N_{MMC} &= \frac{V_{dc}}{V_{SM}^*} \\

N_{hm1} &= \frac{0.5*V_{dc} + V_{ac} \sin \varphi}{V_{SM}^*} \\

N_{fm2} &= \frac{|V'_{min\_cl2}|}{V_{SM}^*}, N_{hm2} = \frac{V'_{max\_cl2}}{V_{SM}^*} - N_{fm2}

\end{aligned} \tag{28}$$

The voltage stress for the diode stack is  $0.5 V_{dc}$ , and the required device number of traditional MMC, HMMR method 1 and 2 at different PF are given in Fig. 18. Noted that the device number is rounded up, so the curve is not smooth.

It can be seen that HMMR could achieve half IGBT reduction compared to the traditional MMC at the unity PF. Since the diode module is a passive device, the gate driver unit and sensor number are reduced as well. When the PF is 0.9, the additional device number is still lower than that of MMC. With the help of third harmonic injection, the device number of method 2 is similar to method 1.

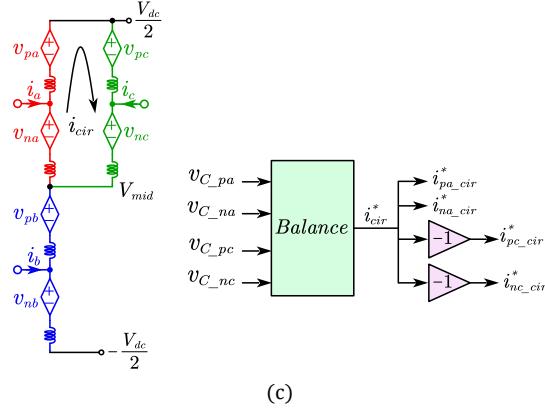

Fig. 20 CL current and energy ripple versus PF.

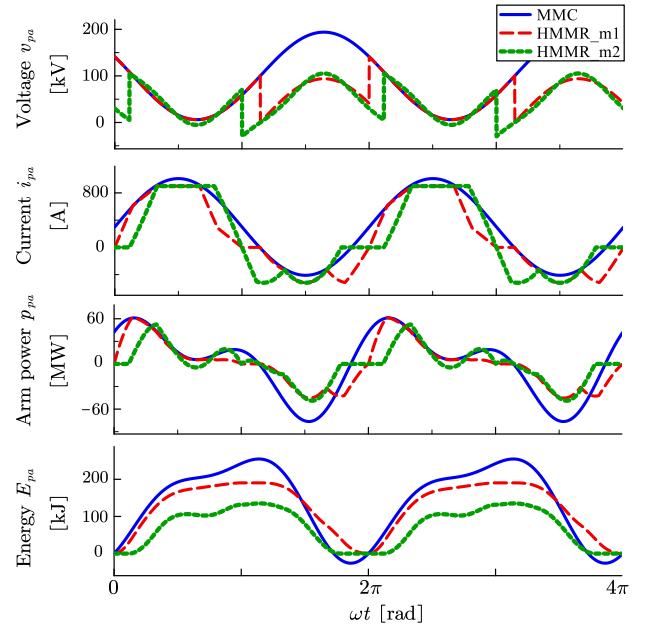

### B. Capacitor Size

Capacitors in MMC are one of the most important factors affecting the power density and cost. HMMR could reduce the SM number successfully, but the capacitance value is still unknown. The capacitor energy storage requirement per unit apparent power  $E_{unit}$  is related to the energy deviation  $\Delta E_{cl}$  and the capacitor voltage ripple coefficient  $\varepsilon$ .

$$E_{unit} = 6N \frac{C_{SM} V_{SM}^*}{2S} = \frac{3\Delta E_{cl}}{2\varepsilon S} \tag{28}$$

Two HMMR methods have different instantaneous CL power, which also varies at different PFs. Due to the symmetric characteristics of two topologies, only upper CL waveforms of phase  $a$  are discussed here. According to the aforementioned equations, CL voltage, current, power and energy variations of PF=0.9 are plotted in Fig. 19. It can be seen that the integration of CL power during one fundamental period is zero, which proves the natural CL energy balancing.

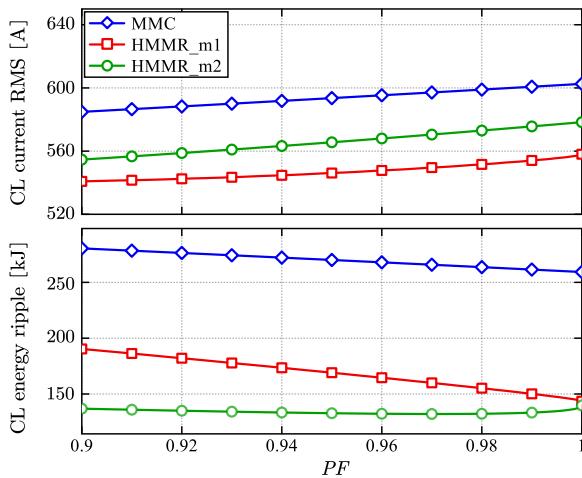

In order to get a clearer relationship between CL variables and PF. The CL current RMS value and peak to peak energy amplitude are presented in Fig. 20. Obviously, both methods have lower CL current than the traditional MMC, which implies lower semiconductor losses. Besides, they also possess lower CL energy ripple. Especially method 2 can achieve half reduction in the entire range. This conclusion matches with previous analysis. Therefore, the energy storage requirement will be smaller than MMC with same  $\varepsilon$  according to (28).

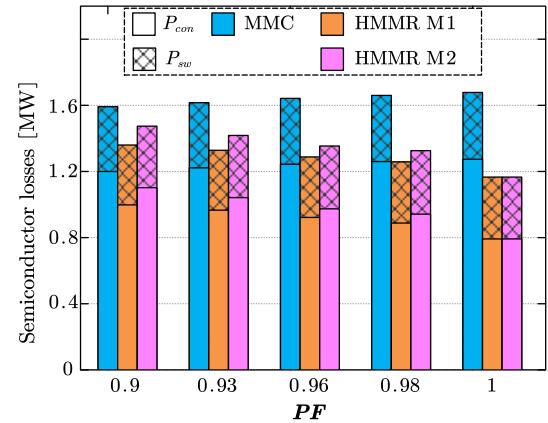

### C. Semiconductor Losses

In order to compare the converters from efficiency point of view, conduction and switching losses for semiconductors are calculated here. The conduction loss is caused by the forward voltage drop of IGBTs and diode stacks, which are considered for the following calculations [30]. For simplification, the on-state voltage drop of IGBT and its antiparallel diode are assumed to be same. Then the conduction losses for 6 CLs in MMC and HMMR can be calculated as,

$$P_{con\_cl} = \frac{6}{2\pi} \int_0^{2\pi} (N_d \cdot v_{f\_IGBT} \cdot |i_f|) d(\omega t) \tag{29}$$

Fig. 21 Power losses in MMC and HMMR with two methods.

where  $N_d$  is the number of devices in the conduction path of each CL,  $v_{f\_IGBT}$  refers to the on-state voltage drop of IGBT, and  $i_f$  denotes the current through the CL.

As for the diode stacks,  $D_{1a}$  and  $D_{2a}$  conduct the current  $i_{pa}$  alternately. Therefore, the conduction loss of two diode stacks can be combined and calculated similar to CL.

$$P_{con\_diode} = \frac{6}{2\pi} \int_0^{2\pi} (N_{diode} \cdot v_{f\_diode} \cdot |i_f|) d(\omega t) \tag{30}$$

where  $N_{diode}$  is the number of devices in the conduction path of each CL,  $v_{f\_diode}$  refers to the on-state voltage drop of diode.

Any SM operation state change corresponds to one-time turn-on loss  $e_{on}$ , turn-off loss  $e_{off}$  of IGBT and reverse recovery loss  $e_{rec}$  of antiparallel diode. The SM capacitor ripple is neglected for to calculate the equivalent value normalized to the reference voltage  $V_{CE,ref}$  in datasheet.

Then the switching losses are added within one fundamental output time period.

$$P_{sw\_cl} = \frac{\omega}{2\pi} \sum_{\gamma=1}^{N_{sw}} \left\{ \frac{V_{SM}}{v_{CE,ref}} \cdot e_{on(off)}(i_f) + \frac{V_{SM}}{v_{F,ref}} \cdot e_{rec}(i_F) \right\} \quad (31)$$

For the HV diode stack, which is turned off naturally at zero current, the reverse recovery loss should be zero. Fig. 21 shows total losses variation of one CL at different PF. The conduction losses are strongly related to the CL RMS current. Benefiting from the HV 7.2 kV diode, the conduction losses of HMMR is reduced a lot from MMC. Due to larger CL current RMS value, method 2 of HMMR has larger total losses compared to method 1.

Above all, the converter parameter of two HMMR methods based on per-unit of MMC are listed in Table III. Method 1 requires only HB SM and has higher modularity, lower losses. Whereas method 2 must use FB SM, and has lower capacitor, and part dc fault tolerant capability.

#### D. Fault Analysis and Redundant Operation

The proposed HMMR belongs to the family of VSCs despite the presence of diodes. Therefore, it does not require a strong ac grid to operate and can ride through ac faults if appropriate control technique is utilized [31]. For the symmetrical ac fault, the active power could be reduced accordingly. There will be no current ripple in dc side due to

TABLE III

Overall converter comparison between HMMR and MMC at PF of 0.9

| Topology      | MMC    | HMMR (m1)                            | HMMR (m2)                            |

|---------------|--------|--------------------------------------|--------------------------------------|

| Device number | 1 p.u. | 0.71 p.u. (CL)<br>+ 0.2 p.u. (diode) | 0.68 p.u. (CL)<br>+ 0.2 p.u. (diode) |

| Capacitor     | 1 p.u. | 0.68 p.u.                            | 0.49 p.u.                            |

| Arm current   | 1 p.u. | 0.93 p.u.                            | 0.95 p.u.                            |

| Device losses | 1 p.u. | 0.85 p.u.                            | 0.93 p.u.                            |

the absence negative sequence components.

However, the asymmetrical faults poses a control challenge owing to the shortage of control freedom [32]. Since the dc side current is synthesized by three-phase independently, the power dip of one phase will cause large dc current ripple. If the three-phase power are controlled the same, the ac side current will not be balanced. The ac fault operation is a very complicated topic and will not discussed comprehensively in this paper.

Similar to the traditional HB-MMC, HMMR with only HB SM does not have dc fault capability. The fault current will rise quickly through the antiparallel diode of IGBT module. So the CL inductor should be designed to limit the current rise rate, and the HV dc circuit breaker is necessary to protect the system [33]. The thyristor inside each SM can protect it from the over current damage [34]. While the press-pack diode has much higher surge current capability, which can withstand the overcurrent before the opening of circuit breaker. On another aspect, the FB-MMC and FB-HMMR has the intrinsic dc fault tolerant capability. So from this point of view, the method 2 with extra FB SM

can help reduce total SM number if FB SM is employed for dc fault.

The redundant operation is also very important for this kind of modular topology. The series HV diode stack can use the press-pack diode construction, whose short circuit failure mode allows for the design of redundancy [35]. As for the CL part, the redundant SMs in hot reserve or cold reserve operation modes have been proposed [36], [37], thus not discussed here.

#### IV. CONTROL METHOD AND SIMULATION RESULTS

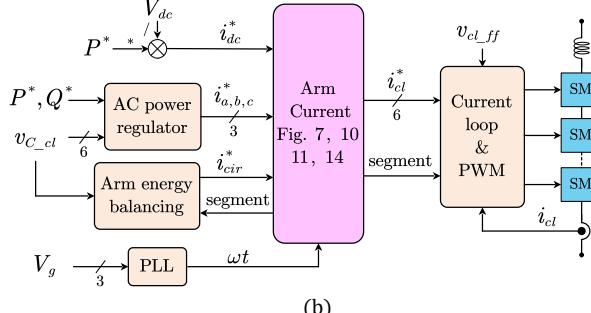

In order to validate the functionality of proposed methods of HMMR, a HVDC simulation model of 200MVA is developed with main circuit parameters listed in Table II. The structure and control block diagram are presented in Fig. 22(a). The output side of HMMR is connected to a dc source.

The key part of HMMR control in Fig. 22(b) is obtaining the six CL current references, which can be categorized into three parts: ac side component, dc side component and circulating component. The active current in the ac side component is responsible for charging the SM capacitors, hence determined by average capacitor voltage feedback control and the active power regulator. While the reactive power regulator generates the phase angle  $\varphi$  and combines with active current to get full ac component. And the circulating component depends on the unbalanced distribution of CL capacitor voltage. The example of first segment is discussed here. As shown in Fig. 22(c), phase  $a$  and phase  $c$  are connected in parallel, which means a circulating current can be injected manually with arbitrary frequency and amplitude. By exchanging energy among four CLs, the CL capacitor voltage equalization can be achieved eventually [38].

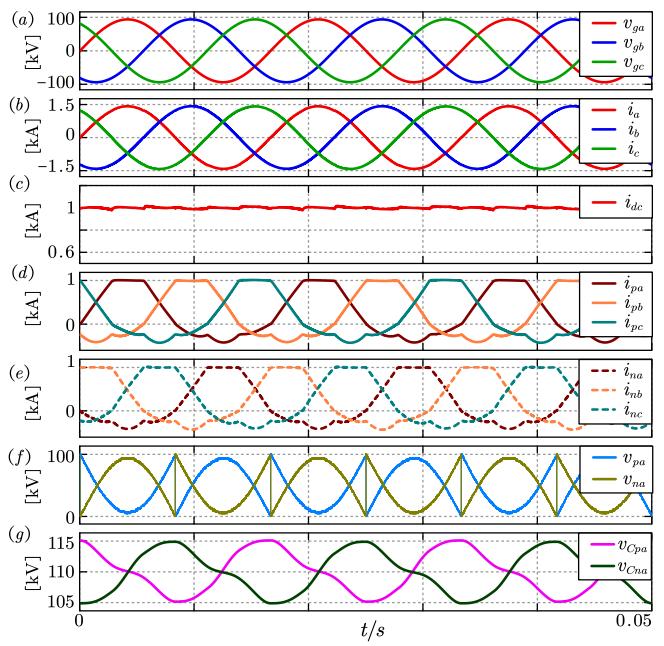

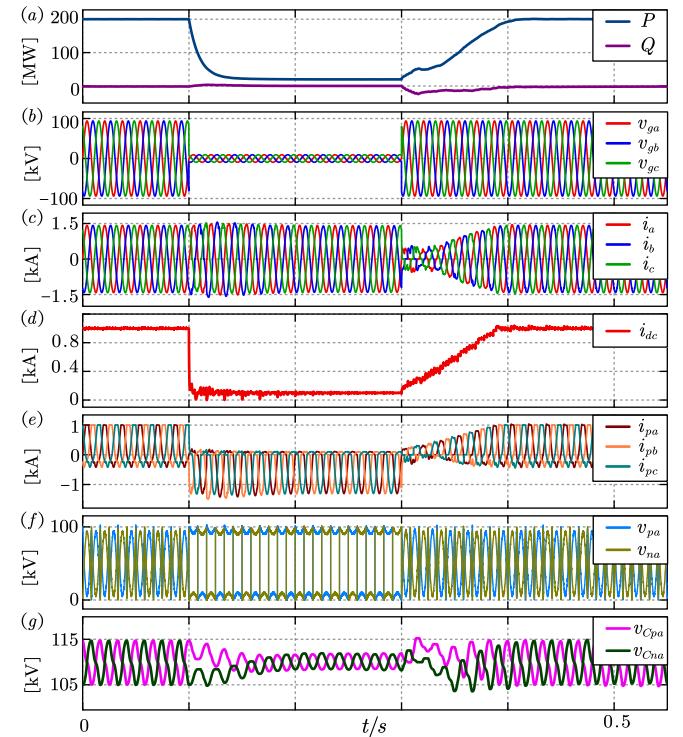

Fig. 23 shows the steady-state operation of HMMR at unity PF and full power. It can be seen that the ripple of dc side current  $i_{dc}$  in Fig. 23(c) is pretty small, which is expected after employing the trapezoidal CL current shown in Fig. 23(c) and (d). The multilevel CL voltage is presented in Fig. 23(f), which validates the half of voltage stress reduction. Fig. 23(g) is the CL capacitor voltage, which is stabled at the rated value and indicates the effectiveness of capacitor voltage balancing scheme.

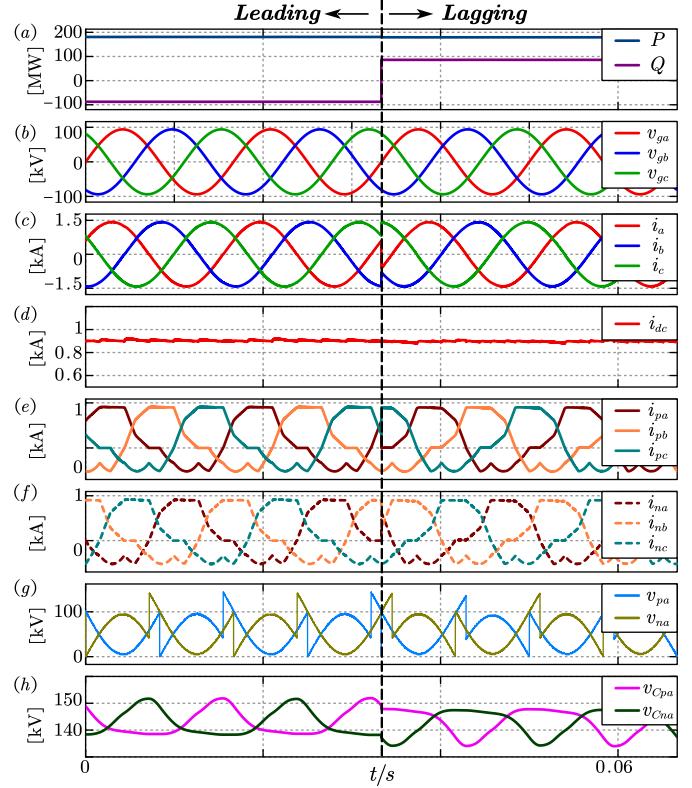

In order to validate the operation methods of HMMR at non-unity PF, the method 1 is applied first with positive and negative phase angle  $\varphi$ . The PF is set to be 0.9, so the active power is reduced to 180 MW in Fig. 24(a) and the dc side current changes to 900 A. The upper and lower CL currents in Fig. 24(e) and (f) are designed to meet the constant dc current, sinusoidal ac current and working state shift. In method 1, the

(a)

(b)

(c)

Fig. 22 (a) Simulation circuit of HMMR-HVDC system, (b) block diagram of overall control structure, (c) CL capacitor voltage balancing method.

Fig. 23 Steady-state simulation waveforms of HMMR at unity PF, (a) ac grid side voltages, (b) ac side currents, (c) dc side current, (d) three-phase upper CL currents, (e) three-phase lower CL currents, (f) phase  $a$  upper and lower CL output voltages, (g) phase  $a$  upper and lower CL capacitor voltages.

Fig. 24 Steady-state simulation waveforms of HMMR at 0.9 PF with method 1, (a) delivered active and reactive power, (b) ac grid side voltages, (c) ac side currents, (d) dc side current, (e) three-phase upper CL currents, (f) three-phase lower CL currents, (g) phase  $a$  upper and lower CL output voltages, (h) phase  $a$  upper and lower CL capacitor voltages.

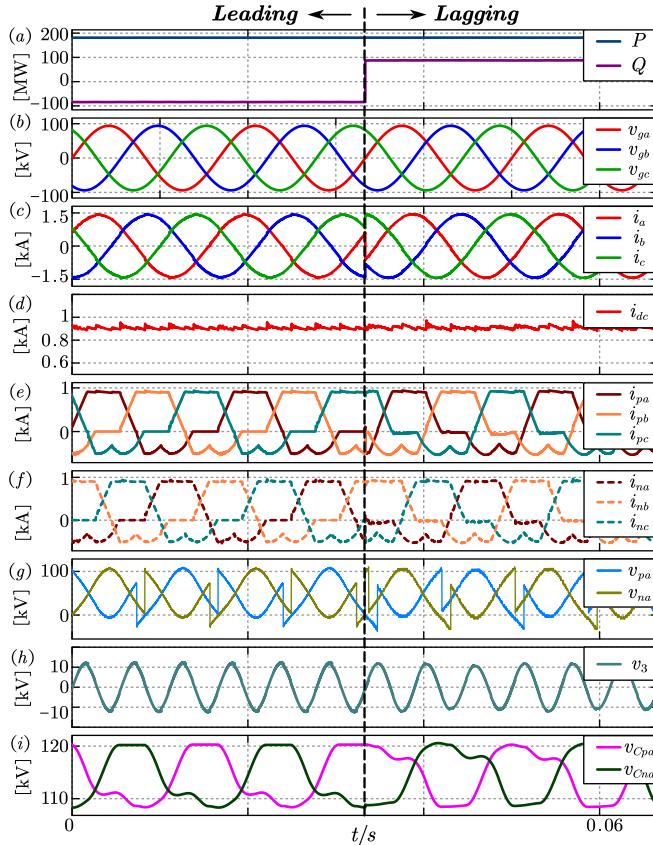

Fig. 25 Steady-state simulation waveforms of HMMR at 0.9 PF with method 2, (a) delivered active and reactive power, (b) ac grid side voltages, (c) ac side currents, (d) dc side current, (e) three-phase upper CL currents, (f) three-phase lower CL currents, (g) phase a upper and lower CL output voltages, (h) injected third-order harmonic voltage, (i) phase a upper and lower CL capacitor voltages.

*PN* state is utilized for current commutation. As the result, the maximum CL voltage is higher than  $0.5 V_{dc}$ , and more HB SMs are connected to support higher CL voltage. And the sum of CL capacitor voltage in Fig. 24(h) is also higher than unity PF case.

The same condition is also applied to HMMR with method 2. Different from former one, method 2 utilizes ZZ state instead. The upper and lower CL currents in Fig. 25(e) and (f) are designed with different shape, and extra FB SMs are connected to support negative CL voltage in Fig. 25(g). And the third order harmonic voltage in Fig. 25(h) is injected to flatten the voltage zero crossing region so that the SM number could be reduced.

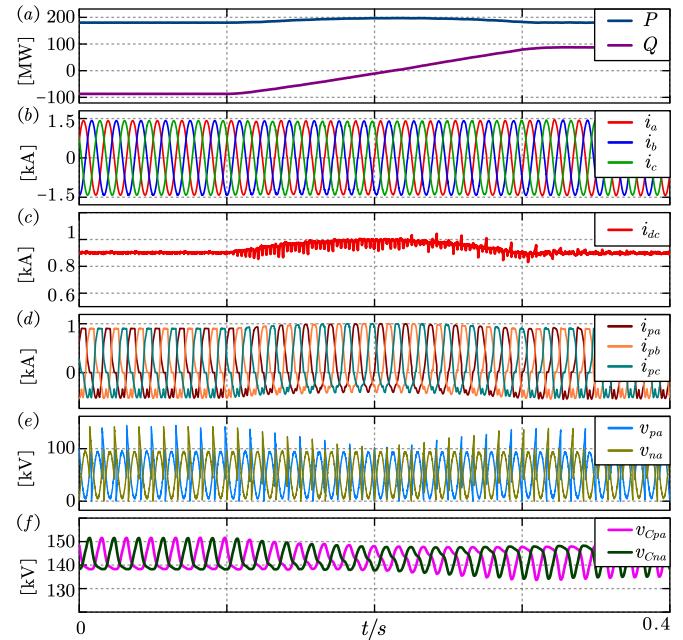

The dynamic performance of active power change with method 1 is shown in Fig. 26. When  $t = 0.2$  s, the reactive power reference is changed from -800 MVar to 800 MVar, and the total apparent power keeps constant during whole process. It can be seen that the CL voltage stress in Fig. 26(e) is larger when the PF is smaller, because the duration of *PN* state is shorter. The amplitude of CL capacitor voltage ripple is also proportional to the delivered reactive power as shown in Fig. 26(f). This waveform matches the theoretical results in Fig. 20.

Fig. 26 Dynamic response to the change in reactive power commands with method 1, (a) delivered active and reactive power, (b) ac side currents, (c) dc side current, (d) three-phase upper CL currents, (e) phase a upper and lower CL output voltages, (f) phase a upper and lower CL capacitor voltages.

Fig. 27 Waveforms during the ac fault, (a) delivered active and reactive power, (b) ac grid voltage, (c) ac side currents, (d) dc side current, (e) three-phase upper CL currents, (f) phase a upper and lower CL output voltages, (g) phase a upper and lower CL capacitor voltages.

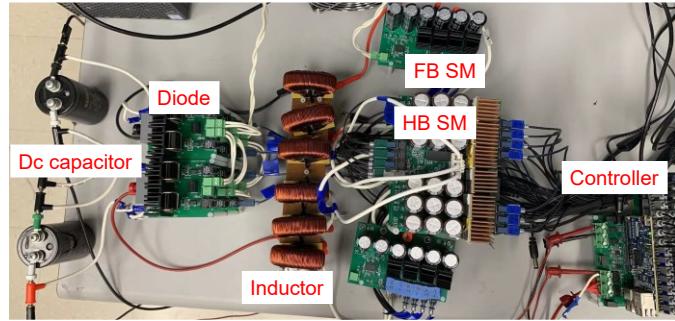

Fig. 28 Picture of laboratory HMMR prototype.

TABLE IV

Electrical parameters of 3L-HMMC system

| Parameters                   | Symbol    | Values   |

|------------------------------|-----------|----------|

| Ac voltage amplitude (phase) | $V_o$     | 180 V    |

| Rated ac frequency           | $f_o$     | 60 Hz    |

| Dc bus voltage               | $V_{dc}$  | 400 V    |

| CL inductance                | $L_{CL}$  | 3 mH     |

| SM voltage                   | $V_{CSM}$ | 85 V     |

| SM capacitance               | $C_{SM}$  | 1.32 mF  |

| Number of HB SM per CL       | $N_h$     | 2~3      |

| Number of HB SM per CL       | $N_f$     | 1        |

| Carrier frequency            | $f_c$     | 14.4 kHz |

| Power factor                 | $PF$      | 0.95     |

Fig. 29 Steady-state waveforms of HMMR with method 1, (a) leading PF, (b) lagging PF.

To test the proposed topology and control in the event of an ac grid fault, a symmetrical solid fault is applied to the ac side at  $t = 0.1$  s and is cleared after 0.2 s. As shown in Fig. 27(b), the grid voltage of the drops to 0.1 p.u. after fault occurrence. As the output power of the HMMR is reduced to 0.1 p.u. accordingly and the three-phase ac current will keep same as shown in Fig. 27(c). The amplitude of dc side current in Fig. 27(d) drops to 0.1 p.u. as well, and the ripple is due to the absence negative sequence components. After fault clearance of  $t=0.3$  s, the power transmission resumes and the system autonomously restores normal operation with a soft start. During the whole process, the CL capacitor voltage in Fig. 27(g) is balanced very well.

## V. EXPERIMENTAL RESULTS

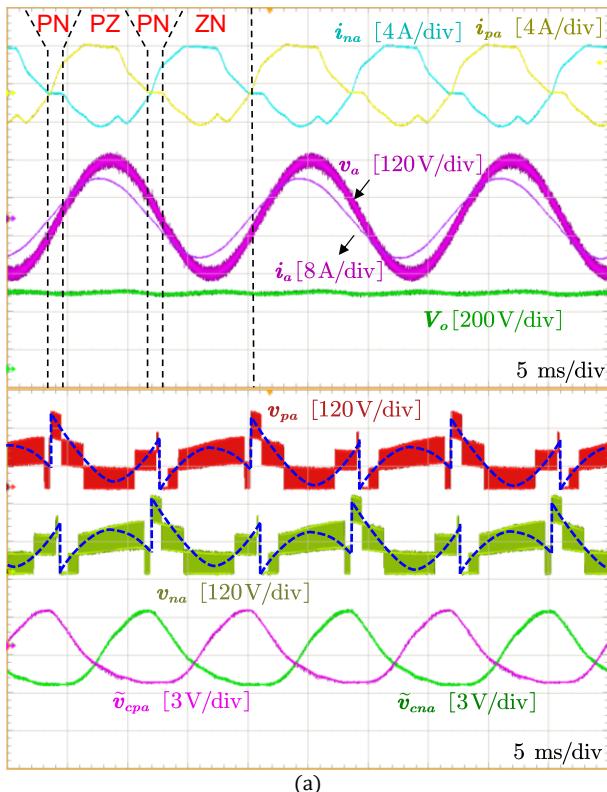

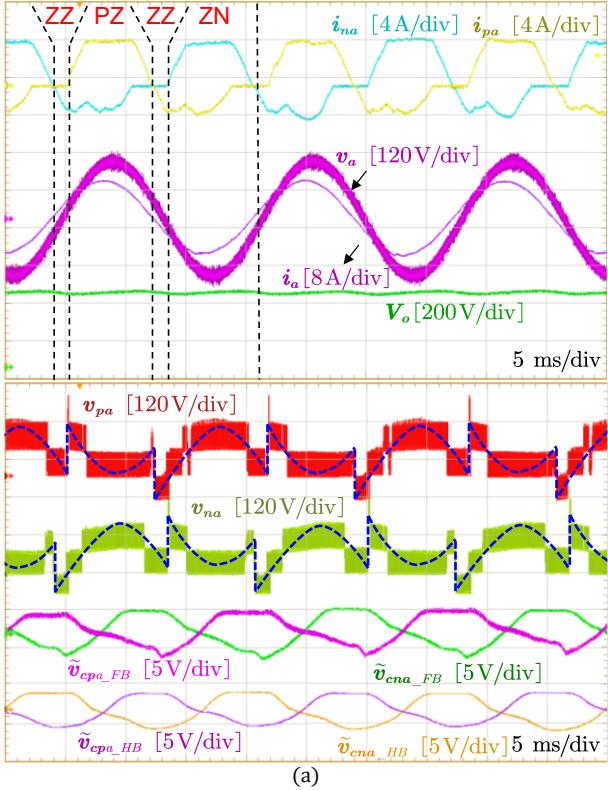

The working principle and performance of the proposed HMMR is also validated using a laboratory prototype with the other circuit parameters as listed in Table IV and the setup is shown in Fig. 28. The dc side uses resistor as load, and the whole system is controlled by digital signal processor (DSP) TMS320F28388. Each CL has three SMs, which are three HB for method 1 and two HB plus one FB for method 2 to verify the non-unity PF operation. The SM capacitor and CL currents sampling results are sent back to controller through SPI communication. Results and key observations obtained using this prototype during steady state and transient conditions are provided to confirm the operating principles and control schemes of HMMR.

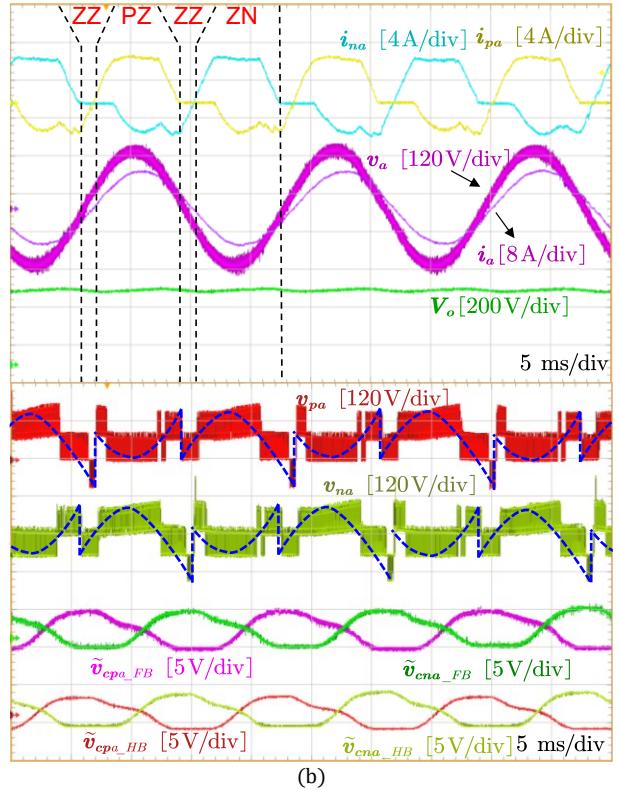

The steady-state results with method 1 are shown in Fig. 29. As explained earlier, the working states of one cycle consist of *PN*, *PZ* and *ZN* states. The four level CL voltage is

generated by the phase-shift modulation of reference voltage. Capacitor voltage of an HB SM in upper and lower

(a)

CLs are shown as well, which are regulated around its nominal value and the

(b)

Fig. 30 Steady-state waveforms of HMMR with method 2, (a) leading PF, (b) lagging PF.

Fig. 31 Dynamic response of HMMR to the change in capacitor voltage reference with method 1.

effectiveness of the proposed control method is substantiated. The ac side current is perfectly sinusoidal as desired, which indicates the good design of current loop parameter.

Similarly, the results obtained with method 2 are shown in Fig. 30. Since ZZ state is inserted between PZ and ZN states, a FB SM is connected in series to replace one HB SM. The capacitor voltage waveform of FB is different from HB, because only FB provides the negative voltage during ZZ state. But their voltage will be balanced during PZ and ZN state with the help of individual voltage balancing control.

The converter operates as expected at both methods and provides satisfactory performance. These results obtained from the hardware prototype are in agreement with the simulation results presented in the previous section.

Fig. 32 Dynamic response of HMMR to the change in output dc voltage reference with method 1.

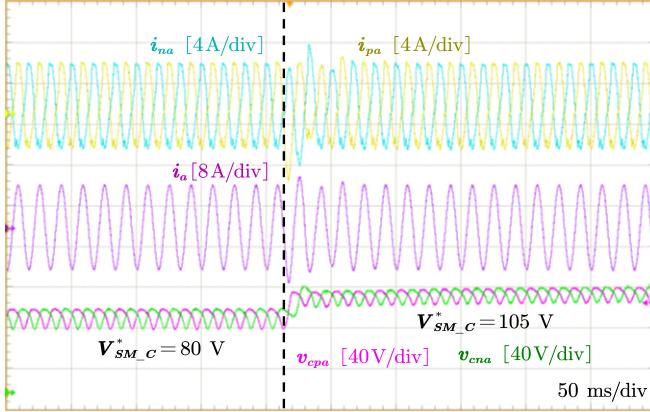

In order to evaluate the performance of the control scheme during transients, the capacitor voltage reference is instantly increased from 80 V to 115 V and key waveforms obtained are presented in Fig. 31. Due to the existence of

capacitor average voltage control, the ac component of CL current will increase immediately. As a result, the ac side current will be higher for a short time, and the capacitor will be charged to the new reference. Since the total active power does not change, the ac and CL currents will be same in the new steady state.

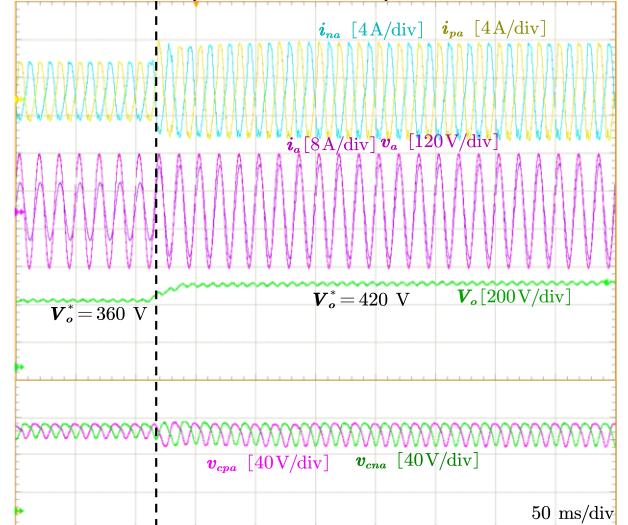

To further verify the ability of HMMR to handle sudden transients in voltage, the output dc voltage reference is suddenly altered from 360 V to 420 V and the corresponding results are given in Fig. 32. Since the load resistor keeps constant, the total power will be larger if dc voltage is higher. Therefore, it can be seen the CL and ac currents amplitude increases proportionally. The amplitude of capacitor voltage fluctuation becomes higher as well due to delivered larger power. The converter operates stably for the aforesaid transients and desired results are obtained. Hence, the feasibility of HMMR and its working principle are verified using the experimental setup and are found to be in agreement with the above-mentioned theoretical analysis and simulation studies.

## VI. CONCLUSIONS

HMMR is a unidirectional ac-dc converter intended for MV and HV ac-dc applications without reverse power flow. For HVDC or other grid applications, non-unity PF operation is important for the rectifier to deliver some amount of reactive power and support the grid during low-voltage transient and weak grid conditions. Two methods are presented in this paper to reduce the required SM number of SM in the leading and lagging PF operation of HMMR. The key concept is inserting *PN* or *ZZ* state between *PN* and *NZ* state as transition. Method 1 requires only HB SM but limited operation range. Whereas method 2 must use FB SM, and part dc fault tolerant capability. Also the third order harmonic is injected to further reduce the SM number of method 2. It is found that both methods can successfully reduce 0.3 p.u. LV device compared to MMC at PF of 0.9. As for the energy storage requirement, the derived average model shows that partial power is delivered from the ac to dc side through diode directly. As a result, method 1 can reduce 32% capacitor and method 2 achieves 52% reduction. Besides, the efficiency of HMMR is lower than MMC as well. Since HMMR is a VSC, it does not require a strong ac grid to operate and can ride through ac faults similar to MMC. Above all, HMMR is a good candidate to replace MMC in rectifier applications to realize higher power density and efficiency.

## REFERENCES

- [1] L. Zhang et al, "Modeling, control, and protection of modular multilevel converter-based multi-terminal HVDC systems: A review," in CSEE Journal of Power and Energy Systems, vol. 3, no. 4, pp. 340-352, Dec. 2017.

- [2] A. Dekka, B. Wu, R. L. Fuentes, M. Perez and N. R. Zargari, "Evolution of Topologies, Modeling, Control Schemes, and Applications of Modular Multilevel Converters," in IEEE Journal of Emerging and Selected Topics in Power Electronics, vol. 5, no. 4, pp. 1631-1656, Dec. 2017.

- [3] A. Nami, J. Liang, F. Dijkhuizen and G. D. Demetriadis, "Modular Multilevel Converters for HVDC Applications: Review on Converter Cells and Functionalities," in IEEE Transactions on Power Electronics, vol. 30, no. 1, pp. 18-36, Jan. 2015.

- [4] M. A. Perez, S. Bernet, J. Rodriguez, S. Kouro, and R. Lizana, "Circuit topologies, modeling, control schemes, and applications of modular multilevel converters," IEEE Trans. Power Electron., vol. 30, no. 1, pp. 4-17, Jan. 2015.

- [5] J. Jung, S. Cui, J. Lee and S. Sul, "A New Topology of Multilevel VSC Converter for a Hybrid HVDC Transmission System," in IEEE Transactions on Power Electronics, vol. 32, no. 6, pp. 4199-4209, June 2017.

- [6] P. Bakas et al, "A Review of Hybrid Topologies Combining Line-Commuted and Cascaded Full-Bridge Converters," in IEEE Transactions on Power Electronics, vol. 32, no. 10, pp. 7435-7448, Oct. 2017.

- [7] L. Hou, S. Zhang, Y. Wei, X. Li and Q. Jiang, "A Hybrid-Arm Modular Multilevel Converters Topology With DC Low Voltage Operation and Fault Ride-Through Capability for Unidirectional HVDC Bulk Power Transmission," in IEEE Transactions on Power Delivery, vol. 35, no. 6, pp. 2812-2820, Dec. 2020.

- [8] O. Kuhn, P. Menke, R. Zurowski, T. Christ, S. Seman, G. Giering, et al, "2nd generation DC grid access for offshore wind farms: HVDC in an AC fashion," CIGRE, Paris, pp. 1-7, 2016.

- [9] R. Blasco-Gimenez, S. Añó-Villalba, J. Rodríguez-D'Derlée, F. Morant and S. Bernal-Perez, "Distributed Voltage and Frequency Control of Offshore Wind Farms Connected With a Diode-Based HVdc Link," in IEEE Transactions on Power Electronics, vol. 25, no. 12, pp. 3095-3105, Dec. 2010.

- [10] R. Blasco-Gimenez, S. Anó-Villalba, J. Rodríguez-D'Derlée, S. Bernal-Perez and F. Morant, "Diode-Based HVdc Link for the Connection of Large Offshore Wind Farms," in IEEE Transactions on Energy Conversion, vol. 26, no. 2, pp. 615-626, June 2011.

- [11] A. Nami, J. L. Rodriguez-Amenedo, S. Arnaltes, M. Á. Cardiel-Álvarez and R. A. Baraciarte, "Frequency Control of Offshore Wind Farm With Diode-Rectifier-based HVdc Connection," in IEEE Transactions on Energy Conversion, vol. 35, no. 1, pp. 130-138, March 2020.

- [12] Y. Tang, Z. Zhang and Z. Xu, "DRU Based Low Frequency AC Transmission Scheme for Offshore Wind Farm Integration," in IEEE Transactions on Sustainable Energy, vol. 12, no. 3, pp. 1512-1524, July 2021.

- [13] T. H. Nguyen, D. Lee and C. Kim, "A Series-Connected Topology of a Diode Rectifier and a Voltage-Source Converter for an HVDC Transmission System," in IEEE Transactions on Power Electronics, vol. 29, no. 4, pp. 1579-1584, April 2014.

- [14] R. Li, L. Yu, L. Xu and G. P. Adam, "Coordinated Control of Parallel DR-HVDC and MMC-HVDC Systems for Offshore Wind Energy Transmission," in IEEE Journal of Emerging and Selected Topics in Power Electronics, vol. 8, no. 3, pp. 2572-2582, Sept. 2020.

- [15] Y. Chang and X. Cai, "Hybrid Topology of a Diode-Rectifier-Based HVDC System for Offshore Wind Farms," in IEEE Journal of Emerging and Selected Topics in Power Electronics, vol. 7, no. 3, pp. 2116-2128, Sept. 2019.

- [16] R. Li and L. Xu, "A Unidirectional Hybrid HVDC Transmission System Based on Diode Rectifier and Full-bridge MMC," in IEEE Journal of Emerging and Selected Topics in Power Electronics.

- [17] P. Bakas et al, "Review of Hybrid Multilevel Converter Topologies Utilizing Thyristors for HVDC Applications," in IEEE Transactions on Power Electronics, vol. 36, no. 1, pp. 174-190, Jan. 2021.

- [18] M. Merlin et al, "The alternate arm converter: A new hybrid multilevel converter with DC-fault blocking capability," IEEE Trans. Power Del., vol. 29, no. 1, pp. 310-317, Feb. 2014.

- [19] M. M. C. Merlin et al, "The extended overlap alternate arm converter: A voltage source converter with dc fault ride-through capability and a compact design," IEEE Trans. Power Electron., vol. 33, no. 5, pp. 3898-3910, May 2018.

- [20] E. M. Farr, R. Feldman, J. C. Clare and O. F. Jasim, "The Alternate Arm Converter "Extended-Overlap" Mode: AC Faults," in IEEE Transactions on Power Electronics, vol. 36, no. 5, pp. 5371-5388, May 2021.

[21] E. Amankwah, A. Watson, R. Feldman, J. Clare and P. Wheeler, "Experimental validation of a parallel hybrid modular multilevel voltage source converter for HVDC transmission," 2013 Twenty-Eighth Annual IEEE Applied Power Electronics Conference and Exposition (APEC), Long Beach, CA, 2013, pp. 1607-1614.

[22] R. Feldman et al., "A Hybrid Modular Multilevel Voltage Source Converter for HVDC Power Transmission," in IEEE Transactions on Industry Applications, vol. 49, no. 4, pp. 1577-1588, July-Aug. 2013.

[23] E. M. Farr, D. R. Trainer, O. E. Idehen and K. Vershinin, "The Series Bridge Converter (SBC): AC Faults," in IEEE Transactions on Power Electronics, vol. 35, no. 5, pp. 4467-4471, May 2020.

[24] J. Liu, D. Dong and D. Zhang, "Hybrid Modular Multilevel Rectifier: A New High-Efficient High-Performance Rectifier Topology for HVDC Power Delivery," in IEEE Transactions on Power Electronics, vol. 36, no. 8, pp. 8583-8587, Aug. 2021.

[25] J. Liu, D. Dong and D. Zhang, "A Hybrid Modular Multilevel Converter Family With Higher Power Density and Efficiency," in IEEE Transactions on Power Electronics, vol. 36, no. 8, pp. 9001-9014, Aug. 2021.

[26] D. Zhang, D. Dong, R. Datta, A. Rockhill, Q. Lei and L. Garces, "Modular Embedded Multilevel Converter for MV/HVDC Applications," in IEEE Transactions on Industry Applications, vol. 54, no. 6, pp. 6320-6331, Nov.-Dec. 2018.

[27] J. Yang, Z. He, J. Ke and M. Xie, "A New Hybrid Multilevel DC-AC Converter With Reduced Energy Storage Requirement and Power Losses for HVDC Applications," in IEEE Transactions on Power Electronics, vol. 34, no. 3, pp. 2082-2096, March 2019.

[28] Infineon IGBT Module Manuals, 2020. [online] Available: <https://www.infineon.com/cms/en/product/power/igbt/igbt-modules/>.

[29] Littelfuse rectifier diode Manuals, 2020. [online] Available: <https://www.littelfuse.com/products/power-semiconductors/discrete-diodes/rectifier/rectifier-capsule-type.aspx#>.

[30] S. Rohner, S. Bernet, M. Hiller and R. Sommer, "Modulation, Losses, and Semiconductor Requirements of Modular Multilevel Converters," in IEEE Transactions on Industrial Electronics, vol. 57, no. 8, pp. 2633-2642, Aug. 2010.

[31] E. M. Farr, R. Feldman, J. C. Clare and O. F. Jasim, "The Alternate Arm Converter "Extended-Overlap" Mode: AC Faults," in IEEE Transactions on Power Electronics, vol. 36, no. 5, pp. 5371-5388, May 2021.

[32] S. Cui, H. Lee, J. Jung, Y. Lee and S. Sul, "A Comprehensive AC-Side Single-Line-to-Ground Fault Ride Through Strategy of an MMC-Based HVDC System," in IEEE Journal of Emerging and Selected Topics in Power Electronics, vol. 6, no. 3, pp. 1021-1031, Sept. 2018.

[33] G. Liu, F. Xu, Z. Xu, Z. Zhang and G. Tang, "Assembly HVDC Breaker for HVDC Grids With Modular Multilevel Converters," in IEEE Transactions on Power Electronics, vol. 32, no. 2, pp. 931-941, Feb. 2017.

[34] W. Xiang, S. Yang, G. P. Adam, H. Zhang, W. Zuo and J. Wen, "DC Fault Protection Algorithms of MMC-HVDC Grids: Fault Analysis, Methodologies, Experimental Validations, and Future Trends," in IEEE Transactions on Power Electronics, vol. 36, no. 10, pp. 11245-11264, Oct. 2021.

[35] H. Li et al., "A Study on the Failure Evolution to Short Circuit of Nanosilver Sintered Press-Pack IGBT," in IEEE Transactions on Components, Packaging and Manufacturing Technology, vol. 10, no. 1, pp. 184-187, Jan. 2020.

[36] W. Xiang, S. Yang, G. P. Adam, H. Zhang, W. Zuo and J. Wen, "DC Fault Protection Algorithms of MMC-HVDC Grids: Fault Analysis, Methodologies, Experimental Validations, and Future Trends," in IEEE Transactions on Power Electronics, vol. 36, no. 10, pp. 11245-11264, Oct. 2021.

[37] B. Li, Y. Zhang, R. Yang, R. Xu, D. Xu and W. Wang, "Seamless Transition Control for Modular Multilevel Converters When Inserting a Cold-Reserve Redundant Submodule," in IEEE Transactions on Power Electronics, vol. 30, no. 8, pp. 4052-4057, Aug. 2015.

[38] J. Liu, D. Dong and D. Zhang, "Control of Hybrid Modular Multilevel Converter and its Capacitor Voltage Balancing," 2020 IEEE 9th International Power Electronics and Motion Control Conference (IPEMC2020-ECCE Asia), 2020, pp. 800-806.