1 IEEE CICC 2022

## A Jitter-Robust 40Gb/s ADC-Based Multicarrier Receiver Front End in 22nm FinFET

Yuanming Zhu\*, Julian Camilo Gomez Diaz\*, Srujan Kumar Kaile, II-Min Yi, Tong Liu, Sebastian Hoyos, and Samuel Palermo

Texas A&M University, College Station, TX, USA \*Equally Credited Authors (ECAs)

Demand for increased data-rates in serial link transceivers calls for innovative architectures capable of overcoming communications impairments such as limited channel bandwidth and stringent jitter specifications. While mixed-signal and ADC-based receiver architectures that utilize simple pulse amplitude modulation (PAM) can take advantage of technology scaling, it is becoming increasingly difficult to deal with the extremely short baseband pulse widths. This paper presents a wireline receiver front-end (RXFE) architecture that supports multicarrier signaling to provide a ~3X relaxation in clock jitter requirements.

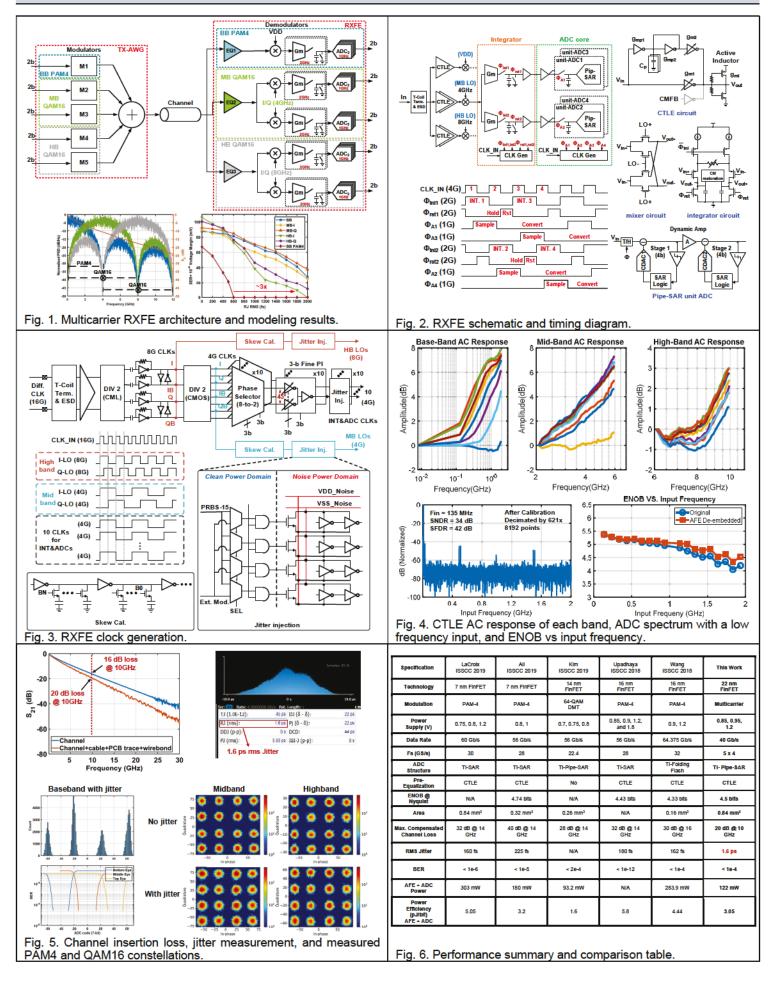

Figure 1 shows the implemented RXFE architecture and the multicarrier signal power spectral density, where orthogonality is leveraged to allow for band overlapping and improved spectral efficiency. The multicarrier signal is formed by three bands to support a total 40Gb/s data rate. This includes baseband (BB) PAM4 operating at 4GS/s and mid-band (MB) and high-band (HB) that both carry 4GS/s QAM16 on 4GHz and 8GHz orthogonal carriers, respectively. This 4GS/s rate has a symbol duration that is 5X longer than a conventional 20GS/s baseband PAM4 signal. Thus, the proposed architecture offers jitter robustness that has been evaluated through system-level simulations with different clock jitter amounts on both the receiver LO down-conversion and sampling clocks when operating over a channel with 20dB loss at 10GHz. The results show that the proposed multicarrier system which can tolerate up to 1.6ps<sub>rms</sub> jitter, whereas a BB PAM4 system cannot tolerate more than 600fs<sub>ms</sub> at a BER=10<sup>-4</sup>.

As shown in Fig. 2, after the input T-coil termination the multiband signal passes through three parallel continuous-time linear equalizers (CTLEs) designed to optimally equalize each of the bands and relax RXFE linearity requirements. The BB CTLE drives a single segment consisting of a dummy mixer, integrating sinc filters, and 4way time-interleaved ADC, while the MB and HB CTLE both drive two I/Q segments with the mixers switched with the 4GHz and 8GHz LO signals, respectively. Inverter-based CTLE structures with two signal paths are utilized [1], with the top branch low-pass response subtracted from the bottom path all-pass response to form a highpass characteristic. The advantage of using this architecture lies on the ability to set equal transconductances for the top and bottom branches to significantly attenuate the low-frequency component of the multiband signal. This results in a more optimal AC response, improved linearity, and lower output-referred noise for the MB and HB segments. The RXFE sinc filters are implemented with resettable integrators built with dynamic amplifiers with common-restoration and programmable source degeneration resistances for gain control.

The Fig. 2 timing diagram shows the integrator operation and interface with the 4-way time-interleaved ADC. The integrator in each segment operates in a 2-way time-interleaved manner to allow for an integrator reset cycle. In this case,  $\phi_{ini}$  going high marks the start of the integration period. The clock  $\phi_{A1}$  will go high right after this to start tracking the output and then perform sampling after  $\phi_{ini}$  goes low. The 25% percent duty cycle  $\phi_{rst}$  creates an integrator hold phase that relaxes the timing requirement for this ADC sample clock. The integrator capacitor is then reset when  $\phi_{rst1}$  goes high. Each 7-bit 1GS/s unit ADC is formed by a pipelined-SAR structure with an output level shifting (OLS) settling technique [2] for low power and high-speed operation. 4-bits are converted in both pipeline stages, with 1-bit redundancy between the two stages to relax the gain, offset, and reference settling requirements. Both stages employ parallel comparators that are asynchronously activated sequentially for each conversion step, eliminating the comparator reset delay and offering significant speed-up.

Fig. 3 shows the RXFE clock generation circuitry that generates the HB and MB LOs and the 10 input clocks for the integrators and ADC local clock generation blocks in each segment. A 16GHz differential clock input passes through a CML divider and CML-to-CMOS

converters to generate 4-phase 8GHz clock signals for the HB LO signals. A subsequent CMOS divider generates 8-phase 4GHz clock signals, with four of these phases used for the MB LO signals. Additionally, these eight 4GHz clocks signals are provided to 10 6b phase interpolators to generate the clocks for the integrators and ADCs with independent sampling phase control. Phase mismatches between I and Q LO signals are compensated with skew calibration blocks consisting of distribution buffers that have digitally-controlled capacitive loading.

To verify the proposed RXFE jitter robustness, the distribution buffers of the LO and integrator/ADC clocks operate on a power domain with programmable noise injection. Large shunting NMOS transistors are driven by either an internal PRBS generator or an external signal to provide jitter with varying frequency content.

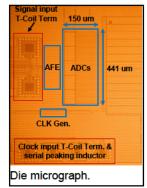

As shown in the 22nm FinFET die micrograph, the entire RXFE occupies 0.84mm² when the input T-coil and clock buffer inductors are included. The CTLE, mixers, and integrators occupy 102um X 225um of this area, while the ADCs consume 150um X 441um. Fig. 4 shows the DFT from one of the decimated (621x) 4-way time interleaved ADC outputs when sampling a low-frequency input at 4GS/s, with an achieved SNDR and SFDR of 33.7dB and 42 dB, respectively. The ADC Nyquist rate ENOB through the entire RXFE is 4.2b and 4.53b when the RXFE is de-embedded. The frequency response of the CTLEs are measured from the ADC output using single-tone inputs, with the BB, MB, and HB CTLEs achieving a highest normalized peaking of 8dB, 7dB, and 3dB, respectively. Fig. 5 show RXFE measurement results with a 40Gb/s multiband input signal with independent PRBS15 patterns in the bands generated with a Keysight M8195A AWG with an 800mVppd total swing. This is passed through a channel with 20dB insertion loss at 10GHz (conventional baseband PAM4 Nyquist) and data is collected with and without jitter added. For the maximum 1.6ps<sub>rms</sub> jitter injection, the BB channel has an average voltage margin of 24 ADC codes at a BER=10<sup>-5</sup> and the MB and HB constellations have a respective EVM of 20.4dB and 18.8dB that translates to BERs of 10-6 and 3.5x10-5. These constellations suffered a respective EVM degradation of 0.5dB and 0.8dB with respect to the no jitter added case. Fig. 6 compares this RXFE with other ADC-based wireline RXFE that utilize conventional PAM4 and multi-tone signaling. The proposed multicarrier RXFE can operate with the highest 1.6ps<sub>rms</sub> jitter and achieves 3.05pJ/bit power efficiency.

## Acknowledgment:

This work was supported in part by SRC TxACE Grant 2810.013 and NSF Grant 1930828. Chip fabrication services were provided through the Intel University Shuttle Program.

## References

- [1] K. Zheng et al., "An Inverter-Based Analog Front-End for a 56-Gb/s PAM-4 Wireline Transceiver in 16-nm CMOS," in IEEE Solid-State Circuits Letters, 2018.

- [2] Y. Zhu et al., "A 1.5GS/s 8b Pipelined-SAR ADC with Output Level Shifting Settling Technique in 14nm CMOS," CICC, 2020.

- [3] M. -A. LaCroix et al., "6.2 A 60Gb/s PAM-4 ADC-DSP Transceiver in 7nm CMOS with SNR-Based Adaptive Power Scaling Achieving 6.9pJ/b at 32dB Loss," ISSCC, 2019.

- [4] T. Ali et al., "A 180mW 56Gb/s DSP-Based Transceiver for High Density IOs in Data Center Switches in 7nm FinFET Technology," ISSCC, 2019.

- [5] G. Kim et al., "30.2 A 161mW 56Gb/s ADC-Based Discrete Multitone Wireline Receiver Data-Path in 14nm FinFET," ISSCC, 2019.

- [6] P. Upadhyaya et al., "A fully adaptive 19-to-56Gb/s PAM-4 wireline transceiver with a configurable ADC in 16nm FinFET," ISSCC, 2018.

- [7] L. Wang et al., "A 64Gb/s PAM-4 transceiver utilizing an adaptive threshold ADC in 16nm FinFET," ISSCC, 2018.