## 2 POD-RACING: Bulk-Bitwise to Floating-Point 3 Compute in Racetrack Memory for Machine 4 Learning at the Edge

5

6 Sébastien Ollivier , Xinyi Zhang, Yue Tang, Chayanika Choudhuri, Jingtong Hu , and Alex K. Jones

7 University of Pittsburgh, Pittsburgh, PA, 15260, USA

8 *Convolutional neural networks (CNNs) have become a ubiquitous algorithm with

9 growing applications in mobile and edge settings. We describe a compute-in-

10 memory (CIM) technique called POD-RACING using Racetrack memory (RM) to

11 accelerate CNNs for edge systems. Using transverse read, a technique that can

12 determine the number of "1"s in multiple adjacent domains, POD-RACING can

13 efficiently implement multioperand bulk-bitwise and addition computations, and

14 two-operand multiplication. We discuss how POD-RACING can implement both

15 variable precision integer and floating point arithmetic using digital CIM. This

16 allows both CNN inference and on-device training without expensive data

17 movement to the cloud. Based on these functions we demonstrate the

18 implementation of several CNNs with backpropagation using RM CIM and compare

19 these to the state-of-the-art implementations of CNN inference and training. During

20 training, POD-RACING improves efficiency by 2 $\times$ , energy consumption by  $\geq 27\%$ , and

Q1 21 increases throughput by  $\geq 18\%$  versus a state-of-the-art FPGA accelerator.*

Q2 22 **E**dge computing has become increasingly

23 attractive for accelerating machine learning

24 algorithms, such as convolutional neural net-

25 works (CNNs), to support the needs of mobile applica-

26 tions. However, edge systems must adhere to

27 constraints often referred to as SWaP (size, weight,

28 and power). For CNN acceleration, field programmable

29 gate arrays (FPGA) are studied as the best possible

30 acceleration engines for low latency while meeting

31 the energy requirements of these edge systems but,

32 are limited by the need for intensive off-chip memory

33 accesses. Compute-in-memory (CIM) is proposed to

34 alleviate this bottleneck. Unfortunately, crossbar-

35 based solutions require high-energy digital/analog

36 conversion, which is inappropriate for mobile devices

37 and DRAM-based solutions have not demonstrated

38 sufficient precision to implement training. Spintronic

39 *Racetrack memory*<sup>1</sup> (RM) is attractive for edge sys-

40 tems as it has the necessary density, i.e., between 1-

41 4F<sup>2</sup> per cell, while not suffering from endurance

42 concerns of other tiered memory candidates, such as

43 phase-change and resistive memories. It also has a

44 low-energy consumption of circa 0.1 pJ<sup>2</sup> per write and

45 a low access latency of circa 1-ns generating excite-

46 ment for use as main memory,<sup>3,4</sup> particularly for SWaP

47 constrained systems.

48 We present *precision optimized deep-learning*

49 using *Racetrack arithmetic computed in-mem-

50 ory for native gradient-descent* (RACING). POD-RAC-

51 ING is the first digital CIM implementation of floating-

52 point multiply-accumulate designed to implement full

53 CNN algorithms under SWaP constraints.

54 With POD-RACING CIM acceleration of deep learn-

55 ing, we achieve as much as 5 $\times$  higher performance

56 than the state-of-the-art DRAM CIM, which leverages

57 ternary (bulk-bitwise and summation) weight calcula-

58 tions<sup>5,6</sup> with a nearly 50% reduction in power. POD-

59 RACING is 2.8 $\times$  faster and more than 3 $\times$  more energy

60 efficient for integer precision (multiplication and addi-

61 tion) than the state-of-the-art RM CIM. We also

62 achieve 18%–74% performance improvement and

63 26%–81% reduction in power compared to a low-

64 energy FPGA for 32-bit floating-point precision online

65 training targeting small to moderate CNNs. In particu-

66 lar, POD-RACING makes the following contributions.

67 ➤ POD-RACING is, to the best of our knowledge,

68 the first RM CIM approach to implement floating-

69 point addition and multiplication.

70 ➤ We propose floating-point CIM designed to con-

71 duct multioperand floating-point addition.

72 ➤ We show that POD-RACING outperforms and

73 provides better efficiency for both CIM (inference)

74 and FPGA (training) targeting edge

75 systems.

76 The remainder of this article is organized as fol-

77 lows. First, we provide the necessary background on

78 CNNs and RM. Next, we describe the basic concepts

79 of POD-RACING, starting with its architecture and

80 how to perform integer operations. We then explain

81 how to perform floating-point multiplication with RM

82 CIM followed by an algorithmic-level explanation on

83 how to extend similar approaches to perform FP multi-

84 operand addition. We provide experimental results

85 comparing improvements of POD-RACING with

86 DRAM CIM for inference and an FPGA accelerator, fol-

87 lowed by conclusions.

## BACKGROUND

88 In this section, we first introduce the elements that

89 compose the CNN inference and the additional opera-

90 tions required for training. Next, we provide a brief

91 introduction to RM.

### 93 Convolutional Neural Network

94 CNN's are primarily based on the convolution opera-

95 tion, which is a windowed pointwise multiplication

96 accumulation of multiple channels of input features

97 with a set of weights to generate output features. As

98 an example, for the input features  $\mathbf{I}$  and weights  $\mathbf{K}$  of

99 size  $N \times R_{\text{in}} \times C_{\text{in}}$  and  $M \times N \times 3 \times 3$ , respectively,

100 the convolution operation for the window at  $m$  (output

101 channel index),  $r$  (row), and  $c$  (column) is

$$\text{Conv}(\mathbf{I}, \mathbf{K})(m, r, c) = \sum_{n=0}^{N-1} \sum_{j=0}^2 \sum_{t=0}^2 \mathbf{K}_{m, n, j, t} \times \mathbf{I}_{n, r+j, c+t}$$

103 where  $M$  is the number of output channels,  $N$  is the

104 number of input channels,  $R_{\text{in}} \times C_{\text{in}}$  is the size of an

105 input feature map. The inference operation requires

106 convolution steps broken up with activation layers

107 composed of pooling layers to reduce the dimension-

108 ality of input matrices through average or maximum

109 value operations and ReLU function, a linear function

110 that will output the input if positive and zero other-

111 wise. Once these convolution layers are completed,

112 fully connected layers are used to provide the

114 classification result. The fully connected layers can be

115 mathematically written as  $\text{ReLU}(\mathbf{Wx} + \mathbf{b})$ .

116 Training of the CNN includes forward propagation,

117 loss backpropagation, and weight update. During the

118 forward propagation, which is the same as in infer-

119 ence, the values at each activation layer are stored for

120 the weight update. The loss is calculated by a loss

121 function, such as cross-entropy loss.<sup>7</sup> After calculating

122 the loss of the last layer, the loss is propagated layer

123 by layer until reaching the first layer of the CNN, by a

124 process that includes weight rotation, convolution,

125 and channelwise accumulation. Based on the loss

126 backpropagation, the weights are updated in each

127 layer individually. The operations in weight updates

128 are depthwise convolution, elementwise multiplica-

129 tion, and elementwise subtraction.

130 While deep learning with CNNs presumes calcula-

131 tions with floating-point values, CNN inference calcu-

132 lations can often be reduced to integer computation

133 with as few as 8-bits achieving reasonable accuracy.

134 Recent DRAM CIM work has shown that in many

135 cases this can be further reduced to ternary

$w \in \{-1, 0, 1\}$ <sup>5</sup> or even binary  $w \in \{0, 1\}$  computa-

136 tions<sup>8</sup> operations to replace the multiplications. How-

137 ever, online training for all but the simplest CNNs still

138 requires full 32-bit floating-point computations to

139 work properly. Without this accuracy, the weight

140 updates can be ineffective and possibly even

141 detrimental.

142 Next, we describe the basics of RM that provides

143 the foundation for CIM acceleration of CNN functions.

### 145 RM Fundamentals

146 Spintronic RM is made of ferromagnetic nanowires

147 consisting of many magnetic domains separated by

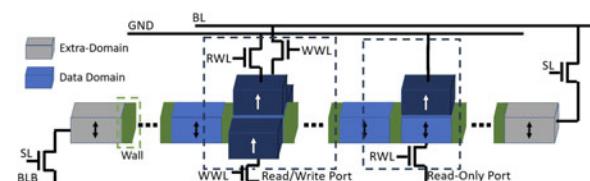

148 domain walls (DWs), as shown in Figure 1. Each

149 domain has its own magnetization direction such that

150 binary values are represented by the magnetization

151 direction of each domain, either parallel/antiparallel to

152 a fixed reference. For a planar nanowire, several

153 domains share one/few access point(s) (APs) for read

154 and write operations.<sup>9</sup> DW motion is controlled by

155 applying a short current pulse laterally along the nano-

156 wire governed by SL. An access requires shifting the

FIGURE 1. Anatomy of a DW memory nanowire.

**TABLE I.** POD-RACING compared to accelerators.

| Inference improvement compared to CIM |                    |               |                 |                  |

|---------------------------------------|--------------------|---------------|-----------------|------------------|

| Benchmark                             | Target             | Throughput    | Power           | Efficiency       |

|                                       |                    | FPS           | W               | FPS/W            |

| LeNet-5                               | DRAM <sup>6</sup>  | 8330          | –               | –                |

| Ternary <sup>5</sup>                  | POD-R              | 32075         | 0.028           | $1.1 \cdot 10^6$ |

| POD-R improvement                     |                    | 3.85 $\times$ | <i>Oslash</i> ; | <i>Oslash</i> ;  |

| AlexNet                               | DRAM <sup>5</sup>  | 84.8          | 2               | 42.4             |

| Ternary <sup>5</sup>                  | POD-R              | 490           | 0.93            | 526              |

| POD-R improvement                     |                    | 5.78 $\times$ | 1.94 $\times$   | 12.4 $\times$    |

| LeNet-5                               | RM <sup>11</sup>   | 59            | 0.017           | 13291            |

| Integer                               | POD-R              | 163           | 0.006           | 44169            |

| POD-R improvement                     |                    | 2.76 $\times$ | 2.33 $\times$   | 3.32 $\times$    |

| AlexNet                               | RM <sup>11</sup>   | 32.1          | 5.89            | 5.45             |

| Integer                               | POD-R              | 90.5          | 4.99            | 18.13            |

| POD-R improvement                     |                    | 2.81 $\times$ | 1.18 $\times$   | 3.33 $\times$    |

| Training improvement compared to FPGA |                    |               |                 |                  |

| Benchmark                             | Target             | Throughput    | Power           | Efficiency       |

|                                       |                    | GFLOPS        | W               | GFLOPS/W         |

| LeNet-10                              | FPGA <sup>17</sup> | 86.12         | 14.23           | 6.05             |

|                                       | POD-R              | 101.5         | 2.76            | 36.77            |

| POD-R improvement                     |                    | 1.18 $\times$ | 5.16 $\times$   |                  |

| AlexNet                               | FPGA <sup>18</sup> | 34.52         | 7.74            | 4.46             |

|                                       | POD-R              | 50.72         | 5.65            |                  |

| POD-R improvement                     |                    | 1.47 $\times$ | 1.36 $\times$   | 2.01 $\times$    |

| VGG-16                                | FPGA <sup>18</sup> | 46.99         | 7.71            |                  |

|                                       | POD-R              | 81.95         | 5.7             | 14.37            |

| POD-R improvement                     |                    | 1.74 $\times$ | 1.35 $\times$   |                  |

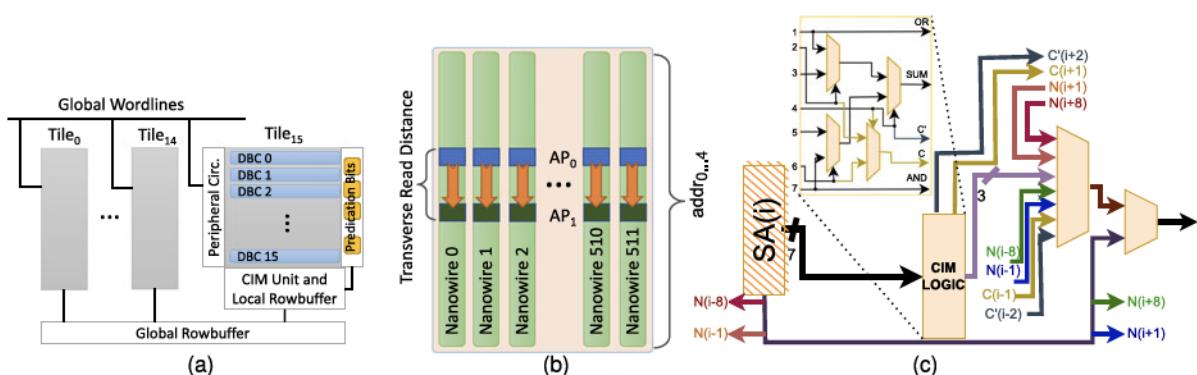

**FIGURE 2.** RM architecture following rank, bank, subarray, and tile conventions. All tiles are decomposed into DBCs with some tiles (e.g., one per subarray) augmented for transverse access and CIM. (a) Subarray built from tiles and DBCs. (b) DBC design: 2 APs for TR. (c) CIM unit for logic, arithmetic, and shifting.

target domain to align it with an AP (dark blue) and apply a current to read or write the target bit. To avoid data loss when shifting, overhead domains, represented in grey, are required.

RM, like many other novel memories, including resistive memory CIM crossbars,<sup>10</sup> has also received significant attention for CIM, particularly for deep learning.<sup>2,11,12</sup> In the next section, we describe the POD-RACING RM CIM approach that can operate at multiple levels of precision from binary/ternary weight inference to full floating-point precision online training.

## POD-RACING

The memory architecture concept behind POD-RACING is shown in Figure 2. We follow a DRAM-inspired hierarchical organization consisting of ranks and banks constructed from subarrays built with tiles [see Figure 2(a)]. Each tile is constructed from bundles of RM nanowires shifted together and referred to as a domain-block cluster (DBC).<sup>4,13</sup> A DBC can accommodate  $D$  rows with parallel access to all bits belonging to the same row through the parallel APs [see Figure 2 (b)].  $D \in \{16, 32, 64\}$  is the number of data domains per nanowire. Each tile maintains a  $512 \times 512$  shape, akin to DRAM. To enable CIM, a tile may be extended in two ways. A second AP is added to the DBCs in that tile to allow a current to traverse all the domains between the two APs indicated by the orange arrow [see Figure 2(b)]. If spaced within a prescribed transverse read distance (TRD), transverse read (TR) can distinguish between resistance levels based on the number of "1"s ( $v$ ) between the APs much like a multi-level cell.<sup>14</sup> Using TR, the local row buffer is extended with a CIM unit that retains a fast (bypass) path for a standard read, but can also convert the "1"s count from a TR into multioperand logic and the building blocks for arithmetic [shown for TRD = 7 in Figure 2 (c)].

FIGURE 3. FP multiplication in memory.

Multioperand AND and OR are naturally determined by sensing the highest (all ones) or lowest (all zeros) resistance levels. Operations of fewer operands can be accomplished by padding with ones or zeros as appropriate. Unlike prior processing using memory approaches POD-RACING includes logic to directly compute XOR from the 1's count, which also serves as the sum  $S$  for addition. All of these *bulk-bitwise* operations may be computed in parallel across the entire memory row. To support arithmetic we also can compute a carry  $C = \frac{v}{2} \bmod 2$  and super carry  $C' = \frac{v}{4}$  with minimal additional logic, which are needed to generate a sum of up to seven "1"s. Addition of TRD-2 operands may be computed directly by activating each nanowire in sequence. For nanowire  $N_i$ ,  $S_i$  is written to AP<sub>0</sub> of  $N_i$  ( $S_i \rightarrow N_{i,0}$ ), while similarly  $C_i \rightarrow N_{i+1,1}$  and  $C'_i \rightarrow N_{i+2,0}$  in parallel enabling a carry chain using navy and yellow connections in the CIM.<sup>12</sup>

The CIM block allows *logical* left and right shifts by both ones (orange and blue) and eight (red and green) positions. These *logical* shifts are different from RM nanowire shifting, which aligns different domains with APs (up and down). The shift by one position along with a small number of predication bits<sup>15</sup> to support multiplication using partial product addition. For more

FIGURE 4. FP addition flow. Steps in blue, green, and red are operating on the mantissa, exponent, and sign bits, respectively.

256 than TRD-2 operands, computing the  $S$ ,  $C$ , and  $C'$  bits

257 in parallel reduces seven operands to three, allowing

258 multiplication and reduction over addition to being

259 computed in  $O(n)$  time where  $n$  is the operand width.

260 To clarify these capabilities from prior work,<sup>12</sup> detailed

261 algorithms for these arithmetic operations are pre-

262 sented in Algorithm 1 of the supplementary material,

263 which can be found in the Computer Society Digital

264 Library at <http://doi.ieeecomputersociety.org/10.1109/MM.2022.3195761>.

265

266 This CIM approach forms the basis to conduct

267 binary, ternary, and integer/fixed point CNN inference.

268 In the next sections, we describe floating-point multi-

269 plication and reduction over addition required for

270 accurate backpropagation used for CNN online

271 training.

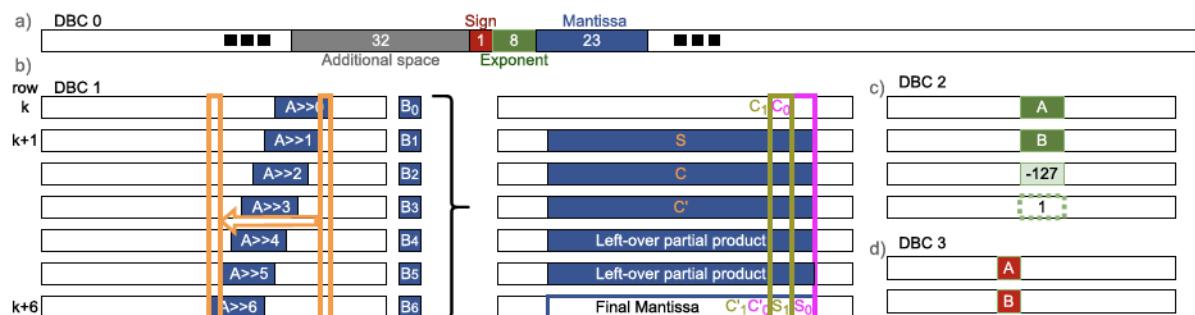

## 272 273 FLOATING-POINT TWO- 274 OPERANDS MULTIPLICATION

275 POD RACING implements 32-bit floating-point multi-

276 plication on operands composed of packed 23-bit

277 mantissas represented in blue, 8-bit exponents (biased

278 by  $2^8 - 1$ ) in green, and a sign bit in red, in rows with

279 64-bit alignment, as shown in Figure 3(a). Data from

280 multiple input channels are packed in 512-bit rows.

281 Each operation executes on eight 64-bit values allow-

282 ing channelwise parallelism regardless of window size

283 or stride. Convolution across multiple windows in par-

284 allel is possible across different subarrays.<sup>12</sup>

285 First, the mantissa  $M_i$ , exponent  $E_i$ , and sign  $S_i$  of

286 each operand  $i \in \{A, B\}$  are masked off with an AND

287 operation, the leading “1” restored with an OR operation

288 and stored in separate DBCs. In Figure 3(b), using inte-

289 ger operations we multiply the two 24-bit mantissas

290 by using operand B and the predication registers to

291 store a shifted copy of A or “0”s depending on each bit

292 of B. We sum the partial products in two major steps.

293 First, we create for all bits in parallel a sum  $\vec{S}$ , carry  $\vec{C}$ ,

294 and supercarry  $\vec{C}'$  vector, using the  $S$ ,  $C$ , and  $C'$  opera-

295 tors, respectively, for each of seven partial products.

296 We continue to reduce the generated  $\vec{S}$ ,  $\vec{C}$ , and  $\vec{C}'$  until

297 we have  $\leq 5$  operands, as shown in the right half of

298 Figure 3(b). Here the final sum is created by summing

299 each bit position carrying  $C$  and  $C'$  where the final

300 sum that is the mantissa product expanded to 48-bits.

301 Because  $1.0 \leq M_i < 2.0$  then it follows that their

302 product  $P$  is  $1.0 \leq P < 4.0$ .

303 To normalize  $P \geq 2.0$  uses the top bit  $t$  to govern a

304 predicated normalization right shift by one [see

305 Figure 2(c)]. Then as shown in Figure 3(c), we add the

306 exponents  $E = E_A + E_B + -127 + t$  using multioper-

307 and integer arithmetic where  $-127$  counteracts the

308 exponent offset and  $t$  is from  $P$  normalization. Finally,

309 to determine the resulting sign of the multiplication,

310 as shown in Figure 3(d), we execute  $S = S_A \text{ XOR } S_B$ . A

311 detailed algorithm is presented in Algorithm 2 of the

312 supplementary material, available online. We leave  $M$ ,

313  $E$ , and  $S$ , decomposed to facilitate reduction over

314 floating-point addition described in the next section.

315

## 316 317 FLOATING-POINT 318 MULTIOPERANDS ADDITION

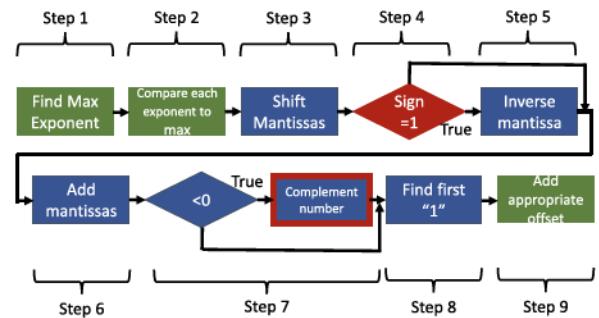

319 FP addition requires nine steps, as shown in Figure 4.

320 Step 1 determines the maximum exponent within the

321 convolution window. The maximum exponent is deter-

322 mined by the searching for “1”s using TR at each posi-

323 tion from most to least significant, if a “1” is present

324 from any exponent in that bit position, all exponents

325 without that bit set are set to zero eliminating all but

326 the maximum value, this process is also used for

327 determining the maximum value during pooling.<sup>12</sup>

328 In step 2 each local exponent is subtracted from

329 the maximum. In step 3 this difference is used to gov-

330 ern right shifts to normalize the corresponding mantis-

331 sas. This is implemented in POD-RACING by copying

332 each difference bit from the lowest to highest into the

333 predication register and executing a series of predi-

334 cated logical right shifts (read and shift using the CIM

335 unit). Each subsequent bit requires increasing the shift

336 distance by powers of two for which we can leverage

337 the orange  $N(i-1)$  or/and red  $N(i-8)$  connections in

338 Figure 2(c) as appropriate.

339 In step 4, the sign bit of each operand is used as a

340 predication value to invert the mantissa using an XOR

341 operation with all “1”s. In step 5, the same predication

342 register governs storing one. These two rows are now

343 necessary for representing the signed representation

344  $M_i$ . In step 6,  $M = \sum_i M_i$ , where each  $M_i$  is repre-

345 sented as two rows, is conducted as discussed in the

346 prior section for adding partial products. In step 7, if

347 the most significant bit of  $M$  is “1,” we complement

348 the number, using this bit as a predicated inversion

349 operation and then add one.

350 In Steps 8 and 9, we normalize the mantissa to 23

351 bits and adjust the exponent based on the normaliza-

352 tion. There are three cases for  $M$ , the leading “1” is

353 higher than bit position 48 requiring to increase the

354 exponent and shift  $M$  right, it is lower than 48 but

355 higher than 23 requiring decreasing the exponent and

356 shift  $M$  right, or it is lower than 23 requiring decreasing

357 the exponent and shifting  $M$  left. We accomplish this

358 by creating a copy of  $M$ . Each cycle  $M$  is shifted left

359 and predicated instructions are issued that are gov-

360 erned by seeing the first “1” to adjust the exponent

361

358 and after seeing the first "1" to shift the actual mantissa. Unfortunately, due to space limitations we were

359 unable to provide precise details in the article, we

360 describe the detailed algorithms for these operations

361 in Algorithm 3 of the supplementary material, available

362 online, which follows the basic flow and intuition laid

363 out here.

## 365 ADDITIONAL OPERATIONS FOR 366 BACKPROPAGATION

367 During backpropagation weight matrices must be

368 rotated 180°, which is equivalent to swapping the values

369 of these relatively small (3×3 up to 11×11) along

370 the vertical and horizontal bisecting lines of the

371 matrix. We use POD-RACING PIM to mask off the individual

372 values of each row using AND, logically shift to the correct

373 position, and recombine using OR. In addition, the weight update operation:  $W' = W - L_R \times \Delta W$  where the new weight  $W'$  is a function of the previous weight  $W$  the learning weight  $L_R$  and the weight difference  $\Delta W$  calculated via gradient descent method. We also use floating-point POD-RACING CIM to compute this function.

## 380 RESULTS

381 POD-RACING enables multiple precision modes from

382 binary weight used for inference to floating-point

383 required for effective training. FPGAs can also use

384 multiple precision modes, however, it has been demonstrated

385 by previous work that DRAM CNN-inference is faster and consumes less energy than FPGA CNN-inference.<sup>16</sup> Thus, we compare POD-RACING for inference against the state-of-the-art DRAM CIM using ternary weights<sup>5,6</sup> and RM using integer weights,<sup>11</sup> where the RM and DRAM (DDR3-1600) have a 1 and 1.6-GHz clock frequency, respectively. We compare POD-RACING for training using floating-point operations against energy-efficient FPGAs suitable for edge systems: Xilinx ZU19EG (LeNet-10)<sup>17</sup> and ZCU102 (AlexNet and VGG-16).<sup>18</sup> We used CIFAR-10 for LeNet-10 and ImageNet for AlexNet and VGG16 as in prior work.<sup>18</sup> The energy and latency parameters of accessing RM and TR in POD-RACING are provided by Yu et al.<sup>2</sup> and Roxy et al.<sup>14</sup> The latency and energy consumption for the CIM unit architecture extensions in Figure 2 were determined by implementing the design with the Cadence ASIC Flow targeting 45-nm technology. POD-RACING simplifies the CIM-unit but expands the shifting capability over prior work on integer CIM using RM requiring an area overhead of 10% creating one CIM-enabled tile per subarray.<sup>12</sup>

Like prior work, we presume the memory controller issues CIM operations from dedicated CIM instructions, which can be included directly in the software code as compiler directives. These instructions indicate the source, destination, the operation, and block size.<sup>12,19</sup> Either the virtual memory management system can be made aware of these instructions or they can be assigned to previously declared regions of CIM memory like in memory mapped I/O. In many cases, such as addition operations the memory controller must issue several instructions in sequence, governed by the block size, such as addition with the carry chain, finding the maximum, and predicated operations. Algorithms 1-3 in the supplementary document, available online, the detailed behavior of the memory controller operations required for these instructions.

## 423 CNN Inference

During the CNN inference phase, precision can be tuned based on the required accuracy. Reduced precision can provide a lower latency result *in situ*, which is particularly valuable for edge networks with small batch sizes. For instance, integer, ternary, or binary weight calculation reduces the complexity of addition and multiplication to simpler integer functional units while providing sufficient accuracy compared to more expensive floating-point computation. In fact, ternary and binary forms convert multiplication to much simpler bulk-bitwise (e.g., XOR) operations.

Using bulk-bitwise ternary weight CNN inference POD-RACING is more than 3× faster than the state-of-the-art DRAM CIM<sup>5,6</sup> with an approximately 2× power advantage leading to an order of magnitude efficiency advantage for AlexNet<sup>a</sup>. In fact, ternary weight CNN inference with POD-RACING is 2–3× faster than even simpler binary weight CNN inference using DRAM CIM.<sup>12</sup> Using integer operations, POD-RACING can outperform by nearly 3× and provides more than 3× the efficiency of the latest RM CIM.<sup>11</sup> The results are detailed in Table 1.

## 446 CNN Training

Given *in situ* training for low latency with small batch sizes and to maintain SWaP of edge systems GPUs may not be practical for their relatively high power. Sending these large datasets to the cloud for GPU acceleration is also impractical. Given CIM has yet to demonstrate CNN training with floating-point

<sup>a</sup>Power and energy data were not reported for the LeNet-5 DRAM CIM implementation<sup>6</sup> and is noted as a “–” in Table 1.

453 precision, we compare with FPGAs accelerators,

454 which are emerging for *in situ* edge CNN training.<sup>17,18</sup>

455 POD-RACING is competitive, even outperforming

456 FPGAs by 18%–74% with a significant improvement in

457 power. We demonstrate a more than 2 $\times$  improvement in

458 efficiency even as the complexity of the CNN

459 increases; POD-RACING for AlexNet is 2 $\times$  more effi-

460 cient, while VGG-16 is 2.36 $\times$  more efficient. Thus, not

461 only is POD-RACING demonstrating that CNN training

462 is possible using CIM, it may even be more practical

463 than FPGAs. When coupled with the high capacity and

464 low-energy consumption of RM-based memory, the

465 capabilities for SWaP constrained edge acceleration

466 of deep learning and beyond are impressive and wor-

467 thy of further exploration.

## 468 CONCLUSION

469 POD-RACING is the first, to the best of our knowledge,

470 approach to enable full CNN architectures in memory,

471 with multiple precision capabilities suitable for tuning

472 both inference and training operations. While floating-

473 point operations have always been a major roadblock

474 for in-memory processing, POD-RACING can perform

475 these operations efficiently at a speed and energy

476 consumption improves over FPGA technology. In par-

477 ticular, POD-RACING is between 18% and 74% faster

478 in terms of throughput, and at least 26% better in

479 terms of energy, resulting in an efficiency improve-

480 ment of more than 2 $\times$  compared to the state-of-the-

481 art FPGAs for small to moderate-sized CNNs. POD-

482 RACING is the first CIM architecture that is suffi-

483 ciently reconfigurable to provide capabilities and

484 improvements over the state-of-the-art techniques for

485 both *in situ* CNN inference and training for edge

486 computing.

## 487 ACKNOWLEDGMENTS

488 This work was supported in part by the <http://dx.doi.org/10.13039/100000001NSF> under Grant CNS-

489 1822085, Grant CNS-2133267, the <http://dx.doi.org/10.13039/100009226>National Security Agency , and

490 Laboratory of Physical Sciences. The authors would

491 like to thank Dr. Xulong Tang and Sheng Li for their

492 consultation on this manuscript.

## 495 REFERENCES

1. S. S. P. Parkin, S. S. Parkin, M. Hayashi, and L. Thomas, "Magnetic domain-wall Racetrack memory," *Science*, vol. 320, no. 5873, pp. 190–194, 2008.

2. H. Yu *et al.*, "Energy efficient in-memory machine learning for data intensive image-processing by non-volatile domain-wall memory," in *Proc. 19th Asia, South Pacific Des. Automat. Conf.*, 2014, pp. 191–196.

3. D. Wang *et al.*, "Shift-optimized energy-efficient Racetrack-based main memory," *J. Circuits, Syst. Comput.*, vol. 27, no. 05, 2018, Art. no. 1850081.

4. A. A. Khan *et al.*, "Shiftsreduce: Minimizing shifts in Racetrack memory 4.0," *ACM Trans. Archit. Code Optim.*, vol. 16, no. 4, pp. 1–23, 2019.

5. Q. Deng *et al.*, "DRACC: A dram based accelerator for accurate CNN inference," in *Proc. 55th Annu. Des. Automat. Conf.*, 2018, pp. 1–6.

6. X. Xin, Y. Zhang, and J. Yang, "Elp2im: Efficient and low power bitwise operation processing in dram," in *Proc. IEEE Int. Symp. High Perform. Comput. Archit.*, 2020, pp. 303–314.

7. P.-T. De Boer *et al.*, "A tutorial on the cross-entropy method," *Ann. Operations Res.*, vol. 134, no. 1, pp. 19–67, 2005.

8. J. Sim, H. Seol, and L. Kim, "NID: Processing binary convolutional neural network in commodity dram," in *Proc. IEEE/ACM Int. Conf. Comput.-Aided Des.*, 2018, pp. 1–8.

9. Y. Zhang *et al.*, "Perpendicular-magnetic-anisotropy CoFeB Racetrack memory," *J. Appl. Phys.*, vol. 111, no. 9, 2012, Art. no. 093925.

10. P. Chi *et al.*, "Prime: A novel processing-in-memory architecture for neural network computation in ReRAM-based main memory," *ACM SIGARCH Comput. Architecture News*, vol. 44, no. 3, pp. 27–39, 2016.

11. B. Liu *et al.*, "An efficient Racetrack memory-based processing-in-memory architecture for convolutional neural networks," in *Proc. IEEE Int. Symp. Parallel Distrib. Process. Appl., IEEE Int. Conf. Ubiquitous Comput. Commun.*, 2017, pp. 383–390.

12. S. Ollivier, S. Longofono, P. Dutta, J. Hu, S. Bhanja, and A. K. Jones, "CORUSCANT: Fast efficient processing-in-Racetrack memories," in *Proc. IEEE/ACM Int. Symp. Microarchitecture*, 2022.

13. R. Venkatesan *et al.*, "Tapecache: A high density, energy efficient cache based on domain wall memory," in *Proc. ACM/IEEE Int. Symp. Low Power Electron. Des.*, 2012, pp. 185–190.

14. K. Roxy, S. Ollivier, A. Hoque, S. Longofono, A. K. Jones, and S. Bhanja, "A novel transverse read technique for domain-wall 'Racetrack' memories," *IEEE Trans. Nanotechnol.*, vol. 19, pp. 648–652, 2020.

15. M. Lenjani *et al.*, "Fulcrum: A simplified control and access mechanism toward flexible and practical *in-situ* accelerators," in *Proc. IEEE Int. Symp. High Perform. Comput. Archit.*, 2020, pp. 556–569.

551 16. L. Jiang, M. Kim, W. Wen, and D. Wang, "XNOR-POP: A

552 processing-in-memory architecture for binary

553 convolutional neural networks in wide-io2 dram," in

554 *IEEE/ACM Int. Symp. Low Power Electron. Des.*, 2017,

555 pp. 1–6.

556 17. Z. Liu, Y. Dou, J. Jiang, Q. Wang, and P. Chow, "An

557 FPGA-based processor for training convolutional

558 neural networks," in *Proc. Int. Conf. Field

559 Programmable Technol.*, 2017, pp. 207–210.

560 18. Y. Tang et al., "EF-Train: Enable efficient on-device

561 CNN training on FPGA through data reshaping for

562 online adaptation or personalization," *ACM Trans. Des.

563 Automat. Electron. Syst.*, vol. 27, no. 5, 2022, Art. no. 49.

564 19. V. Seshadri et al., "Ambit: In-memory accelerator for

565 bulk bitwise operations using commodity dram

566 technology," in *Proc. 50th Annu. IEEE/ACM Int. Symp.

567 Microarchit.*, 2017, pp. 273–287.

Q4 567

568 **SÉBASTIEN OLLIVIER** research interests include novel mem-

569 ory reliability, computing units for processing in memory and

570 application acceleration. He has authored or coauthored sev-

571 eral articles focusing on domain-wall memory. Ollivier

572 received his Ph.D. degree in electrical and computer engi-

573 neering from the University of Pittsburgh, Pittsburgh, PA,

574 USA. Contact him at [sbo15@pitt.edu](mailto:sbo15@pitt.edu).

575 **XINYI ZHANG** research interests include software-hardware

576 code-design for machine learning algorithms, deep-learning

577 algorithm compression, and FPGA high-level synthesis. Zhang

578 received his Ph.D. degree in electrical and computer engi-

579 neering from the University of Pittsburgh, Pittsburgh, PA,

580 USA. Contact him at [xinyizhang@pitt.edu](mailto:xinyizhang@pitt.edu).

581 **YUE TANG** is currently a Ph.D. candidate with the University

582 of Pittsburgh, Pittsburgh, PA, 15260, USA, in electrical and

583 computer engineering. Her research interests include FPGA-

584 based CNN training and on-device artificial intelligence. Tang 584

585 received her M.S. degree from the School of Automation Sci- 585

586 ence and Electrical Engineering, Beihang University, Beijing, 586

587 China. Contact her at [yut51@pitt.edu](mailto:yut51@pitt.edu). 587 **Q5**

588 **CHAYANIKA CHOWDHURI** is a research volunteer with the 588

589 University of Pittsburgh, Pittsburgh, PA, 15260, USA, in electri- 589

590 cal and computer engineering under the supervision of Pro- 590

591 fessor Alex K. Jones. Her research interests focusses on 591

592 novel memories as domain-wall memory. Contact her at 592

593 [roc74@pitt.edu](mailto:roc74@pitt.edu). 593 **Q6**

594 **JINGTONG HU** is currently an Associate Professor and Wil- 594

595 liam Kepler Whiteford Facultyfellow in the Department of 595

596 Electrical and Computer Engineering, University of Pitts- 596

597 burgh, Pittsburgh, PA, 15260, USA. His current research inter- 597

598 ests include hardware/software co-design for machine 598

599 learning algorithms, on-device AI, embedded systems.. Hu 599

600 received his Ph.D. degree in computer science from the Uni- 600

601 versity of Texas at Dallas, Richardson, TX, USA. He is a senior 601

602 member of IEEE. Contact him at [jthu@pitt.edu](mailto:jthu@pitt.edu). 602

603 **ALEX K. JONES** is a professor of ECE and CS with the Univer- 603

604 sity of Pittsburgh, Pittsburgh, PA, 15260, USA. He is currently 604

605 serving as a program director with the U.S. NSF in the CNS 605

606 Division of the CISE Directorate. His research interests 606

607 include compilation for configurable systems and architec- 607

608 tures, scaled and emerging memory, reliability, fault toler- 608

609 ance, and sustainable computing. He has authored or 609

610 coauthored more than 200 publications in these areas. His 610

611 research is funded by the NSF, DARPA, NSA, and industry. 611

612 Jones received his Ph.D. degree in ECE from Northwestern 612

613 University, Evanston, IL, USA. He is a senior member of IEEE 613

614 and ACM. Contact him at [akjones@pitt.edu](mailto:akjones@pitt.edu). 614