1 IEEE CICC 2022

## A Fully In-Package 4-Phase Fixed-Frequency DAB Hysteretic Controlled DC-DC Converter with Enhanced Efficiency, Load Regulation and Transient Response

Lei Zhao, Junyao Tang, and Cheng Huang

Iowa State University, Ames, IA, US

Multiphase DC-DC converters have been widely used to deliver more power more efficiently with smaller ripples and faster large-signal dynamic responses [1-5]. In terms of closed-loop voltage regulation, traditional linear PWM control has limited small-signal bandwidth, which is further compromised to ensure stability at different loading conditions with different PVT and LC variations. Non-linear control, such as hysteretic control, does not have small-signal bandwidth limitations nor stability concerns, thus can potentially achieve a faster dynamic performance. Among different topologies, current-mode hysteretic control has been adopted in 4-phase converters [2, 3]. To ensure proper operation at higher frequency, they require careful matching between the inductor current-sensing RC networks and the inductance and parasitic DC resistance (DCR) of the power inductors [2], or more complex RC sensing networks [3]. Also, the converters in [2-4] did not include current balancing, which could introduce unbalanced current due to mismatches in power transistors, control timing, and power inductors among different phases, and result in significant compromise in efficiency. To maintain optimum efficiency over a wide loading range, active-phase-count (APC) control has been introduced in [1, 2, 4]. In [4], APC is realized by a multi-bit ADC, which increases the design complexity and power consumption. Double-adaptive-bound (DAB) hysteretic control in [6] has demonstrated fast transient responses, however, it only works in single phase, and the operation is very sensitive to the delay of the comparator, the gate driver and other circuits in the control path, and the matching of the RC filters, especially at higher switching frequencies. Besides, due to the lack of a high-gain amplifier, output voltage DC accuracy is also compromised in hysteretic controlled switching converters, with a 40mV/1A load regulation in [2].

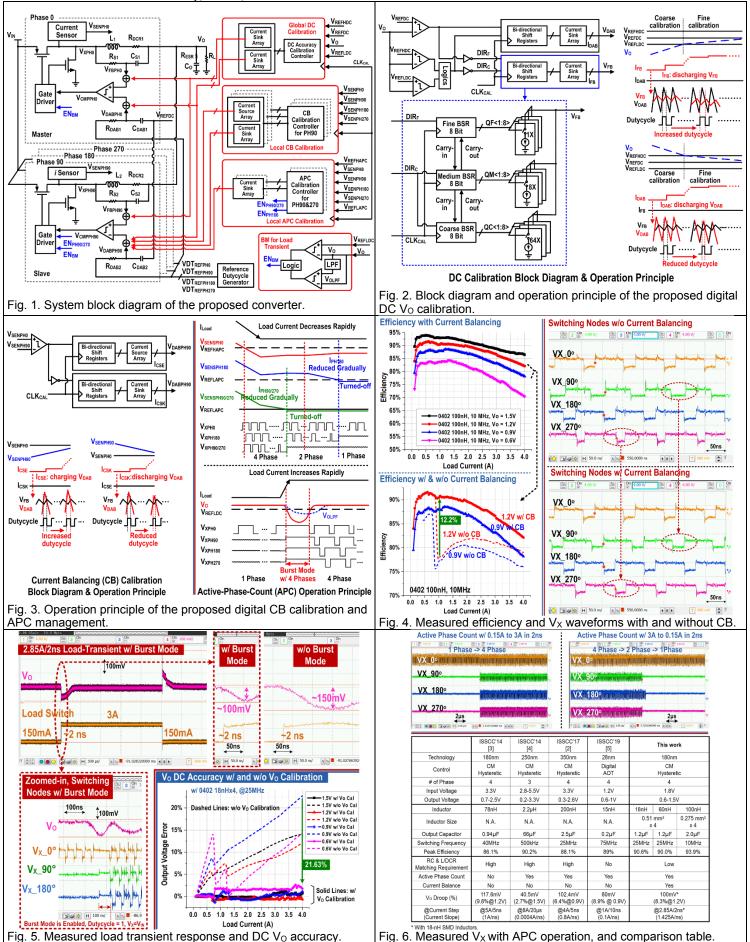

To address these limitations, this paper proposes a 4-phase DAB hysteretic controlled converter with digital DC calibration, current balancing, and APC management (Fig. 1). The DAB control achieves fixed-frequency operation and the digital calibration functions are all based on similar bidirectional-shift registers-controlled logics. This makes the converter easily extendable to adapt more phases with minimum design complexity overhead. Fig. 1 shows the system block diagram of the proposed converter. Two RC filters (RDABCDAB, RSCS) are used for establishing the comparison boundary V<sub>DAB</sub> and V<sub>FB</sub> to regulate the output voltage. Instead of using well-matched RCs [6], RsCs is chosen to be 4 times of RDABCDAB (Rs=RDAB, Cs=4\*CDAB), with which the amplitude of  $V_{DAB}$  is larger than  $V_{FB}$  for a higher tolerance to circuit delays from  $V_{CMP}$  to  $V_X$  to work at higher frequency. In this work, matching of RsCs to 4 RDABCDAB or with the L/DCR is not needed due to the existence of the digital calibrations, thus, the requirement of power inductors can be much more flexible.

The block diagram and operation principle of the digital DC output voltage ( $V_O$ ) calibration is shown in Fig. 2. A dead-zone boundary between  $V_{REFHDC}$  and  $V_{REFLDC}$  is set for DC calibration. To achieve a wide range as well as a fine resolution, the bidirectional-shift-registers (BSRs) are designed including 8-bit fine, 8-bit medium and 8-bit coarse segments with carry in/out operations. When  $V_O$  is beyond the dead-zone region, the medium and coarse BSRs shift the output codes to control the current sink array to adjust the Slope of  $V_{DAB}$  or  $V_{FB}$  in all 4 phases globally. If  $V_O$  is lower than  $V_{REFLDC}$ ,  $I_{FB}$  will be increased to discharge  $V_{DAB}$ . The cross-point between  $V_{DAB}$  will be controlled to discharge  $V_{DAB}$ . The cross-point between  $V_{DAB}$  and  $V_{FB}$  changes accordingly when the slope of  $V_{DAB}$  or  $V_{FB}$  changes, resulting in an increase or decrease of duty cycle for accuracy calibration. When  $V_O$  is calibrated into the dead-zone, the fine BSRs continue to further reduce the DC offset.

Current balancing (CB) digital calibration is also developed in this work (the left of Fig. 3). Four current sensors, with one in each phase, are designed to sense the high-side power PMOS current. By comparing the sensed voltage of Phase 90, 180 and 270 ( $V_{\text{SENPH90}}$ ,  $V_{\text{SENPH180}}$  and  $V_{\text{SENPH270}}$ , respectively) with the sensed voltage of Phase 0 ( $V_{\text{SENPH0}}$ ), the BSRs operate to adjust the duty cycle of each

phase locally to maintain the same amount of current as Phase 0. Take CB calibration for Phase 90 as an example. If  $V_{SENPH90}$  is smaller than  $V_{SENPH0}$ , only  $I_{CSE}$  increases to charge  $V_{DABPH90}$  to increase the duty cycle of Phase 90 while  $I_{CSK}$  remains 0. If  $V_{SENPH90}$  is larger than  $V_{SENPH90}$ , only  $I_{CSK}$  increases to discharge  $V_{DABPH90}$  to reduce the duty cycle while  $I_{CSE}$  remains 0.

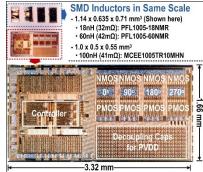

Chip photo with 0402 miniature SMD inductors in the same scale.

APC management is also developed in this work (the right of Fig.3). If  $V_{\text{SENPH0}}$  is smaller than  $V_{\text{REFHAPC}}$ , only Phase 0 is activated. If the load current increases such that  $V_{\text{O}}$  drops below  $V_{\text{REFLDC}}$ , the burstmode (BM) will be activated for the full 4-phase operation with 100% duty cycle to charge the power inductors with full thrust. The BM will be disabled when  $V_{\text{O}}$  starts to recover, meaning that the inductor current has been increased larger than the load current. This is achieved by comparing  $V_{\text{O}}$  with  $V_{\text{OLPF}}$ , a delayed version of  $V_{\text{O}}$ . In terms of heavy-to-light load change, when load current steps down to light load rapidly, the system will first turn off Phase 90 and Phase 270. If  $V_{\text{SENPH0}}$  is still lower than  $V_{\text{REFHAPC}}$ , after a preset settling period, Phase 180 will also be turned off. To avoid significant output voltage fluctuations, the duty cycle of the corresponding phase(s) will be reduced gradually. When the sensed voltage is lower than  $V_{\text{REFLAPC}}$ , the corresponding phase(s) will be completely turned off.

The proposed converter has been fabricated in 180-nm CMOS and measured at 10MHz and 25MHz with 18-to-100-nH 0402 inductors for full in-package integration (chip & inductor photo above), converting 1.8V to 0.6V-1.5V. Fig. 4 shows the measured efficiency versus load currents at different voltages. A 93.9% peak efficiency is achieved with 100-nH 0402 inductors. Up to 12.2% efficiency improvement and better V<sub>X</sub> duty-cycle matching in measured waveforms are observed by enabling the CB calibration. Fig. 5 shows the measured load transient performance with fast current steps of 2.85A/2ns. The measured droop is 100mV with BM, which is 33.3% smaller than the 150 mV without BM. Fig. 5 also shows the steadystate DC Vo accuracy comparison with and without the DC calibration. A significant improvement of 21.63% is observed with the calibration, with error remains within 2.5% in the full loading range with different voltages. This verified that the proposed DC calibration can effectively relax the accuracy and matching requirement of the RC current-sensing network in previous current-mode hysteretic designs, while remaining a load regulation comparable to designs with linear control. Fig. 6 shows the measured V<sub>X</sub> waveforms in fast load transients for APC demonstration, as well as the comparison table with recent multiphase non-linearly controlled switching converters. This work achieves higher efficiency using smaller-thanthe-chip inductors with relaxed tolerances in L, matching and DCR, and decent transient responses with faster current steps.

Acknowledgement: This work is supported by National Science Foundation under project 2007154.

## References:

[1] C. Huang *et al.*, "An 82.4% Efficiency Package-Bondwire-Based Four-Phase Fully Integrated Buck Converter with Flying Capacitor for Area Reduction." *ISSCC*, Feb. 2013.

for Area Reduction," *ISSCC*, Feb. 2013.

[2] B. Lee *et al.*, "A 25MHz 4-Phase SAW Hysteretic DC-DC Converter with 1-Cycle APC Achieving 190ns t<sub>settle</sub> to 4A Load Transient and Above 80% Efficiency in 96.7% of the Power Range," *ISSCC*, Feb. 2017.

[3] M. K. Song et al., "A 6A 40MHz Four-Phase ZDS Hysteretic DC-DC Converter with 118mV Droop and 230ns Response Time for a 5A/5ns Load Transient," ISSCC, Feb. 2014

[4] C. K. The *et al.*, "A 3-Phase Digitally Controlled DC-DC Converter with 88% Ripple Reduced 1-Cycle Phase Adding/Dropping Scheme and 28% Power Saving CT/DT Hybrid Current Control," *ISSCC*, 2014. [5] M. Choi *et al.*, "A Synthesizable Digital AOT 4-Phase Buck Voltage Regulator for Digital Systems with 0.0054mm<sup>2</sup> Controller and 80ns Recovery Time," *ISSCC*, Feb. 2019.

[6] K. Wei et al., "A 10-MHz DAB Hysteretic Control Switching Power Converter for 5G IoT Power Delivery," JSSC, Jul. 2021.