## Schottky contacts to N-polar GaN with SiN interlayer for elevated temperature operation

Cite as: Appl. Phys. Lett. 120, 172109 (2022); https://doi.org/10.1063/5.0083588 Submitted: 27 December 2021 • Accepted: 19 April 2022 • Published Online: 29 April 2022

🤟 Dolar Khachariya, 🔟 Dennis Szymanski, Pramod Reddy, et al.

#### COLLECTIONS

Paper published as part of the special topic on Wide- and Ultrawide-Bandgap Electronic Semiconductor Devices

### ARTICLES YOU MAY BE INTERESTED IN

Record >10 MV/cm mesa breakdown fields in Al<sub>0.85</sub>Ga<sub>0.15</sub>N/Al<sub>0.6</sub>Ga<sub>0.4</sub>N high electron mobility transistors on native AIN substrates

Applied Physics Letters 120, 172106 (2022); https://doi.org/10.1063/5.0083966

AIN/GaN/InGaN coupling-channel HEMTs with steep subthreshold swing of sub-60 mV/ decade

Applied Physics Letters 120, 173502 (2022); https://doi.org/10.1063/5.0088585

The observation of Gaussian distribution and origination identification of deep defects in AlGaN/GaN MIS-HEMT

Applied Physics Letters 120, 172107 (2022); https://doi.org/10.1063/5.0088928

# Schottky contacts to N-polar GaN with SiN interlayer for elevated temperature operation

Cite as: Appl. Phys. Lett. **120**, 172109 (2022); doi: 10.1063/5.0083588 Submitted: 27 December 2021 · Accepted: 19 April 2022 · Published Online: 29 April 2022

Dolar Khachariya, <sup>1</sup> (i) Dennis Szymanski, <sup>2</sup> (i) Pramod Reddy, <sup>3</sup> Erhard Kohn, <sup>2</sup> Zlatko Sitar, <sup>2,3</sup> (i) Ramón Collazo, <sup>2</sup> and Spyridon Pavlidis <sup>1,a)</sup> (i)

#### **AFFILIATIONS**

Note: This paper is part of the APL Special Collection on Wide- and Ultrawide-Bandgap Electronic Semiconductor Devices.

a) Author to whom correspondence should be addressed: spavlidis@ncsu.edu

#### **ABSTRACT**

In this Letter, we unveil the high-temperature limits of N-polar GaN Schottky contacts enhanced by a low-pressure chemical vapor deposited (LPCVD) SiN interlayer. Compared to conventional Schottky diodes, the insertion of a 5 nm SiN lossy dielectric interlayer in-between Ni and N-polar GaN increases the turn-on voltage ( $V_{ON}$ ) from 0.4 to 0.9 V and the barrier height ( $\phi_B$ ) from 0.4 to 0.8 eV. This modification also reduces the leakage current at zero bias significantly: at room temperature, the leakage current in the conventional Schottky diode is  $>10^3$  larger than that observed in the device with the SiN interlayer, while at 200 °C, this ratio increases to  $10^5$ . Thus, the rectification ratio ( $I_{ON}/I_{OFF}$ ) at  $\pm 1.5$  V reduces to less than one at 250 °C for the conventional Schottky diode, whereas for SiN-coated diodes, rectification continues until 500 °C. The I–V characteristics of the diode with an SiN interlayer can be recovered after exposure to 400 °C or lower. Contact degradation occurs at 500 °C, although devices are not destroyed yet. Here, we report N-polar GaN Schottky contact operation up to 500 °C using an LPCVD SiN interlayer.

Published under an exclusive license by AIP Publishing. https://doi.org/10.1063/5.0083588

N-polar GaN has demonstrated great potential for electronic and optoelectronic devices. <sup>1-6</sup> One example is for high electron mobility transistors (HEMTs), where the two-dimensional electron gas (2DEG) is formed with an AlGaN back-barrier because of the opposite polarization field compared to Ga-polar GaN. <sup>1,3</sup> This permits superior scaling and reduced contact resistance for the source and drain, leading to N-polar GaN HEMTs now experimentally outperforming Ga-polar GaN HEMTs. <sup>7,8</sup> Another interesting application of N-polar GaN material is in GaN-based superjunction devices using a lateral polar junction structure where Ga- and N-polar GaN could be p- and n-type doped, respectively, because of asymmetric defect incorporation. <sup>9-12</sup>

In Schottky barrier diodes and HEMTs, the quality of the Schottky contact plays an essential role in determining the device's performance. Usually, a higher Schottky barrier is required to reduce leakage. The opposite polarization field in N-polar vs Ga-polar GaN means that the barrier height in N-polar GaN is lower compared to that observed in Schottky contacts to Ga-polar GaN. <sup>13–19</sup> This low barrier leads to higher reverse bias leakage and limits high-temperature

operation. Liu *et al.* recently demonstrated that Ru-based Schottky contacts yield a higher Schottky barrier and reduce the reverse bias leakage compared to other contact schemes.<sup>20</sup> The temperature-dependent I–V (I–V–T) characteristics were reported up to 175 °C. To date, however, there are no reports in the literature of N-polar GaN Schottky diodes operating at higher temperatures (>200 °C), which would both not only facilitate deployment of these devices in harsh environments but also give way to more reliable performance overall. Moreover, relaxed cooling requirements eliminate the need for bulky cooling systems, making it easier to integrate these systems into automotive, aerospace, and energy production sectors.<sup>21</sup> The well-documented chemical sensitivity of N-polar GaN presents an additional hurdle to obtaining high-temperature performance.<sup>19</sup>

We recently demonstrated that a thin SiN layer placed between the N-polar GaN and Schottky metal via LPCVD passivates the surface polarization charge and, critically, raises the barrier height via a unique amphoteric miniband<sup>22,23</sup> and a tunable surface termination.<sup>24</sup> Here, we have extended this technique by reducing the thickness of the LPCVD SiN interlayer to improve the performance of N-polar

Department of Electrical and Computer Engineering, North Carolina State University, Raleigh, North Carolina 27695-7911, USA

<sup>&</sup>lt;sup>2</sup>Department of Materials Science and Engineering, North Carolina State University, Raleigh, North Carolina 27695-7919, USA

<sup>&</sup>lt;sup>3</sup>Adroit Materials, Inc., 2054 Kildaire Farm Rd., Cary, North Carolina 27518, USA

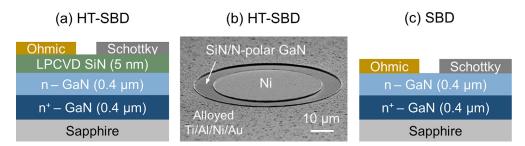

FIG. 1. (a) Schematic cross section and (b) SEM image of the fabricated N-polar GaN Schottky diode with a 5 nm LPCVD SiN interlayer. (c) Cross section of conventional N-polar GaN SBD.

GaN diodes and unlock operation above 400 °C, which is a first for N-polar GaN technology.

N-polar GaN layers were grown on c-plane sapphire with a 4° offcut toward the m-plane using a vertical, cold-wall, radio frequency (RF) heated, low-pressure metal-organic chemical vapor deposition (MOCVD) system. A 0.4- $\mu$ m-thick n<sup>+</sup>-doped layer followed by a 0.4- $\mu$ m-thick n-type layer was grown with unintentional oxygen carrier concentrations of 5 × 10<sup>19</sup> and 5 × 10<sup>17</sup> cm<sup>-3</sup>, respectively. Then, a 5-nm-thick SiN (slightly Si-rich) film was deposited using LPCVD at 725 °C and 320 mTorr with dichlorosilane (40 sccm) and ammonia (120 sccm) precursors. An *in situ* cleaning step with ammonia was performed prior to deposition to remove native oxides. The SiN layer was characterized using ellipsometry and reflectometry. <sup>24–26</sup>

After the growth, a metal stack consisting of Ti/Al/Ni/Au (30/ 100/70/70 nm) was deposited over a large area using e-beam evaporation and annealed at 850 °C for 30 s in N2 ambient to obtain Ohmic behavior through the SiN interlayer. 24,26 Schottky contacts were then formed via e-beam evaporation of Ni (250 nm). Figures 1(a) and 1(b) show the schematic cross section and tilted view scanning electron microscope (SEM) image of a fabricated N-polar GaN Schottky barrier diode with a 5 nm SiN interlayer. Henceforth, this device is referred to as the HT-SBD (high temperature Schottky barrier diode). Conventional Schottky barrier diodes lacking the SiN interlayer, henceforth referred to as SBD (Schottky barrier diode), were also fabricated for a controlled comparison of the HT-SBD's properties. The schematic cross section of the SBD is shown in Fig. 1(c). It should be noted that the Schottky metal for the SBD was deposited using a metal shadow mask to avoid exposing the N-polar GaN surface to photolithography developer.<sup>24</sup> In this work, no acid cleaning was performed prior to the Ni Schottky contact deposition for both cases.

I–V–T measurements were performed on a heated stage mounted in a vacuum chamber ( $\sim\!10^{-7}\,\rm Torr)$  using a Keithley 4200 semiconductor parameter analyzer. I–V measurements were conducted on diodes with a diameter of 300  $\mu\rm m$  for both SBD and HT-SBD cases. All the devices were stressed for at least 1 h at each temperature measurement. The temperature readings were taken by placing the thermocouple directly on the surface of the sample. At least five diodes were measured at each temperature for both SBD and HT-SBD devices. The electrical performances of these diodes are identical for each type of device.

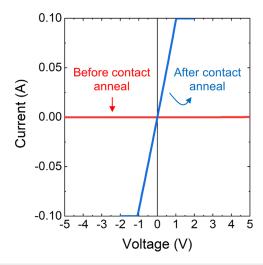

Figure 2 shows the comparison of the I–V characteristics measured between two Ohmic contacts before and after contact annealing. It can be observed that the I–V becomes linear after the contact annealing at 850 °C even though the Ohmic metallization was in direct

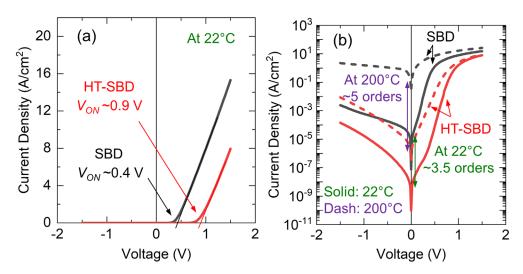

contact with the thin SiN interlayer. A comparison of room temperature (R.T. = 22 °C) I-V characteristics in linear and semilog scales for both the HT-SBD and SBD is shown in Fig. 3. The turn-on voltage  $(V_{ON})$  is  $\sim$ 0.4 V in the SBD compared to 0.9 V in the HT-SBD because of the additional voltage drop across the SiN interlayer present in the latter device. It should be noted that the  $V_{ON}$  is extracted by extrapolating a line from the series resistance limited current regime of the diode for each case as shown in Fig. 3(a). It is worth noting that the slope of the I–V after knee voltage for both cases is similar. This means the on-resistance does not change after inserting the 5 nm SiN interlayer. The semilog I-V shows that the leakage current measured at zero bias is  $\sim$ 3.5 orders of magnitude lower in the HT-SBD than in the SBD at R.T. At 200 °C, the leakage current for the SBD increases significantly, which renders a leakage current ratio difference of ~5 orders [see dashed lines in Fig. 3(b)]. The ideality factors (n) for the SBD and HT-SBD are  $\sim$ 1.1 and  $\sim$ 1.4, respectively. Thus, adding an ultra-thin SiN interlayer reduces the leakage current compared to conventional N-polar GaN SBDs without significantly deteriorating their low voltage performance, which is enabled by the unique properties of the LPCVD SiN.

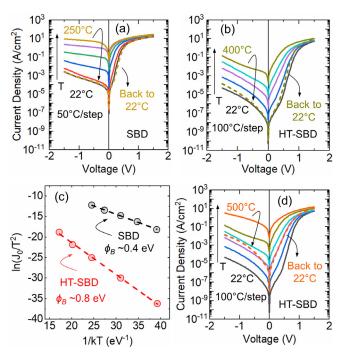

The I-V-T characteristics of the SBD from 22 °C to 250 °C are shown in Fig. 4(a). The leakage current increases significantly with

FIG. 2. Comparison of the I–V characteristics measured between two Ohmic contacts before and after contact annealing.

FIG. 3. (a) Comparison of room temperature I–V characteristics of the HT-SBD and SBD in linear scale. (b) I–V comparison of the HT-SBD and SBD at 22 °C and 200 °C in semilog scale, respectively. Solid lines are for 22 °C, and dashed lines are for 200 °C. There is a 3.5-order of magnitude difference in leakage current at zero bias at 22 °C between the HT-SBD and SBD, which increases to ~5 orders of magnitude at 200 °C.

temperature. At 250 °C, the rectification ratio ( $I_{ON}/I_{OFF}$ ) at voltage bias  $\pm 1.5 \, \text{V}$  reduces to less than one order of magnitude, as seen in Fig. 4(a). It is worth noting that the reason for choosing the  $\pm 1.5 \, \text{V}$  for the rectification ratio is because the diode is completely turned on at

**FIG. 4.** Temperature-dependent I–V (I–V–T) characteristics of (a) SBD diode from room temperature 22 °C to 250 °C with a step of 50 °C and (b) with 5 nm SiN (HT-SBD) diode from 22 °C to 400 °C with a step of 100 °C. (c) Barrier height extracted from I–V–T. (d) I–V–T characteristics of diode with HT-SBD diode from 22 °C to 500 °C. For (a), (b), and (d), dashed line represents the I–V at 22 °C after cooling down from respective high-temperature measurement in all cases.

that potential in forward bias. After 250 °C, the SBDs were cooled to R.T. and measured again [dashed line Fig. 4(a)]. It is seen that the I–V behavior measured before and after 250 °C overlaps, meaning no chemical degradation happened between Ni and N-polar GaN during the high-temperature measurements. Figure 4(b) shows the I–V–T characteristics of HT-SBD from 22 °C to 400 °C. The rectification ratio at 400 °C is still  $\sim\!\!2$  orders of magnitude. When returning to R.T. again from 400 °C, a negligible change is observed in I–V characteristics [dashed line in Fig. 4(b)] after high-temperature stress. This suggests no chemical degradation at the Ni/SiN/N-polar GaN interfaces, and repeatable/reliable diode performance can be expected. These results affirm that N-polar GaN Schottky diodes with an ultrathin SiN interlayer can be operated at significantly higher temperatures compared to conventional N-polar GaN SBD's.

Barrier heights ( $\phi_B$ ) for both devices were extracted from the I–V–T characteristics, as shown in Fig. 4(c). The  $\phi_B$  for SBD and HT-SBD is  $\sim$ 0.4 and  $\sim$ 0.8 eV, respectively. It should be noted that the barrier height values for both diodes match with the V<sub>ON</sub> values extracted at R.T. The barrier for the HT-SBD should be at the Ni/SiN interface; our previous work has demonstrated that the barrier at the SiN/N-polar GaN interface should not be more than 0.4 eV.<sup>24</sup> Thus, an ultra-thin SiN interlayer does, indeed, increase the barrier height. This, in turn, helps reduce leakage current and improves the diode's high temperature operation capability. The Richardson constant (A\*) for both SBD and HT-SBD is extracted from Fig. 4(c), which are  $\sim$ 0.1 and  $\sim$ 0.01 A cm<sup>-2</sup> K<sup>-2</sup>.

Figure 4(d) shows I–V–T characteristics of the HT-SBD from  $22\,^{\circ}\text{C}$  to  $500\,^{\circ}\text{C}$ . Interestingly, the rectification ratio is still around one order of magnitude at  $500\,^{\circ}\text{C}$ , although, when coming back to R.T., the I–V behavior [dashed line in Fig. 4(d)] deviates from what has been measured at R.T. before  $500\,^{\circ}\text{C}$  stress. It should be noted that the diode is not destroyed, and the rectification ratio is still more than three orders of magnitude. This I–V behavior change must be due to chemical degradation in the diode after the  $400\,^{\circ}\text{C}$  temperature operation. It was speculated to be due to the interaction between Ni and

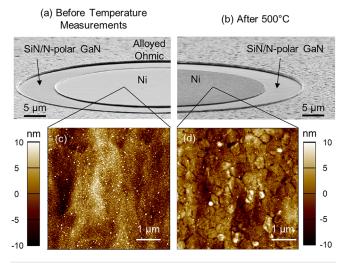

**FIG. 5.** Tilted view SEM images of HT-SBD (a) before any temperature measurements (as fabricated) and (b) after 500 °C exposure in a vacuum. AFM scan on Ni metal surface (c) before and (d) after 500 °C exposure.

Si-rich SiN instead of a chemical reaction at the SiN/N-polar GaN since Ni-silicide usually forms at around  $400\,^{\circ}\text{C}.^{27}$

To investigate further, the devices operated at 500 °C were analyzed using SEM and atomic force microscopy (AFM). Figures 5(a) and 5(b) show tilted view SEM images before any temperature measurements (as fabricated) and after 500 °C temperature measurements, respectively. From SEM, the surface of the Ni appears to be alloyed after 500 °C. The AFM scan on the Ni metal surface reveals changes in the surface morphology, which indicates alloying might happened after 400 °C, as seen in Figs. 5(c) and 5(d). However, the exposed SiN on N-polar GaN surface is similar for both cases. The root mean square (RMS) roughness values are extracted from AFM images shown in Figs. 5(c) and 5(d). The RMS roughness for as-deposited Ni contact is 3.6 nm. In comparison, the RMS roughness after 500 °C exposure is 3.1 nm, which indicates that the roughness did not change. Thus, most likely, the chemical degradation only happened at Ni/SiN interface due to the interaction of Ni and Si-rich SiN, possibly forming Ni-silicide phases, after 400 °C. The results call for further exploration of the metal contact system in order to avoid silicide formation and increase the elevated temperature operation capability of N-polar GaN Schottky diodes, which is left for future work.

In summary, high-temperature stable Schottky contacts to N-polar GaN are achieved using LPCVD SiN interlayers. The ultra-thin SiN increases the barrier height, reduces the leakage current, and increases the thermal stability of the N-polar GaN Schottky diode. The SiN interlayer diodes show reproducible electrical properties even after being operated up to 400 °C. However, degradation happens at 500 °C, which could be due to the reaction at Ni/SiN interface. In this way, we have shown that careful material selection and device design make it possible for N-polar GaN Schottky diodes to operate up to 500 °C. These results should enable reliable N-polar GaN devices with better performance.

This work was supported in part by NSF (Nos. ECCS-1610992, ECCS-1916800, and ECCS-1653383), AFOSR (Nos.

FA-95501710225 and FA-9550-1910114), U.S. Department of Energy (No. DEAR0000873), and the PowerAmerica Institute at North Carolina State University. This work was performed in part at the NCSU Nanofabrication Facility (NNF) and Analytical Instrumentation Facility (AIF), which are supported by the State of North Carolina and the National Science Foundation (Award No. ECCS-1542015). The NNF and AIF are members of the North Carolina Research Triangle Nanotechnology Network, a site in the National Nanotechnology Coordinated Infrastructure.

#### **AUTHOR DECLARATIONS**

#### **Conflict of Interest**

The authors have no conflicts to disclose.

#### **DATA AVAILABILITY**

The data that support the findings of this study are available from the corresponding author upon reasonable request.

#### **REFERENCES**

- <sup>1</sup>S. Rajan, A. Chini, M. H. Wong, J. S. Speck, and U. K. Mishra, J. Appl. Phys. **102**, 044501 (2007).

- <sup>2</sup>F. Akyol, D. N. Nath, S. Krishnamoorthy, P. S. Park, and S. Rajan, Appl. Phys. Lett. 100, 111118 (2012).

- <sup>3</sup>M. H. Wong, S. Keller, N. Dasgupta Sansaptak, D. J. Denninghoff, S. Kolluri, D. F. Brown, J. Lu, N. A. Fichtenbaum, E. Ahmadi, U. Singisetti, A. Chini, S. Rajan, S. P. DenBaars, J. S. Speck, and U. K. Mishra, Semicond. Sci. Technol. 28, 074009 (2013).

- <sup>4</sup>S. Keller, H. Li, M. Laurent, Y. Hu, N. Pfaff, J. Lu, D. F. Brown, N. A. Fichtenbaum, J. S. Speck, S. P. DenBaars, and U. K. Mishra, Semicond. Sci. Technol. 29, 113001 (2014).

- <sup>5</sup>O. S. Koksaldi, J. Haller, H. Li, B. Romanczyk, M. Guidry, S. Wienecke, S. Keller, and U. K. Mishra, IEEE Electron Device Lett. 39, 1014 (2018).

- <sup>6</sup>Y. Cho, J. Encomendero, S.-T. Ho, H. G. Xing, and D. Jena, Appl. Phys. Lett. \_117, 143501 (2020).

- <sup>7</sup>B. Romanczyk, S. Wienecke, M. Guidry, H. Li, E. Ahmadi, X. Zheng, S. Keller, and U. K. Mishra, IEEE Trans. Electron Devices 65, 45 (2018).

- <sup>8</sup>B. Romanczyk, X. Zheng, M. Guidry, H. Li, N. Hatui, C. Wurm, A. Krishna, E. Ahmadi, S. Keller, and U. K. Mishra, IEEE Electron Device Lett. **41**, 349 (2020).

- <sup>9</sup>R. Collazo, S. Mita, A. Rice, R. F. Dalmau, and Z. Sitar, Appl. Phys. Lett. 91, 212103 (2007).

- <sup>10</sup>R. Collazo, S. Mita, A. Rice, R. Dalmau, P. Wellenius, J. Muth, and Z. Sitar, Phys. Status Solidi C 5, 1977 (2008).

- <sup>11</sup>D. Khachariya, D. Szymanski, P. Reddy, E. Kohn, Z. Sitar, R. Collazo, and S. Pavlidis, ECS Trans. 98, 69 (2020).

- <sup>12</sup>D. Szymanski, D. Khachariya, T. B. Eldred, P. Bagheri, S. Washiyama, A. Chang, S. Pavlidis, R. Kirste, P. Reddy, E. Kohn, L. Lauhon, R. Collazo, and Z. Sitar, J. Appl. Phys. 131, 015703 (2022).

- <sup>13</sup>M. Stutzmann, O. Ambacher, M. Eickhoff, U. Karrer, A. L. Pimenta, R. Neuberger, J. Schalwig, R. Dimitrov, P. J. Schuck, and R. D. Grober, Phys. Status Solidi B 228, 505 (2001).

- <sup>14</sup>A. Rizzi and H. Lüth, Appl. Phys. Lett. **80**, 530 (2002).

- <sup>15</sup>J. Osvald, J. Kuzmik, G. Konstantinidis, P. Lobotka, and A. Georgakilas, Microelectron. Eng. 81, 181 (2005).

- <sup>16</sup>B. P. Downey, D. J. Meyer, D. S. Katzer, D. F. Storm, and S. C. Binari, Solid-State Electron. 86, 17 (2013).

- <sup>17</sup>P. Reddy, I. Bryan, Z. Bryan, W. Guo, L. Hussey, R. Collazo, and Z. Sitar, J. Appl. Phys. 116, 123701 (2014).

- <sup>18</sup>T. Suemitsu and I. Makabe, Phys. Status Solidi B **257**, 1900528 (2020).

- <sup>19</sup>D. Khachariya, D. Szymanski, R. Sengupta, P. Reddy, E. Kohn, Z. Sitar, R. Collazo, and S. Pavlidis, J. Appl. Phys. 128, 064501 (2020).

- <sup>20</sup>W. Liu, I. Sayed, B. Romanczyk, N. Hatui, M. Guidry, W. J. Mitchell, S. Keller, and U. K. Mishra, IEEE Electron Device Lett. 41, 1468 (2020).

- P. G. Neudeck, R. S. Okojie, and L.-Y. Chen, Proc. IEEE 90, 1065 (2002).

H. Wong, M. C. Poon, Y. Gao, and T. Kok, J. Electrochem. Soc. 148, G275

- <sup>23</sup>S. Choi, H. Yang, M. Chang, S. Baek, H. Hwang, S. Jeon, J. Kim, and C. Kim, Appl. Phys. Lett. **86**, 251901 (2005).

- <sup>24</sup>D. Khachariya, D. Szymanski, M. H. Breckenridge, P. Reddy, E. Kohn, Z. Sitar, R. Collazo, and S. Pavlidis, Appl. Phys. Lett. 118, 122103 (2021).

- <sup>25</sup>P. Reddy, S. Washiyama, F. Kaess, M. Hayden Breckenridge, L. H. Hernandez-Balderrama, B. B. Haidet, D. Alden, A. Franke, B. Sarkar, E. Kohn, R. Collazo, and Z. Sitar, J. Appl. Phys. 119, 145702 (2016).

<sup>26</sup>P. Reddy, D. Khachariya, D. Szymanski, M. H. Breckenridge, B. Sarkar, S.

- Pavlidis, R. Collazo, Z. Sitar, and E. Kohn, Semicond. Sci. Technol. 35, 055007 (2020). <sup>27</sup>A. Noya and M. B. Takeyama, Electron. Commun. Jpn. **99**, 85 (2016).