# A Scalable Integrated DC/DC Converter with Enhanced Load Transient Response and Security for Emerging SoC Applications

Xingye Liu, Paul Ampadu

Department of Electrical and Computer Engineering

Virginia Tech

Blacksburg, USA

{xingye15, ampadu}@vt.edu

Abstract— In this paper we propose a novel integrated DC/DC converter featuring a single-input-multiple-output architecture for emerging System-on-Chip applications to improve load transient response and power side-channel security. The converter is able to provide multiple outputs ranging from 0.3V to 0.92V using a global 1V input. By using modularized circuit blocks, the converter can be extended to provide higher power or more outputs with minimal design complexity. Performance metrics including power efficiency and load transient response can be well maintained as well. Implemented in 32nm technology, single output efficiency can reach to 88% for the post layout models. By enabling delay blocks and circuits sharing, the Pearson correlation coefficient of input and output can be reduced to 0.1 under rekeying test. The reference voltage tracking speed is up to 31.95 V/μs and peak load step response is 53 mA/ns. Without capacitors, the converter consumes 2.85 mm<sup>2</sup> for high power version and only 1.4 mm<sup>2</sup> for the low power case.

Keywords—DC/DC converter, load transient response, dynamic voltage scaling, scalability, power side-channel security.

## I. Introduction

Power management for System-on-Chip (SoC) applications is facing new challenges as both load transient responses and side-channel security requirements are becoming more important [1]. Meanwhile, as more Internet-of-Things (IoT) and Edge Computing enabled applications come to the market, we are looking for more flexible and scalable solutions to lower design complexity and reduce cost without sacrificing any performance. Traditionally, large off-chip power converters are working with point-of-load on-chip converters to meet power delivery and management requirements. However, the limited area cannot allow independent power supplies for each of the ever-increasing number of workloads [2, 3]. On the other hand, protecting such embedded devices from various types of attacks are also urgent. Among them power side-channel attack is still the most common and effective one to steal critical information from the circuit. Thus, conventional architectures may not be sufficient, to match response speed, efficiency, scalability, and security requirements [4, 5]. In this paper we will target these problems and propose a hardware-based solution by using single-input-multiple-output DC/DC converter. The proposed converter will feature modularized circuit blocks in order to be scaled easily. In Section II we will show the converter schematics and related control blocks. Both transient response waveforms and security related test results are shown in Section III with a brief discussion about scalability. In Section IV we will summarize the work with some future works.

#### II. PROPOSED DESIGN

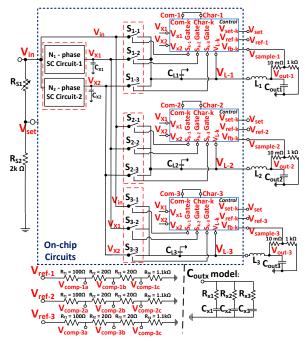

In this paper most of the results will be based on the 3-output DC/DC converter shown in Figure 1 and later the 6-output version will be shown to demonstrate scalability. In this figure the first stage is used to generate additional voltage rails and the second stage is to do voltage regulations. Reference voltages are generated from off-chip circuits and output capacitors are modelled off-chip as well.  $V_{\text{set}}$  here is added externally to help select the right pair of switches for charging and discharging.

Fig. 1. Schematic of the 3-output converter, showing 2 switched capacitor circuits as the first stage, and 3 controllable switches and low pass filters as the second stage. Reference voltages come from off-chip sources and are used to generate 3 compensation voltages for delay and auxiliary blocks.

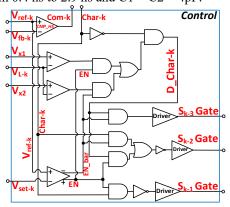

Details of the control block are shown in Figure 2. In this work we use  $V_{\text{set}} = V_{\text{set-k}} = 550 \text{mV}$ . Without enabling the delay block, port *Com-k* and *Char-k* are connected directly. Auxiliary

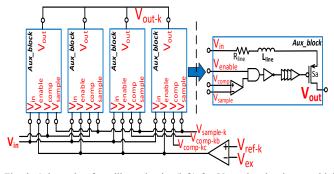

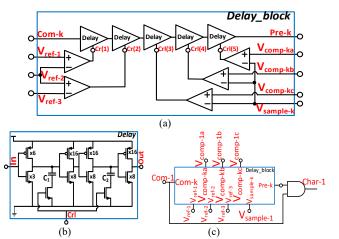

circuits and delay blocks are shown in Figure 3 and 4. Auxiliary blocks are only added when power ratings are higher to improve efficiency. Delay blocks are inserted between port Com-k and Char-k to enhance side-channel leakage resistance. The delay time varies based on the 5-bit results Crl(x) coming from the five comparators. From post-layout simulations, the delay varies from 0.4 ns to 2.9 ns and Cl = C2 = 4pF.

Fig. 2. Schematic of the control block where gate driving signals for switches are generated based on multiple references.

Fig. 3. Schematic of auxiliary circuits (left) for  $V_{\text{out-k}}$  showing how multiple compensation and sampled voltages are used, and aux blocks (right) is shown in details with  $R_{\text{line}} = 0.03~\Omega$ ,  $L_{\text{line}} = 8.7~\text{pH}$ .

Fig. 4. Schematics of (a) the delay block; (b) details of each delay unit; and (c) usage of the delay block of output-1 by inserting it between port *Com-1* and *Char-1* of the control block.

The regulated output  $V_{\text{out-k}}$  follows equation (1) and (2) where  $T_{\text{char}}$  and  $T_{\text{disc}}$  are charging and discharging time determined by the control block.

$$\begin{aligned} \text{When } V_{\text{set}} < V_{\text{ref-k}} < V_{\text{in}} \;, \\ V_{\text{out-k}} &= T_{\text{char}} * V_{\text{in}} + T_{\text{disc}} * V_{\text{x1}} \\ \text{When } 0 < V_{\text{ref,k}} < V_{\text{set}} \;. \end{aligned} \tag{1}$$

When

$$0 < V_{\text{ref-k}} < V_{\text{set}}$$

,

$V_{\text{out-k}} = T_{\text{char}} * V_{x1} + T_{\text{disc}} * V_{x2}$  (2)

In this work we follow our previous works [6] by using modularized PMOS and NMOS switches and fixed switched-capacitor circuits to lower design complexity and enable scalability. We let  $V_{x1} = 2/3 \ V_{in}$  and  $V_{x2} = 1/3 \ V_{in}$ . Each basic MOS switch block is designed to support up to 40mA load current and each switched capacitor circuit reaches about 81.6% efficiency while supporting 40mA current.

## III. IMPLEMENTATION AND RESULTS

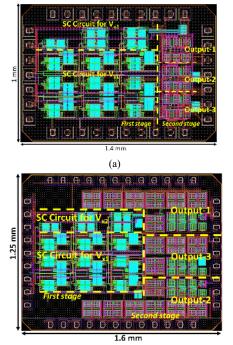

Post-layout models (in 32nm technology) are implemented to get all the simulation results. We first designed a low-power version as shown in Figure 5, which only supports up to 150mA each output and there are no delays or auxiliary blocks added. Then we propose a high-power version that supports up to 1A load and delays and Aux blocks are added as well, as shown in Figure 5(b).

Fig. 3. (a) Layout view of low-power version in which three outputs are identical and supposed to provide up to 150mA to each load; (b) layout view of the high-power version where output-1 and output-2 is scaled to support high power, while output-3 is designed for lower power.

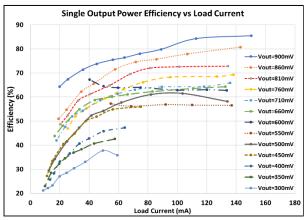

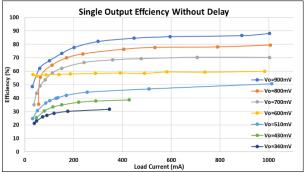

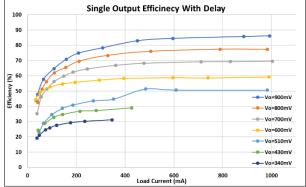

In this section both steady-state and load transient responses results will be listed based on post-layout simulations. We also add a total of 12.8 nF output capacitor based on off-chip ceramic models. Single output power efficiency is shown from Figure 7 to 9 for different cases. We can find out that the efficiency can be well maintained for different cases and these curves remain relatively flat for different loads. However, low voltage and lower power cases still suffer from additional loss due to additional control loss and charging loss. A 6-output

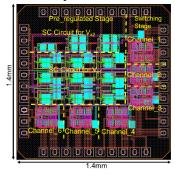

version is shown in Figure 6 while each output is designed to support about 150mA load. All the performance metrics maintain same as the 3-output one.

Fig. 6. Layout of the extended version of the converter with 6 output channels consuming 1.4mm x 1.4mm area;

Fig. 7. Single-channel power efficiency versus load current for low power.

Fig. 8. Single output efficiency when no delays are added for high power case.

Fig. 9. Single output efficiency with delays blocks, for high power case.

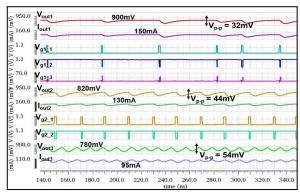

Fig. 10. Steady-state waveforms of three outputs for lower-power version, each supplying 150mA at 900mV, 130mA at 820mV and 95mA at 780mV with gate driving signals for output-1 and output-2 shown as well.

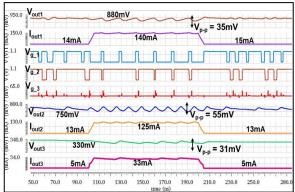

Fig. 11. Transient responses of all outputs (for low-power version) while responding to at least 6 times change in the load simultaneously showing no voltage droops/spikes and no observable cross regulations.

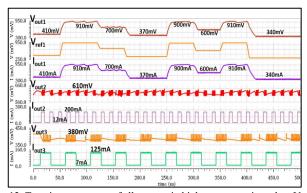

Fig. 12. Transient responses of all outputs in high-power version when  $V_{\text{out1}}$  is doing voltage scaling, and output-2 and -3 are responding to digital loads.

We can see from steady-state waveforms shown in Figure 10 that all the outputs are stable. We check load transient response including both load transitions voltage scaling. From Figure 11 and 12 for different versions, we can find out that all the outputs can remain stable without generating additional voltage spikes or droops, and there are no cross regulations among all the output voltages. A maximum step-up reference tracking speed of 30.6 V/ $\mu$ s and step-down of 31.9 V/ $\mu$ s are achieved. Max load current step response is 53 mA/ns.

Based on single-trace re-keying scenario, where the attacker can only get a few repetitive traces, we will do correlation coefficient and SNR studies which can reflect the security level of the converter. SNR in our work is

$$SNR = \frac{Var(I_{load})}{Var(I_{L} - I_{load})}$$

(3)

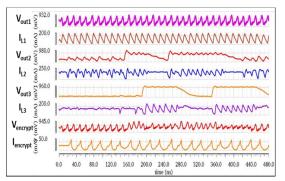

We first do an open-loop switch assignment test that connects the encryption load to different outputs following this sequence: to  $V_{out1}$  between 0-150 ns and  $440 ns-2 \mu s;$  to  $V_{out2}$  between 150 ns-220 ns and 260 ns-340 ns; to  $V_{out3}$  between 200 ns-260 ns and 340 ns-440 ns. The transient waveforms are shown below in Figure 13.

Fig. 13. Transient waveforms showing three output voltages, three inductor currents, encryption load supply voltage and current.

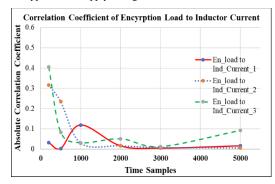

Fig. 14. Power correlation coefficient between actual encryption load current and different measurable inductor currents based on the switch assignment scheme.

| TABLE V. | COMPARISON | WITH RELATED | Works |

|----------|------------|--------------|-------|

|----------|------------|--------------|-------|

| Reference                            | [7]                    | [8]   | [9]           | [10]        | This<br>work       |

|--------------------------------------|------------------------|-------|---------------|-------------|--------------------|

| Technology                           | 28nm                   | 180nm | 130nm         | 180nm       | 32nm               |

| Input Voltage<br>(V)                 | 2.8-<br>4.2            | 3.3   | 1.2           | 1.8         | 1                  |

| Output Voltage<br>(V)                | 0.6-<br>1.2            | 1-2.5 | 0.45-<br>1.05 | 0.4-<br>1.6 | 0.3-0.92           |

| Load Current<br>per Phase(mA)        | 33.3                   | 1800  | 70            | 150         | 1000               |

| Peak Efficiency<br>(%)               | 78                     | 90.7  | 71            | 87.5        | 88.0               |

| Max Load Step<br>Response<br>(mA/ns) | 0.2                    | 23.6  | 0.75          | 0.07        | 53                 |

| Reference<br>Tracking (V/μs)         | N/A                    | 4.25  | 2.9           | 0.0375      | 31.9               |

| Max Voltage<br>Ripple (mV)           | 12                     | < 20  | 84            | 100         | 95                 |

| Voltage Spike /<br>Droop (mV)        | Non-<br>observ<br>able | 225   | 100           | 160         | Non-<br>observable |

| Inductor (nH)                        | 3                      | 150   | 11.8          | 4700        | 1                  |

| Output Cap (nF)                      | 50                     | 660   | 3.2           | 6000        | 15.8               |

| Chip Area (mm²)                      | 1.5                    | 2.3   | 0.5           | 1.95        | 2.85               |

We can find out that the by using different outputs to supply the encryption workload, the correlations between the real encryption load and the measurable inductor currents all become quite week. More measurements are needed at first place to determine the connections between the inputs and the load and it becomes more difficult to further derive the key. We also compare the current work with other works in Table I.

### IV. CONCLUSION

We presented a scalable DC/DC converter for multiple outputs to improve both load transient responses and side-channel security for emerging heterogeneous SoCs. Due to the modularized circuit blocks, the converter can be easily scaled to different power levels with low design complexity. Load transient responses are improved as the converter provides more than 2 times faster load transitions and 7 times faster voltage scaling speed than other works. Under re-keying scheme, with circuit sharing architecture, the correlation coefficient between input and output is reduced to less than 0.1, The proposed converter shows potentials in mitigating power side-channel attacks and solving load transient response power management issues for future SoCs.

Our future works include detailed modeling of the converter and exploring specific side-channel attack mitigations with a dynamic key insertion scheme.

#### REFERENCES

- [1] N. Tang, W. Hong, B. Nguyen, Z. Zhou, J. -H. Kim and D. Heo, "Fully Integrated Switched-Inductor-Capacitor Voltage Regulator With 0.82-A/mm² Peak Current Density and 78% Peak Power Efficiency," in *IEEE Journal of Solid-State Circuits*, vol. 56, no. 6, pp. 1805-1815, June 2021.

- [2] Shalf John. 2020 The future of computing beyond Moore's Law. Phil. Trans. R. Soc. A.378:20190061.

- [3] T. M. Andersen et al., "A 10 W On-Chip Switched Capacitor Voltage Regulator With Feedforward Regulation Capability for Granular Microprocessor Power Delivery," in *IEEE Transactions on Power Electronics*, vol. 32, no. 1, pp. 378-393, Jan. 2017.

- [4] W. Huang, J. A. A. Qahouq and Z. Dang, "CCM–DCM Power-Multiplexed Control Scheme for Single-Inductor Multiple-Output DC–DC Power Converter With No Cross Regulation," in *IEEE Transactions on Industry Applications*, vol. 53, no. 2, pp. 1219-1231, March-April 2017.

- [5] Z. Dong, Z. Li, X. L. Li, C. K. Tse and Z. Zhang, "Single-Inductor Multiple-Input Multiple-Output Converter With Common Ground, High Scalability, and No Cross-Regulation," in *IEEE Transactions on Power Electronics*, vol. 36, no. 6, pp. 6750-6760, June 2021.

- [6] X. Liu and P. Ampadu, "Distributed On-Chip Power Supply for Security Enhancement in Multicore NoC," 2021 IEEE 34th International Systemon-Chip Conference (SOCC), 2021, pp. 212-217.

- [7] F. Conti et al., "An IoT Endpoint System-on-Chip for Secure and Energy-Efficient Near-Sensor Analytics," in *IEEE Transactions on Circuits and Systems I: Regular Papers*, vol. 64, no. 9, pp. 2481-2494, Sept. 2017.

- [8] P.-Y. Wang, Y.-W. Huang and T.-H. Kuo, "A Reconfigurable Transient Optimizer Applied to a Four-Phase Buck Converter for Optimizing Both DVS and Load Transient Responses," in *IEEE Transactions on Circuits* and Systems II: Express Briefs, vol. 67, no. 1, pp. 52-56, Jan. 2020.

- [9] M. Kar, A. Singh, A. Rajan, V. De and S. Mukhopadhyay, "An All-Digital Fully Integrated Inductive Buck Regulator With A 250-MHz Multi-Sampled Compensator and a Lightweight Auto-Tuner in 130-nm CMOS," in *IEEE Journal of Solid-State Circuits*, vol. 52, no. 7, pp. 1825-1835, July 2017.

- [10] Z. Zhou, N. Tang, B. Nguyen, W. Hong, P. P. Pande and D. Heo, "A Wide Output Voltage Range Single-Input-Multi-Output Hybrid DC-DC Converter Achieving 87.5% Peak Efficiency With a Fast Response Time and Low Cross Regulation for DVFS Applications," 2020 IEEE Custom Integrated Circuits Conference (CICC), Boston, MA, USA, 2020, pp. 1-4.