# $\beta$ -Ga<sub>2</sub>O<sub>3</sub> FinFETs with ultra-low Hysteresis by Plasma-Free Metal-Assisted Chemical Etching

Hsien-Chih Huang,<sup>1</sup> Zhongjie Ren,<sup>2</sup> A F M Anhar Uddin Bhuiyan,<sup>3</sup> Zixuan Feng,<sup>3</sup> Zhendong Yang,<sup>2</sup> Xixi Luo,<sup>2</sup> Alex Q. Huang,<sup>2</sup> Andrew Green,<sup>4</sup> Kelson Chabak,<sup>4</sup> Hongping Zhao,<sup>3</sup> Xiuling Li,<sup>1,2,\*</sup>

<sup>1</sup>Department of Electrical and Computer Engineering, Micro and Nanotechnology Laboratory, University of Illinois at Urbana-Champaign, Urbana, IL 61801, USA

<sup>2</sup>Department of Electrical and Computer Engineering, Microelectronics Research Center, University of Texas, Austin, TX 78758, USA

<sup>3</sup>Electrical and computer engineering department, Ohio State University, Dayton, OH, USA

<sup>4</sup>Air Force Research Laboratory, Sensors Directorate, WPAFB, OH, USA

\*e-mail: xiuling.li@utexas.edu

**Abstract**—In this work,  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> FinFETs with MOCVD grown epitaxial Si-doped channel layer on (010) semi-insulating  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> substrates are demonstrated.  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> fin channels with smooth sidewalls are produced by the plasma-free metal-assisted chemical etching (MacEtch) method. A specific on-resistance ( $R_{on,sp}$ ) of 6.5 m $\Omega$ ·cm<sup>2</sup> and a 370 V breakdown voltage are achieved. In addition, these MacEtch-formed FinFETs demonstrate DC transfer characteristics with near zero (9.7 mV) hysteresis. The effect of channel orientation on threshold voltage, subthreshold swing, hysteresis and breakdown voltages are also characterized. The FinFET with channel perpendicular to [102] direction is found to exhibit the lowest subthreshold swing and hysteresis.

Beta-Gallium Oxide ( $\beta$ -Ga<sub>2</sub>O<sub>3</sub>) has drawn tremendous attention in power-electronics due to its ultra-wide band gap (4.8 eV),<sup>1,2</sup> high breakdown field (8 MV/cm), and reasonable 150 cm<sup>2</sup>/V-s electron mobility,<sup>3</sup> leading to a 1721 Baliga's figure of merit. In addition to the high Baliga's figure of merit that outperforms SiC and GaN,<sup>4–6</sup> single crystalline bulk substrate with wide range of controllable *n*-type doping concentration<sup>7,8</sup> is also available for  $\beta$ -Ga<sub>2</sub>O<sub>3</sub>. Over the past decade, plenty of high power  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> devices, such as metal–semiconductor field-effect transistors (MESFETs),<sup>9</sup> metal–oxide–semiconductor field-effect transistors (MOSFETs),<sup>10–13</sup> vertical transistors<sup>14–16</sup> and Fin field-effect transistors (FinFETs),<sup>17</sup> with breakdown voltage ( $V_{br}$ ) over 2.6 kV<sup>18</sup> and specific on-resistance ( $R_{on,sp}$ ) down to 2 m $\Omega$ ·cm<sup>2</sup> have been

demonstrated.<sup>18</sup> Nonetheless, the reported  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> transistors so far still suffer from low drive current and  $R_{on,sp}$  compared to GaN devices. A solution to this issue is fabricating  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> transistors with high aspect ratio channels. Since  $R_{on,sp}$  is normalized to device area for top-view, increasing channel aspect ratio would create an enhanced drive current but still remains low in device area, leading to a reduced  $R_{on,sp}$ .<sup>19</sup> Therefore, the development for transistors with high aspect ratios and smooth sidewalls is crucial for  $\beta$ -Ga<sub>2</sub>O<sub>3</sub>.

Although a  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> vertical transistor with an aspect ratio over 9.27 has been fabricated through reactive ion etching (RIE),<sup>18</sup> the high-energy ion induced damage and interface traps caused by RIE still degrades the device performance, leading to a limited  $30 \text{ cm}^2/\text{V}\cdot\text{s}$  effective channel mobility.<sup>20</sup> In addition, the ion-induced damages typically result in notable hysteresis (200 mV – 2V) in all  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> transistors utilizing RIE process.<sup>17,18</sup> On the other hand, the plasma-free metal-assisted chemical etch (MacEtch) can produce a wide variety of 3D semiconductor structures with high aspect ratio and damage-free surfaces.<sup>21–25</sup>  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> fins with low interface trap density has previously been demonstrated by MacEtch,<sup>26,27</sup> and an almost hysteresis-free CV loop was achieved on the MacEtch-formed  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> MOSCAP structures, making it a promising etching technique for  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> transistor fabrication.

In this work, we demonstrate  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> FinFETs produced by MacEtch. The DC transfer and output characteristics, and breakdown voltage are fully characterized. The effect of channel orientation on threshold voltage ( $V_{th}$ ), subthreshold swing (SS), hysteresis, and  $V_{br}$  are also studied.

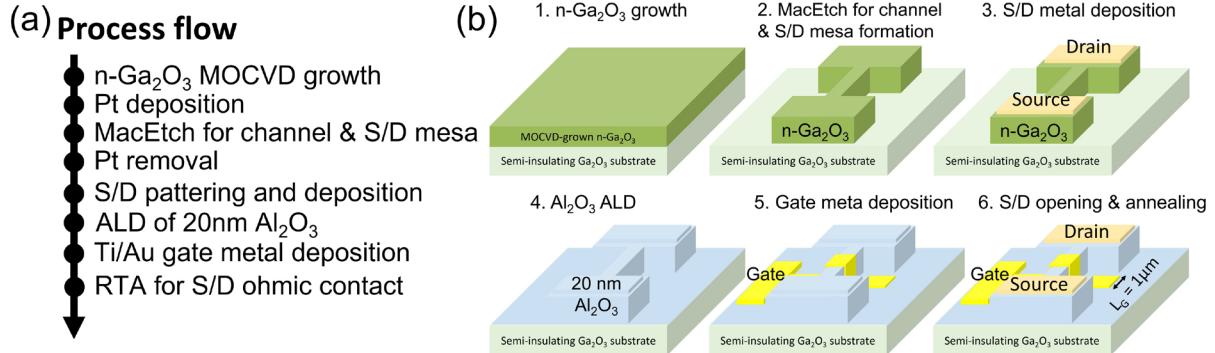

Fig. 1 presents a schematic illustration of the process flow for  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> FinFET fabrication. First, a  $\sim 2 \mu\text{m}$ -thick lightly silicon-doped  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> film was grown on a (010) Fe-doped semi-insulating substrate by metalorganic chemical vapor deposition (MOCVD).<sup>28,29</sup> The doping concentration is around  $4 \times 10^{17} \text{ cm}^{-3}$ . Then, channel and source/drain regions were defined through lithography followed by 30 nm Pt deposition by ebeam evaporation (Fig. 1). After standard lift-off process, the samples were immersed into a MacEtch solution consisting of a mixture of 49% HF and K<sub>2</sub>S<sub>2</sub>O<sub>8</sub>,<sup>27</sup> to form fin-shaped channels and source/drain mesas (Fig. 1). Subsequently, the Pt was removed by aqua regia followed by 25 nm/20 nm Ti/Au films deposition with ebeam evaporation for source and drain contact. 20 nm of Al<sub>2</sub>O<sub>3</sub> was then deposited through atomic layer deposition (ALD) process followed by 1 min of 490°C rapid thermal annealing (RTA) with N<sub>2</sub> ambient to improve interface quality between Al<sub>2</sub>O<sub>3</sub> and  $\beta$ -Ga<sub>2</sub>O<sub>3</sub>.<sup>30</sup> After the removal of Al<sub>2</sub>O<sub>3</sub> on top of the source/drain mesa by HF, 25 nm/20 nm Ti/Au gold gate electrodes were then deposited on the high-k layer to form the gate stack. Finally, 1 min of 480°C RTA under N<sub>2</sub> ambient was applied for source/drain ohmic contact formation.

Fig. 1 (a) Process flow and (b) schematic diagram of  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> FinFET fabrication.

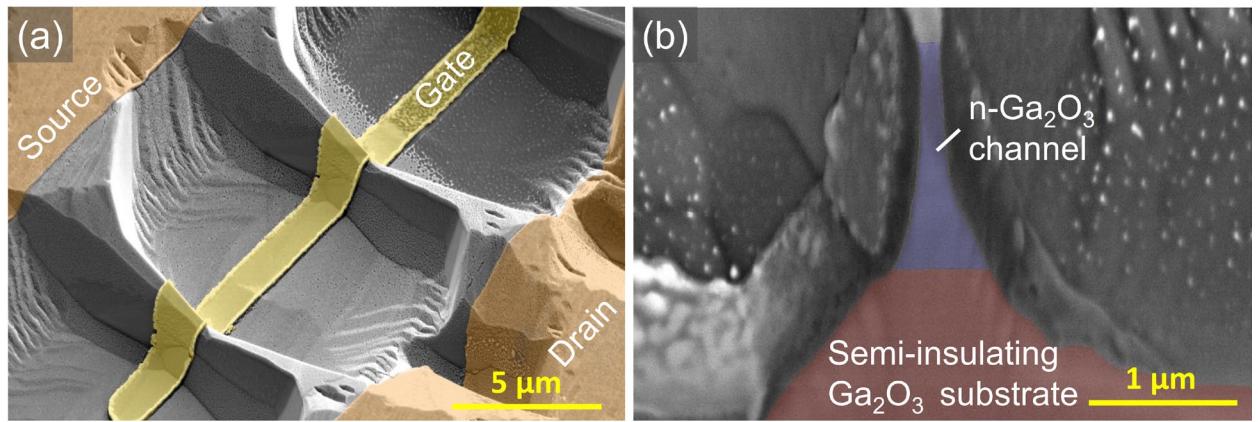

A trapezoid-like fin shape channel was first formed using the MacEtch process.<sup>26</sup> Fig. 2 (a) and (b) show the tilted-view and focused ion beam (FIB) cut cross-section SEM images of a fully fabricated  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> FinFET. Note that the source/drain mesa height of 3.57  $\mu$ m is larger than the thickness of epitaxial n-type  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> film (2  $\mu$ m), suggesting the fin channel consists of both the n-Ga<sub>2</sub>O<sub>3</sub> epitaxial layer and the semi-insulating substrate. This divides the structure into two parts: a much wider triangular part at the bottom (highlighted in red, Fig. 2(b)) and a narrow fin on top (highlighted in blue). Due to the nature of carrier transport process in MacEtch,<sup>25,27,31-33</sup>  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> MacEtch is also found to be dependent on the doping concentration.<sup>34</sup> Therefore, the sharp transition line on the sidewall is indicative of the interface between the top n-Ga<sub>2</sub>O<sub>3</sub> layer and the semi-insulating substrate. The active n-channel of the device is 142/570 nm in top/bottom width and  $\sim$  1.5  $\mu$ m in height, leading to an aspect ratio of 4.2:1 using the average fin width (Fig. 2(b)). Moreover, a smooth sidewall morphology can be observed on the MacEtch-formed structures (Fig.

Fig. 2. (a) Tilted and (b) cross-section SEM images of  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> FinFETs formed by MacEtch. Note that the distance between source and drain is 5  $\mu$ m and the SEM images are colored for identification. The tiny particles covering the FinFET in (b) are Au particles deposited after the IV measurement to reduce the charging issue and acquire SEM images with better-quality.

S1) compared to the rough sidewall produced by typical RIE processes. Note that the  $1.5\text{ }\mu\text{m}$  fin height is smaller than the epitaxial  $n\text{-Ga}_2\text{O}_3$  thickness ( $2\text{ }\mu\text{m}$ ), suggesting the top parts of fins might be removed in the MacEtch process due to side etching.

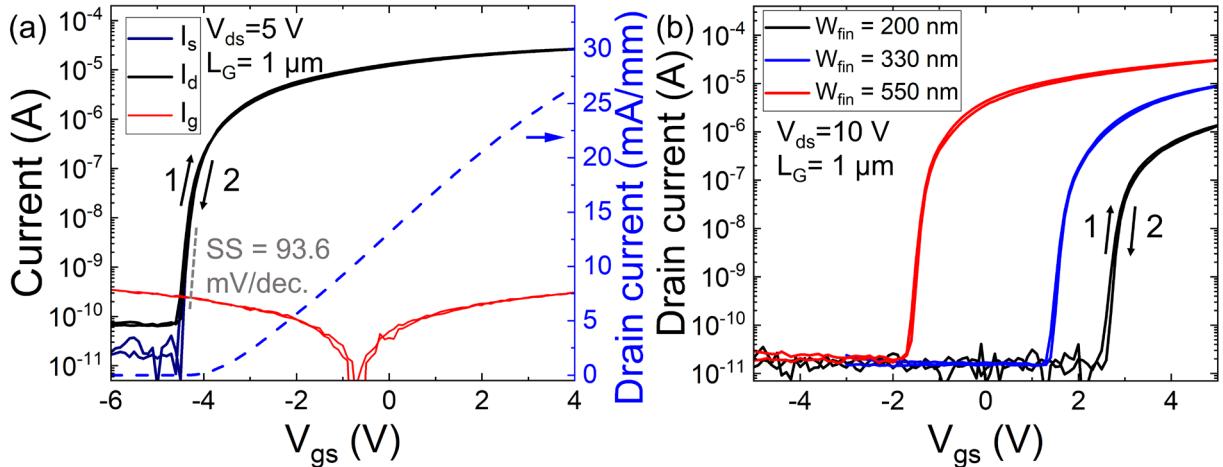

Fig. 3(a) shows the DC transfer characteristics of the MacEtch-formed  $\beta\text{-Ga}_2\text{O}_3$  FinFETs with  $1\text{ }\mu\text{m}$  gate length ( $L_G$ ) and  $630\text{ nm}$  top fin width ( $W_{\text{fin},\text{top}}$ ) under  $V_{\text{ds}} = 5\text{ V}$ . At  $V_{\text{gs}} = 4\text{ V}$ , the drive current reaches  $2.7 \times 10^{-5}\text{ A/fin}$  or  $26.7\text{ mA/mm}$  when normalized to the bottom width of the active fin channels (blue region in Fig. 2(b)). The on/off ratio is  $\sim 10^5$  with gate leakage current at  $100\text{ pA}$  level, suggesting that a gate stack with good control and low leakage is formed. DC transfer characteristics of  $\beta\text{-Ga}_2\text{O}_3$  FinFETs with different fin widths are shown in Fig. 3(b). With  $L_G = 1\text{ }\mu\text{m}$  and  $V_{\text{ds}} = 10\text{ V}$ ,  $V_{\text{th}}$  values are found to be highly dependent on the fin dimension, causing the FinFETs to shift from depletion mode (normally on) to enhancement mode (normally off) as the fin width decreases. As expected, a more negative gate bias is required to deplete the channel and turn off the device with increasing fin width. The  $V_{\text{th}}$  dependence on fin width also provides a general guideline to design transistor operation mode depending on the applications. In addition to  $V_{\text{th}}$ , SS are extracted to be  $93.6$ ,  $84.5$ , and  $89.9\text{ mV/dec.}$  for  $550$ ,  $330$  and  $200\text{ nm}$   $W_{\text{fin},\text{top}}$ , respectively. With  $SS = \frac{kT}{q} \ln 10 \cdot (1 + \frac{C_D + q \cdot D_{it}}{C_{ox}})$ ,<sup>35</sup> where  $C_D$ ,  $D_{it}$  and  $C_{ox}$  are the depletion capacitance, interface trap density and oxide capacitance, respectively, the upper bound of  $D_{it}$  in the MacEtch-formed  $\beta\text{-Ga}_2\text{O}_3$  FinFETs is estimated to be around  $1.4 \times 10^{12}\text{ cm}^{-2} \cdot \text{eV}^{-1}$ , which is not far from the CV measurement results of MacEtch-formed vertical MOSCAPs.<sup>26</sup> This indicates the MacEtch process does not damage the surface and has created an interface with superior  $D_{it}$  between  $\text{Al}_2\text{O}_3$  and  $\beta\text{-Ga}_2\text{O}_3$ .

Fig. 3 (a) DC transfer characteristic of  $\beta\text{-Ga}_2\text{O}_3$  FinFET in semi-log and linear scale. The channel orientation is  $80^\circ$  from  $[102]$  direction and  $W_{\text{fin},\text{top}} = 630\text{ nm}$ . (b) Transfer characteristic of  $\beta\text{-Ga}_2\text{O}_3$  FinFETs with different  $W_{\text{fin},\text{top}}$  and channel perpendicular to  $[102]$  direction.

Note that all the transfer characteristics showed almost zero hysteresis ( $\Delta V_{th}$  between voltage sweep 1 and 2 shown in Fig. 3(a)), which is unprecedented for  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> FETs with vertical sidewall structures. The largest hysteresis is only 9.7 mV clockwise, which is dramatically reduced compared to the 120 – 800 mV hysteresis of previously reported  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> FETs.<sup>14,18,36,37</sup> This nearly hysteresis-free characteristic could be attributed to the absence of RIE-induced ion damages and traps due to the MacEtch nature and is consistent with the CV results of MacEtch-formed  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> MOSCAPs.<sup>26</sup>

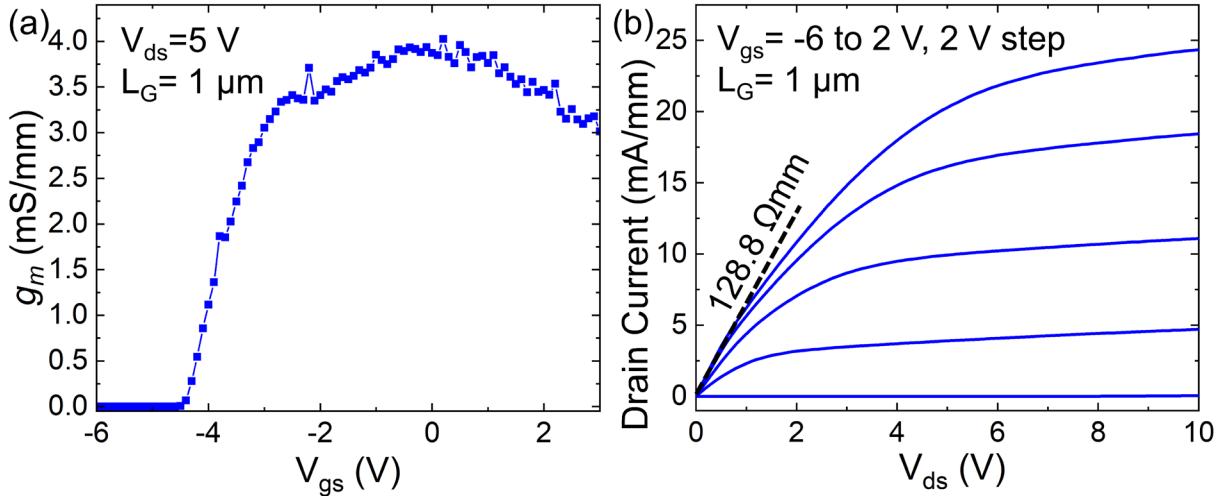

Fig. 4(a) shows the linear transfer characteristics at  $V_{ds} = 5$  V for the  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> FinFET. The output characteristics with  $L_G = 1 \mu\text{m}$  and  $W_{\text{fin,top}} = 630 \text{ nm}$  is shown in Fig. 4(b). At  $V_{gs} = 2\text{V}$  and  $V_{ds} = 10\text{V}$ , a 24.4 mA/mm drain current is achieved. On resistance ( $R_{on}$ ) can be extracted from the slope of low  $V_{ds}$  region. With the fin width extracted from the cross-section SEM images (blue region in Fig 2(b)), the  $R_{on}$  is estimated to be around 128.8  $\Omega\text{-mm}$  at  $V_{gs} = 2\text{V}$ . Thus, the  $R_{on,sp}$  is around 6.5  $\text{m}\Omega\text{-cm}^2$  when normalized to the distance between source and drain (5  $\mu\text{m}$ ). If we consider the source/drain contact transfer length ( $L_T$ ) as 1  $\mu\text{m}$ , the  $R_{on,sp} = R_{on} \times \text{gate width} \times (L_{SD} + 2L_T)$  can be extracted as 9.1  $\text{m}\Omega\text{-cm}^2$ . Note that since the carrier concentration at source/drain is only from the intrinsic doping during the MOCVD growth ( $\sim 4 \times 10^{17} \text{ cm}^{-3}$ ), the 1  $\mu\text{m}$  transfer length could be an overestimation. As a result, the 9.1  $\text{m}\Omega\text{-cm}^2$  of  $R_{on,sp}$  when considering  $L_T$  might also be overestimated. On the other hand, the  $R_{on,sp}$  is expected to be further reduced though additional ion implantation to increase source/drain doping concentration, leading to a decreased contact resistivity and parasitic source/drain resistance.

Fig. 4 (a) linear transfer characteristics and (b) output I-V characteristics of  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> FinFET. The channel orientation is 80° from [102] direction and  $W_{\text{fin,top}} = 630 \text{ nm}$ . Note that the  $g_m$  and current is normalized to the bottom width of active fin channel region (yellow-colored region in Fig.2 (b)).

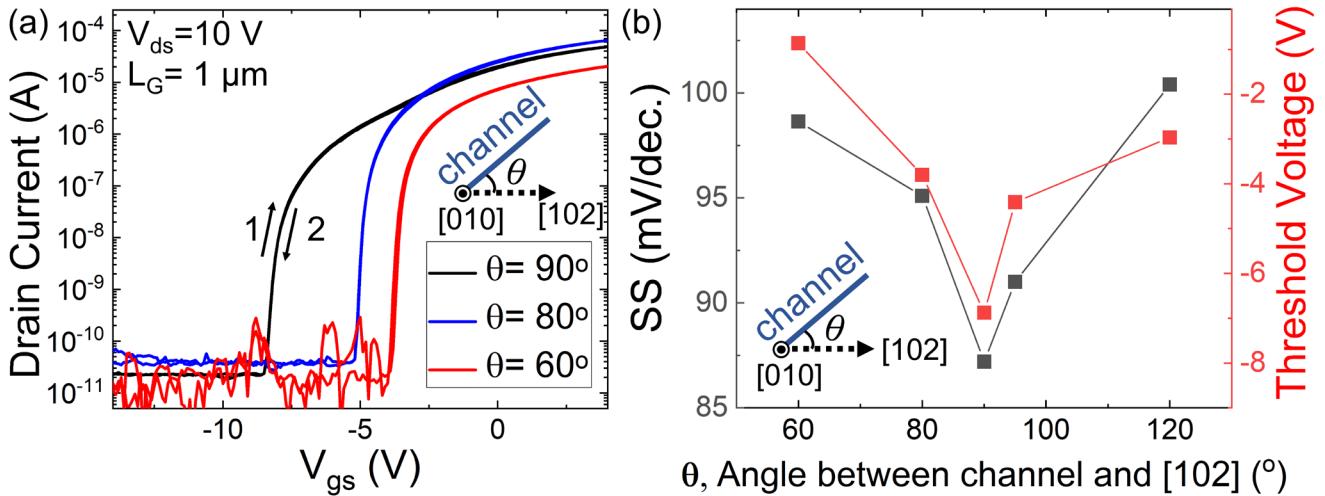

With the asymmetric crystal structure of  $\beta$ -Ga<sub>2</sub>O<sub>3</sub>, it has also been reported that the channel orientation affects the  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> transistor characteristics.<sup>18</sup> The DC transfer characteristics of  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> FinFETs with  $\sim 750$  nm  $W_{fin,top}$  and different channel orientations are shown in Fig. 5(a). At  $V_{ds} = 10$  V and  $V_{ov} = \sim 5$  V, the drain currents are  $\sim 2 \times 10^{-5}$ ,  $2.3 \times 10^{-5}$  and  $1.9 \times 10^{-5}$  A for  $\theta = 60^\circ$ ,  $85^\circ$ , and  $90^\circ$ , respectively. This shows all the drive current saturates at a similar level and suggests the channel mobility does not vary much with the orientation. Nonetheless, a clear voltage shift of the  $I_d$ - $V_{gs}$  curves can be observed as the channel orientation changes. To further analyse this shift, the  $V_{th}$  of  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> FinFETs with similar  $W_{fin,top}$  ( $\sim 750$  nm) and different channel orientations are extracted and plotted in Fig. 5(b). When  $\theta$ , the angle between the channel direction and [102], is  $60^\circ$  (Fig. 5(b)), a  $-0.9$  V  $V_{th}$  is observed. Then, the  $V_{th}$  becomes more negative as the fin rotates away from [102] direction and reaches its minimum at  $-6.9$  V when the channel is counter-clockwise  $90^\circ$  from [102] direction. As the angle becomes larger than  $90^\circ$ , the  $V_{th}$  starts to increase again as the channel is more aligned with [102]. This V-shaped  $V_{th}$  distribution has also been reported in (001)  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> vertical transistors<sup>18</sup> and could be attributed to two reasons: first, as shown in our previous work,<sup>26</sup> the fin sidewalls become more vertical as the fin orientation approaching  $90^\circ$  from [102]. This leads to a wider channel width and thus a more negative bias to deplete the channel. Therefore, a most negative  $V_{th}$  at  $90^\circ$  is expected. On the other hand, the interface trap quantity on the sidewalls has also been reported to vary with the fin orientation.<sup>26</sup> As a result, this  $V_{th}$  trend might also imply that the interface traps on sidewalls decrease as the channel getting more perpendicular to [102] direction; and the sidewalls have the lowest interface trap

Fig. 5 (a) DC transfer characteristics of  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> FinFETs with different channel orientations. (b) Subthreshold swings and threshold voltages of  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> FinFETs vs  $\theta$ , the angle between channel orientation and [102] direction. Note that  $W_{fin,top} = 741, 735, 750, 724$  and  $747$  nm for the devices with  $\theta = 60^\circ, 80^\circ, 90^\circ, 85^\circ$  and  $120^\circ$ , respectively.

density and negative interface charges, leading to the lowest  $V_{th}$ . It is also likely that these two factors both contribute to this  $V_{th}$  variation.

To further analyze the impact of these sidewall interface trap densities on the transistor performance, the SS of  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> FinFETs with different channel orientations are also extracted (Fig. 5(b)). SS decreases as the channel orientation rotates away from [102] and reaches its minimum value of 87.2 mV/dec. at  $\theta = 90^\circ$ . Like the  $V_{th}$ , the SS vs fin orientation also shows a V-shaped distribution. The SS can be modeled as  $SS = \frac{kT}{q} \ln 10 \cdot (1 + \frac{C_D + q \cdot D_{it}}{C_{ox}})$ ,<sup>35</sup> where  $C_D$ ,  $D_{it}$  and  $C_{ox}$  are the depletion capacitance, interface trap density and oxide capacitance, respectively. Accordingly, the V-shaped distribution of SS suggests that the interface trap density could be the lowest on the MacEtch-formed sidewalls when  $\theta = 90^\circ$ , consistent with the previous observation on  $V_{th}$ .

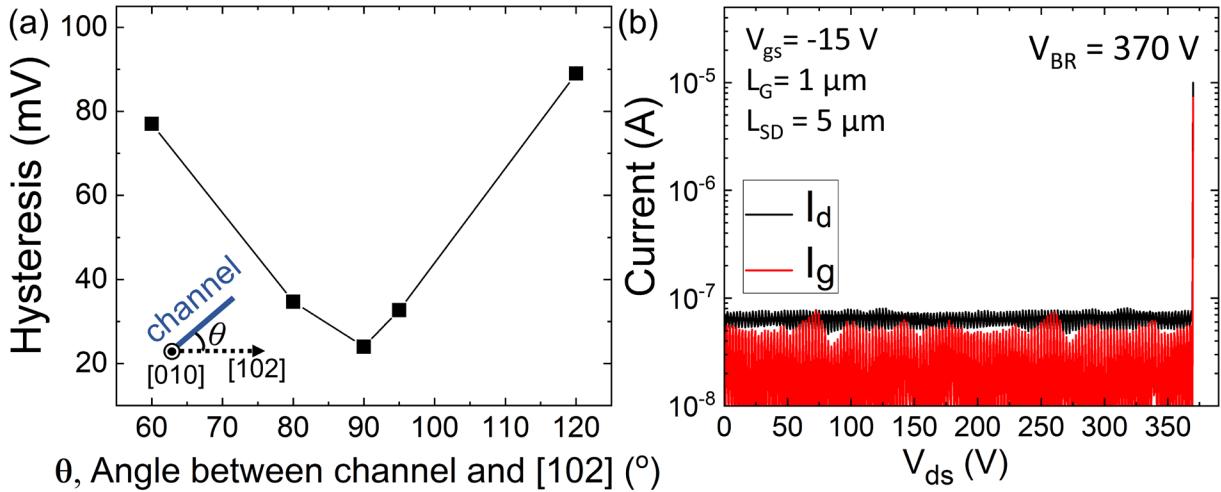

In addition to SS, the hysteresis of  $I_d$ - $V_{gs}$  curves also reflects the device and interface quality of  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> FinFETs. Thus, We have examined the hysteresis for MacEtch-formed devices with different orientations. As shown in Fig. 6 (a), the hysteresis vs  $\theta$  also demonstrate a similar V-shaped distribution with the minimum hysteresis (24 mV) at  $\theta = 90^\circ$  (Fig. 6(a)). It was reported that the interface quality (i.e.  $D_{it}$ ) had a direct impact on the hysteresis of the RIE-fabricated  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> FETs.<sup>38</sup> Therefore, this V-shape hysteresis might imply that sidewalls have the lowest  $D_{it}$  when the channel is perpendicular to [102] direction, in agreement with the previous results on  $V_{th}$  and SS.

Fig. 6 (a) Hysteresis of  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> FinFETs vs  $\theta$ , the angle between channel orientation and [102] direction. Note that  $W_{fin,top} = 741, 735, 750, 724$  and 747 nm for the devices with  $\theta = 60^\circ, 80^\circ, 90^\circ, 85^\circ$  and  $120^\circ$ , respectively.

(b) three-terminal off-state  $I_d$ / $I_g$ - $V_{ds}$  characteristics and breakdown voltage of  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> FinFET ( $W_{fin,top} = 630$  nm,  $\theta = 80^\circ$ ).

Fig. 6 (b) shows the high-voltage off-state characterization of the  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> FinFETs (the same device as shown in Fig. 3 (a) and 4). A negative  $V_{gs}$  bias is applied to keep the device at off state. The gate and drain current remain low, at the detection limit of the tool, until breakdown at  $\sim 370$ V, where a spike in drain and gate current are observed. By assuming a one-dimensional electrical field distribution ( $E = V_{gd}/L_{GD}$ ), the electric field under the gate is estimated to be  $\sim 1.4$  MV/cm when the breakdown occurs, which is smaller than the theoretical breakdown field of  $\beta$ -Ga<sub>2</sub>O<sub>3</sub>.<sup>39</sup> However, this simplified one-dimensional distribution is inaccurate for the FinFET structure. The simulated results show a significantly higher local electrical field occurs at the corner of the fin structure.<sup>40</sup> This could cause the breakdown to happen at a lower voltage compared to theoretical value. As a result, a greater breakdown voltage should be achieved in the future by incorporating field plate structures into the FinFETs<sup>18,37</sup>.

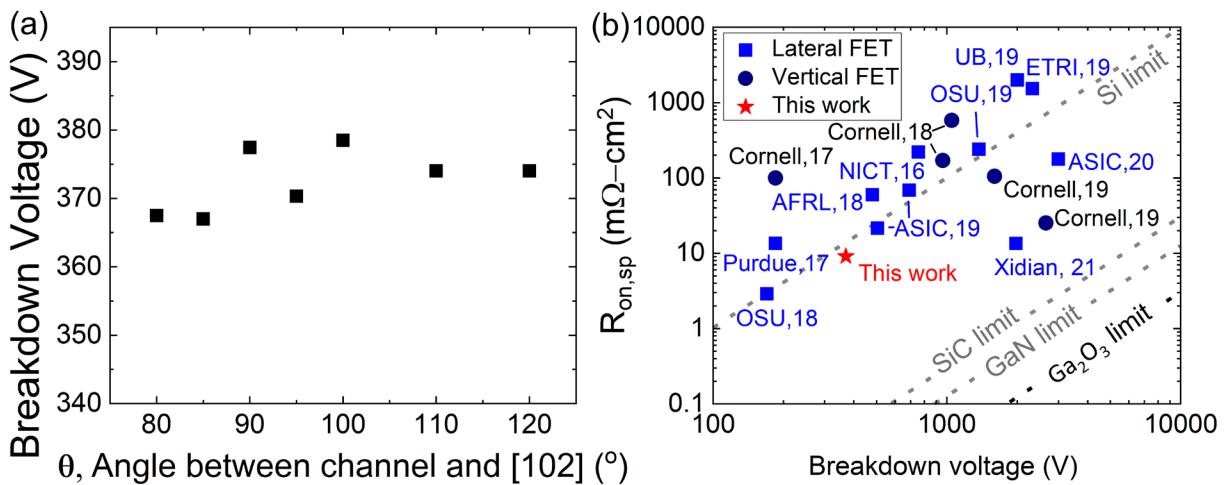

Fig. 7(a) shows the average breakdown voltage of the FinFETs with different channel orientations. The  $V_{br}$  are within the range of 365 - 380 V and do not vary much with different  $\theta$ , suggesting the interface properties might not play an important role in the breakdown mechanism. Fig. 7(b) shows the benchmark chart of reported  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> transistors in the literature. Note that the  $R_{on,sp}$  values plotted are extracted from the slope for the family of curves at low  $V_{ds}$  region under  $V_{ov} = \sim 5$ V for all cited works. Then, the  $R_{on,sp}$  are normalized to the area  $W_g \times (L_{SD} + 2L_T)$  and plotted in Fig. 7(b). For those works not reporting  $L_T$ , and a 1  $\mu$ m  $L_T$  is assumed for the calculation (raw data found in the cited work are plotted in Fig. S2 in the Supplementary Material). We believe this would provide a better reference point for benchmarking, since originally reported  $R_{on,sp}$  in different papers are extracted with quite different  $V_{ov}$  (ranging from 3V to 100V).

Fig. 7 (a) Breakdown voltages of  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> FinFETs vs  $\theta$ , the angle between channel orientation and [102] direction.

(b)  $R_{on,sp}$  vs  $V_{br}$  benchmark plot of  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> FETs.<sup>9,14,17,18,37,41-52</sup>

An alternative version of benchmarking with originally reported  $R_{on,sp}$  is also provided in Fig. S2. Here, the MacEtch-formed  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> FinFET demonstrates reasonable 370 V breakdown voltage and a 9.1 m $\Omega$ ·cm<sup>2</sup>  $R_{on,sp}$ , which is relatively low compared to other reported  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> transistors. With the nearly zero hysteresis and comparable device performance, we believe this work represents a step towards three-dimensional  $\beta$ -Ga<sub>2</sub>O<sub>3</sub>-based power electronics with high quality interface.

In summary,  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> FinFETs, produced by MacEtch with channels of good aspect ratios and smooth sidewalls, are demonstrated. The devices show near hysteresis-free  $I_d$ - $V_{gs}$  characteristics, presumably because of the absence of ion-induced damage, inherent to the MacEtch process. A 6.5 m $\Omega$ ·cm<sup>2</sup> specific on-resistance and a 370 V breakdown voltage are achieved. The effect of channel orientation on  $V_{th}$ , SS, hysteresis, and breakdown voltages are also analysed. The results suggest the sidewalls possess the lowest interface trap density when channel is perpendicular to [102] direction and best suited for FinFETs.

## SUPPLEMENTARY MATERIAL

Fig. S1 and S2 show the zoomed-in SEM image of the FinFET sidewall and the  $R_{on,sp}$  raw data found in literature before normalization, respectively.

## ACKNOWLEDGEMENT

This material is based upon work supported in part by the National Science Foundation under Grant No. 18-09946.

## DATA AVAILABILITY

The data that supports the findings of this study are available within the article and its supplementary material.

## REFERENCES

- <sup>1</sup> M.Orita, H.Ohta, M.Hirano, andH.Hosono, *Appl. Phys. Lett.* **77**, 4166 (2000).

- <sup>2</sup> H.He, R.Orlando, M.A.Blanco, R.Pandey, E.Amzallag, I.Baraille, andM.Rérat, *Phys. Rev. B* **74**, 195123 (2006).

- <sup>3</sup> N.Ma, N.Tanen, A.Verma, Z.Guo, T.Luo, H. (Grace)Xing, andD.Jena, *Appl. Phys. Lett.* **109**, 1 (2016).

- <sup>4</sup> S.Rafique, L.Han, M.J.Tadjer, J.A.Freitas, N.A.Mahadik, andH.Zhao, *Appl. Phys. Lett.* **108**, 182105 (2016).

- <sup>5</sup> M.J.Tadjer, T.J.Anderson, T.I.Feygelson, K.D.Hobart, J.K.Hite, A.D.Koehler, V.D.Wheeler, B.B.Pate,

C.R.Eddy, and F.J.Kub, *Phys. Status Solidi* **213**, 893 (2016).

<sup>6</sup> M.Kodama, M.Sugimoto, E.Hayashi, N.Soejima, O.Ishiguro, M.Kanechika, K.Itoh, H.Ueda, T.Uesugi, and T.Kachi, *Appl. Phys. Express* **1**, 021104 (2008).

<sup>7</sup> K.D.Leedy, K.D.Chabak, V.Vasilyev, D.C.Look, J.J.Boeckl, J.L.Brown, S.E.Tetlak, A.J.Green, N.A.Moser, A.Crespo, D.B.Thomson, R.C.Fitch, J.P.Mccandless, and G.H.Jessen, *Appl. Phys. Lett* **111**, 12103 (2017).

<sup>8</sup> Q.T.Thieu, D.Wakimoto, and Y.Koishikawa, *Appl. Phys. Express* **8**, 15503 (2015).

<sup>9</sup> Z.Xia, C.Joishi, S.Krishnamoorthy, S.Bajaj, Y.Zhang, M.Brenner, S.Lodha, and S.Rajan, *IEEE Electron Device Lett.* **39**, 568 (2018).

<sup>10</sup> M.Si, L.Yang, H.Zhou, and P.D.Ye, *ACS Omega* **2**, 49 (2017).

<sup>11</sup> K.D.Chabak, J.P.McCandless, N.A.Moser, A.J.Green, K.Mahalingam, A.Crespo, N.Hendricks, B.M.Howe, S.E.Tetlak, K.Leedy, R.C.Fitch, D.Wakimoto, K.Sasaki, A.Kuramata, and G.H.Jessen, *IEEE Electron Device Lett.* **39**, 67 (2018).

<sup>12</sup> J.Noh, M.Si, H.Zhou, M.J.Tadjer, and P.D.Ye, in *2018 76th Device Res. Conf.* (IEEE, 2018), pp. 1–2.

<sup>13</sup> C.Joishi, Z.Xia, J.Mcglone, Y.Zhang, A.R.Arehart, S.Ringel, S.Lodha, and S.Rajan, *Appl. Phys. Lett* **113**, 123501 (2018).

<sup>14</sup> Z.Hu, K.Nomoto, W.Li, N.Tanen, K.Sasaki, A.Kuramata, T.Nakamura, D.Jena, and H.G.Xing, *IEEE Electron Device Lett.* **39**, 869 (2018).

<sup>15</sup> Z.Hu, K.Nomoto, W.Li, Z.Zhang, N.Tanen, Q.T.Thieu, K.Sasaki, A.Kuramata, T.Nakamura, D.Jena, and H.G.Xing, *Appl. Phys. Lett.* **113**, 122103 (2018).

<sup>16</sup> M.H.Wong, K.Goto, H.Murakami, Y.Kumagai, and M.Higashiwaki, *IEEE Electron Device Lett.* **40**, 431 (2018).

<sup>17</sup> K.D.Chabak, N.Moser, A.J.Green, D.E.Walker, S.E.Tetlak, E.Heller, A.Crespo, R.Fitch, J.P.McCandless, K.Leedy, M.Baldini, G.Wagner, Z.Galazka, X.Li, and G.Jessen, *Appl. Phys. Lett.* **109**, 213501 (2016).

<sup>18</sup> W.Li, K.Nomoto, Z.Hu, T.Nakamura, D.Jena, and H.G.Xing, *Tech. Dig. - Int. Electron Devices Meet. IEDM 2019-Decem*, 270 (2019).

<sup>19</sup> L.Nela, J.Ma, C.Erine, P.Xiang, T.H.Shen, V.Tileli, T.Wang, K.Cheng, and E.Matioli, *Nat. Electron.* **4**, 284 (2021).

<sup>20</sup> Z.Hu, K.Nomoto, W.Li, Z.Zhang, N.Tanen, Q.T.Thieu, K.Sasaki, A.Kuramata, T.Nakamura, D.Jena, and H.G.Xing, *Appl. Phys. Lett.* **113**, 3 (2018).

<sup>21</sup> X.Li and P.W.Bohn, *Appl. Phys. Lett.* **77**, 2572 (2000).

<sup>22</sup> Y.Song, P.K.Mohseni, S.H.Kim, J.C.Shin, T.Ishihara, I.Adesida, andX.Li, IEEE Electron Device Lett. **37**, 970 (2016).

<sup>23</sup> C.Y.Chan, S.Namiki, J.K.Hite, M.A.Mastro, S.B.Qadri, andX.Li, J. Vac. Sci. Technol. A **39**, 053212 (2021).

<sup>24</sup> L.Kong, Y.Song, J.D.Kim, L.Yu, D.Wasserman, W.K.Chim, S.Y.Chiam, andX.Li, ACS Nano **11**, 10193 (2017).

<sup>25</sup> X.Li, Curr. Opin. Solid State Mater. Sci. **16**, 71 (2012).

<sup>26</sup> H.-C.Huang, M.Kim, X.Zhan, K.Chabak, J.D.Kim, A.Kvit, D.Liu, Z.Ma, J.-M.Zuo, andX.Li, (2019).

<sup>27</sup> M.Kim, H.-C.Huang, J.D.Kim, K.D.Chabak, A.Raj, K.Kalapala, W.Zhou, andX.Li, Appl. Phys. Lett **113**, 222104 (2018).

<sup>28</sup> Z.Feng, A.F.M.Anhar Uddin Bhuiyan, M.R.Karim, andH.Zhao, Appl. Phys. Lett. **114**, (2019).

<sup>29</sup> Z.Feng, A.F.M.A.U.Bhuiyan, Z.Xia, W.Moore, Z.Chen, J.F.McGlone, D.R.Daughton, A.R.Arehart, S.A.Ringel, S.Rajan, andH.Zhao, Phys. Status Solidi - Rapid Res. Lett. **14**, 1 (2020).

<sup>30</sup> H.Zhou, S.Alghamdi, M.Si, G.Qiu, andP.D.Ye, IEEE Electron Device Lett. **37**, 1411 (2016).

<sup>31</sup> Z.Huang, N.Geyer, P.Werner, J.deBoor, andU.Gösele, Adv. Mater. **23**, 285 (2011).

<sup>32</sup> A.De andC.E.Pryor, Phys. Rev. B - Condens. Matter Mater. Phys. **81**, (2010).

<sup>33</sup> S.H.Kim, P.K.Mohseni, Y.Song, T.Ishihara, andX.Li, Nano Lett. **15**, 641 (2015).

<sup>34</sup> H.C.Huang, Z.Ren, C.Chan, andX.Li, J. Mater. Res. **36**, 4756 (2021).

<sup>35</sup> S.M.Sze andK.K.Ng, *Physics of Semiconductor Devices* (Wiley-Interscience, 2007).

<sup>36</sup> K.D.Chabak, N.Moser, A.J.Green, D.E.Walker, S.E.Tetlak, E.Heller, A.Crespo, R.Fitch, J.P.McCandless, K.Leedy, M.Baldini, G.Wagner, Z.Galazka, X.Li, andG.Jessen, Appl. Phys. Lett. **109**, 213501 (2016).

<sup>37</sup> Y.Lv, X.Zhou, S.Long, Y.Wang, X.Song, X.Zhou, G.Xu, S.Liang, Z.Feng, S.Cai, X.Fu, A.Pu, andM.Liu, Phys. Status Solidi - Rapid Res. Lett. **14**, 1 (2020).

<sup>38</sup> W.Hao, Q.He, K.Zhou, G.Xu, W.Xiong, X.Zhou, G.Jian, C.Chen, X.Zhao, andS.Long, Appl. Phys. Lett. **118**, 0 (2021).

<sup>39</sup> M.Higashiwaki, K.Sasaki, A.Kuramata, T.Masui, andS.Yamakoshi, Appl. Phys. Lett. **100**, 013504 (2012).

<sup>40</sup> M.H.Wong, K.Goto, H.Murakami, Y.Kumagai, andM.Higashiwaki, IEEE Electron Device Lett. **PP**, 1 (2018).

<sup>41</sup> Y.Zhang, A.Neal, Z.Xia, C.Joishi, J.M.Johnson, Y.Zheng, S.Bajaj, M.Brenner, D.Dorsey, K.Chabak, G.Jessen, J.Hwang, S.Mou, J.P.Heremans, andS.Rajan, Appl. Phys. Lett. **112**, 173502 (2018).

<sup>42</sup> C.Joishi, Y.Zhang, Z.Xia, W.Sun, A.R.Arehart, S.Ringel, S.Lodha, andS.Rajan, IEEE Electron Device Lett. **40**, 1241 (2019).

<sup>43</sup> K.Zeng, A.Vaidya, andU.Singisetti, Appl. Phys. Express **12**, 1 (2019).

<sup>44</sup> H.Gong, F.Zhou, W.Xu, X.Yu, Y.Xu, Y.Yang, F.F.Ren, S.Gu, Y.Zheng, R.Zhang, H.Lu, andJ.Ye, IEEE Trans. Power Electron. **36**, 12213 (2021).

<sup>45</sup> N.Allen, M.Xiao, X.Yan, K.Sasaki, M.J.Tadjer, J.Ma, R.Zhang, H.Wang, andY.Zhang, IEEE Electron Device Lett. **40**, 1399 (2019).

<sup>46</sup> N.K.Kalarickal, Z.Xia, J.F.McGlone, Y.Liu, W.Moore, A.R.Arehart, S.A.Ringel, andS.Rajan, J. Appl. Phys. **127**, 215706 (2020).

<sup>47</sup> J.K.Mun, K.Cho, W.Chang, H.-W.Jung, andJ.Do, ECS J. Solid State Sci. Technol. **8**, Q3079 (2019).

<sup>48</sup> B.Song, A.K.Verma, K.Nomoto, M.Zhu, D.Jena, andH.G.Xing, Device Res. Conf. - Conf. Dig. DRC **2016-Augus**, 2016 (2016).

<sup>49</sup> Y.Lü, X.Song, Z.He, Y.Wang, X.Tan, S.Liang, C.Wei, X.Zhou, andZ.Feng, J. Semicond. **40**, 83 (2019).

<sup>50</sup> K.D.Chabak, J.P.Mccandless, N.A.Moser, A.J.Green, K.Mahalingam, A.Crespo, N.Hendricks, B.M.Howe, S.E.Tetlak, K.Leedy, R.C.Fitch, D.Wakimoto, K.Sasaki, A.Kuramata, andG.H.Jessen, IEEE Electron Device Lett. **39**, 67 (2018).

<sup>51</sup> H.Zhou, M.Si, S.Alghamdi, G.Qiu, L.Yang, andP.D.Ye, IEEE Electron Device Lett. **38**, 103 (2017).

<sup>52</sup> M.H.Wong, K.Sasaki, A.Kuramata, S.Yamakoshi, andM.Higashiwaki, IEEE Electron Device Lett. **37**, 212 (2016).