# Robustness of Passivated ALD Zinc Tin Oxide TFTs to Aging and Bias Stress

Christopher R. Allemang<sup>✉</sup>, Member, IEEE, Tae H. Cho<sup>✉</sup>, Neil P. Dasgupta<sup>✉</sup>, and Rebecca L. Peterson<sup>✉</sup>, Senior Member, IEEE

**Abstract**—Thin-film electronics fabricated with amorphous oxide semiconductors (AOS) are being studied for beyond-display technologies because of their superior electron transport. To widen the commercial applications, robust devices fabricated using scalable deposition techniques are required. Here, we fabricate bottom-gate, top contact thin-film transistors (TFTs) using zinc tin oxide, an AOS deposited by atomic layer deposition (ALD), and study robustness to aging and bias stress for devices stored in a dark air ambient with and without  $\text{Al}_2\text{O}_3$  passivation. All samples exhibit excellent mobility ( $\mu_{\text{FE}}$ ) and subthreshold swing (SS) robustness to aging. Most of the device aging occurs within the first 25 days, after which the performance stabilizes. Changes due to positive bias stress, which are dominated by interactions with ambient molecules, are greatly reduced by passivation. Passivation, however, results in an increase in contact resistance ( $R_C$ ), SS, and negative bias illumination stress (NBIS) instability. The increase in  $R_C$  is attributed to the diffusion of oxygen vacancies that occurs during the passivation process, while the increase in SS and NBIS instability is attributed to subgap interface defects. The experimental results are compared to Silvaco ATLAS simulations to confirm the proposed physical mechanisms and allow quantification of the associated defects and non-idealities.

**Index Terms**—Amorphous semiconductors, current-voltage characteristics, stability, thin-film transistors.

## I. INTRODUCTION

ELECTRONIC circuits comprised of thin-film transistors (TFTs) are essential to nearly every modern display technology. For decades, the TFT industry relied on

Manuscript received 17 September 2022; accepted 18 October 2022. Date of publication 2 November 2022; date of current version 30 November 2022. This work was supported by the National Science Foundation under Grant CMMI-1727918. The review of this article was arranged by Editor J.-S. Park. (Corresponding author: Rebecca L. Peterson.)

Christopher R. Allemang was with the Electrical Engineering and Computer Science Department, University of Michigan, Ann Arbor, MI 48109 USA. He is now with Sandia National Laboratories, Albuquerque, NM 87185 USA.

Tae H. Cho is with the Department of Mechanical Engineering, University of Michigan, Ann Arbor, MI 48109 USA.

Neil P. Dasgupta is with the Department of Mechanical Engineering and the Department of Materials Science and Engineering, University of Michigan, Ann Arbor, MI 48109 USA.

Rebecca L. Peterson is with the Department of Electrical Engineering and Computer Science and the Department of Materials Science and Engineering, University of Michigan, Ann Arbor, MI 48109 USA (e-mail: blpeters@umich.edu).

Color versions of one or more figures in this article are available at <https://doi.org/10.1109/TED.2022.3216791>.

Digital Object Identifier 10.1109/TED.2022.3216791

amorphous silicon for the active layer; however, increasing performance demands require semiconductors with superior electron transport. Amorphous oxide semiconductors (AOS) can meet those performance demands [1] and sputtered indium-gallium-zinc-oxide (IGZO), a widely studied AOS, has been successfully commercialized as the active layer of display backplane TFTs [2]. Furthermore, there is a growing interest in developing thin-film electronics for beyond-display technologies, enabled by the superior performance of AOS. These include monolithic 3-D integration on Si CMOS integrated circuits (ICs) [3]. All of these applications require devices with excellent robustness to aging (i.e., stability under ambient conditions) and robustness to electrical bias stress.

While  $\text{In}_2\text{O}_3$  [4] and IGZO [5] TFTs with low process temperature and excellent performance have been demonstrated, here we focus on an indium-free AOS material, zinc tin oxide (ZTO), because indium is comparatively scarce and costly [6], [7], [8]. ZTO has been studied using various deposition techniques including solution [9] and vacuum-based processes [10], [11], [12], [13], [14]. Here we use atomic layer deposition (ALD) because it is a low-temperature vapor-phase deposition method allowing for conformal and uniform thin-films with precise control over interfaces, stoichiometry, and thicknesses [15]. Previous work on aging of ZTO TFTs used ZTO films made by sputtering [16] or solution-based processes [17], [18]. These works attributed observed increases in subthreshold swing and threshold voltages as well as changes in ON and OFF current to water or oxygen adsorption or desorption at the back channel. The only investigation of aging with back channel passivated devices (using  $\text{TiO}_2$ ) was limited to 20 days of aging [16]. No study has been done linking ZTO process conditions to aging effects, and no aging study has been done using ZTO films made by ALD. Similarly, for bias stress measurements, most of the existing work is on ZTO films deposited by sputtering [19], [20] or solution processing [21]. The only known work on bias stress in ALD ZTO TFTs tested only negative bias stress (NBS) up to 3000 s [10], which does not allow assessment of the ionization of bulk oxygen vacancies, which is traditionally done in AOS by negative bias illumination stress (NBIS) [22]. Since it is known that device robustness varies with deposition technique [23], here, we seek to address these knowledge gaps by investigating aging, positive bias stress (PBS), and NBIS in ALD ZTO.

In this study, we examine the robustness of ALD ZTO TFT threshold voltage,  $V_t$ , field-effect mobility,  $\mu_{\text{FE}}$ , hysteresis,  $\Delta V_c$ , and subthreshold swing, SS, to aging and bias stress prepared under two different sets of process conditions, with and without a passivation layer. Devices without a passivation

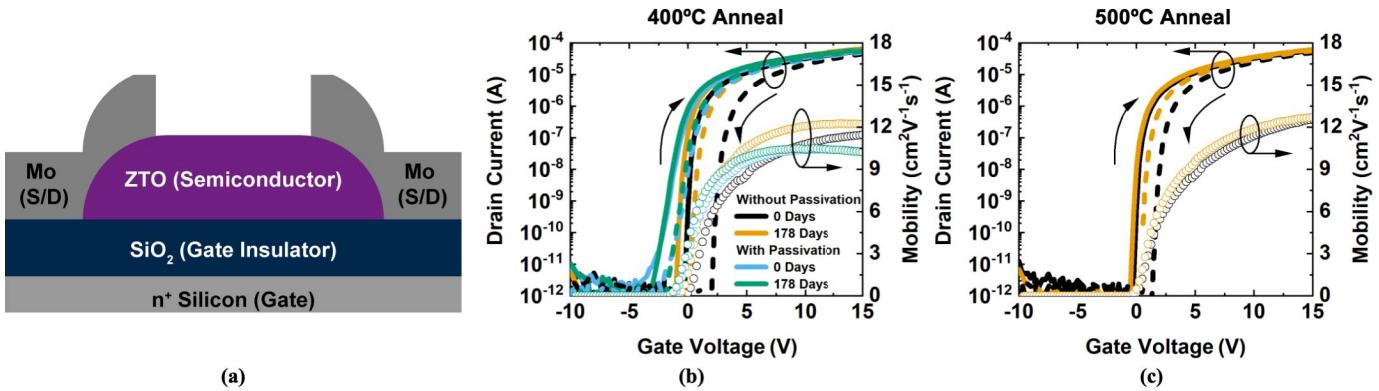

**Fig. 1.** (a) Schematic illustration of a ZTO TFT cross section with bottom-gate top-contact structure. Representative transfer characteristics ( $I_D$ – $V_{GS}$ ) with  $V_{DS} = 1$  V are plotted on the left  $y$ -axis for devices without passivation on the first day of measurement (black) and after 178 days of aging (yellow) with ZTO annealed at (b) 400 °C and (c) 500 °C. In (b), we show traces for 400 °C annealed devices with passivation on the first day of measurement (blue) and after 178 days of aging (green). The forward  $I$ – $V$  curves are indicated by the solid lines and the reverse  $I$ – $V$  curves are indicated by the dashed lines. Linear field effect mobility extracted from these  $I$ – $V$  curves are plotted on the right  $y$ -axis using open circles.

layer show minor changes in  $V_t$  and  $\Delta V_c$  during the first 25 days of aging in a dark air ambient, after which they stabilize. Passivation greatly improves robustness to aging and PBS but also results in a one-time decrease in  $V_t$  and increases in SS and contact resistance, which are extracted using the transmission line method (TLM). Silvaco Atlas simulations are used to show that these one-time changes in  $V_t$  and SS are likely due to back-channel interface states induced during the deposition of the passivation layer. NBIS is reduced by using optimal ZTO process conditions but is not eliminated by passivation. The work presented here demonstrates the robustness of passivated ALD ZTO TFTs to aging and bias stress, which paves the way for their adoption in thin-film electronics for beyond-display technologies.

## II. EXPERIMENTAL METHODS

TFTs were fabricated on heavily doped n<sup>+</sup>-Si with approximately 100 nm of thermal oxide grown to form the gate and gate insulator, respectively, in a bottom-gate top-contact structure schematically illustrated in Fig. 1(a). The active layer, approximately 12 nm of ZTO, was deposited by ALD using a Veeco Fiji G2 flow-type ALD tool at a deposition temperature of 150 °C with a hybrid thermal H<sub>2</sub>O and O<sub>2</sub>-plasma process and a 45% Sn cycle ratio which is expected to yield a film with approximately 21 at. % Sn content, as described in [24]. The ZTO films were then wet-etched for device isolation before being annealed at either 400 °C or 500 °C on a hotplate in an air ambient in a custom-built moisture-controlled glovebox with less than 20% relative humidity [25]. Finally, approximately 100 nm of molybdenum was deposited by sputtering and patterned by lift-off to form source-drain ohmic contacts [26]. Devices have channel lengths,  $L$ , and widths,  $W$ , of 10 and 120  $\mu$ m, respectively, unless otherwise stated. Passivated devices were encapsulated with approximately 30 nm of Al<sub>2</sub>O<sub>3</sub> deposited by ALD at 100 °C in a Veeco/Cambridge Nanotech Savannah system using an ozone process [27], chosen to reduce the  $V_t$  shift introduced by passivation [28]. Samples were stored and aged at room temperature in a dark air ambient between measurements.

Temporal stability and TLM measurements were taken using a Keysight B1505A power device analyzer while bias stress measurements were taken using an HP4156A semiconductor

parameter analyzer. All measurements were taken at room temperature in an air ambient using continuous voltage sweeps. When both forward and reverse  $I$ – $V$  curves are shown, the measurement was first taken in the forward direction, negative to positive  $V_{GS}$ , immediately followed by the reverse direction, positive to negative  $V_{GS}$ . PBS was applied by biasing the gate at +20 V while the source and drain were kept at 0 V. NBIS was applied by biasing the gate at -20 V while the source and drain were kept at 0 V under the illumination of a green LED (520 nm) with an optical power density of 900  $\mu$ W cm<sup>-2</sup>. All other measurements were taken in the dark.

The linear field-effect mobility,  $\mu_{FE}$ , is extracted using the equation  $\mu_{FE} = (dI_D/dV_{GS})L(WC_{ox}V_{DS})^{-1}$  where  $C_{ox}$  refers to the oxide capacitance per unit area and  $dI_D/dV_{GS}$  is the slope of the  $I_D$ – $V_{GS}$  curve in the linear region.  $\mu_{FE}$  values were extracted from the  $I_D$ – $V_{GS}$  curve over the range 13 V <  $V_{GS}$  < 15 V with  $V_{DS} = 1$  V, unless otherwise stated. The threshold voltage,  $V_t$ , was found to be the  $x$ -axis intercept of a linear fit to the linear region of an  $I_D$ – $V_{GS}$  sweep with  $V_{DS} = 1$  V. The subthreshold swing, SS, is the inverse of the logarithmic rate of device current turn-on, in units of volts per decade of current. Hysteresis,  $\Delta V_c$ , is defined as the difference in the value of  $V_{GS}$  at  $I_D = 100$  nA between the forward and reverse sweeps when  $V_{GS}$  is swept between -10 and 30 V.

Silvaco ATLAS was used to conduct 2-D numerical simulations of the TFTs to understand the changes in device performance with the addition of a passivation layer. Simulation parameters and fitting processes from [29], [30] were used as a starting point and then iterated to fit the device characteristics presented here, similar to the method described in [31]. The final band model of the subgap states is shown in Fig. 2 (parameters found in Table I) where BG refers to the ZTO/gate insulator interface, BC refers to the ZTO/passivation interface, and IT refers to parameters applied to both BG and BC where BC parameters were only applied to simulations that include a passivation layer.

## III. RESULTS AND DISCUSSION

The transfer characteristics for devices without passivation and annealed at 400 °C and 500 °C are shown in Fig. 1(b) and (c), respectively, and are summarized in Table II for 0 and 178 days of aging. The excellent performance of unaged devices has been discussed in [24]. For both samples without passivation, the  $\mu_{FE}$  and SS before and after 178 days

Fig. 2. (a) Band structure of bulk ZTO and (b) interfaces used in Silvaco ATLAS simulations. For (b), solid lines indicate the semiconductor/gate insulator interface (BG) used in all simulations while the dashed lines indicate the semiconductor/passivation interface (BC) used in simulations including a passivation layer.

TABLE I

PARAMETERS USED IN SILVACO ATLAS SIMULATIONS

| Symbol (Unit)                                  | Description                            | Value                  |

|------------------------------------------------|----------------------------------------|------------------------|

| $\mu_n(\text{cm}^2\text{V}^{-1}\text{s}^{-1})$ | Electron Mobility                      | 13.46                  |

| $N_C/N_V(\text{cm}^{-3})$                      | Conduction/Valence Band Effective DOS  | $4.14 \times 10^{18}$  |

| $E_G(\text{eV})$                               | Band Gap                               | 3.08                   |

| $N_{TA}/N_{TD}(\text{cm}^{-3}\text{eV}^{-1})$  | Tail Acceptor/Donor State Peak Density | $8.25 \times 10^{19}$  |

| $W_{TA}(\text{eV})$                            | Tail Acceptor State Width              | 0.019                  |

| $W_{TD}(\text{eV})$                            | Tail Donor State Width                 | 0.1                    |

| $N_{GD}(\text{cm}^{-3}\text{eV}^{-1})$         | Gaussian Donor State Peak Density      | $6.5 \times 10^{16}$   |

| $E_{GD}(\text{eV})$                            | Gaussian Donor State Peak Position     | 2.93                   |

| $W_{GD}(\text{eV})$                            | Gaussian Donor State Peak Width        | 0.05                   |

| $N_{TA,IT}(\text{cm}^{-3}\text{eV}^{-1})$      | IT Tail Acceptor State Peak Density    | $8.34 \times 10^{11}$  |

| $N_{TD,IT}(\text{cm}^{-3}\text{eV}^{-1})$      | IT Tail Donor State Peak Density       | $2.25 \times 10^{16}$  |

| $W_{TA,IT}(\text{eV})$                         | IT Tail Acceptor State Width           | 0.19                   |

| $Q_{F,BG}(\text{cm}^{-2})$                     | BG Fixed Charge                        | $-5.20 \times 10^{10}$ |

| $W_{TD,BG}(\text{eV})$                         | BG Tail Donor State Width              | 0.1                    |

| $Q_{F,BC}(\text{cm}^{-2})$                     | BC Fixed Charge                        | $2.38 \times 10^{11}$  |

| $W_{TD,BC}(\text{eV})$                         | BC Tail Donor State Width              | 0.28                   |

| $N_{GD,BC}(\text{cm}^{-3}\text{eV}^{-1})$      | BC Gaussian Donor State Peak Density   | $6.5 \times 10^{17}$   |

| $E_{GD,BC}(\text{eV})$                         | BC Gaussian Donor State Peak Position  | 2.334                  |

| $W_{GD,BC}(\text{eV})$                         | BC Gaussian Donor State Peak Width     | 0.05                   |

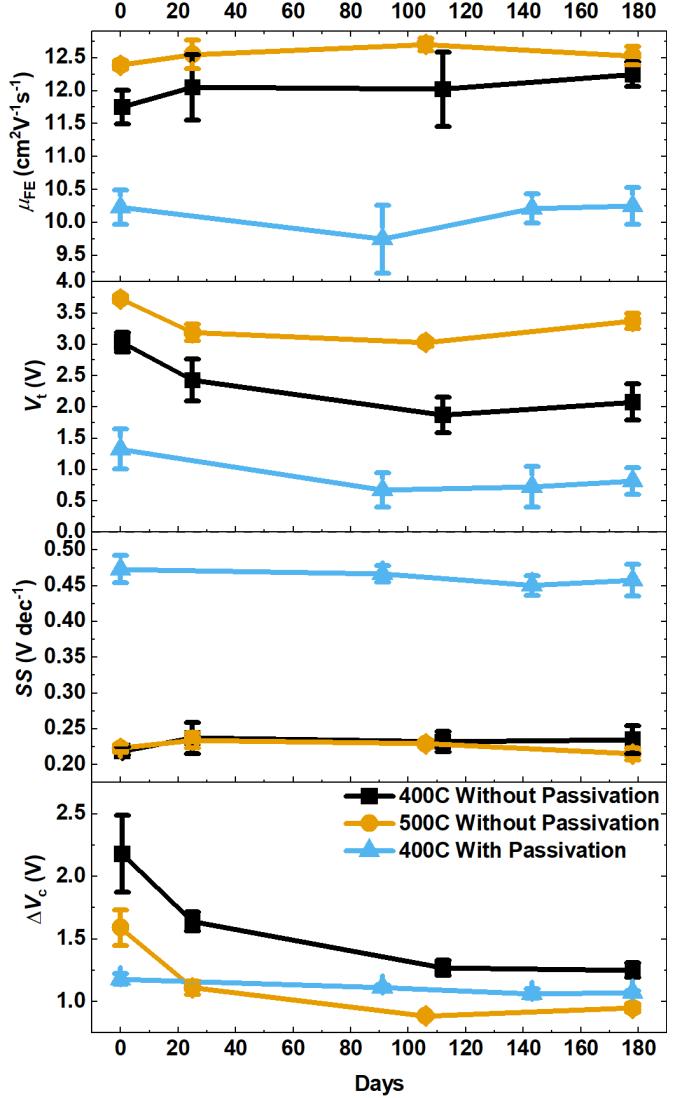

of aging agree within the measured standard deviation. (Five devices of each type were measured on each date.) The stability of  $\mu_{FE}$  indicates the bulk tail acceptors at the conduction band edge do not change with time [32], while the stability of  $SS$  indicates a stable semiconductor/gate insulator interface [33]. There are, however, statistically significant decreases in  $V_t$  and  $\Delta V_c$  within the first 25 days of aging (see Fig. 3).

It has previously been found for AOS TFTs that robustness to aging and bias stress varies with the ambient atmosphere [34], the thickness of the active layer [35], [36], active layer structure [37], and passivation [38], [39]. Ambient interactions can include the exchange of water and oxygen molecules, where water can act as an electron donor [35], [36] or an acceptor-like trap [40] and oxygen acts as an electron trap [35], [36], [40]. Passivation layers have been applied to prevent interactions with ambient mole-

Fig. 3. Electrical characteristics of TFTs as they age. Symbols indicate the average of five measured devices and error bars indicate the standard deviation. The devices were aged at room temperature in a dark air ambient.

cules [35], [38], [39], [41]. Building on this literature, there are at least two possible explanations for the decrease in  $V_t$  with aging observed here. The first is the adsorption of water molecules that would then act as electron donors [35], [36]. This explanation is unlikely to apply here because water has been shown to act as an electron donor only in thicker AOS films [36] and adsorption/desorption of water should also correspond to an increase in hysteresis [40], which is not seen for these devices (see Fig. 3). The other, more likely explanation is an increase in the oxygen vacancies that are native defect dopants and the main contributor to free electrons in AOS materials [42]. As  $V_t$  stabilizes after 25 days of aging (see Fig. 3), the concentration of oxygen vacancies must reach an equilibrium value during that time due to kinetic constraints or a self-limiting reaction [43]. Hysteresis, however, continues to vary after 25 days of aging (see Fig. 3) because of interactions between ambient molecules and the exposed AOS surface, commonly referred to as the back-channel, requiring passivation to inhibit these interactions [27], [36].

TABLE II

AVERAGE ELECTRICAL CHARACTERISTICS OF TFTs. THE STANDARD DEVIATION FOR EACH VALUE IS SHOWN IN FIG. 3

|                           |          | $\mu_{FE}$<br>( $\text{cm}^2\text{V}^{-1}\text{s}^{-1}$ ) | $V_t$<br>(V) | $SS$<br>(V dec $^{-1}$ ) | $\Delta V_c$<br>(V) |

|---------------------------|----------|-----------------------------------------------------------|--------------|--------------------------|---------------------|

| 400°C without passivation | 0-day    | 11.8                                                      | 3.03         | 0.220                    | 2.18                |

|                           | 178-days | 12.2                                                      | 2.08         | 0.235                    | 1.25                |

|                           | Change   | 0.4                                                       | -0.95        | 0.015                    | -0.92               |

| 500°C without passivation | 0-day    | 12.4                                                      | 3.73         | 0.223                    | 1.59                |

|                           | 178-days | 12.5                                                      | 3.37         | 0.215                    | 0.949               |

|                           | Change   | 0.1                                                       | -0.36        | -0.008                   | -0.641              |

| 400°C with passivation    | 0-day    | 10.2                                                      | 1.32         | 0.473                    | 1.18                |

|                           | 178-days | 10.3                                                      | 0.815        | 0.458                    | 1.07                |

|                           | Change   | 0.1                                                       | -0.505       | -0.015                   | -0.11               |

As the 400 °C and 500 °C annealed devices without passivation show similar trends with aging, studies implementing an Al<sub>2</sub>O<sub>3</sub> passivation layer were only performed on devices with a 400 °C anneal as that process is within the 450 °C thermal budget for 3-D monolithic integration [44]. Like the samples without passivation, the passivated TFTs'  $\mu_{FE}$  and  $SS$  values are largely invariant with aging, and  $V_t$  shows an initial shift and then stabilizes (see Fig. 3). The passivated TFTs show a smaller initial value of  $\Delta V_c$  compared to the unpassivated devices, but  $\Delta V_c$  shows the same trend: it decreases to a value of  $\sim 1$  V during the first 100 days of aging. Since the passivation layer is expected to largely inhibit ambient interactions, the residual  $\sim 1$  V of hysteresis observed may be due to the trapping and detrapping of electrons into defect states at the BC [43], [45].

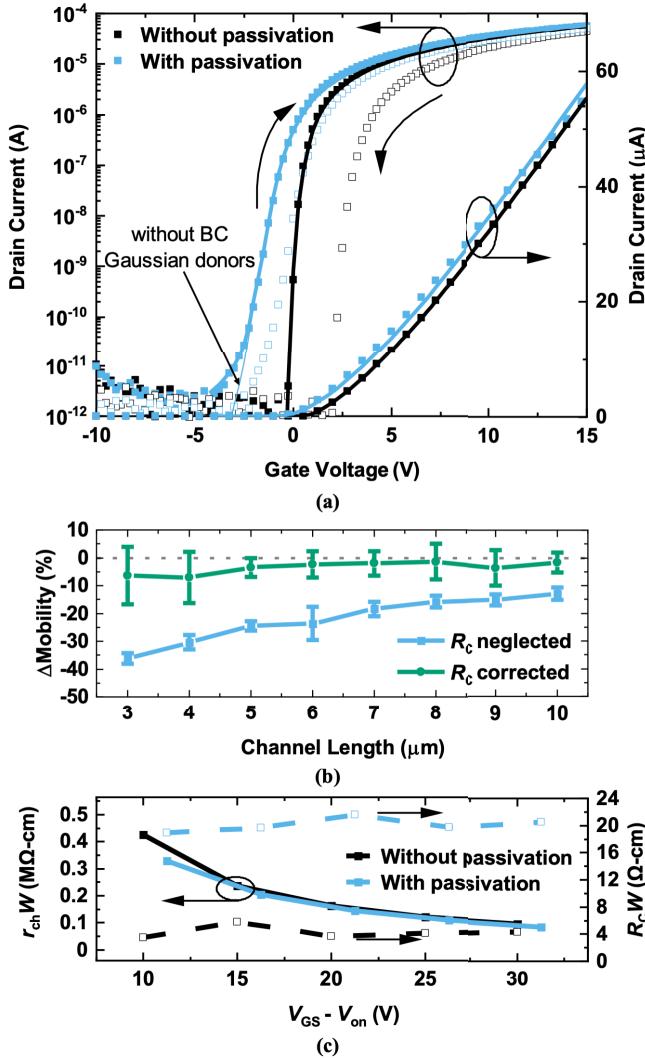

Transfer characteristics for 400 °C annealed devices with and without passivation are shown in Fig. 4(a). From these transfer curves, there is a notable decrease in  $V_t$  and  $\Delta V_c$  and an increase in  $SS$  with passivation. The reduction of  $\Delta V_c$  with passivation is an expected result because the main contributor to hysteresis for devices without passivation—interactions between ambient molecules and the back-channel—is blocked by passivation, and is now attributed to BC defect states [40]. Silvaco ATLAS simulations [see Fig. 4(a)] performed with the parameters listed in Table I were used to explain the change in  $SS$  and  $V_t$  with passivation. The simulated Gaussian distribution of donor states at the BC [see Fig. 2(b)] creates a second parallel channel that results in a kink in the subthreshold  $I_D$  between  $-5$  and  $-2$  V  $V_{GS}$  [see Fig. 4(a)], while the tail donors increase the  $SS$  of the main channel [46]. The parallel negative shift in  $V_t$  was modeled by a positive fixed charge at the BC that may result from reactions with highly reactive trimethylaluminum or ozone [41], positive fixed charge in the bulk Al<sub>2</sub>O<sub>3</sub> passivation layer [47], or defect modulation doping [48]. The kink in the subthreshold  $I_D$  is no longer present in the aged sample, indicating the reduction of BC states with time.

The TFT mobility after passivation was measured for five devices at each gate length. For TFTs with  $L = 10 \mu\text{m}$ , passivation reduces the average  $\mu_{FE}$  from 11.8 to 10.2  $\text{cm}^2\text{V}^{-1}\text{s}^{-1}$ , a reduction of  $\sim 14\%$ . The percentage change in  $\mu_{FE}$  with passivation increases as  $L$  decreases, as shown in Fig. 4(b). This apparent  $\mu_{FE}$  degradation as  $L$  decreases may be caused by non-negligible contact resistance,  $R_C$ . That is, as  $L$  decreases,  $R_C$  becomes a larger portion of the total resistance, effectively

reducing the voltage,  $V_{DS}$ , across the channel by  $I_{DS}R_C$ . The  $\mu_{FE}$  equation given above neglects  $R_C$ . It can be included by replacing  $V_{DS}$  with  $V_{DS} - ((R_C V_{DS}) R_{\text{Tot}}^{-1})$ , where  $R_{\text{Tot}} = R_C + r_{\text{ch}}L$  and  $r_{\text{ch}}$  is the channel resistance [26]. To assess the impact of contact resistance, TLM measurements were used to extract  $r_{\text{ch}}$  and  $R_C$  values for devices with and without passivation, as shown in Fig. 4(c). As expected,  $r_{\text{ch}}$  decreases as  $V_{GS}$  increases (as the channel charge increases), while  $R_C$  stays constant. The fact that  $r_{\text{ch}}$  does not change with passivation indicates that the bulk ZTO is unchanged. In contrast, the value of  $R_C$  increases by approximately a factor of five after passivation. The measured  $R_C$  values are used to correct the extracted values of  $\mu_{FE}$ . The analysis is plotted in Fig. 4(b). The corrected  $\mu_{FE}$  values show no dependence on gate length, indicating that the  $5 \times$  increase in  $R_C$  likely causes the apparent decrease in  $\mu_{FE}$  following passivation.

During the passivation process, the sample is placed in an ALD chamber and exposed to a vacuum environment at 100 °C. These conditions may cause an increase in contact resistance with passivation. To test whether these conditions would increase the contact resistance, a sample with identical ZTO film was prepared and  $R_C$  was estimated. The fresh sample has an estimated contact resistance of about 6.89 Ω-cm, similar to the 0 day device without passivation (4.19 Ω-cm). To test whether a vacuum treatment would impact  $R_C$ , the sample was placed in a vacuum chamber for one hour and re-measured in an air ambient. Vacuum treatment caused the estimated  $R_C$  to increase to about 13.5 Ω-cm. Subsequently, the sample was annealed for one hour in a vacuum at 100 °C to test whether a vacuum anneal would change the contact resistance. After the vacuum annealing, the estimated  $R_C$  further increases to about 19.8 Ω-cm, similar to the 0-day device with passivation (20.0 Ω-cm). Therefore, the increase in contact resistance with passivation may be attributed to the coincidental vacuum anneal of the ALD passivation process. Contact resistance may increase during a vacuum anneal because the oxygen vacancies induced by the top metallization process [26], [49] will readily diffuse from the metal/semiconductor junction increasing the potential barrier and, therefore, the interfacial contact resistance [50]. Further work is required to verify these proposed mechanisms. Nonetheless, from the aging stability of  $\mu_{FE}$  we can conclude that the contact resistance—after undergoing the one-time change induced during passivation—appears stable under aging.

Fig. 4. (a) Experimental (symbols) and simulated (lines)  $I_D$ - $V_{GS}$  curves for 0 day 400 °C annealed ZTO devices. Closed symbols indicate forward sweeps while open symbols indicate reverse sweeps. The experimental data is the same as that shown in Fig. 1(b). (b) Percent change in  $\mu_{FE}$  due to passivation as a function of channel length for 0 day 400 °C annealed ZTO devices.  $R_C$  neglected (blue) does not account for  $V_{DS}$  dropped across the contacts while  $R_C$  corrected (green) does. Symbols and error bars indicate averages and standard deviations of five devices, respectively. (c) Width-normalized channel resistance (left y-axis) and contact resistance (right y-axis) as a function of  $V_{GS} - V_{on}$  as extracted using TLM for 0 day 400 °C annealed ZTO devices.

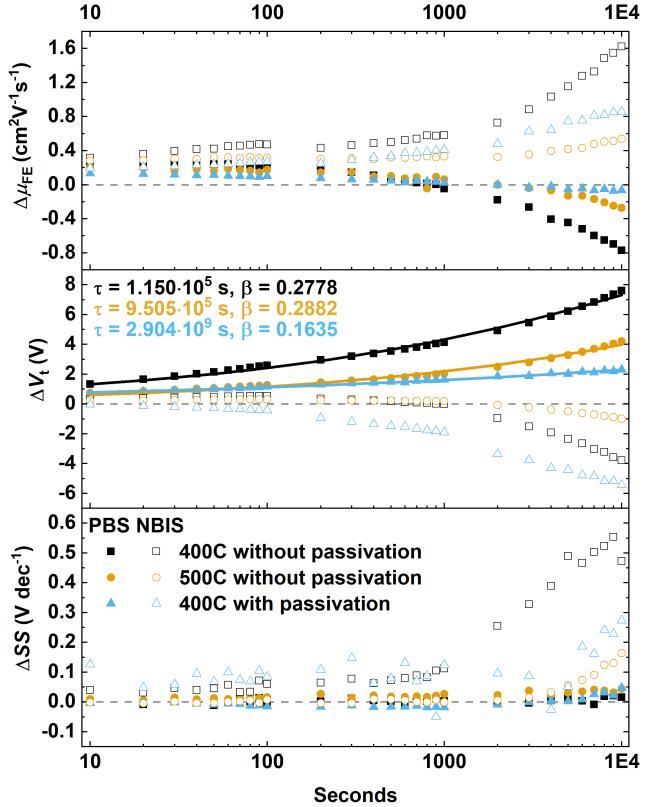

In contrast, the bias stress stability is dependent on the stress time and magnitude, where longer stress times and larger magnitudes generally result in larger changes [35], [36]. These changes can result from creation of defect states near the gate insulator/semiconductor interface [51], charge trapping in the gate insulator [52], or interactions with ambient molecules [53]. The reliability of the aged devices was studied by PBS and NBIS, and the results are shown in Fig. 5. Under PBS, there is an increase in  $V_t$  with increasing stress time for all samples. The source of the PBS for the 400 °C device without passivation is related to the interaction between the ambient oxygen and the back channel and can be described by the stretched exponential,  $\Delta V_t(t) = \Delta V_{t0}[1 - \exp(-(t/\tau)^\beta)]$  where  $\Delta V_{t0} = V_{\text{stress}} - V_t(t = 0 \text{ s})$ ,  $\beta$  is the stretched exponential, and  $\tau$  is the characteristic trapping time of carriers [53]. In the  $\Delta V_t$  plot in Fig. 5, the filled symbols indicate the measured change in  $V_t$  with time while the line indicates the

Fig. 5. Change in  $\mu_{FE}$ ,  $V_t$ , and SS with stress time. The filled symbols indicate PBS, the open symbols indicate NBIS, and the lines in the plot of  $\Delta V_t$  are fits to the stretched-exponential equation for PBS  $\Delta V_t$ .

$\Delta V_t(t)$  fit equation. For the devices without passivation,  $\tau$  is on the order of  $10^5$  s which is in line with previous ZTO results attributed to oxygen adsorption [54]. After passivation, however,  $\tau$  increases to approximately  $10^9$  s, indicating a significant increase in stability, as observed previously in IGZO [55]. Recent work on RF sputtered and microwave annealed IGZO reports a value of  $\tau$  on the order of  $10^8$  s significantly better than our devices without passivation but an order of magnitude lower than our passivated devices, indicating our passivation process may offer a way to improve stability to PBS [56]. Without passivation,  $\beta$  is approximately 0.28 while after passivation it decreases to 0.16. These changes in  $\tau$  and  $\beta$  indicate that the dominant charge trapping shifts from oxygen adsorption without passivation to interface states (likely the shallow Gaussian donors) after passivation, and that an improved passivation layer, with reduced interface states, could further reduce  $\Delta V_t$  from PBS.

Under NBIS, there is a decrease in  $V_t$  with increasing stress time for all samples. The source of negative  $V_t$  shift in AOS materials with NBIS has been attributed to the photo-ionization of oxygen vacancy sites from  $\text{V}_O$  to  $\text{V}_O^{2+}$  which occurs under the combination of visible light  $\sim 2.3$  eV and negative gate bias. These  $\text{V}_O^{2+}$  states contribute free electrons, causing parallel negative  $V_t$  shifts and persistent photoconductivity [57]. The neutral oxygen vacancy sites and/or local under-coordination of oxygen can be correlated with the simulated valence band tail-states with a density of  $\sim 10^{20} \text{ cm}^{-3}$  (see Fig. 2), and are experimentally observable in absorption spectra as subgap absorption [58], [59]. The larger negative  $V_t$  shift of the 400 °C samples with and without passivation, compared to that of the 500 °C sample, maybe due to a greater concentration of subgap defects. The

passivated sample exhibits the largest negative  $V_t$  shift with NBIS, likely due to the presence of donor-like tail states at the back channel/passivation interface [see Fig. 2(b)] [22], [60]. Between 1000 and 2000 s,  $|\Delta V_t|$  exceeds 2.5 V, while similar work on ALD IGZO devices passivated with ALD  $\text{Al}_2\text{O}_3$  showed  $|\Delta V_t| = 2.5$  V after 3600 s [61] indicating there is room to improve our devices by lowering the interface state density at the passivation interface. In addition to a negative  $V_t$  shift, the 400 °C annealed sample without passivation shows a large increase in SS with increased NBIS time. The other two samples also show an increase in SS for stress times greater than approximately 4000 s. These SS increases may be due to changes in subgap defect states or interface states [51].

The mobility values for Fig. 5 were extracted using the same gate over-drive voltage for every measurement for a given sample to reduce the impact of  $\Delta V_t$  on mobility extraction. Even with this method of extraction, there are clear trends in the mobility for samples without passivation where PBS causes a decrease in  $\mu_{FE}$  and NBIS causes an increase in  $\mu_{FE}$ . The decrease in  $\mu_{FE}$  with PBS can be understood from the interaction of carriers with the chemisorbed oxygen that also causes the positive  $V_t$  shift. As the passivated sample does not suffer from interaction with ambient molecules, the  $\Delta\mu_{FE}$  with PBS is significantly reduced for that sample. The increase in  $\mu_{FE}$  with NBIS can be understood as the increase in free carriers resulting in more band-like conduction with higher mobility.

#### IV. CONCLUSION

Understanding and improving the robustness of AOS TFTs fabricated using promising techniques such as ALD to aging and bias stress is critical for their adoption in beyond-display technologies. Here, we have investigated the robustness of BEOL-compatible zinc tin oxide n-TFTs with and without back-channel passivation. Devices without passivation exhibit slight changes within the first 25 days of aging and then excellent temporal stability. PBS instability, predominately caused by interactions with ambient molecules in samples without passivation, is significantly reduced for samples with passivation. However, the passivation method used here also causes an increase in contact resistance and SS, and does not completely eliminate NBIS instabilities. Future experiments considering different passivation/etch stop layer materials and processes, and informed by simulation, are needed to reduce the interface defect density at the back channel, and to confirm the physical mechanism driving the increased contact resistance following  $\text{Al}_2\text{O}_3$  deposition.

#### ACKNOWLEDGMENT

Portions of this work were performed in the Lurie Nanofabrication Facility, which is supported by the University of Michigan's College of Engineering.

#### REFERENCES

- [1] K. Nomura, H. Ohta, A. Takagi, T. Kamiya, M. Hirano, and H. Hosono, "Room-temperature fabrication of transparent flexible thin-film transistors using amorphous oxide semiconductors," *Nature*, vol. 432, no. 4016, pp. 488–492, Nov. 2004, doi: [10.1038/nature03090](https://doi.org/10.1038/nature03090).

- [2] L. Petti et al., "Metal oxide semiconductor thin-film transistors for flexible electronics," *Appl. Phys. Rev.*, vol. 3, no. 2, Jun. 2016, Art. no. 021303, doi: [10.1063/1.4953034](https://doi.org/10.1063/1.4953034).

- [3] Y. Son, B. Frost, Y. Zhao, and R. L. Peterson, "Monolithic integration of high-voltage thin-film electronics on low-voltage integrated circuits using a solution process," *Nature Electron.*, vol. 2, no. 11, pp. 540–548, Nov. 2019, doi: [10.1038/s41928-019-0316-0](https://doi.org/10.1038/s41928-019-0316-0).

- [4] M. Si, A. Charnas, Z. Lin, and P. D. Ye, "Enhancement-mode atomic-layer-deposited  $\text{In}_2\text{O}_3$  transistors with maximum drain current of 2.2 A/mm at drain voltage of 0.7 V by low-temperature annealing and stability in hydrogen environment," *IEEE Trans. Electron Devices*, vol. 68, no. 3, pp. 1075–1080, Mar. 2021, doi: [10.1109/TED.2021.3053229](https://doi.org/10.1109/TED.2021.3053229).

- [5] J. Sheng, K.-L. Han, T. Hong, W.-H. Choi, and J.-S. Park, "Review of recent progresses on flexible oxide semiconductor thin film transistors based on atomic layer deposition processes," *J. Semicond.*, vol. 39, no. 1, Jan. 2018, Art. no. 011008, doi: [10.1088/1674-4926/39/1/011008](https://doi.org/10.1088/1674-4926/39/1/011008).

- [6] M. Lokanc, R. Eggert, and M. Redlinger, "The availability of indium: The present, medium term, and long term," National Renew. Energy Lab. (NREL), Colorado School Mines, Golden, CO, USA, Tech. Rep. NREL/SR-6A20-62409, Oct. 2015.

- [7] *Mineral Commodity Summaries 2019*, Nat. Minerals Inf. Center, U.S. Geol. Surv., Reston, VA, USA, 2019.

- [8] P. Schlupp, F.-L. Schein, H. von Wenckstern, and M. Grundmann, "All amorphous oxide bipolar heterojunction diodes from abundant metals," *Adv. Electron. Mater.*, vol. 1, nos. 1–2, Feb. 2015, Art. no. 1400023, doi: [10.1002/aelm.201400023](https://doi.org/10.1002/aelm.201400023).

- [9] C. Kim, N.-H. Lee, Y.-K. Kwon, and B. Kang, "Effects of film thickness and Sn concentration on electrical properties of solution-processed zinc tin oxide thin film transistors," *Thin Solid Films*, vol. 544, pp. 129–133, Oct. 2013, doi: [10.1016/j.tsf.2013.04.051](https://doi.org/10.1016/j.tsf.2013.04.051).

- [10] B. D. Ahn, D.-W. Choi, C. Choi, and J.-S. Park, "The effect of the annealing temperature on the transition from conductor to semiconductor behavior in zinc tin oxide deposited atomic layer deposition," *Appl. Phys. Lett.*, vol. 105, no. 9, Sep. 2014, Art. no. 092103, doi: [10.1063/1.4895102](https://doi.org/10.1063/1.4895102).

- [11] J. Heo, S. B. Kim, and R. G. Gordon, "Atomic layer deposited zinc tin oxide channel for amorphous oxide thin film transistors," *Appl. Phys. Lett.*, vol. 101, no. 11, Sep. 2012, Art. no. 113507, doi: [10.1063/1.4752727](https://doi.org/10.1063/1.4752727).

- [12] J. S. Kim et al., "Substrate-dependent growth behavior of atomic-layer-deposited zinc oxide and zinc tin oxide thin films for thin-film transistor applications," *J. Phys. Chem. C*, vol. 124, no. 49, pp. 26780–26792, Dec. 2020, doi: [10.1021/acs.jpcc.0c07800](https://doi.org/10.1021/acs.jpcc.0c07800).

- [13] H. Frenzel, A. Lajn, and M. Grundmann, "One decade of fully transparent oxide thin-film transistors: Fabrication, performance and stability," *Phys. Status Solidi (RRL) Rapid Res. Lett.*, vol. 7, no. 9, pp. 605–615, Sep. 2013, doi: [10.1002/pssr.201307259](https://doi.org/10.1002/pssr.201307259).

- [14] O. Lahr, S. Vogt, H. Wenckstern, and M. Grundmann, "Low-voltage operation of ring oscillators based on room-temperature-deposited amorphous zinc-tin-oxide channel MESFETs," *Adv. Electron. Mater.*, vol. 5, no. 12, Dec. 2019, Art. no. 1900548, doi: [10.1002/aelm.201900548](https://doi.org/10.1002/aelm.201900548).

- [15] N. P. Dasgupta, H.-B.-R. Lee, S. F. Bent, and P. S. Weiss, "Recent advances in atomic layer deposition," *Chem. Mater.*, vol. 28, no. 7, pp. 1943–1947, Apr. 2016, doi: [10.1021/acs.chemmater.6b00673](https://doi.org/10.1021/acs.chemmater.6b00673).

- [16] M. R. Shijeesh, A. C. Saritha, and M. K. Jayaraj, "Investigations on the reasons for degradation of zinc tin oxide thin film transistor on exposure to air," *Mater. Sci. Semicond. Process.*, vol. 74, pp. 116–121, Feb. 2018, doi: [10.1016/j.mssp.2017.10.015](https://doi.org/10.1016/j.mssp.2017.10.015).

- [17] Q. Zhang, G. Xia, L. Li, W. Xia, H. Gong, and S. Wang, "High-performance zinc-tin-oxide thin film transistors based on environment friendly solution process," *Current Appl. Phys.*, vol. 19, no. 2, pp. 174–181, Feb. 2019, doi: [10.1016/j.cap.2018.10.012](https://doi.org/10.1016/j.cap.2018.10.012).

- [18] I.-H. Cho, H.-W. Park, K.-B. Chung, C.-J. Kim, and B.-H. Jun, "Influence of lithium doping on the electrical properties and ageing effect of  $\text{ZnSnO}$  thin film transistors," *Semicond. Sci. Technol.*, vol. 33, no. 8, Aug. 2018, Art. no. 085004, doi: [10.1088/1361-6641/aacbe3](https://doi.org/10.1088/1361-6641/aacbe3).

- [19] C.-X. Huang, J. Li, Y.-Z. Fu, J.-H. Zhang, X.-Y. Jiang, and Z.-L. Zhang, "Suppression in the negative bias illumination instability of  $\text{ZnSnO}$  thin-film transistors using hafnium doping by dual-target magnetron cosputtering system," *IEEE Trans. Electron Devices*, vol. 63, no. 9, pp. 3552–3557, Sep. 2016, doi: [10.1109/TED.2016.2589240](https://doi.org/10.1109/TED.2016.2589240).

- [20] H. Zuo, X. Zhang, Y. Yang, H. Yang, and S. Zhang, "22.2: The influence of oxygen partial pressure on the performance of back-channel-etched a-ZTO thin-film transistors," in *SID Symp. Dig. Tech. Papers*, vol. 50, no. S1, Sep. 2019, pp. 216–219, doi: [10.1002/sdtp.13445](https://doi.org/10.1002/sdtp.13445).

- [21] L.-C. Liu, J.-S. Chen, and J.-S. Jeng, "Role of oxygen vacancies on the bias illumination stress stability of solution-processed zinc tin oxide thin film transistors," *Appl. Phys. Lett.*, vol. 105, no. 2, Jul. 2014, Art. no. 023509, doi: [10.1063/1.4890579](https://doi.org/10.1063/1.4890579).

- [22] P. Migliorato, M. D. H. Chowdhury, J. G. Um, M. Seok, and J. Jang, "Light/negative bias stress instabilities in indium gallium zinc oxide thin film transistors explained by creation of a double donor," *Appl. Phys. Lett.*, vol. 101, no. 12, Sep. 2012, Art. no. 123502, doi: [10.1063/1.4752238](https://doi.org/10.1063/1.4752238).

[23] J. F. Conley, Jr., "Instabilities in amorphous oxide semiconductor thin-film transistors," *IEEE Trans. Device Mater. Rel.*, vol. 10, no. 4, pp. 460–475, Dec. 2010, doi: [10.1109/TDMR.2010.2069561](https://doi.org/10.1109/TDMR.2010.2069561).

[24] C. R. Allemang et al., "High-performance zinc tin oxide TFTs with active layers deposited by atomic layer deposition," *Adv. Electron. Mater.*, vol. 6, no. 7, Jun. 2020, Art. no. 2000195, doi: [10.1002/aelm.202000195](https://doi.org/10.1002/aelm.202000195).

[25] Y. Son, A. Liao, and R. L. Peterson, "Effect of relative humidity and pre-annealing temperature on spin-coated zinc tin oxide films made via the metal–organic decomposition route," *J. Mater. Chem. C*, vol. 5, no. 32, pp. 8071–8081, 2017, doi: [10.1039/C7TC02343J](https://doi.org/10.1039/C7TC02343J).

[26] W. Hu and R. L. Peterson, "Molybdenum as a contact material in zinc tin oxide thin film transistors," *Appl. Phys. Lett.*, vol. 104, no. 19, May 2014, Art. no. 192105, doi: [10.1063/1.4875958](https://doi.org/10.1063/1.4875958).

[27] C. R. Allemang and R. L. Peterson, "Passivation of thin channel zinc tin oxide TFTs using  $\text{Al}_2\text{O}_3$  deposited by  $\text{O}_3$ -based atomic layer deposition," *IEEE Electron Device Lett.*, vol. 40, no. 7, pp. 1120–1123, Jul. 2019, doi: [10.1109/LED.2019.2914238](https://doi.org/10.1109/LED.2019.2914238).

[28] M. Fakhri, N. Babin, A. Behrendt, T. Jakob, P. Görn, and T. Riedl, "Facile encapsulation of oxide based thin film transistors by atomic layer deposition based on ozone," *Adv. Mater.*, vol. 25, no. 20, pp. 2821–2825, 2013, doi: [10.1002/adma.201300549](https://doi.org/10.1002/adma.201300549).

[29] T.-C. Fung et al., "Two-dimensional numerical simulation of radio frequency sputter amorphous In–Ga–Zn–O thin-film transistors," *J. Appl. Phys.*, vol. 106, no. 8, Oct. 2009, Art. no. 084511, doi: [10.1063/1.3234400](https://doi.org/10.1063/1.3234400).

[30] Y. Kim et al., "Amorphous InGaZnO thin-film transistors—Part I: Complete extraction of density of states over the full subband-gap energy range," *IEEE Trans. Electron Devices*, vol. 59, no. 10, pp. 2689–2698, Oct. 2012, doi: [10.1109/TED.2012.2208969](https://doi.org/10.1109/TED.2012.2208969).

[31] K. Mashooq, J. Jo, and R. L. Peterson, "Extraction of  $\text{SnO}$  subbandgap defect density by numerical modeling of p-type TFTs," *IEEE Trans. Electron Devices*, vol. 69, no. 5, pp. 2422–2436, May 2022, doi: [10.1109/TED.2022.3162803](https://doi.org/10.1109/TED.2022.3162803).

[32] S. Lee et al., "Trap-limited and percolation conduction mechanisms in amorphous oxide semiconductor thin film transistors," *Appl. Phys. Lett.*, vol. 98, no. 20, May 2011, Art. no. 203508, doi: [10.1063/1.3589371](https://doi.org/10.1063/1.3589371).

[33] Y. Wang, X. W. Sun, G. K. L. Goh, H. V. Demir, and H. Y. Yu, "Influence of channel layer thickness on the electrical performances of inkjet-printed In-Ga-Zn Oxide thin-film transistors," *IEEE Trans. Electron Devices*, vol. 58, no. 2, pp. 480–485, Feb. 2011, doi: [10.1109/TED.2010.2091131](https://doi.org/10.1109/TED.2010.2091131).

[34] K. Hoshino, B. Yeh, and J. F. Wager, "Impact of humidity on the electrical performance of amorphous oxide semiconductor thin-film transistors," *J. Soc. Inf. Display*, vol. 21, no. 7, pp. 310–316, 2013, doi: [10.1002/jisd.184](https://doi.org/10.1002/jisd.184).

[35] L.-C. Liu, J.-S. Chen, and J.-S. Jeng, "Ambient constancy of passivation-free ultra-thin zinc tin oxide thin film transistor," *ECS Solid State Lett.*, vol. 4, no. 12, pp. Q59–Q62, Jan. 2015, doi: [10.1149/2.0051512ssl](https://doi.org/10.1149/2.0051512ssl).

[36] J.-S. Park, J. K. Jeong, H.-J. Chung, Y.-G. Mo, and H. D. Kim, "Electronic transport properties of amorphous indium-gallium-zinc oxide semiconductor upon exposure to water," *Appl. Phys. Lett.*, vol. 92, no. 7, Feb. 2008, Art. no. 072104, doi: [10.1063/1.2838380](https://doi.org/10.1063/1.2838380).

[37] J. C. Park and H.-N. Lee, "Improvement of the performance and stability of oxide semiconductor thin-film transistors using double-stacked active layers," *IEEE Electron Device Lett.*, vol. 33, no. 6, pp. 818–820, Jun. 2012, doi: [10.1109/LED.2012.2190036](https://doi.org/10.1109/LED.2012.2190036).

[38] E. S. Sundholm et al., "Passivation of amorphous oxide semiconductors utilizing a zinc-tin-silicon-oxide barrier layer," *IEEE Electron Device Lett.*, vol. 33, no. 6, pp. 836–838, Jun. 2012, doi: [10.1109/LED.2012.2191530](https://doi.org/10.1109/LED.2012.2191530).

[39] K. Nomura, T. Kamiya, and H. Hosono, "Stability and high-frequency operation of amorphous In–Ga–Zn–O thin-film transistors with various passivation layers," *Thin Solid Films*, vol. 520, no. 10, pp. 3778–3782, Mar. 2012, doi: [10.1016/j.tsf.2011.10.068](https://doi.org/10.1016/j.tsf.2011.10.068).

[40] M. Fakhri, H. Johann, P. Görn, and T. Riedl, "Water as origin of hysteresis in zinc tin oxide thin-film transistors," *ACS Appl. Mater. Interfaces*, vol. 4, no. 9, pp. 4453–4456, Sep. 2012, doi: [10.1021/am301308y](https://doi.org/10.1021/am301308y).

[41] P. Görn, T. Riedl, and W. Kowalsky, "Encapsulation of zinc tin oxide based thin film transistors," *J. Phys. Chem. C*, vol. 113, no. 25, pp. 11126–11130, Jun. 2009, doi: [10.1021/jp9018487](https://doi.org/10.1021/jp9018487).

[42] H. Q. Chiang, B. R. McFarlane, D. Hong, R. E. Presley, and J. F. Wager, "Processing effects on the stability of amorphous indium gallium zinc oxide thin-film transistors," *J. Non-Cryst. Solids*, vol. 354, pp. 2826–2830, May 2008, doi: [10.1016/j.jnoncrysol.2007.10.105](https://doi.org/10.1016/j.jnoncrysol.2007.10.105).

[43] Y. Song, A. Katsman, A. L. Butcher, D. C. Paine, and A. Zaslavsky, "Temporal and voltage stress stability of high performance indium-zinc-oxide thin film transistors," *Solid-State Electron.*, vol. 136, pp. 43–50, Oct. 2017, doi: [10.1016/j.sse.2017.06.023](https://doi.org/10.1016/j.sse.2017.06.023).

[44] S. Sedky, A. Witvrouw, H. Bender, and K. Baert, "Experimental determination of the maximum post-process annealing temperature for standard CMOS wafers," *IEEE Trans. Electron Devices*, vol. 48, no. 2, pp. 377–385, Feb. 2001, doi: [10.1109/16.902741](https://doi.org/10.1109/16.902741).

[45] Y. S. Chun, S. Chang, and S. Y. Lee, "Effects of gate insulators on the performance of a-IGZO TFT fabricated at room-temperature," *Microelectron. Eng.*, vol. 88, no. 7, pp. 1590–1593, Jul. 2011, doi: [10.1016/j.mee.2011.01.076](https://doi.org/10.1016/j.mee.2011.01.076).

[46] H. Im, H. Song, J. Jeong, Y. Hong, and Y. Hong, "Effects of defect creation on bidirectional behavior with hump characteristics of InGaZnO TFTs under bias and thermal stress," *Jpn. J. Appl. Phys.*, vol. 54, no. 3S, Mar. 2015, Art. no. 03CB03, doi: [10.7567/JJAP.54.03CB03](https://doi.org/10.7567/JJAP.54.03CB03).

[47] B. Shin, J. R. Weber, R. D. Long, P. K. Hurley, C. G. Van de Walle, and P. C. McIntyre, "Origin and passivation of fixed charge in atomic layer deposited aluminum oxide gate insulators on chemically treated InGaAs substrates," *Appl. Phys. Lett.*, vol. 96, no. 15, Apr. 2010, Art. no. 152908, doi: [10.1063/1.3399776](https://doi.org/10.1063/1.3399776).

[48] M. Weidner et al., "Defect modulation doping," *Adv. Funct. Mater.*, vol. 29, no. 14, Apr. 2019, Art. no. 1807906, doi: [10.1002/adfm.201807906](https://doi.org/10.1002/adfm.201807906).

[49] Y.-H. Joo et al., "Work function tuning of zinc–tin oxide thin films using high-density  $\text{O}_2$  plasma treatment," *Coatings*, vol. 10, no. 11, p. 1026, Oct. 2020, doi: [10.3390/coatings10111026](https://doi.org/10.3390/coatings10111026).

[50] H. Yang et al., "Metal reaction-induced bulk-doping effect in forming conductive source-drain regions of self-aligned top-gate amorphous InGaZnO thin-film transistors," *ACS Appl. Mater. Interface*, vol. 13, no. 9, pp. 11442–11448, Mar. 2021, doi: [10.1021/acsami.0c21123](https://doi.org/10.1021/acsami.0c21123).

[51] J. Gwang Um, M. Mativenga, P. Migliorato, and J. Jang, "Increase of interface and bulk density of states in amorphous-indium-gallium-zinc-oxide thin-film transistors with negative-bias-under-illumination-stress time," *Appl. Phys. Lett.*, vol. 101, no. 11, Sep. 2012, Art. no. 113504, doi: [10.1063/1.4751849](https://doi.org/10.1063/1.4751849).

[52] S. Y. Lee, "Comprehensive review on amorphous oxide semiconductor thin film transistor," *Trans. Electr. Electron. Mater.*, vol. 21, no. 3, pp. 235–248, Jun. 2020, doi: [10.1007/s42341-020-00197-w](https://doi.org/10.1007/s42341-020-00197-w).

[53] M. G. Yun, S. H. Kim, C. H. Ahn, S. W. Cho, and H. K. Cho, "Effects of channel thickness on electrical properties and stability of zinc tin oxide thin-film transistors," *J. Phys. D, Appl. Phys.*, vol. 46, no. 47, Nov. 2013, Art. no. 475106, doi: [10.1088/0022-3727/46/47/475106](https://doi.org/10.1088/0022-3727/46/47/475106).

[54] Y.-C. Chen et al., "Bias-induced oxygen adsorption in zinc tin oxide thin film transistors under dynamic stress," *Appl. Phys. Lett.*, vol. 96, no. 26, Jun. 2010, Art. no. 262104, doi: [10.1063/1.3457996](https://doi.org/10.1063/1.3457996).

[55] A. Kiazadeh et al., "Improving positive and negative bias illumination stress stability in parylene passivated IGZO transistors," *Appl. Phys. Lett.*, vol. 109, no. 5, Aug. 2016, Art. no. 051606, doi: [10.1063/1.4960200](https://doi.org/10.1063/1.4960200).

[56] J. Shin and W. Cho, "Characteristics of amorphous In-Ga-Zn-O thin films with various compositions under microwave annealing," *Phys. Status Solidi A*, vol. 216, no. 16, Aug. 2019, Art. no. 1900217, doi: [10.1002/pssa.201900217](https://doi.org/10.1002/pssa.201900217).

[57] J. S. Park, W.-J. Maeng, H.-S. Kim, and J.-S. Park, "Review of recent developments in amorphous oxide semiconductor thin-film transistor devices," *Thin Solid Films*, vol. 520, no. 6, pp. 1679–1693, Jan. 2012, doi: [10.1016/j.tsf.2011.07.018](https://doi.org/10.1016/j.tsf.2011.07.018).

[58] K. Nomura et al., "Subgap states in transparent amorphous oxide semiconductor, In-Ga-Zn-O, observed by bulk sensitive X-ray photoelectron spectroscopy," *Appl. Phys. Lett.*, vol. 92, no. 20, May 2008, Art. no. 202117, doi: [10.1063/1.2927306](https://doi.org/10.1063/1.2927306).

[59] S. Sallis et al., "Origin of deep subgap states in amorphous indium gallium zinc oxide: Chemically disordered coordination of oxygen," *Appl. Phys. Lett.*, vol. 104, no. 23, Jun. 2014, Art. no. 232108, doi: [10.1063/1.4883277](https://doi.org/10.1063/1.4883277).

[60] C. C. Yen, A.-H. Tai, Y.-C. Liu, T.-L. Chen, C.-H. Chou, and C. W. Liu, "Oxygen-related reliability of amorphous InGaZnO thin film transistors," *IEEE J. Electron Devices Soc.*, vol. 8, pp. 540–544, May 2020, doi: [10.1109/JEDS.2020.2993018](https://doi.org/10.1109/JEDS.2020.2993018).

[61] M. H. Cho et al., "Comparative study on performance of IGZO transistors with sputtered and atomic layer deposited channel layer," *IEEE Trans. Electron Devices*, vol. 66, no. 4, pp. 1783–1788, Apr. 2019, doi: [10.1109/TED.2019.2899586](https://doi.org/10.1109/TED.2019.2899586).