# Device-level Transient Cooling of β-Ga<sub>2</sub>O<sub>3</sub> MOSFETs

Samuel H. Kim<sup>1</sup>, James Spencer Lundh<sup>2</sup>, Daniel Shoemaker<sup>2</sup>, Bikramjit Chatterjee<sup>1</sup>, Kelson D. Chabak<sup>3</sup>, Andrew J. Green<sup>3</sup>, Kyle Liddy<sup>3</sup>, Samuel Graham<sup>4</sup>, and Sukwon Choi<sup>2,\*</sup>

<sup>1</sup>Georgia Institute of Technology, Atlanta, GA 30332

<sup>2</sup>The Pennsylvania State University, University Park, PA 16802

<sup>3</sup>Air Force Research Laboratory, Dayton, OH 45433

<sup>4</sup>University of Maryland, College Park, MD 20742

\*Email: sukwon.choi@psu.edu

Abstract — β-phase gallium oxide (β-Ga<sub>2</sub>O<sub>3</sub>) has garnered considerable attention due to its large critical electric field strength and the availability of low cost/high quality melt-grown substrates, both of which are advantages over silicon carbide (SiC) and gallium nitride (GaN) in terms of the development radio frequency (RF) and power switching devices. However, because of the low thermal conductivity of β-Ga<sub>2</sub>O<sub>3</sub>, thermal management strategies at the device-level are required to accomplish the targeted high power operation. Recent package- and system-level thermal management studies have shown that design solutions based on steady-state operation could lead to ineffective cooling performance under transient thermal loading conditions, and result in an overdesigned cooling system. For these reasons, we performed a comparative study of the thermal dynamics of \beta-Ga<sub>2</sub>O<sub>3</sub> and GaN based transistor devices, which sheds light on the design of device-level transient cooling solutions for B-Ga<sub>2</sub>O<sub>3</sub> metal-oxide-semiconductor field-effect transistors (MOSFETs). Results show that replacing the host β-Ga<sub>2</sub>O<sub>3</sub> substrate with a high thermal conductivity material, similar to device-level thermal management solutions established for GaN devices, is effective in terms of heat extraction from the device active region under direct current (DC) operating conditions, but not under high frequency power dissipating conditions beyond the ~102 kHz range. In order to cool lateral β-Ga<sub>2</sub>O<sub>3</sub> MOSFETs under transient pulse-powered conditions, additional topside heat extraction via a high thermal conductivity passivation overlayer is necessary.

Keywords—Gallium oxide ( $\beta$ -Ga<sub>2</sub>O<sub>3</sub>), MOSFET, Raman spectroscopy, self-heating, transient thermal management, thermal modeling

# I. INTRODUCTION

β-phase gallium oxide (β-Ga<sub>2</sub>O<sub>3</sub>) is an ultra-wide bandgap (UWBG) semiconductor that offers outstanding electronic properties and potentially low manufacturing cost, that are both necessary to develop next-generation high power electronic devices. The large bandgap energy (~4.8 eV) translates into a high breakdown electric field (~8 MV/cm), leading to a high Baliga's figure of merit (BFOM) and Johnson's figure of merit (JFOM), that render the material ideal for high-voltage/power switching devices as shown in Table 1 [1]–[4]. For example, recent reports have demonstrated the development of depletion mode lateral metal-oxide-semiconductor field-effect transistors (MOSFETs), with a high critical field strength (3.8 MV/cm) [5], high current density (600 mA/mm) [6], and high breakdown

voltage (2.32 kV) [7]. However,  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> possesses a poor thermal conductivity as compared to other wide band gap semiconductors (e.g., GaN and SiC), as shown in Table 1. Therefore,  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> devices suffer from device self-heating under nominal operating conditions [8]–[12]. Also, the low anisotropic thermal conductivity of  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> (9 – 26 W/m-K at room temperature) [13] leads to excessively high operational channel temperatures that compromise the device performance and reliability. Therefore, the design of thermal management solutions with highest cooling performance is critical for the commercialization of  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> device technologies.

Table 1. Electronic and thermal properties of semiconductors used to construct radio frequency (RF) and power switching devices [14]–[16].

| Material<br>Property                    | Si     | 4H-SiC | GaN    | β-Ga <sub>2</sub> O <sub>3</sub> |

|-----------------------------------------|--------|--------|--------|----------------------------------|

| Bandgap (eV)                            | 1.1    | 3.25   | 3.4    | 4.6-4.9                          |

| Breakdown field (MV/cm)                 | 0.3    | 3      | 3.3    | 8                                |

| Normalized<br>BFOM                      | 1      | 320    | 860    | 1100 -<br>3250                   |

| Normalized<br>JFOM                      | 1      | 8.2    | 22.9   | 37.5                             |

| Density (g/m³)                          | 2.33   | 3.21   | 6.15   | 6.44                             |

| Specific heat (J/kg-K)                  | 710    | 670    | 490    | 490                              |

| Thermal diffusivity (m <sup>2</sup> /s) | 9.1e-5 | 2.3e-4 | 4.3e-5 | 4.1e-6                           |

| Thermal conductivity at 300 K (W/m-K)   | 135    | 490    | 130    | 26 [010]<br>13 [001]<br>9 [100]  |

Package- and system-level thermal management solutions, that are designed based on steady-state operation, were shown to be often ineffective for applications that operate under transient thermal loading, and could result in overdesigned cooling systems [17]. Since the practical operation of RF and

power electronic devices involve pulsed power dissipation, it is necessary to consider the device transient thermal dynamics when designing device-level cooling solutions. In this study, we investigated the effectiveness of different device-level cooling schemes applied to a β-Ga<sub>2</sub>O<sub>3</sub> MOSFET under transient operating conditions. The device thermal time constant ( $\tau$ ) [18]– [20] (the rise time for a device to reach ~63% of its steady-state temperature in response to a power step input) [21] is inversely proportional to the thermal diffusivity ( $\alpha$ ), i.e.,  $\tau \propto 1/\alpha =$  $\rho c_p/\kappa$ , where  $\rho$  is the density,  $c_p$  is the specific heat at constant pressure, and  $\kappa$  is the thermal conductivity. Since the thermal conductivity of β-Ga<sub>2</sub>O<sub>3</sub> is an order of magnitude lower than those for GaN and SiC, the thermal diffusivity is an order of magnitude lower as well (Table 1). This renders β-Ga<sub>2</sub>O<sub>3</sub> transistors to possess a significantly longer thermal time constant than those for GaN and SiC devices. Because of this relatively long thermal time constant, the heat diffusion length in β-Ga<sub>2</sub>O<sub>3</sub> is limited under short transient thermal loading; therefore, device-level thermal management established for GaN devices [22] may not be applicable to β-Ga<sub>2</sub>O<sub>3</sub> devices, especially under high frequency operating conditions that involve switching power losses. This study builds upon our recent reports on the growth of polycrystalline diamond on β-Ga<sub>2</sub>O<sub>3</sub> [23] and the fabrication of β-Ga<sub>2</sub>O<sub>3</sub> composite substrates [24]. As a follow-up study, this work highlights key considerations for the design of transient cooling solutions for high power β-Ga<sub>2</sub>O<sub>3</sub> electronic devices using transient thermal modeling.

#### II. DEVICE DESCRIPTION

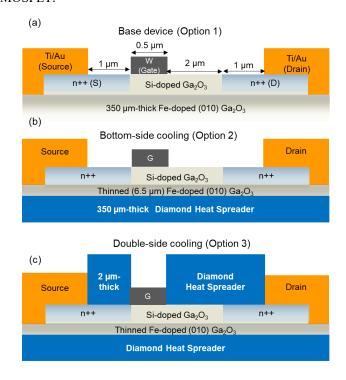

The steady-state and transient self-heating behavior of the β-Ga<sub>2</sub>O<sub>3</sub> MOSFET was compared to experimental results for a GaN-on-Si high electron mobility transistor (HEMT) acquired from our previous work [25], [26]. Fig. 1 (a) shows the crosssectional schematic of a single channel β-Ga<sub>2</sub>O<sub>3</sub> MOSFET tested in this work. A Si-doped β-Ga<sub>2</sub>O<sub>3</sub> channel layer was grown on a Fe-doped (010)-oriented β-Ga<sub>2</sub>O<sub>3</sub> commercial substrate using metal organic vapor phase epitaxy (MOVPE). The channel length is  $2.5 \mu m$ , where the gate length is  $0.5 \mu m$ and the gate-drain length is 2 μm. The gate width is 100 μm. More fabrication details, including the gate metal stack and ionimplant conditions/activation can be found in [25]. A GaN HEMT was grown on a Si substrate, which consisted of a 10 nm in situ SiN<sub>x</sub> passivation layer, a 4 nm GaN cap layer, a 24 nm AlGaN barrier layer, a 514 nm GaN layer, and a 4.4 µm GaN buffer layer. The GaN HEMT has a gate length of 2 µm, a gate width of 100 μm, a gate-to-source spacing of 2 μm, and a gateto-drain spacing of 15 µm. More details of this device can be found in [27].

Based on the experimental data acquired from our previous thermal characterization studies on the homoepitaxial  $\beta\text{-}Ga_2O_3$  MOSFET (Fig. 1 (a): option 1) [16], [25], [28], a transient device thermal model was created. This model was then extended to study a hypothetical  $\beta\text{-}Ga_2O_3$  device fabricated on a  $\beta\text{-}Ga_2O_3$ /diamond composite substrate (Fig. 1 (b): option 2) and another device structure that also employs a polycrystalline diamond passivation layer grown on top of the  $\beta\text{-}Ga_2O_3$  channel (Fig. 1 (c): option 3). The  $\beta\text{-}Ga_2O_3$ /diamond composite wafer is assumed to be constructed by bonding a 6.5  $\mu\text{m}$ -thick  $\beta\text{-}Ga_2O_3$  layer thinned from the host substrate (similar to our previous

work [14]) onto a polycrystalline diamond substrate with a thickness of 350  $\mu$ m. For these simulated device structures, the device geometries (gate-to-source distance, gate length, gate-to-drain distance) were kept identical to the homoepitaxial MOSFET.

Fig. 1 (a) Option 1: Schematic of a homoepitaxial  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> MOSFET. (b) Option 2: A simulated device structure with the host substrate replaced by a  $\beta$ -Ga<sub>2</sub>O<sub>3</sub>/diamond composite wafer. (c) Option 3: A simulated device that further augments the device architecture in (b) by depositing a polycrystalline diamond heat spreader over the  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> channel layer.

### III. EXPERIMENTAL AND MODELING DETAILS

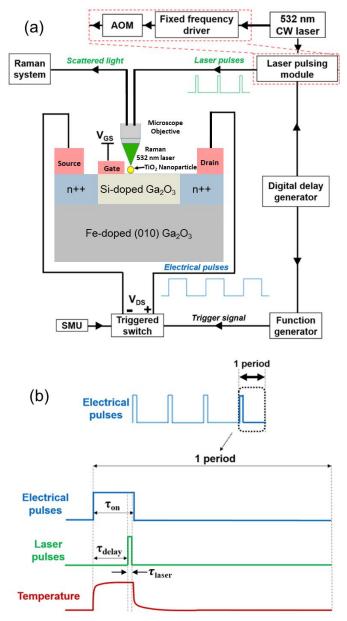

To experimentally quantify the transient temperature rise of the channel of the homoepitaxial β-Ga<sub>2</sub>O<sub>3</sub> MOSFET (option 1), micro-Raman spectroscopy measurements were performed using a Horiba LabRAM HR Evolution spectrometer with a 532 nm excitation source [26]. Measurements were performed in a 180° backscattering configuration with a long working distance  $50 \times$  objective (NA = 0.45). Nanoparticle-assisted Raman thermometry was used to probe the surface temperature of the β-Ga<sub>2</sub>O<sub>3</sub> MOSFET using anatase titanium dioxide (TiO<sub>2</sub>) nanoparticles (99.98% purity) deposited on the device surface [29]. The spatial resolution is dictated by the size of submicrometer nanoparticles serving as surface temperature transducers. The experimental setup used for transient Raman thermometry experiments is illustrated in Fig. 2 (a). This setup adopts a lock-in modulation scheme, in which the electrical and laser pulse trains are synchronized while the Raman signal accumulates over many periods. Using this experimental setup, a temporal resolution of 15 ns was achieved and used in this study. Fig. 2 (b) shows the synchronized pulsing scheme that allows to control the electrical pulse width  $(\tau_{on})$  of the applied drain-source voltage ( $V_{DS}$ ) and the laser pulse width ( $\tau_{laser}$ ) that produces a Raman signal, which is collected by the detector of

the Raman system. The time delay ( $\tau_{\rm delay}$ ) between the electrical and laser pulses is controlled by a digital delay generator to measure the full transient temperature rise of the device in response to a square electrical pulse with a 10% duty cycle. Thermoreflectance thermal imaging was performed on the gate electrode of a GaN-on-Si HEMT using a Microsanj NT-210B system equipped with a  $1626 \times 1236$  charge coupled device (CCD) camera. Experiments were carried out with a  $20 \times$  objective (NA =0.35) with 530 nm LED [26]. Temperature rise was measured at 1.6 W/mm under 10 kHz pulsed (10% duty cycle) conditions [26].

Fig. 2 (a) Experimental setup used for transient Raman Thermometry. (b) The synchronized pulsing scheme used to capture the transient thermal response of the  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> MOSFET.

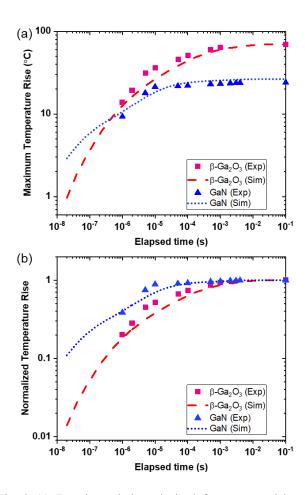

In order to validate the trends observed in the experiments and to further understand the device transient thermal dynamics, a 3D transient device thermal model was constructed (using COMSOL Multiphysics). The β-Ga<sub>2</sub>O<sub>3</sub> MOSFET and GaN HEMT were operated under a fully open channel condition [16], [28], [30], [31] by keeping the gate voltage at 4 V. Under such bias condition, the Joule-heating profile across the device channel could be approximated as a uniform heat flux that is applied between source and drain [32]. In the device model, the temperature dependence (~1/T<sup>1.3</sup> dependence) as well as the anisotropy of the thermal conductivity of β-Ga<sub>2</sub>O<sub>3</sub> were accounted for as shown in Table 1 [33]. Also, a temperature dependent specific heat was used in the model [34]. A temperature boundary condition (T<sub>bottom</sub> = 25°C) was applied to the bottom of the device substrate, and a convective boundary condition (h = 5 W/m<sup>2</sup>-K,  $T_{inf}$  = 25°C) was applied elsewhere. The thermal conductivity of the polycrystalline diamond substrate (part of the composite wafer in Fig. 1 (b)) was 1940 W/m-k at room temperature [35]. For the diamond passivation layer (in Fig. 1 (c)), a directionally averaged thickness dependent thermal conductivity of high quality/large grain polycrystalline diamond (0-0.25 μm: 110 W/m-K, 0.25-1 μm: 240 W/m-K, 0.25-1 µm: 660 W/m-K) and a recently published thermal boundary conductance value at the β-Ga<sub>2</sub>O<sub>3</sub>/diamond interface (179 MW/m<sup>2</sup>-K) were used in the device thermal model [23], [24], [36]. The transient thermal model for the GaN HEMT was constructed in a similar manner. A GaN/Si interfacial thermal boundary conductance of 10 MW/m<sup>2</sup>-K was used in the GaN HEMT thermal model [27]. In Fig. 3, simulated channel surface temperatures are compared with the experimental data obtained from nanoparticle-assisted Raman thermometry showing excellent agreement.

### IV. RESULTS AND DISCUSSION

Fig. 3 (a) shows the transient temperature rise of both the homoepitaxial β-Ga<sub>2</sub>O<sub>3</sub> MOSFET and the GaN-on-Si HEMT under 1 W/mm and 1.6 W/mm power dissipation levels, respectively. Under steady-state, the β-Ga<sub>2</sub>O<sub>3</sub> MOSFET exhibits a  $2.7 \times \text{higher temperature rise}$  than the GaN HEMT despite the β-Ga<sub>2</sub>O<sub>3</sub> MOSFET is operating under a ~38% lower power The corresponding device-to-package thermal resistances of the β-Ga<sub>2</sub>O<sub>3</sub> MOSFET and the GaN HEMT are 65 °C-mm/W and 15 °C-mm/W, respectively. To interrogate and compare the device transient dynamics, Fig. 3 (a) is replotted as Fig. 3 (b), where the channel temperature rise of both devices are normalized with respect to their steady-state temperature rise. Obviously, as shown in Fig. 3 (b), the GaN device exhibits a shorter thermal time constant than the homoepitaxial β-Ga<sub>2</sub>O<sub>3</sub> MOSFET, which means its channel temperature reaches the steady-state value much faster than the β-Ga<sub>2</sub>O<sub>3</sub> device.

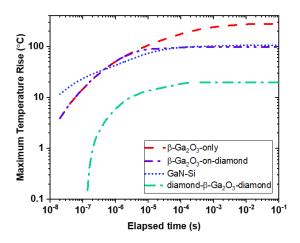

To estimate the channel temperature rise in the four device architectures under a realistic power dissipation level, device simulation was performed at a power dissipation level of 4 W/mm, and results are plotted in Fig. 4. Today's GaN devices typically operate under 5–6 W/mm to ensure that the operating temperature does not exceed the safe allowable range for reliable operation [22]. Without any cooling solution applied, the steady-state channel temperature rise of the homoepitaxial  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> MOSFET (option 1) is 278°C (i.e., the channel temperature is 303°C while the base temperature is 25°C), which exceeds typical operational safety limits (e.g., 175°C for GaN and 125°C

for Si devices) [20], [37]. Because of the low thermal conductivity of β-Ga<sub>2</sub>O<sub>3</sub>, replacing the β-Ga<sub>2</sub>O<sub>3</sub> substrate with diamond (option 2) reduces the steady-state channel temperature rise by 65% (dropping from 278°C to 97.5°C). However, the red and purple lines (simulation results for the homoepitaxial β-Ga<sub>2</sub>O<sub>3</sub> MOSFET and the MOSFET fabricated on a β-Ga<sub>2</sub>O<sub>3</sub>/diamond composite wafer) in Fig. 4 show that, for high frequency power switching applications operating beyond the  $\sim 10^2$  kHz range (elapsed time  $< \sim 10^{-5}$  s), employing a composite substrate (i.e., bottom-side cooling) does not improve the transient thermal response (i.e., self-heating) of the device. The channel temperature rise for both device structures are identical up to ~2×10<sup>-6</sup> s, which corresponds to transient thermal loading under ~500 kHz. Therefore, solely relying on a bottom-side cooling strategy (i.e., employing a composite substrate similar to the case of GaN-on-diamond devices [22]) is insufficient for the thermal management of pulse-powered β-Ga<sub>2</sub>O<sub>3</sub> MOSFETs.

Fig. 3 (a) Experimental data obtained from nanoparticle-assisted Raman thermometry and thermoreflectance imaging along with simulated results for the  $\beta\text{-}Ga_2O_3$  MOSFET and GaN-on-Si HEMT that were operated under 1 W/mm and 1.6 W/mm power dissipation levels, respectively. (b) Normalized temperature rise of the  $\beta\text{-}Ga_2O_3$  MOSFET and GaN-on-Si HEMT with respect to their steady-state temperature rise. The steady-state temperature rise of the  $\beta\text{-}Ga_2O_3$  MOSFET is 65°C for a power dissipation level of 1 W/mm. The steady state temperature rise of the GaN-on-Si HEMT is 24°C for a power dissipation level of 1.6 W/mm.

Fig. 4 shows the transient thermal response of a β-Ga<sub>2</sub>O<sub>3</sub> MOSFET augmented by not only the β-Ga<sub>2</sub>O<sub>3</sub>/diamond composite wafer, but also a 2 µm-thick polycrystalline diamond passivation layer over the device channel (i.e., option 3), as shown in Fig. 1. The steady-state temperature rise of this doubleside cooled device is 19.7°C under 4 W/mm, which is even lower than that for the GaN-on-Si HEMT, 105.5°C. Also, the addition of a top-side heat spreader (i.e., diamond passivation) effectively reduces the temperature rise during short transient conditions (e.g., elapsed time  $< \sim 10^{-5}$  s). The diamond passivation layer with a moderately high thermal conductivity effectively reduces the device temperature not only under steady-state conditions, but also under the high frequency operating regime, since it is located in proximity (i.e., less than several tens of nanometers) to the β-Ga<sub>2</sub>O<sub>3</sub> device active region, where Joule heating occurs. Therefore, device-level thermal management of β-Ga<sub>2</sub>O<sub>3</sub> MOSFETs requires the combined use of a composite wafer and a top-side heat spreader, in order to cope with thermal loading that occurs during both direct current (DC; steady-state) and pulsed (transient) operating conditions.

Fig. 4 The transient channel temperature rise under a power density of 4 W/mm for a homoepitaxial  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> MOSFET (option 1:  $\beta$ -Ga<sub>2</sub>O<sub>3</sub>-only), a  $\beta$ -Ga<sub>2</sub>O<sub>3</sub>-on-diamond), a  $\beta$ -Ga<sub>2</sub>O<sub>3</sub>-on-diamond MOSFET further augmented by diamond passivation (option 3: diamond- $\beta$ -Ga<sub>2</sub>O<sub>3</sub>-diamond), and a GaN-on-Si HEMT.

# V. CONCLUSION

In this study, we compared the transient self-heating behavior of a homoepitaxial  $\beta\text{-}Ga_2O_3$  MOSFET and a GaN-on-Si HEMT using nanoparticle-assisted Raman thermometry and thermoreflectance thermal imaging. The effectiveness of bottom-side and double-side cooling schemes using a polycrystalline diamond substrate and a diamond passivation layer were studied via transient thermal modeling. Because of the low thermal diffusivity of  $\beta\text{-}Ga_2O_3$ , the use of a  $\beta\text{-}Ga_2O_3$  composite substrate (bottom-side cooling) must be augmented by a diamond passivation layer (top-side cooling) to effectively cool the device active region under both steady-state and transient operating conditions. Without no proper cooling applied, the steady-state device-to-package thermal resistance

of a homoepitaxial  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> MOSFET is 2.6 times higher than that for a GaN-on-Si HEMT. Replacing the substrate with polycrystalline diamond (under a 6.5 µm-thick  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> layer) could reduce the steady-state temperature rise by 65% compared to that for a homoepitaxial  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> MOSFET. However, for high frequency power switching applications beyond the ~10² kHz range, bottom-side cooling (integration with a high thermal conductivity substrate) does not improve the transient thermal response of the device. Adding a diamond passivation over layer diamond not only suppresses the steady-state temperature rise, but also drastically reduces the transient temperature rise under high frequency operating conditions.

#### ACKNOWLEDGMENT

This work was supported by the National Science Foundation under Grant No. CBET-1934482 (Program Director: Ying Sun).

#### REFERENCES

- [1] J. Y. Tsao *et al.*, "Ultrawide-Bandgap Semiconductors: Research Opportunities and Challenges," *Adv. Electron. Mater.*, vol. 4, no. 1, pp. 1–49, 2018, doi: 10.1002/aelm.201600501.

- [2] M. Higashiwaki, K. Sasaki, A. Kuramata, T. Masui, and S. Yamakoshi, "Development of gallium oxide power devices," *Phys. Status Solidi Appl. Mater. Sci.*, vol. 211, no. 1, pp. 21–26, 2014, doi: 10.1002/pssa.201330197.

- [3] S. J. Pearton, F. Ren, M. Tadjer, and J. Kim, "Perspective: Ga<sub>2</sub>O<sub>3</sub> for ultra-high power rectifiers and MOSFETS," *J. Appl. Phys.*, vol. 124, no. 22, 2018, doi: 10.1063/1.5062841.

- [4] M. Higashiwaki, H. Murakami, and Y. Kumagai, "State-of-the-art technologies of gallium oxide power devices Current status of Ga<sub>2</sub>O<sub>3</sub> power devices," *J. Phys. D Appl. Phys. Masataka Higashiwaki al J. Phys. D Appl. Phys.*, vol. 50, 2017.

- [5] A. J. Green *et al.*, "3.8-MV/cm Breakdown Strength of MOVPE-Grown Sn-Doped β-Ga<sub>2</sub>O<sub>3</sub> MOSFETs," *IEEE Electron Device Lett.*, vol. 37, no. 7, pp. 902–905, 2016, doi: 10.1109/LED.2016.2568139.

- [6] H. Zhou, M. Si, S. Alghamdi, G. Qiu, L. Yang, and P. D. Ye, "High-Performance Depletion/Enhancement-mode β-Ga<sub>2</sub>O<sub>3</sub> on Insulator (GOOI) Field-Effect Transistors with Record Drain Currents of 600/450 mA/mm," *IEEE Electron Device Lett.*, vol. 38, no. 1, pp. 103–106, 2017, doi: 10.1109/LED.2016.2635579.

- [7] J. K. Mun, K. Cho, W. Chang, H.-W. Jung, and J. Do, "Editors' Choice—2.32 kV Breakdown Voltage Lateral β-Ga<sub>2</sub>O<sub>3</sub> MOSFETs with Source-Connected Field Plate," *ECS J. Solid State Sci. Technol.*, vol. 8, no. 7, pp. Q3079–Q3082, 2019, doi: 10.1149/2.0151907jss.

- [8] J. S. Lundh *et al.*, "Device-Level Multidimensional Thermal Dynamics With Implications for Current and Future Wide Bandgap Electronics," *J. Electron.*

- Packag., vol. 142, no. 3, May 2020, doi: 10.1115/1.4047100.

- [9] B. Chatterjee *et al.*, "Electro-thermal co-design of β-(Al<sub>x</sub>Ga<sub>1-x</sub>)<sub>2</sub>O<sub>3</sub>/Ga<sub>2</sub>O<sub>3</sub> modulation doped field effect transistors," *Appl. Phys. Lett.*, vol. 117, no. 15, 2020, doi: 10.1063/5.0021275.

- [10] B. Chatterjee, A. Jayawardena, E. Heller, D. W. Snyder, S. Dhar, and S. Choi, "Thermal characterization of gallium oxide Schottky barrier diodes," *Rev. Sci. Instrum.*, vol. 89, no. 11, 2018, doi: 10.1063/1.5053621.

- [11] A. Bhattacharyya *et al.*, "130 mA mm<sup>-1</sup> β-Ga<sub>2</sub>O<sub>3</sub> metal semiconductor field effect transistor with low-temperature metalorganic vapor phase epitaxy-regrown ohmic contacts," *Appl. Phys. Express*, vol. 14, no. 7, pp. 1–5, 2021, doi: 10.35848/1882-0786/ac07ef.

- [12] B. Chatterjee, W. Li, K. Nomoto, H. G. Xing, and S. Choi, "Thermal design of multi-fin Ga<sub>2</sub>O<sub>3</sub> vertical transistors," *Appl. Phys. Lett.*, vol. 119, no. 10, 2021, doi: 10.1063/5.0056557.

- [13] M. Higashiwaki *et al.*, "Anisotropic thermal conductivity in single crystal β-gallium oxide," *Appl. Phys. Lett.*, vol. 106, no. 11, p. 111909, 2015, doi: 10.1063/1.4916078.

- [14] Y. Song *et al.*, "Ga<sub>2</sub>O<sub>3</sub>-on-SiC Composite Wafer for Thermal Management of Ultrawide Bandgap Electronics," *ACS Appl. Mater. Interfaces*, vol. 13, no. 34, pp. 40817–40829, 2021, doi: 10.1021/acsami.1c09736.

- [15] S. Kim *et al.*, "Thermal Management of β-Ga<sub>2</sub>O<sub>3</sub> Current Aperture Vertical Electron Transistors," *IEEE Trans. Components, Packag. Manuf. Technol.*, vol. 11, no. 8, pp. 1171–1176, 2021, doi: 10.1109/TCPMT.2021.3089321.

- [16] S. H. Kim *et al.*, "The effectiveness of heat extraction by the drain metal contact of  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> MOSFETs," pp. 324–327, 2021, doi: 10.1109/itherm51669.2021.9503276.

- [17] N. R. Jankowski and F. P. McCluskey, "Modeling transient thermal response of pulsed power electronic packages," *PPC2009 17th IEEE Int. Pulsed Power Conf.*, pp. 820–825, 2009, doi: 10.1109/PPC.2009.5386368.

- [18] K. R. Bagnall and E. N. Wang, "Theory of Thermal Time Constants in GaN High-Electron-Mobility Transistors," doi: 10.1109/TCPMT.2017.2773065.

- [19] K. R. Bagnall, O. I. Saadat, S. Joglekar, T. Palacios, and E. N. Wang, "Experimental Characterization of the Thermal Time Constants of GaN HEMTs Via Micro-Raman Thermometry," *IEEE Trans. Electron Devices*, vol. 64, no. 5, pp. 2121–2128, 2017, doi: 10.1109/TED.2017.2679978.

- [20] B. Chatterjee *et al.*, "Device-Level Thermal Management of Gallium Oxide Field-Effect Transistors," vol. 9, no. 12, pp. 2352–2365, 2019.

- [21] J. Dallas *et al.*, "Thermal characterization of gallium nitride p-i-n diodes," *Appl. Phys. Lett.*, vol. 112, no. 7,

- 2018, doi: 10.1063/1.5006796.

- [22] A. Bar-Cohen, J. J. Maurer, and D. H. Altman, "Embedded cooling for wide bandgap power amplifiers: A review," *J. Electron. Packag. Trans. ASME*, vol. 141, no. 4, pp. 1–14, 2019, doi: 10.1115/1.4043404.

- [23] M. Malakoutian *et al.*, "Polycrystalline diamond growth on β-Ga<sub>2</sub>O<sub>3</sub> for thermal management," *Appl. Phys. Express*, vol. 14, no. 5, 2021, doi: 10.35848/1882-0786/abf4f1.

- [24] Z. Cheng *et al.*, "Integration of polycrystalline Ga<sub>2</sub>O<sub>3</sub> on diamond for thermal management," *Appl. Phys. Lett.*, vol. 116, no. 6, 2020, doi: 10.1063/1.5125637.

- [25] K. J. Liddy *et al.*, "Thin channel β-Ga<sub>2</sub>O<sub>3</sub> MOSFETs with self-aligned refractory metal gates," *Appl. Phys. Express*, vol. 12, no. 12, pp. 0–4, 2019, doi: 10.7567/1882-0786/ab4d1c.

- [26] H. P. de Bock *et al.*, "A System to Package Perspective on Transient Thermal Management of Electronics," *J. Electron. Packag.*, vol. 142, no. 4, pp. 1–11, 2020, doi: 10.1115/1.4047474.

- [27] B. Chatterjee *et al.*, "Cumulative Impacts of Proton Irradiation on the Self-heating of AlGaN/GaN HEMTs," *ACS Appl. Electron. Mater.*, vol. 2, no. 4, pp. 980–991, 2020, doi: 10.1021/acsaelm.0c00048.

- [28] S. H. Kim *et al.*, "Thermally-Aware Layout Design of β-Ga<sub>2</sub>O<sub>3</sub> Lateral MOSFETs," *IEEE Trans. Electron Devices*, vol. 69, no. 3, pp. 1251–1257, 2022, doi: 10.1109/TED.2022.3143779.

- [29] J. Dallas *et al.*, "Thermal characterization of gallium nitride p-i-n diodes," *Appl. Phys. Lett.*, vol. 112, no. 7, pp. 1–5, 2018, doi: 10.1063/1.5006796.

- [30] J. S. Lundh *et al.*, "Multidimensional thermal analysis of an ultrawide bandgap AlGaN channel high electron mobility transistor," *Appl. Phys. Lett.*, vol. 115, no. 15, 2019, doi: 10.1063/1.5115013.

- [31] S. Choi, E. Heller, D. Dorsey, R. Vetury, and S. Graham, "The impact of mechanical stress on the degradation of AlGaN/GaN high electron mobility transistors," *J. Appl. Phys.*, vol. 114, no. 16, p. 164501, 2013, doi: 10.1063/1.4826524.

- [32] R. Pearson, B. Chatterjee, S. Kim, S. Graham, A. Rattner, and S. Choi, "Guidelines for reduced-order thermal modeling of multifinger GaN HEMTs," *J. Electron. Packag. Trans. ASME*, vol. 142, no. 2, pp. 1–12, 2020, doi: 10.1115/1.4046620.

- [33] P. Jiang, X. Qian, X. Li, and R. Yang, "Three-dimensional anisotropic thermal conductivity tensor of single crystalline β-Ga<sub>2</sub>O<sub>3</sub>," *Appl. Phys. Lett.*, vol. 113, no. 23, pp. 8–13, 2018, doi: 10.1063/1.5054573.

- Z. Guo *et al.*, "Anisotropic thermal conductivity in single crystal β-gallium oxide," *Appl. Phys. Lett.*, vol. 106, no. 11, pp. 1–6, 2015, doi: 10.1063/1.4916078.

- [35] L. Yates *et al.*, "Characterization of the Thermal Conductivity of CVD Diamond for GaN-on-Diamond Devices," *Tech. Dig. IEEE Compd. Semicond. Integr. Circuit Symp. CSIC*, vol. 2016-Novem, pp. 31–34,

- 2016, doi: 10.1109/CSICS.2016.7751032.

- [36] J. Anaya *et al.*, "Simultaneous determination of the lattice thermal conductivity and grain/grain thermal resistance in polycrystalline diamond," *Acta Mater.*, vol. 139, pp. 215–225, 2017, doi: 10.1016/j.actamat.2017.08.007.

- [37] M. J. Tadjer, "Cheap Ultra-Wide Bandgap Power Electronics? Gallium Oxide May Hold the Answer," *Electrochem. Soc. Interface*, vol. 27, no. 4, pp. 49–52, 2018, doi: 10.1149/2.f05184if.