# Optimal Tracking and Resonance Damping Design of Cascaded Modular Model Predictive Control for Common-Mode Stabilized Grid-Tied *LCL* Inverter

Liwei Zhou, *Student Member, IEEE*, Matthias Preindl, *Senior Member, IEEE*

**Abstract**—A cascaded modular model predictive control (MMPC) method is designed for a modified non-isolated *LCL* grid-connected inverters to provide resonance damping, improved dynamic performance and leakage current attenuation capabilities. The continuous control set model predictive control (CCS-MPC) strategy is applied for the proposed method. The active damping function of the inner-loop MMPC is analyzed in detail to illustrate the mechanism of improving the system dynamic performance. The cascaded MMPC method is compared with conventional PI control methods with/without notch filter to show the merits in resonance damping and dynamic response. The optimal control parameters design procedure is elucidated with the tuning mechanism of MMPC weighing factor and PI gain. With the proposed optimal MMPC control design method, the dynamic performance of rising-time and overshoot are improved compared to the conventional PI control methods with/without notch filter. The simulation and experimental results verified the proposed control design method.

**Index Terms**—Modular model predictive control, Non-isolated grid-connected inverter, *LCL* filter, zero-sequence voltage control, active damping, dynamic performance.

## I. INTRODUCTION

**M**ODEL predictive control (MPC) is an advanced control technique that is gaining more attention with the increasing demand of better system dynamic performance in power electronics. Different from the conventional proportional-integral (PI) control, the MPC has a better transient performance in the aspects of rising-time, steady-state error, overshoot and disturbance rejection. Especially in high-order filtered power converter system, such as *LCL* filtered converter, there exists an intrinsic resonance frequency that can cause oscillation or instability issues with a conventional PI controller [1]. The resonance cannot be naturally attenuated by PI control.

Passive/active damping resistors can be added in the physical/control loops to compensate for the resonance [2]. However, on one hand, a passive resistor in the main physical loop will introduce extra power losses [3]. On the other hand, the active damping method requires extra voltage/current sensors that brings more system cost [4], [5]. Besides the hardware solutions of passive/active damping methods with extra physical resistors/sensors, another option to attenuate the resonance is notch filter from the software perspective [6]. The notch filter can be added at the resonant frequency of the *LCL* filter to compensate for the resonant spikes. However, the inserted notch filter will also reduce the control bandwidth and slow down the reference tracking. Notch filter is a desired

solution to reduce the high frequency EMI noise [7]. But at the same time, the system dynamic performance might be deteriorated.

MPC is capable of increasing the control bandwidth to achieve a high reference tracking speed [8], [9]. Based on this characteristic of MPC, the resonant frequency of an *LCL* filtered converter can be shifted to a higher range by down-sizing the filter values and increasing the switching frequency [10], [11]. With the advantageous dynamic performance of MPC, the volume and weight of *LCL* filter can be reduced. Thus, the system cost will be saved. Another intrinsic function of MPC is active damping for *LCL* resonance which has not been studied in detail [12]. The MPC can be functioned as an active damping control block that compensates the system resonance especially in a cascaded PI+MPC control architecture. Thus, the stability of the system can be improved which makes it possible to enlarge the proportional gain and increase the control bandwidth without exciting oscillation [13].

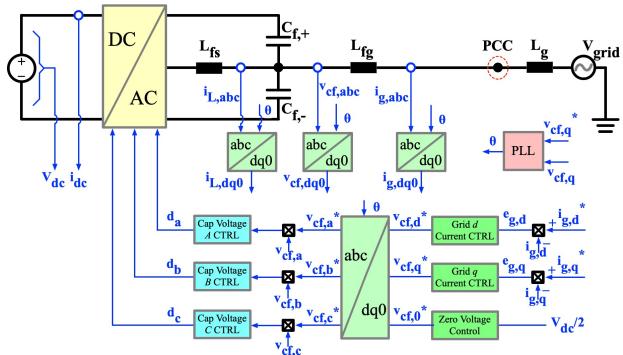

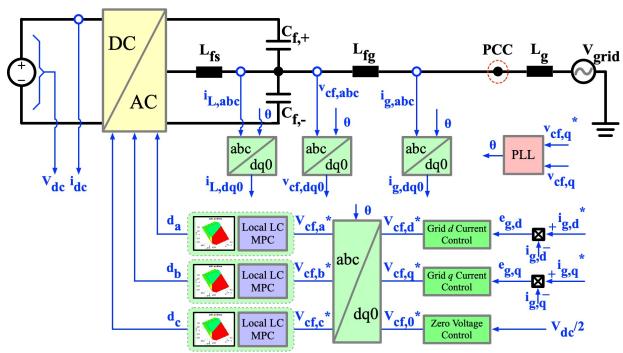

This paper designs a cascaded modular model predictive control architecture for a modified non-isolated *LCL* filtered grid-connected inverter. The proposed method is configured as continuous control set model predictive control (CCS-MPC) for the implementation. The designed MMPC includes an upper level grid side inductor current PI control and lower level per phase switch side inductor, output capacitor (*LC*) filter MPC control. The inner loop MPC can be functioned as an active damping term to attenuate the resonance and improve the system stability. Thus, the control bandwidth can be increased by enlarging the outer loop gain without exciting oscillations. Also, since only the switch side *LC* parameters are leveraged for the MPC state space model and the grid side inductor current is controlled by the PI, the uncertainty of grid side inductance will not influence the control performance. The paper is organized as follows. Firstly, the modified non-isolated *LCL* filtered inverter is introduced with the system modeling in *abc* and *dq0* reference frames. The modified topology is capable of bypassing the leakage current from flowing into the grid. Secondly, three control structures are designed for the modified non-isolated converter with zero-sequence stabilization capabilities to attenuate the leakage current which include PI control, PI control+notch filter, PI control cascaded with MMPC. Thirdly, three control architectures are compared and analyzed with transfer functions to study the resonance rejection capabilities. The cascaded MMPC method attenuates most of the resonance

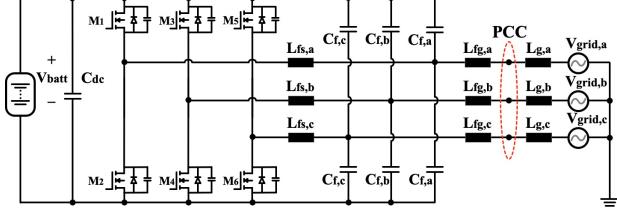

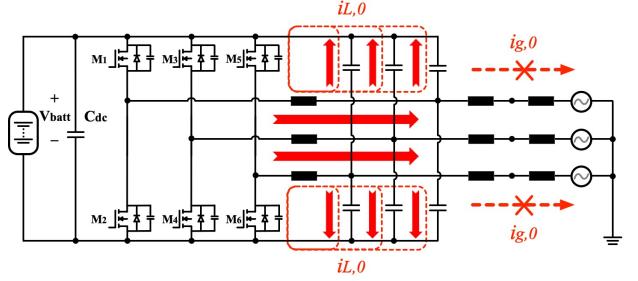

Fig. 1. Non-isolated *LCL* inverter with low leakage current.

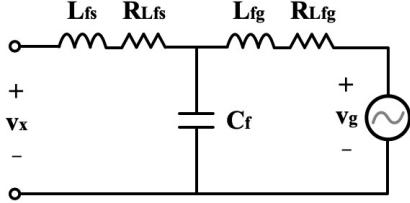

Fig. 2. Equivalent *LCL* circuit with consideration of ESR.

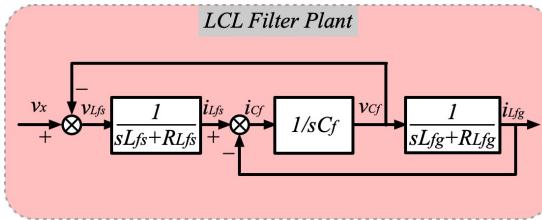

Fig. 3. *LCL* plant model with consideration of ESR.

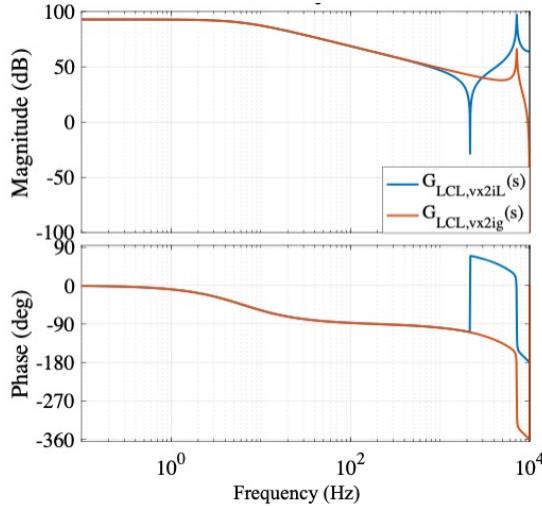

Fig. 4. *LCL* plant model transfer function bode plots with consideration of ESR.

and achieves the highest control bandwidth with the help of intrinsic active damping capability. An optimal control design method is developed for the cascaded MMPC to achieve better dynamic performance. Finally, the active damping analysis and proposed control design method are validated experimentally.

## II. *LCL* SYSTEM MODELING

The *LCL* system modeling is based on a modified non-isolated three-phase DC/AC converter which has been shown

in Fig. 1. Several methods have been proposed to improve the common mode performance of the traditional DC/AC converters. [14] connected the grid neutral to the three-phase output capacitors common point for the compensation of unbalanced three-phase power system. [15] inserted a grounding capacitor between the three-phase output capacitors common point and the ground to create a zero sequence bypassing path to reduce the leakage current. [16] introduced a fourth leg to be connected between the common point of three-phase output capacitors and DC bus neutral to attenuate the common mode voltage. [17] directly connected the fourth leg to the three-phase output capacitors common point with an extra *LC* circuit to stabilize the common mode voltage. Most of them cost extra switches to attenuate the common mode voltage. Different from the traditional two-level three-phase DC/AC converter, the common point of three-phase capacitors is connected to the DC bus positive/negative terminals to create a bypassing path for zero-sequence capacitor voltage and zero-sequence switch side inductor current control. By leveraging the topological modification and zero-sequence control methods, the common mode voltage can be stabilized to reduce the leakage current. From the perspective of system dynamic performance, the state space equations and transfer functions of the *LCL* plant model are derived for optimal design.

### A. DC/AC *LCL* Plant Modeling

For a precise modeling of the *LCL* filtered converter system, the equivalent series resistors (ESR) of the switch side and grid side inductors are both taken into considerations [18], [19]. For per phase switch side inductor current,  $i_{Lfs}$ , capacitor voltage,  $v_{Cf}$ , grid side inductor current,  $i_{Lfg}$ , grid voltage,  $v_g$  and phase leg output voltage,  $v_x$ , the equivalent *LCL* circuit with ESR has been shown in Fig. 2. The corresponding state space equations can be expressed as:

$$L_{fs} \frac{di_{Lfs}}{dt} = -v_{Cf} - R_{Lfs}i_{Lfs} + v_x \quad (1a)$$

$$C_f \frac{dv_{Cf}}{dt} = i_{Lfs} - i_{Lfg} \quad (1b)$$

$$L_{fg} \frac{di_{Lfg}}{dt} = v_{Cf} - R_{Lfg}i_{Lfg} - v_g \quad (1c)$$

where  $L_{fs}$ ,  $C_f$  and  $L_{fg}$  are the switch side inductor, output capacitor and grid side inductor, respectively.  $R_{Lfs}$  and  $R_{Lfg}$  are the ESR of the switch side inductor and grid side inductor, respectively.

To further derive the standardized format for transfer function, the state space equations can be expressed as matrix format [20]:

$$\frac{dX}{dt} = \mathbf{AX} + \mathbf{B}_c v_x + \mathbf{B}_g v_g \quad (2a)$$

$$i_{Lfs} = \mathbf{C}_c X \quad (2b)$$

$$i_{Lfg} = \mathbf{C}_g X \quad (2c)$$

where  $X$  is the state variable matrix and can be illustrated as:

$$\mathbf{X} = \begin{bmatrix} i_{Lfs} \\ v_{Cf} \\ i_{Lfg} \end{bmatrix}. \quad (3)$$

$\mathbf{A}$ ,  $\mathbf{B}_c$ ,  $\mathbf{B}_g$ ,  $\mathbf{C}_c$ ,  $\mathbf{C}_g$  are the system matrices and can be expressed as:

$$\mathbf{A} = \begin{bmatrix} \frac{-R_{Lfs}}{L_{fs}} & \frac{-1}{L_{fs}} & 0 \\ \frac{1}{C_f} & 1 & \frac{-1}{C_f} \\ 0 & \frac{1}{L_{fg}} & \frac{-R_{Lfg}}{L_{fg}} \end{bmatrix} \quad (4a)$$

$$\mathbf{B}_c = \begin{bmatrix} \frac{1}{L_{fs}} \\ 0 \\ 0 \end{bmatrix}, \quad \mathbf{B}_g = \begin{bmatrix} 0 \\ 0 \\ \frac{-1}{L_{fs}} \end{bmatrix} \quad (4b)$$

$$\mathbf{C}_c = \begin{bmatrix} 1 \\ 0 \\ 0 \end{bmatrix}, \quad \mathbf{C}_g = \begin{bmatrix} 0 \\ 0 \\ 1 \end{bmatrix} \quad (4c)$$

Based on the state space matrix equations, the transfer functions can be derived accordingly to illustrate the *LCL* plant model. Specifically, the transfer function from phase leg output voltage,  $v_x$ , to switch side inductor current,  $i_{Lfs}$ , can be expressed as:

$$G_{LCL,vx2iL}(s) = \frac{i_{Lfs}(s)}{v_x(s)} = \mathbf{C}_c(s\mathbf{I} - \mathbf{A})^{-1}\mathbf{B}_c, \quad (5)$$

where  $\mathbf{I}$  is the  $3 \times 3$  identity matrix. The transfer function from phase leg output voltage,  $v_x$ , to grid side inductor current,  $i_{Lfg}$ , can be expressed as:

$$G_{LCL,vx2ig}(s) = \frac{i_{Lfg}(s)}{v_x(s)} = \mathbf{C}_g(s\mathbf{I} - \mathbf{A})^{-1}\mathbf{B}_c. \quad (6)$$

For the illustration of the resonance issue in *LCL* filter system to control the grid current and consider the ESR, the equation (6) can be expanded as:

$$G_{LCL,vx2iLfg}(s) = \frac{i_{Lfg}(s)}{v_x(s)} = \frac{V_{dc}}{(sL_{fs} + R_{Lfs})(sL_{fg} + R_{Lfg})sC_f + (L_{fs} + L_{fg})s + (R_{Lfs} + R_{Lfg})}. \quad (7)$$

In the plant model transfer function, the quadratic term coefficient of the denominator is multiplied by the ESR of switch and grid side inductors,  $R_{Lfs}$  and  $R_{Lfg}$ . These two ESR values are ranged at a level of milliohms which are not enough to damp the resonance because of a too small portion of quadratic term coefficient [21]. The bode plots of equations (5) and (6) has been shown in Fig. 4. In the resonant frequency of

$$\omega_{res} = \sqrt{\frac{L_{fs} + L_{fg}}{L_{fs}L_{fg}C_f}}, \quad (8)$$

there exists a convex magnitude spike which could cause system stability issue.

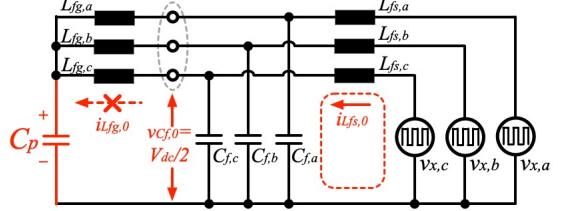

Fig. 5. Leakage current bypassing paths with the modified non-isolated topology.

Fig. 6. Equivalent common mode circuit of the modified non-isolated topology.

### B. Zero-Sequence Modeling

In a traditional transformerless three-phase grid-connected inverter, a leakage current path could be excited by the high frequency fluctuation of common mode voltage [22], [23]. In a *dq0* reference frame system, the common mode voltage is represented as the zero-sequence component. Thus, a high frequency oscillation of zero-sequence voltage can cause high leakage current in the parasitic paths [24]. The value of leakage current,  $i_{lkg}$ , is mainly determined by the parasitic capacitance,  $C_{para}$ , and the change rate of zero-sequence voltage,  $v_{Cf,0}$ , [5]:

$$i_{lkg} = C_{para} \frac{dv_{Cf,0}}{dt} \quad (9)$$

where  $v_{Cf,0}$  is the mean value of three-phase output capacitor voltages,  $v_{Cf,a}$ ,  $v_{Cf,b}$ ,  $v_{Cf,c}$ . In a conventional *LCL* filtered grid-tied inverter, the zero-sequence voltage always fluctuates in high frequency:

$$v_{Cf,0} = \frac{v_{Cf,a} + v_{Cf,b} + v_{Cf,c}}{3}. \quad (10)$$

However, with the modified non-isolated converter topology in Fig. 1, the zero-sequence voltage can be stabilized as half of DC bus voltage,  $V_{dc}/2$ . And the connections of three-phase output capacitors common points to the positive/negative DC bus terminals enables the grid side leakage current to be bypassed and attenuated as is shown in Fig. 5. With the improved topology, the zero-sequence current only flows through the switch side inductors and output capacitors instead of further injecting into the grid. Leveraging the zero-sequence voltage/current control methods, the leakage current can be limited within the standard requirements of less than 30mA in a EV system by IEC 62955:2018 and IET Wiring Regulation 18th Edition (BS 7671:2018) Section 722.531.2.101 [25].

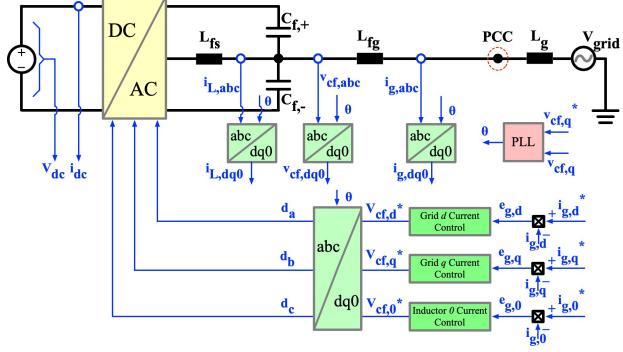

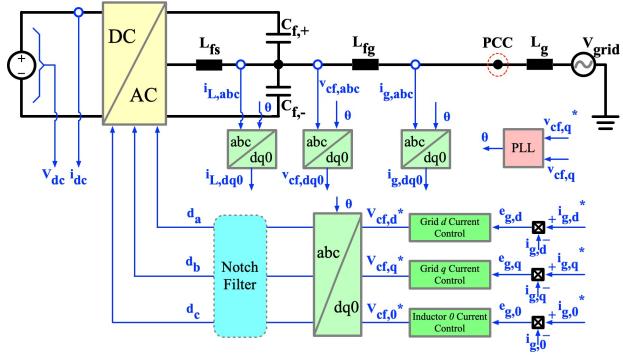

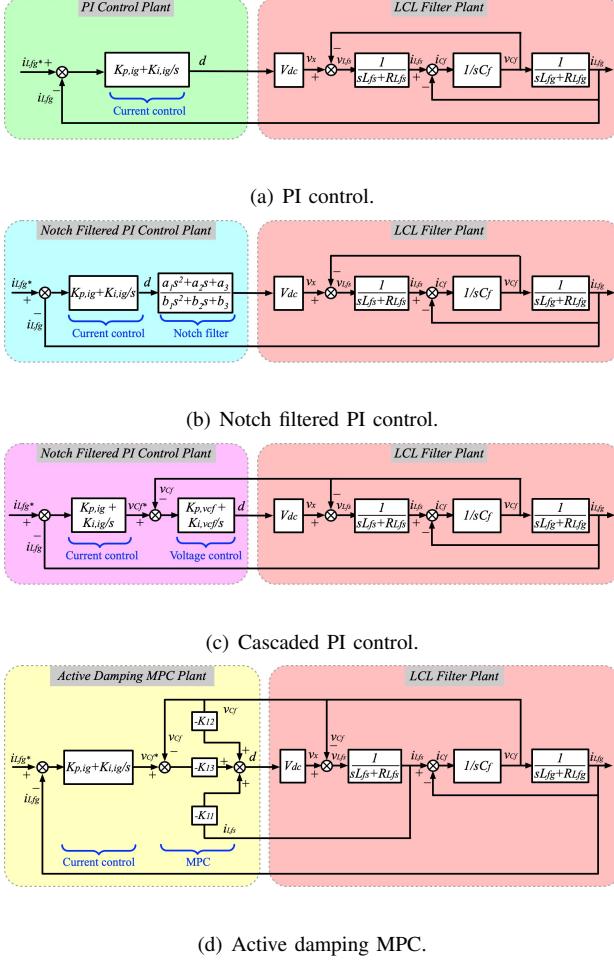

(a) PI control.

(b) Notch filtered PI control.

(c) Cascaded PI control.

(d) Active damping MPC.

Fig. 7. Control diagrams of the (a) PI (b) notch filtered PI (c) cascaded PI and (d) active-damping MPC for the transformerless *LCL* inverter.

### III. CONTROL STRUCTURES ANALYSIS

The control strategies of the modified *LCL* filtered inverter are analyzed in this section. Different from the conventional control methods of grid-connected inverters [26], the zero-sequence components of output capacitor voltage and switch side inductor current are stabilized with specific controllers. To analyze the dynamic performances and resonance behaviors of different control strategies in *LCL* filter system, four control structures are studied including PI control, PI control with notch filter, cascaded PI and cascaded modular model predictive control methods.

#### A. PI Control

The PI method of control diagram is shown in Fig. 7(a). The grid current is transformed from *abc* to *dq0* reference frame based on Park and Clarke transformations. Then, the *d*, *q* and 0 sequences of the grid current are controlled by PI in DC frame for a better dynamic tracking performance. *d*, *q* and 0 are corresponding to active power, reactive power and common mode components, respectively. The output of the grid current controller will be transformed from *dq0* back to *abc* reference frame for duty cycle of PWM modulation. With the zero-sequence controller to minimize the zero-sequence grid current with a tracking reference of 0A, the common mode leakage current on the grid side can be attenuated to a low level.

The transfer functions of *dq0* grid current controllers can be expressed as:

$$G_{iLfgd,PI}(s) = K_{p,iLfgd} + \frac{K_{i,iLfgd}}{s} \quad (11a)$$

$$G_{iLfgq,PI}(s) = K_{p,iLfgq} + \frac{K_{i,iLfgq}}{s} \quad (11b)$$

$$G_{iLfg0,PI}(s) = K_{p,iLfg0} + \frac{K_{i,iLfg0}}{s}. \quad (11c)$$

With the PI control strategy, the resonance of *LCL* filter in Fig. 4 still exists at the resonant frequency point.

#### B. PI Control with Notch Filter

To attenuate the resonance of *LCL* system, a notch filter can be added after the output of grid current controllers as is shown in Fig. 7(b). The principle of notch filter is to flatten the spike within a certain range centered at resonant frequency point. The notch filter can be designed in continuous-time as

$$G_{Notch}(s) = \frac{s^2 + \omega_{res}^2}{s^2 + \frac{\omega_{res}}{Q}s + \omega_{res}^2} \quad (12)$$

and implemented in discrete-time as difference equations. The variable *Q* represents the quality factor and is configured to adjust the frequency range of notch filter.

With the help of notch filter, the resonance of the peak spike from the *LCL* system can be attenuated. However, on one hand, another concave spike may be excited because of the notch filter. On the other hand, the added notch filter reduces the control bandwidth and slows down the dynamic performance.

### C. Cascaded PI Control

To make a comprehensive comparison of resonance damping and dynamic performance before introducing the proposed cascaded modular model predictive control method, the cascaded PI control is analyzed as is shown in Fig. 7(c). The cascaded PI control diagram for the *LCL* filtered inverter includes the the outer loop of grid side inductor current control and inner loop capacitor voltage control. The references for the inner loop capacitor voltage control are derived from the output of the outer loop grid side inductor current control.

The transfer functions of capacitor voltage controller can be expressed as:

$$G_{vCf,PI}(s) = K_{p,vCf} + \frac{K_{i,vCf}}{s} \quad (13)$$

The output of the capacitor voltage controller will be transformed to the duty cycle for PWM modulation.

### D. Cascaded Modular Model Predictive Control

To increase the control speed and solve the concave spike of PI+notch filter method and attenuate the resonance spike issue of PI control method, a cascaded modular model predictive control method is developed in this section. The control diagram of the cascaded MMPC is shown in Fig. 7(d). It includes two cascaded control layers: (1) the outer loop of grid side inductor current PI control in *dq0* reference frame; (2) the inner loop of per phase switch side *LC* filter inductor current/capacitor voltage MPC control in *abc* reference frame and zero-sequence output capacitor voltage MPC control. The reasons for implementing the grid side inductor current PI control in *dq0* and per phase switch side *LC* current/voltage MPC control in *abc* reference frames, respectively, can be concluded in two aspects: (1) the MPC has better tracking performance and transient behavior on time-varying AC reference signals than PI; (2) the outer loop grid side *d* and *q* current are corresponding to the active and reactive power, respectively. Thus, instead of configuring AC references for grid side *abc* phase current, *dq* grid current references can be directly linked to the active/reactive power control when grid services are required.

1) *Outer loop grid current PI control*: For the outer loop control, the grid side inductor current is firstly transformed from *abc* to *dq* reference frame with Clarke and Park transformations. Then, two PI controllers are configured to regulate the *dq* sequence of grid currents,  $i_{Lfg,d}$  and  $i_{Lfg,q}$ , respectively. The *d* and *q* components of grid current references,  $i_{Lfg,d}^*$  and  $i_{Lfg,q}^*$ , represent the active and reactive power, respectively. Then, the outputs of grid current controller are configured as the references for *dq* sequence output capacitor voltages,  $v_{Cf,d}^*$  and  $v_{Cf,q}^*$ , which will be transformed to *abc* reference frame and configured as the references of inner loop per phase *LC* capacitor voltage MPC.

2) *Zero-sequence capacitor voltage MPC*: For the stabilization of common mode voltage to bypass the grid side leakage current, the zero sequence component of output capacitor voltages is independently controlled through MPC as half of DC bus voltage. Thus, half of DC bus voltage measurement,

$V_{dc}$ , is configured as the reference of per phase zero sequence voltage MPC. With the zero sequence voltage MPC, the grid side leakage current can be attenuated to be lower than the standard requirement.

3) *Inner loop per phase LC MPC*: An explicit MPC method is designed for the switch side capacitor voltage and inductor current control. As is shown in Fig. 7(d) of the control diagram, the three-phase capacitor voltages are controlled in *abc* frame to follow the references from the cascaded grid current controller's outputs. The switch side inductor currents are also regulated with the MPC by adjusting the weighing factor between  $i_{Lfs,abc}$  and  $u_{Cf,abc}$ . The benefits to configure the MPC per phase in *abc* frame can be concluded as: (1) the state space matrix of LC per phase is simpler than *dq* system to implement the offline piecewise affine optimization code in a less costly DSP controller; (2) The time-varying angular speed term,  $\omega$ , can be omitted in the explicit MPC state space matrix for the offline optimization calculation; (3) Per phase MPC for LC is more flexible for a modular design perspective to extend the paralleled phase number and other topologies, e.g., DC/DC, single-phase DC/AC converters.

For the MPC implementation, in every control period, the MPC controller receives the measured switch side inductor current,  $i_{Lfs,abc}$ , output capacitor voltage,  $v_{Cf,abc}$ , grid side inductor current,  $i_{Lfg,abc}$ , from ADC and output capacitor voltage references,  $v_{Cf,abc}^*$  from the outer loop grid side inductor current PI controller. An offline generated piecewise affine search tree is applied to derive the optimal duty cycle for the explicit MPC. The state equations of switch side LC filter can be expressed as

$$i_{Lfs}(k+1) = i_{Lfs}(k) - \frac{T_s}{L_{fs}} v_{Cf}(k) + \frac{V_{dc} T_s}{L_{fs}} d(k) \quad (14a)$$

$$v_{Cf}(k+1) = \frac{T_s}{C_f} i_{Lfs}(k) + v_{Cf}(k) - \frac{T_s}{C_f} i_{Lfg}(k). \quad (14b)$$

For the flexibility of implementing the explicit MPC and the convenience of experimentally adjusting the DC bus voltage during test, the last term of (14),  $V_{dc} d(k)$ , can be replaced by the phase leg output voltage,  $v_x(k)$ . The state-space model can be expressed in standard matrix format of

$$X_{k+1} = AX_k + Bu_k + Ee_k \quad (15)$$

where the variables and matrices represent

$$A = \begin{bmatrix} 1 - \frac{R_{Lfs}}{L_{fs}} & -\frac{T_s}{L_{fs}} \\ \frac{T_s}{C_f} & 1 \end{bmatrix}, B = \begin{bmatrix} \frac{T_s}{L_{fs}} \\ 0 \end{bmatrix}, E = \begin{bmatrix} 0 \\ -\frac{T_s}{C_f} \end{bmatrix}, \quad (16a)$$

$$X_k = \begin{bmatrix} i_{Lfs}(k) \\ v_{Cf}(k) \end{bmatrix}, u_k = [ V_{dc} d(k) ], e_k = [ i_{Lfg}(k) ]. \quad (16b)$$

In the MPC formulation, the inductor current/capacitor voltage references can be defined as  $\bar{X}$  and the tracking errors between

the measurement and the references are expressed as  $\tilde{X}$  which are composed of

$$\bar{X}_k = \begin{bmatrix} i_{Lfs,ref}(k) \\ v_{Cf,ref}(k) \end{bmatrix}, \tilde{X}_k = \begin{bmatrix} i_{Lfs,ref}(k) - i_{Lfs}(k) \\ v_{Cf,ref}(k) - v_{Cf}(k) \end{bmatrix}. \quad (17)$$

Thus, the cost function includes two terms

$$\min \sum_{k=0}^{N_c} \tilde{X}_k^T Q \tilde{X}_k + \sum_{k=0}^{N_p-1} \Delta u_k^T R \Delta u_k. \quad (18)$$

For the penalties of the cost function,  $Q$  and  $R$  represent the weighing factor matrices that are implemented on the state values and input values, respectively.

The constraints of the MPC controller can be expressed as

$$\tilde{X}_{k+1} = A\tilde{X}_k + Bu_k + Ee_k \in \mathcal{X} \quad (19)$$

$$\Delta u_k = u_k - u_{k-1} \in \mathcal{U} \quad (20)$$

$$\begin{bmatrix} -I_{Lfs,max} \\ 0 \end{bmatrix} \leq X_k \leq \begin{bmatrix} I_{Lfs,max} \\ V_{dc} \end{bmatrix} \quad (21)$$

$$\begin{bmatrix} 0 \\ V_{dc} \end{bmatrix} \leq u_k \leq \begin{bmatrix} V_{dc} \end{bmatrix} \quad (22)$$

$$\begin{bmatrix} -I_{Lfg,max} \end{bmatrix} \leq e_k \leq \begin{bmatrix} I_{Lfg,max} \end{bmatrix}. \quad (23)$$

For the implementation of MPC algorithm in every control period [27], the cost function in (18) will be solved to predict the future steps of optimal input variable,  $u_k$ . And the first step of the input value will be implemented as the MPC output for the PWM modulation. Different from the PI control process, the MPC algorithm derives the optimal duty cycle by processing the state variable,  $X_k$ , and tracking error,  $\tilde{X}_k$ , in a linear way with specific coefficients. Since no integration procedure is needed in MPC, the dynamic performance of MPC is better than PI with less overshoot and higher tracking speed. Also, the inner loop MPC has higher control bandwidth which can be functioned as an active damping term to solve the *LCL* resonance. Due to the active damping and high bandwidth of the inner loop MPC, the outer loop PI gains can be largely increased to speed up the dynamic reference tracking performance without causing extra resonance issue.

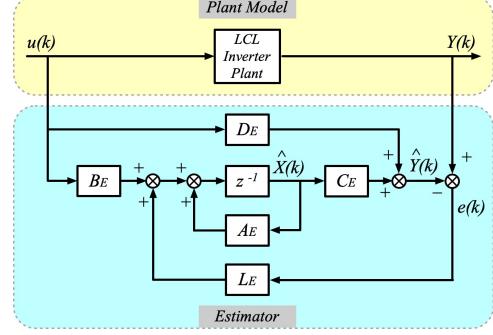

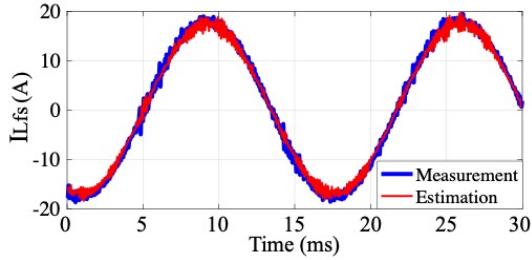

For the cascaded model predictive control of *LCL* filter system, a state estimator is designed in Fig. 8 to reduce the sensor count. One of the three variables,  $i_{Lfs}, v_{Cf}, i_{Lfg}$ , can be estimated by the other two. The merits of the estimator include the anti-noise capability for better control performance and the reduction of sensor cost.

Specifically, the Luenberger observer is designed to estimate the switch side inductor current,  $\hat{i}_{Lfs}$ , capacitor voltage,  $\hat{v}_{Cf}$ , and grid side inductor current,  $\hat{i}_{Lfg}$ , with the samplings of capacitor voltage,  $v_{Cf}$ , and grid side inductor current,  $i_{Lfg}$ . The state-space equations for the discrete-time state estimator can be expressed in standard matrix format of

$$\hat{X}_{k+1} = A_E \hat{X}_k + B_E u_k + L_E (Y_k - \hat{Y}_k) \quad (24a)$$

$$\hat{Y}_{k+1} = C_E \hat{X}_k + D_E u_k \quad (24b)$$

where the variables and matrices for Luenberger observer represent

Fig. 8. Diagram of the state estimator.

$$A_E = \begin{bmatrix} 0 & -\frac{1}{L_{fs}} & 0 \\ \frac{1}{C_f} & 0 & -\frac{1}{C_f} \\ 0 & 0 & 0 \end{bmatrix}, B_E = \begin{bmatrix} \frac{1}{L_{fs}} \\ 0 \\ 0 \end{bmatrix}, \quad (25a)$$

$$C_E = \begin{bmatrix} 0 & 1 & 0 \\ 0 & 0 & 1 \end{bmatrix}, D_E = \begin{bmatrix} 0 \\ 0 \end{bmatrix}, \quad (25b)$$

$$\hat{X}_k = \begin{bmatrix} \hat{i}_{Lfs}(k) \\ \hat{v}_{Cf}(k) \\ \hat{i}_{Lfg}(k) \end{bmatrix}, \hat{Y}_k = \begin{bmatrix} \hat{v}_{Cf}(k) \\ \hat{i}_{Lfg}(k) \end{bmatrix}. \quad (25c)$$

$L_E$  is a  $3 \times 2$  observer gain matrix that can be tuned to achieve minimal estimation errors. The diagram of the state estimator is shown in Fig. 8. The state observer minimizes the estimation error,  $e(k)$ , with a dynamic equation of

$$e_{k+1} = (A_E - L_E C_E) e_k. \quad (26)$$

The estimation gain can be derived by

$$L_E^T = R M^{-1} \quad (27)$$

where  $R$  is composed of tuning factors and  $M$  is determined by solving the Sylvester equation

$$A_E^T M - M \Lambda = C_E^T R \quad (28)$$

in which  $\Lambda$  is a matrix with the desired eigenvalues.

#### IV. OPTIMAL CONTROL DESIGN FOR RESONANCE DAMPING AND DYNAMIC PERFORMANCE

The optimal control design for resonance damping and dynamic performance of *LCL* filtered grid-connected inverter is analyzed in this section. Four control strategies in Fig. 7 are compared with transfer functions, bode plots, step responses and root locus to illustrate the active damping and dynamic performance improvement capabilities of the cascaded MMPC method [28].

##### A. Control Plant Model Analysis

The integrated plant models of the three control strategies including *LCL* filter and control blocks are derived in Fig. 9. The former stages are the three types of control blocks with the input variable of grid side inductor current and output

Fig. 9. Plant models of the (a) PI (b) notch filtered PI (c) cascaded PI and (d) active-damping MPC for the transformerless *LCL* inverter.

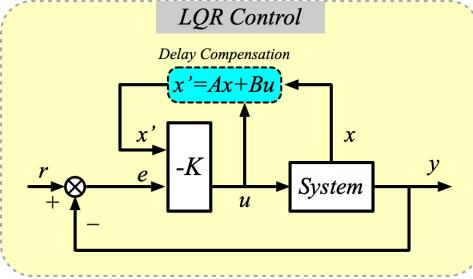

Fig. 10. Typical LQR control diagram with delay compensation.

variable of duty cycle. The latter stage is the *LCL* filter plant model which has been derived in Fig. 3. Thus, the complete transfer functions can be expressed based on different control strategies.

1) *PI control transfer function*: For the first control strategy of PI method in Fig. 7(a), the corresponding system plant model has been shown in Fig. 9(a). Based on the derivations in (7) and (11), the transfer function from tracking error,  $i_{Lfg,err}$ , to the measurement,  $i_{Lfg}$ , of grid side inductor current can be expressed as:

$$G_{iLfg,err2iLfg,PI}(s) = G_{iLfg,PI}(s) \cdot G_{LCL,vx2iLfg}(s). \quad (29)$$

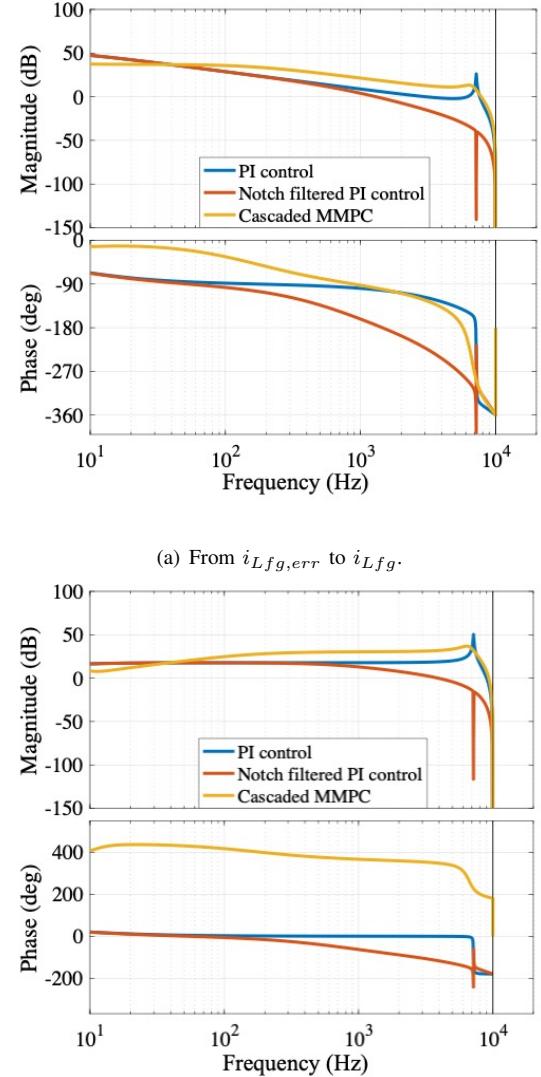

Fig. 11. Comparison of bode plots for three control strategies (a) from  $i_{Lfg,err}$  to  $i_{Lfg}$  and (b) from  $i_{Lfg,err}$  to  $v_{Cf}$ .

2) *Notch filtered PI control transfer function*: For the second control strategy of adding a notch filter after the PI controller to attenuate the resonance spike in Fig. 7(b), the corresponding system plant model has been shown in Fig. 9(b). Based on the derivation of notch filter design in (12), the transfer function from tracking error,  $i_{Lfg,err}$ , to the measurement,  $i_{Lfg}$ , of grid side inductor current can be expressed as:

$$G_{iLfg,err2iLfg,NotchPI}(s) = G_{iLfg,PI}(s) \cdot G_{Notch}(s) \cdot G_{LCL,vx2iLfg}(s). \quad (30)$$

3) *Cascaded PI control transfer function*: For the third control strategy of cascaded PI controller in Fig. 7(c), the corresponding system plant model has been shown in Fig. 9(c). Based on the derivations in (7) and (13), the transfer function from tracking error of output capacitor voltage,  $v_{Cf,err}$ , to

(a) From  $i_{Lfg,err}$  to  $i_{Lfg}$ .(b) From  $i_{Lfg,err}$  to  $v_{Cf}$ .

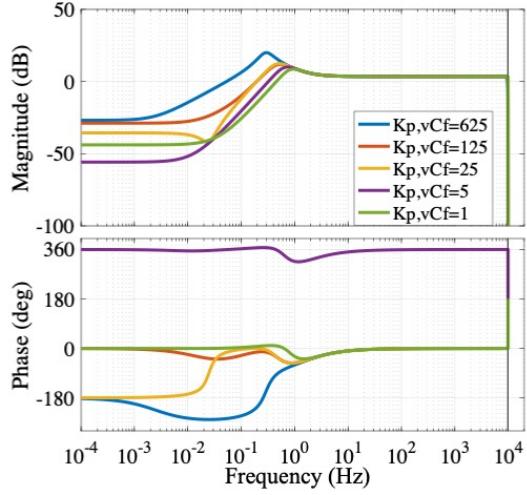

Fig. 12. Bode plots for cascaded PI control from (a)  $i_{Lfg,err}$  to  $i_{Lfg}$  and (b)  $i_{Lfg,err}$  to  $v_{Cf}$  with the inner loop  $K_{p,vCf}$  gain swept from 1 to 625.

the measurement of grid side inductor current,  $i_{Lfg}$ , can be derived as:

$$G_{vCferr2iLfg,CascadedPI}(s) = G_{vCf,PI}(s) \cdot G_{LCL,vx2iLfg}(s). \quad (31)$$

Then, the transfer function from the reference of output capacitor voltage,  $v_{Cf,ref}$ , to the measurement of grid side inductor current,  $i_{Lfg}$ , can be expressed as:

$$G_{vCfref2iLfg,CascadedPI}(s) = \frac{G_{vCferr2iLfg,CascadedPI}(s)}{1 + G_{vCferr2iLfg,CascadedPI}(s)}. \quad (32)$$

Furthermore, adding the outer loop grid side inductor current PI control, the transfer function from the tracking error,  $i_{Lfg,err}$ , to the measurement,  $i_{Lfg}$ , of grid side inductor current can be expressed as:

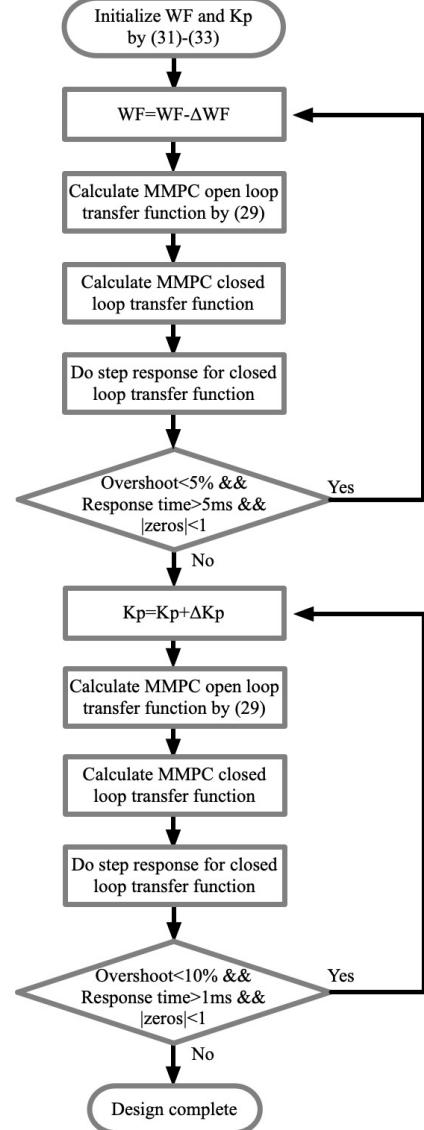

Fig. 13. The cascaded MMPC control parameter design flow chart.

$$G_{iLfgerr2iLfg,CascadedPI}(s) = G_{vCfref2iLfg,CascadedPI}(s) \cdot G_{vCfref2iLfg,CascadedPI}(s). \quad (33)$$

Then, the transfer function from the reference,  $i_{Lfg,ref}$ , to the measurement,  $i_{Lfg}$ , of grid side inductor current can be derived as:

$$G_{iLfgref2iLfg,CascadedPI}(s) = \frac{G_{iLfgerr2iLfg,CascadedPI}(s)}{1 + G_{iLfgerr2iLfg,CascadedPI}(s)}. \quad (34)$$

And, based on equation (34) and the LCL plant model in Fig. 3, the transfer function from the reference of switch side inductor current,  $i_{Lfg,ref}$ , to the measurement of output capacitor voltage,  $v_{Cf}$ , can be derived as

$$G_{iLfgref2vCf,CascadedPI}(s) = G_{iLfgref2iLfg,CascadedPI}(s) \cdot (sL_{fg} + R_{Lfg}). \quad (35)$$

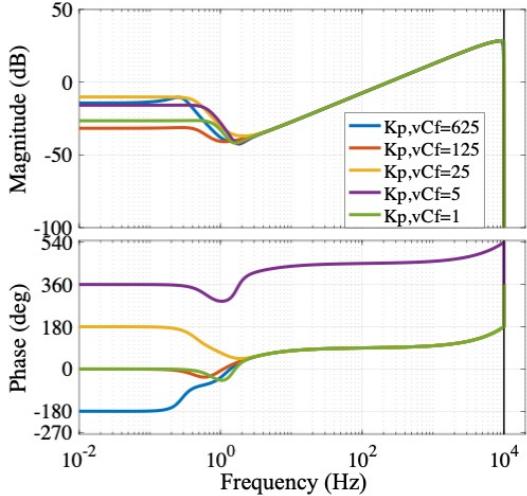

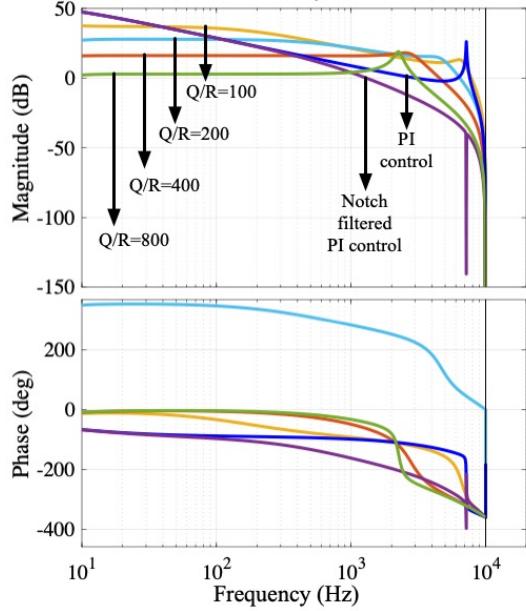

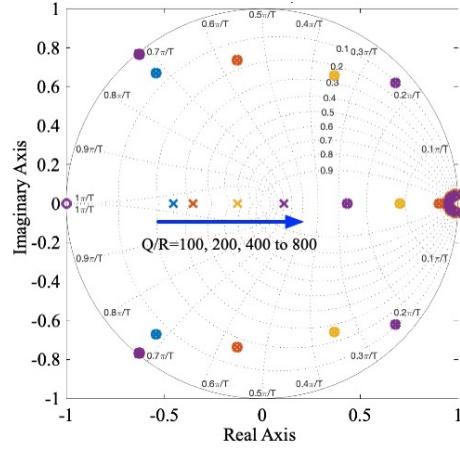

(a) Weighing factor Q/R swept from 100 to 800 at the  $K_p$  gain of 10.

(b)  $K_p$  gain swept from 10 to 40 at the Q/R of 400.

Fig. 14. The bode plots of the PI control, notch filtered PI control and cascaded MMPC methods transfer functions from  $i_{Lfg,err}$  to  $i_{Lfg}$  with the cascaded MMPC (a) weighing factor Q/R swept from 100 to 800 at the  $K_p$  gain of 10 and (b)  $K_p$  gain swept from 10 to 40 at the Q/R of 400.

4) *Cascaded MMPC control transfer function:* For the fourth control strategy of cascaded MMPC in Fig. 7(d), the corresponding system plant model has been shown in Fig. 9(d). The inner loop per phase switch side *LC* MMPC is cascaded with the outer loop of grid side inductor current control. A linear-quadratic regulator (LQR) can be applied to derive the transfer function for the MPC algorithm part in the control plant model of Fig. 9(d) to solve the cost function of (18).

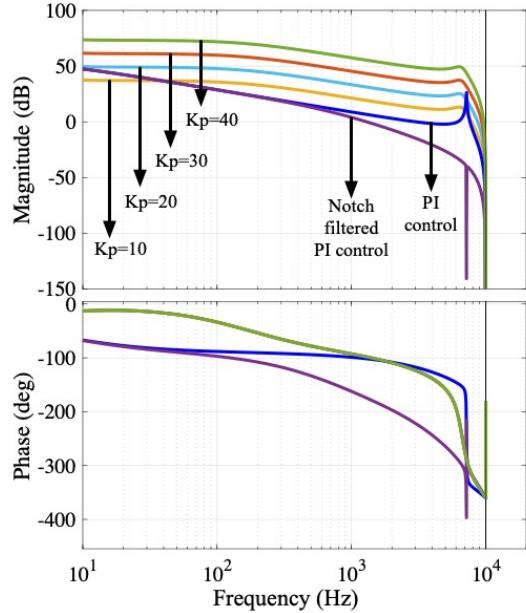

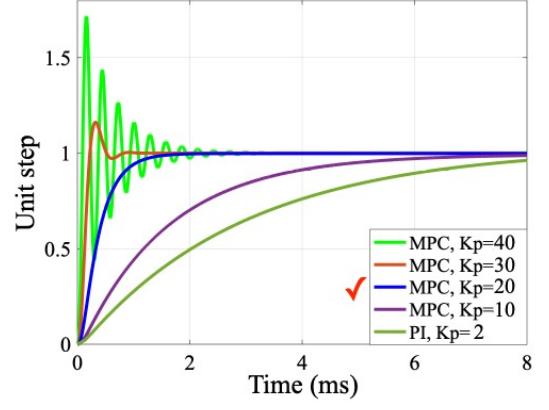

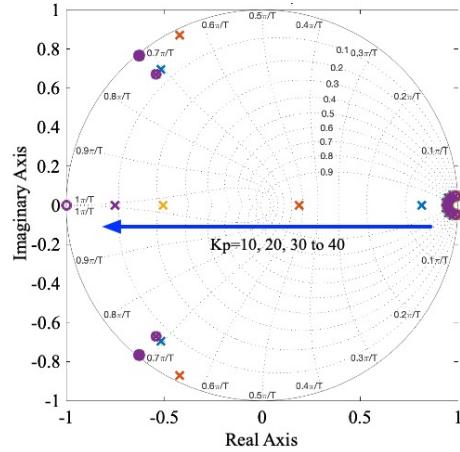

(a) Weighing factor Q/R swept from 100 to 800.

(b)  $K_p$  gain swept from 10 to 40.

Fig. 15. The step responses of the cascaded MMPC close loop transfer function from  $i_{Lfg,err}$  to  $i_{Lfg}$  with (a) weighing factor Q/R swept from 100 to 800 and (b)  $K_p$  gain swept from 10 to 40.

A typical LQR control diagram integrated with a dynamic system is shown in Fig. 10 where  $x, y, u, r$  represent the state variable,  $[i_{Lfs}; v_{Cf}]$ , output variable,  $i_{Lfs}$ , input variable of duty cycle,  $d$ , and tracking reference,  $i_{Lfs,ref}$ , respectively. The middle block of Fig. 10 is the core algorithm of MPC to calculate the optimal duty cycle which is a linear coefficient matrix,  $-\mathbf{K}$ . And the MPC equation to calculate the optimal duty cycle based on the tracking error and state variable can be expressed as:

$$d = -\mathbf{K} \begin{bmatrix} i_{Lfs} \\ v_{Cf} \\ v_{Cf,err} \end{bmatrix} = -[K_{11}, K_{12}, K_{13}] \begin{bmatrix} i_{Lfs} \\ v_{Cf} \\ v_{Cf,err} \end{bmatrix} \quad (36)$$

where  $v_{Cf,err}$  is the tracking error of the MPC calculated as  $v_{Cf,ref} - v_{Cf}$ .

Thus, the inner loop of MPC can be expressed in the transfer function as Fig. 9(d). The transfer function from tracking error,  $v_{Cf,err}$ , to the measurement,  $v_{Cf}$ , of output capacitor voltage can be expressed as:

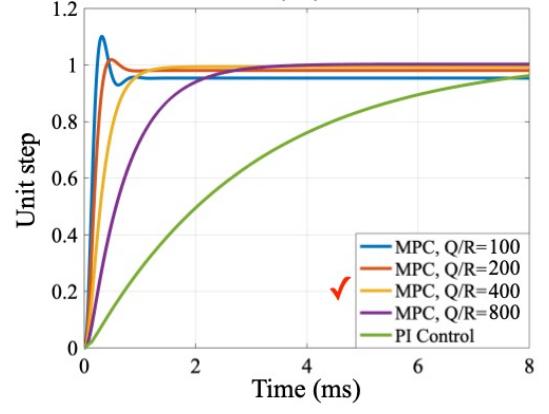

(a) Weighing factor Q/R swept from 100 to 800.

(b)  $K_p$  gain swept from 10 to 40.

Fig. 16. The zeros and poles plots of the cascaded MMPC from  $i_{Lfg,err}$  to  $i_{Lfg}$  with (a) weighing factor Q/R swept from 100 to 800 and (b)  $K_p$  gain swept from 10 to 40.

$$G_{vCferr2vCf,MPC}(s) = \frac{-K_{13}G_{LCL,vx2ig}(s)(sL_{fg} + R_{Lfg})(sL_{fs} + R_{Lfs})/V_{dc}}{\{(sL_{fs} + R_{Lfs}) + K_{11}[V_{dc} - G_{LCL,vx2ig}(s)(sL_{fg} + R_{Lfg})]/V_{dc} + K_{12}G_{LCL,vx2ig}(s)(sL_{fs} + R_{Lfs})(sL_{fg} + R_{Lfg})/V_{dc} - K_{13}G_{LCL,vx2ig}(s)(sL_{fs} + R_{Lfs})(sL_{fg} + R_{Lfg})/V_{dc}\}}. \quad (37)$$

Furthermore, the transfer function from the reference,  $v_{Cf,ref}$ , to the measurement,  $v_{Cf}$ , of output capacitor voltage can be expressed as:

$$G_{vCfref2vCf,MPC}(s) = G_{vCferr2vCf,MPC}(s)/[1 + G_{vCferr2vCf,MPC}(s)]. \quad (38)$$

Based on equation (38) and the *LCL* plant model in Fig. 3, the transfer function from the reference of output capacitor voltage,  $v_{Cf,ref}$ , to the measurement of grid side inductor current,  $i_{Lfg}$ , can be derived as:

$$G_{vCfref2iLfg,MPC}(s) = G_{vCfref2vCf,MPC}(s)/(sL_{fg} + R_{Lfg}). \quad (39)$$

Then, taking the outer loop grid side inductor current PI control into consideration, the cascaded MMPC transfer function from tracking error,  $i_{Lfg,err}$ , to the measurement,  $i_{Lfg}$ , of grid side inductor current can be expressed as:

$$G_{iLfgerr2iLfg,MPC}(s) = G_{vCfref2iLfg,MPC}(s) \cdot G_{iLfg,PI}(s). \quad (40)$$

The cascaded MMPC transfer function from tracking error of grid side inductor,  $i_{Lfg,err}$ , to the measurement of output capacitor voltage,  $v_{Cf}$ , can be expressed as:

$$G_{iLfgerr2vCf,MPC}(s) = G_{vCfref2vCf,MPC}(s) \cdot G_{iLfg,PI}(s). \quad (41)$$

### B. Mechanism of Inner-loop MMPC for Active Damping

The resonance behavior and dynamic performance of the four control strategies for *LCL* filtered grid-connected inverter are analyzed based on the derived transfer functions. Fig. 11(a), 12(a) and Fig. 11(b), 12(b) show the bode plots comparison of transfer functions from the tracking error to the measurement of grid side inductor current and from the tracking error of grid side inductor current to the measurement of output capacitor voltage, respectively. The magnitude plots manifest that the PI control in Fig. 9(a) has a convex spike at the resonant frequency point. The notch filtered PI control in Fig. 9(b) has a concave spike at the resonant frequency point. The cascaded PI control in Fig. 9(c) has a narrow bandwidth at high frequency range. The cascaded MMPC in Fig. 9(d) attenuates the spike at the resonant frequency point and the control bandwidth is wider than the conventional PI, notch filtered PI and cascaded PI methods.

Thus, the inner loop MPC of the cascaded MMPC is functioned as an active damping term to mitigate the resonance in *LCL* system. This active damping term contributes to the improvement of stability and control bandwidth. Furthermore, the fast response and active damping characteristics of the inner loop MPC permits a wider control bandwidth for the outer loop PI control. Instead of concerning about instability of resonance in the PI control method of Fig. 9(a), the gains of the outer loop grid side inductor PI controller can be largely increased to improve the dynamic performance. So, by carefully designing the outer loop PI control gain,  $K_p$ , and the inner loop MPC weighing factor of the cascaded MMPC,  $WF = Q/R$ , the *LCL* system dynamic performance can be further improved.

### C. Cascaded Control Design for Dynamic Performance

The control design of the proposed cascaded MMPC is analyzed in this section. Two key parameters of outer loop PI control gain,  $K_p$ , and the inner loop MPC weighing factor,  $WF$ , need to be designed. The bode plots of open loop transfer functions, closed loop step responses and zero-pole maps are evaluated for the design procedure.

The optimal cascaded control design flowchart is shown in Fig. 13 which includes inner loop MPC weighing factor,  $WF$ , design and outer loop grid side inductor current PI gain,  $K_p$ , design. Since the inner loop MPC can attenuate the resonance spike by functioning as an active damping term, the outer loop PI gain is permitted with a larger tuning range without losing stability. The control parameter design starts from the inner loop.

Firstly, the design parameters should be initialized based on the bandwidths of inner and outer loop controllers. Typically, the PI control bandwidth,  $BW_{PI}$ , is configured to be 5-10 times slower than the inner loop MPC bandwidth,  $BW_{MPC}$  [29]:

$$5BW_{PI} \leq BW_{MPC} \leq 10BW_{PI}. \quad (42)$$

And the PI control cutoff frequency,  $\omega_c$ , should be set below 30% of the  $LCL$  resonant frequency,  $\omega_{res}$ :

$$\omega_c \leq 30\% \omega_{res}. \quad (43)$$

The initial values for optimal PI gains design flow chart can follow the equations below [12]:

$$K_{p,iLfg} = \frac{(L_{fs} + L_{fg})f_{sw}}{3} \quad (44a)$$

$$\tau_{i,iLfg} = \frac{L_{fs} + L_{fg}}{R_{fs} + R_{fg}} \quad (44b)$$

where  $f_{sw}$  and  $\tau_{i,iLfg}$  are the switching frequency and integral time constant, respectively. The initial value for weighing factor can start from a typical range of 800-1000.

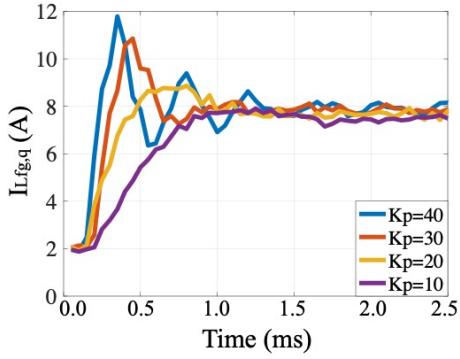

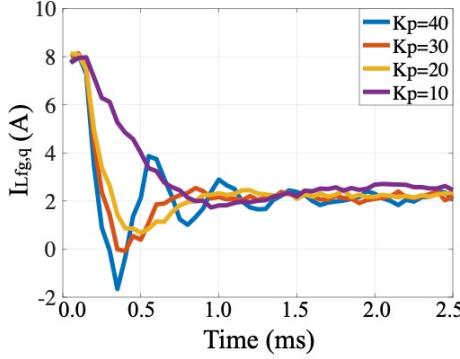

Secondly, based on the initial  $WF$  and  $K_p$ , the inner loop weighing factor is swept from 100 to 800. During the sweeping period, the bode plots of open loop transfer functions from  $i_{Lfg,err}$  to  $i_{Lfg}$  are derived in Fig. 14(a). Also, the step responses and zero-pole map of closed loop transfer functions from  $i_{Lfg,err}$  to  $i_{Lfg}$  are derived in Fig. 15(a) and Fig. 16(a), respectively. With the reduction of weighing factor, the control bandwidth is increased in Fig. 14(a). And the response time is decreased with more overshoot in the transient period as is shown in Fig. 15(a). The sweeping check conditions of inner loop MPC weighing factor are the overshoot percentage, response time and poles magnitude. Since the outer loop  $K_p$  gain is kept in low level and has not been tuned yet, the overshoot is not a big issue in the sweeping process of inner loop weighing factor. And the response time is largely determined by the outer loop  $K_p$  gain and has not been shortened yet in the inner loop sweeping process. Thus, for the sweeping procedure of weighing factor, the overshoot check condition threshold can be configured smaller than the outer loop sweeping process. And the response time check condition threshold can be configured larger than the outer loop sweeping process. If the overshoot is larger than 5%, response time is smaller than 5ms or poles are outside of the unit circle, the weighing factor sweeping is stopped to entering the outer loop PI gain sweeping procedure.

Thirdly, the outer loop PI gain is swept from 10 to 40. During the sweeping period, the bode plots of open loop

transfer functions from  $i_{Lfg,err}$  to  $i_{Lfg}$  are also derived in Fig. 14(b). Also, the step responses and zero-pole map of closed loop transfer functions from  $i_{Lfg,err}$  to  $i_{Lfg}$  are derived in Fig. 15(b) and Fig. 16(b), respectively. With the increment of gain, the control bandwidth is increased in Fig. 14(b). And the response time is decreased with more overshoot in the transient period as is shown in Fig. 15(b). Same sweeping check items of outer loop PI gain are configured as the overshoot percentage, response time and poles magnitude with different thresholds. Compared with the inner loop weighing factor sweeping, the outer loop gain sweeping procedure addresses more on the tracking speed and less on overshoot issue, since the inner loop MPC has been proved to guarantee an active damping function for the whole  $LCL$  system stability to attenuate the resonance. If the overshoot is larger than 10%, response time is smaller than 1ms or poles are outside of the unit circle, the weighing factor sweeping is stopped to finalize the outer loop PI gain sweeping procedure.

## V. RESULTS

The proposed optimal control design method for resonance damping and dynamic performance improvement is validated experimentally on the modified non-isolated three-phase converter with grid simulator. The testing parameters are 400-450V<sub>dc</sub> to 110-120V<sub>L-N</sub> with switching frequency of 80kHz. The  $LCL$  filter parameters are 45μH for  $L_{fs}$ , 12μF for  $C_f$  and 450μH for  $L_{fg}$ . C3M0021120K SiC from Cree and TMS320F28379D from TI are applied for switches and controller, respectively.

### A. State Estimation Test

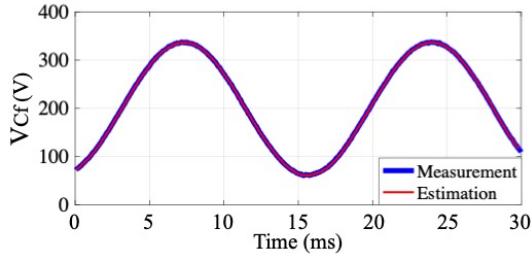

The state estimator combined with the MPC has been tested experimentally for the reduction of sensor count. Fig. 17(a), 17(b) and 17(c) show the captured ADC readings of estimation and measurement for switch side inductor current, output capacitor voltage and grid side inductor current, respectively. The switch side inductor current can be accurately estimated

TABLE I

SYSTEM PARAMETER CONFIGURATIONS

| Parameter                      | Value            |

|--------------------------------|------------------|

| Grid voltage, $V_{grid,L-N}$   | 110V-120V        |

| DC voltage, $V_{dc}$           | 400V-450V        |

| Switching frequency            | 80kHz            |

| Switch side inductor, $L_{fs}$ | 45μH             |

| Grid side inductor, $L_{fg}$   | 450μH            |

| Output Capacitor, $C_f$        | 12μF             |

| MOSFET                         | C3M0021120K      |

| Controller                     | LAUNCHXL-F28379D |

| Leakage current                | ≤ 15mA           |

TABLE II

CONTROL PARAMETERS OF DIFFERENT METHODS

|                   | Q/R | $K_p$          |

|-------------------|-----|----------------|

| PI                | n/a | 2, 20          |

| Notch filtered PI | n/a | 20             |

| MMPC              | 400 | 10, 20, 30, 40 |

(a) Switch side inductor current.

(b) Output capacitor voltage.

(c) Grid side inductor current.

Fig. 17. Comparison of the experimentally captured estimation and measurement of (a) switch side inductor current (b) output capacitor voltage and (c) grid side inductor current.

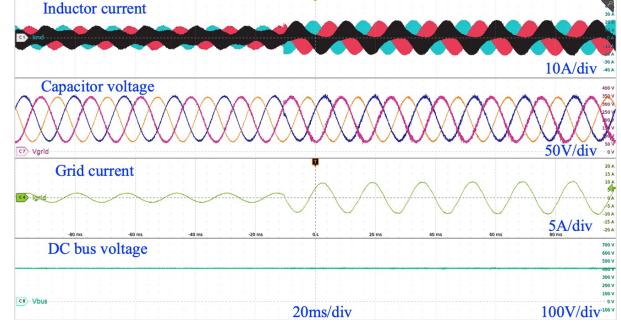

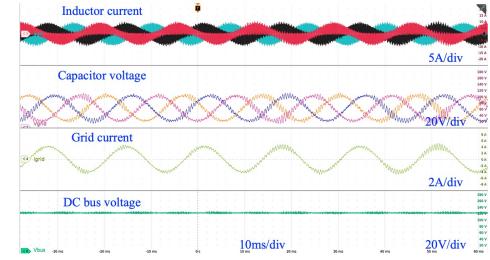

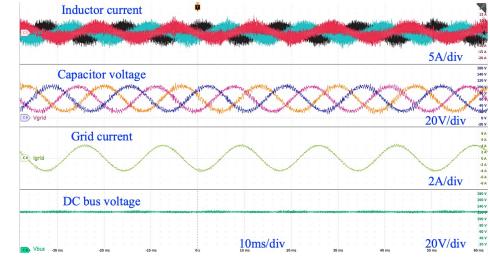

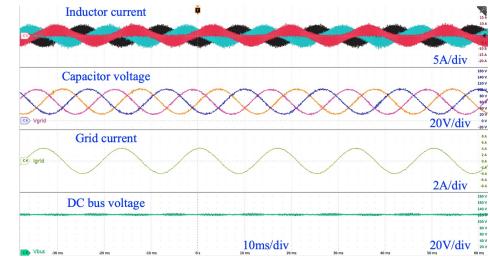

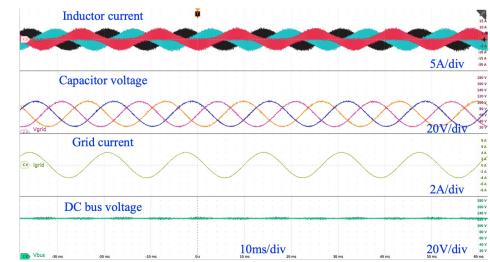

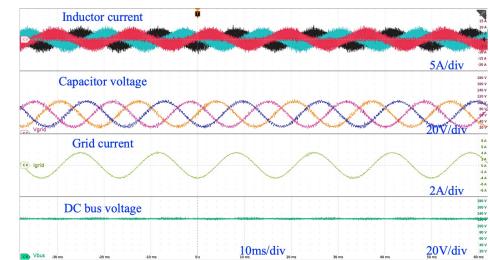

Fig. 18. Steady state waveforms of switch side inductor current, output capacitor voltage, grid side inductor current and DC bus voltage.

for MPC control purpose based on the measurement of output capacitor voltage and grid side inductor current.

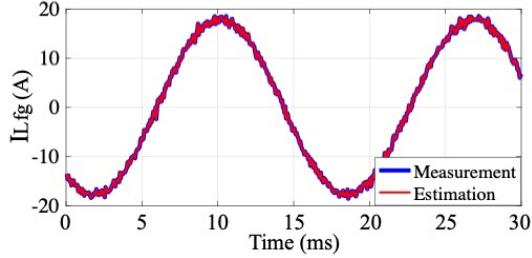

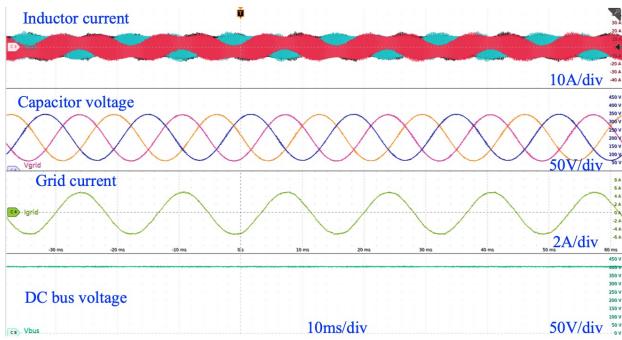

#### B. Steady State Common Mode Test

The steady state performance of the cascaded MMPC is tested experimentally to show the stabilized zero-sequence

Fig. 19. Steady state waveforms of three-phase grid voltage, leakage current, DC bus voltage and zero-sequence grid voltage.

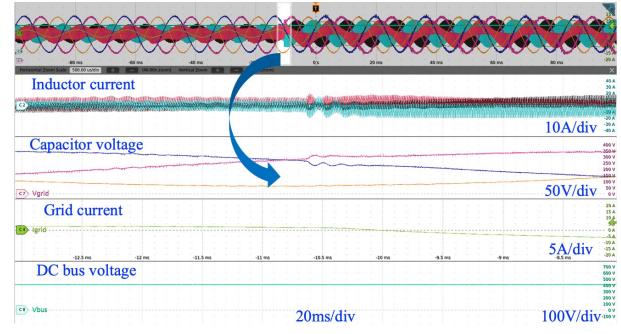

(a) Transient waveforms of  $i_{Lfg,q}$  from 3A to 10A.(b) Zoomed transient waveforms of  $i_{Lfg,q}$  from 3A to 10A.

Fig. 20. (a) Transient and (b) zoomed transient waveforms of switch side inductor current, output capacitor voltage, grid side inductor current and DC bus voltage with  $i_{Lfg,q}$  from 3A to 10A.

grid voltage and reduced leakage current. Fig. 18 shows the switch side inductor current, output capacitor voltage, grid side inductor current and DC bus voltage in steady state. The leakage current and zero-sequence grid voltage performances are shown in Fig. 19 with 450V DC bus. It can be seen from the bottom waveform that the zero-sequence grid voltage has been stabilized to be constant at half of DC bus, 225V. And the leakage current has been attenuated to be less than 15mA. Thus, the developed zero-sequence voltage MPC method is capable of reducing leakage current in the modified non-isolated  $LCL$  inverter. The standard requirements of leakage current in IEC and IET are also satisfied.

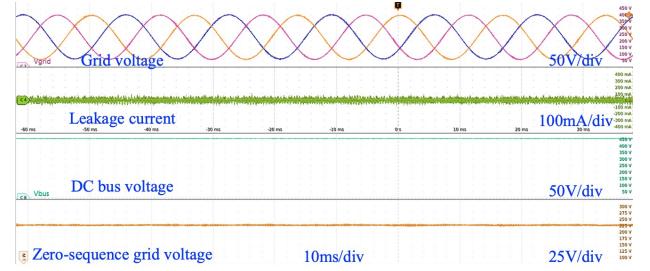

#### C. Dynamic and Stability Performance Test

The dynamic performance of the developed optimal control design method for cascaded MMPC is validated with step

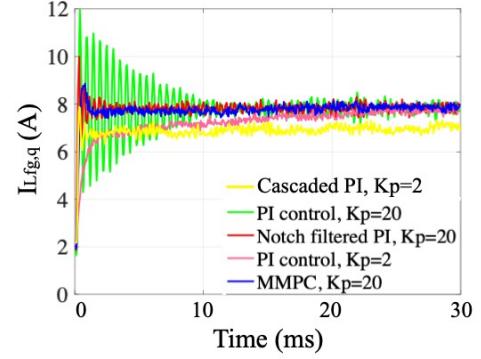

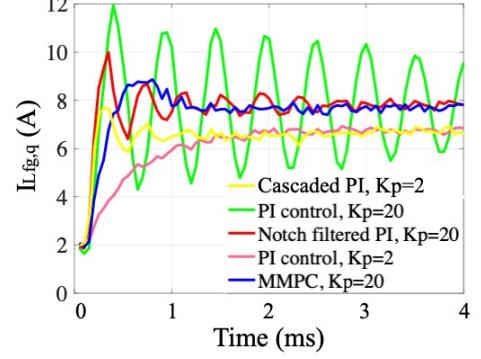

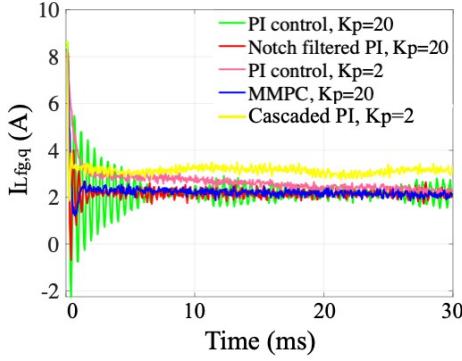

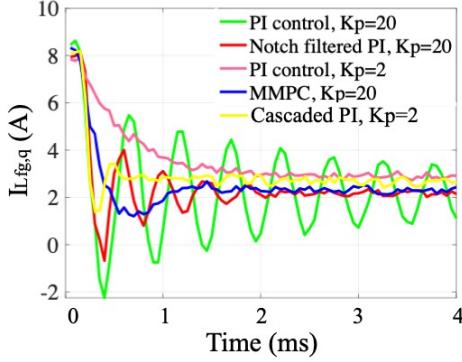

(a) MMPC transient of  $i_{Lfg,q}$  from 2A to 8A.(b) MMPC transient of  $i_{Lfg,q}$  from 8A to 2A.

Fig. 21. Cascaded MMPC transient captured ADC readings of grid side inductor current  $q$  component (a) from 2A to 8A and (b) from 8A to 2A with  $K_p$  gain of 10, 20, 30 and 40.

transient testing. Fig. 20 shows the transient waveforms of switch side inductor current, output capacitor voltage, grid side inductor current and DC bus voltage with a current step of 7A. The transient performance of control methods are evaluated by capturing the experimental ADC readings with current steps. Fig. 21(a) and Fig. 21(b) show the  $i_{Lfg,q}$  steps from 2A to 8A and 8A to 2A with different outer loop grid side inductor current control gains of 10, 20, 30 and 40, respectively. Thus, the optimal gain is selected as 20 based on the control parameter design flow chart. For the dynamic performance comparison of PI control, notch filtered PI control, cascaded MMPC and cascaded PI methods, Fig. 22 and Fig. 23 show the  $i_{Lfg,q}$  steps and zoomed waveforms from 2A to 8A and 8A to 2A under five testing cases: (1) PI control with  $K_p$  gain of 20; (2) notch filtered PI control with  $K_p$  gain of 20; (3) PI control with  $K_p$  gain of 2; (4) MMPC control with  $K_p$  gain of 20; (5) cascaded PI control with  $K_p$  gain of 2. It can be seen that the MMPC behaves more stable than either PI control or notch filtered PI control at high  $K_p$  gain of 20 with less overshoot and oscillation. Even though the PI and cascaded PI methods can act stably with a smaller  $K_p$  gain of 2, the response time is much longer than MMPC. For a more intuitional comparison, the inductor current, output capacitor voltage, grid current and DC bus voltage waveforms of these five testing cases are shown in Fig. 24(a), 24(b), 24(c), 24(d) and 24(e), respectively.

(a) Transient comparison of PI and MMPC.

(b) Zoomed transient comparison of PI and MMPC.

Fig. 22. Comparison of PI, notch filtered PI and MMPC transient captured ADC readings of (a) grid side inductor current  $q$  component from 2A to 8A and (b) zoomed waveforms.

The PI control has more oscillation than MMPC method at the same high  $K_p$  gain condition of 20. Even with the notch filter, a high  $K_p$  gain of 20 could also oscillate the waveforms with slightly less ripple than pure PI. The cascaded PI has more oscillation than PI at a low  $K_p$  of 2. The cascaded PI will diverge faster than PI method at higher  $K_p$  gain. The MMPC can operate at a  $K_p$  of 20 without oscillation and shorten the response time without the need of reducing the  $K_p$  gain as pure PI method. Thus, the experimental comparison of PI, notch filtered PI, MMPC and cascaded PI verifies that the optimal control design method for cascaded MMPC improves the dynamic performance with shorter response time, less overshoot and less oscillation. Based on the theoretical analysis in this paper, the improvements of MMPC is resulted from the inner loop MPC which has the function of active damping and attenuation of resonance in  $LCL$  filtered grid-connected inverter. The corresponding control parameters for the experiments have been summarized in table II.

#### D. Comparison with the State of Art

The proposed active damping MMPC is compared with the state of art for the grid-connected  $LCL$  inverter MPC control methods in this section. [30] proposed an observations-based FCS-MPC method with grid side inductor current sensors for balanced and unbalanced grid voltage conditions. [31]

(a) Transient comparison of PI and MMPC.

(b) Zoomed transient comparison of PI and MMPC.

Fig. 23. Comparison of PI and MMPC transient captured ADC readings of (a) grid side inductor current  $q$  component from 8A to 2A and (b) zoomed waveforms.

proposed two implementations of FCS-MPC methods to eliminate the low-order grid current harmonics and decrease the sensitivity to grid voltage distortion. [32] and [33] proposed also FCS-MPC methods to deal with the dynamic performance of grid-connected  $LCL$  inverter in  $\alpha\beta$  reference frame. The advantages of the proposed MMPC can be concluded in three aspects: (1) The computation burden is low to be implemented explicitly on a low cost DSP instead of the expensive FPGA for the above mentioned references. The proposed MMPC is implemented in per phase switch side  $LC$  of  $abc$  reference frame instead of  $dq$  or  $\alpha\beta$ . Thus, the variable of grid angular speed is not required in the state space matrix and the order of the per phase  $LC$  state space matrix is lower. The execution time for MMPC is within  $4\mu\text{s}$  at each control interrupt. (2) The proposed MMPC is combined with the modified inverter topology to stabilized the zero-sequence voltage and attenuate the leakage current. This function enables the non-isolated converter applications to satisfy the grid-connection standard requirements for common mode behavior. (3) The size of offline generated piecewise affine function C code file is small to be fit into the DSP controller. Since the MMPC is implemented for per phase  $LC$  in  $abc$  reference frame, the explicit solver function is largely simplified and the C file is within 5KB. This size could be easily fit into the DSP memory.

(a) PI control with  $K_p$  of 20.(b) Notch filtered PI control with  $K_p$  of 20.(c) PI control with  $K_p$  of 2.(d) MMPC control with  $K_p$  of 20.(e) Cascaded PI control with  $K_p$  of 2.

Fig. 24. Waveforms comparison of inductor current, output capacitor voltage, grid current and DC bus voltage for (a) PI control with  $K_p$  of 20 (b) notch filtered PI control with  $K_p$  of 20 (c) PI control with  $K_p$  of 2 (d) MMPC control with  $K_p$  of 20 and (e) cascaded PI control with  $K_p$  of 2.

## VI. CONCLUSION

This paper develops an optimal control design method for resonance damping and dynamic performance improvement of cascaded modular model predictive control for a modified grid-connected *LCL* inverter. The *LCL* system is modeled to show the intrinsic resonance issue. Also, the common mode circuit is analyzed for the modified non-isolated grid-connected inverter to manifest the leakage current bypassing and zero-sequence voltage stabilization functions. Three control strategies, including PI control, notch filtered PI control and cascaded MMPC, are studied with zero-sequence stabilization capabilities to explore the dynamic and stability performance. The cascaded MMPC is validated to have the active damping function by inserting an inner loop MPC cascaded with outer loop PI control. This cascaded control structure is capable of damping the resonance and increasing the control bandwidth to improve the system dynamic performance. A control parameter design method is finally proposed for the cascaded MMPC to derive the optimal weighing factor and gain. The experiments have validated the proposed method.

## VII. ACKNOWLEDGEMENT

This research is based in part upon work supported by National Science Foundation under Grant Number 1653574.

## REFERENCES

- [1] T. F. Wu, M. Misra, L. C. Lin, and C. W. Hsu, "An improved resonant frequency based systematic LCL filter design method for grid-connected inverter," *IEEE Transactions on Industrial Electronics*, vol. 64, no. 8, pp. 6412–6421, 2017.

- [2] Y. Tang, W. Yao, P. C. Loh, and F. Blaabjerg, "Design of LCL Filters with LCL Resonance Frequencies beyond the Nyquist Frequency for Grid-Connected Converters," *IEEE Journal of Emerging and Selected Topics in Power Electronics*, vol. 4, no. 1, pp. 3–14, 2016.

- [3] E. Rodriguez-Diaz, F. D. Freijedo, J. C. Vasquez, and J. M. Guerrero, "Analysis and Comparison of Notch Filter and Capacitor Voltage Feedforward Active Damping Techniques for LCL Grid-Connected Converters," *IEEE Transactions on Power Electronics*, vol. 34, no. 4, pp. 3958–3972, 2019.

- [4] R. A. Fantino, C. A. Busada, and J. A. Solsona, "Optimum PR Control Applied to LCL Filters with Low Resonance Frequency," *IEEE Transactions on Power Electronics*, vol. 33, no. 1, pp. 793–801, 2018.

- [5] F. Chen, R. Burgos, and D. Boroyevich, "A Bidirectional High-Efficiency Transformerless Converter with Common-Mode Decoupling for the Interconnection of AC and DC Grids," *IEEE Transactions on Power Electronics*, vol. 34, no. 2, pp. 1317–1333, 2019.

- [6] W. Yao, Y. Yang, X. Zhang, F. Blaabjerg, and P. C. Loh, "Design and Analysis of Robust Active Damping for LCL Filters Using Digital Notch Filters," *IEEE Transactions on Power Electronics*, vol. 32, no. 3, pp. 2360–2375, 2017.

- [7] J. Fang, G. Xiao, X. Yang, and Y. Tang, "Parameter Design of a Novel Series-Parallel-Resonant LCL Filter for Single-Phase Half-Bridge Active Power Filters," *IEEE Transactions on Power Electronics*, vol. 32, no. 1, pp. 200–217, 2017.

- [8] H. T. Nguyen and J. W. Jung, "Finite control set model predictive control to guarantee stability and robustness for surface-mounted PM synchronous motors," *IEEE Transactions on Industrial Electronics*, vol. 65, no. 11, pp. 8510–8519, 2018.

- [9] S. R. Mohapatra and V. Agarwal, "Model Predictive Controller With Reduced Complexity for Grid-Tied Multilevel Inverters," *IEEE Transactions on Industrial Electronics*, vol. 66, no. 11, pp. 8851–8855, 2019.

- [10] S. C. Ferreira, R. B. Gonzatti, R. R. Pereira, C. H. Da Silva, L. E. Da Silva, and G. Lambert-Torres, "Finite control set model predictive control for dynamic reactive power compensation with hybrid active power filters," *IEEE Transactions on Industrial Electronics*, vol. 65, no. 3, pp. 2608–2617, 2018.

- [11] C. Xue, L. Ding, H. Tian, and Y. Li, "Multi-rate Finite-Control-Set Model Predictive Control for High Switching Frequency Power Converters," *IEEE Transactions on Industrial Electronics*, vol. 0046, no. c, pp. 1–11, 2021.

- [12] R. Peña-Alzola, M. Liserre, F. Blaabjerg, M. Ordonez, and Y. Yang, "LCL-filter design for robust active damping in grid-connected converters," *IEEE Transactions on Industrial Informatics*, vol. 10, no. 4, pp. 2192–2203, 2014.

- [13] T. Liu, J. Liu, Z. Liu, and Z. Liu, "A study of virtual resistor-based active damping alternatives for LCL resonance in grid-connected voltage source inverters," *IEEE Transactions on Power Electronics*, vol. 35, no. 1, pp. 247–262, 2020.

- [14] A. Hintz, U. R. Prasanna, and K. Rajashekara, "Comparative study of the three-phase grid-connected inverter sharing unbalanced three-phase and/or single-phase systems," *IEEE Transactions on Industry Applications*, vol. 52, no. 6, pp. 5156–5164, 2016.

- [15] H. Ayano, K. Murakami, and Y. Matsui, "A novel technique for reducing leakage current by application of zero-sequence voltage," *IEEE Transactions on Industry Applications*, vol. 51, no. 4, pp. 3094–3100, 2015.

- [16] S.-J. Chee, S. Ko, H.-S. Kim, and S.-K. Sul, "Common-mode voltage reduction of three-level four-leg pwm converter," *IEEE Transactions on Industry Applications*, vol. 51, no. 5, pp. 4006–4016, 2015.

- [17] X. Guo, R. He, J. Jian, Z. Lu, X. Sun, and J. M. Guerrero, "Leakage current elimination of four-leg inverter for transformerless three-phase pv systems," *IEEE Transactions on Power Electronics*, vol. 31, no. 3, pp. 1841–1846, 2016.

- [18] G. Shen, D. Xu, L. Cao, and X. Zhu, "An improved control strategy for grid-connected voltage source inverters with an LCL filter," *IEEE Transactions on Power Electronics*, vol. 23, no. 4, pp. 1899–1906, 2008.

- [19] M. Castilla, J. Miret, and H. Mart, "Variable Structure Control in Natural," *Eee Transactions on Power Electronics*, vol. 33, no. 5, pp. 4512–4522, 2018.

- [20] D. Pan, X. Ruan, X. Wang, H. Yu, and Z. Xing, "Analysis and Design of Current Control Schemes for LCL-Type Grid-Connected Inverter Based on a General Mathematical Model," *IEEE Transactions on Power Electronics*, vol. 32, no. 6, pp. 4395–4410, 2017.

- [21] Z. Xin, P. Mattavelli, W. Yao, Y. Yang, F. Blaabjerg, and P. C. Loh, "Mitigation of Grid-Current Distortion for LCL-Filtered Voltage-Source Inverter with Inverter-Current Feedback Control," *IEEE Transactions on Power Electronics*, vol. 33, no. 7, pp. 6248–6261, 2018.

- [22] L. Zhou, F. Gao, and T. Xu, "Implementation of Active NPC Circuits in Transformer-Less Single-Phase Inverter With Low Leakage Current," *IEEE Transactions on Industry Applications*, vol. 53, no. 6, pp. 5658–5667, 2017.

- [23] L. Zhang, K. Sun, Y. Xing, and M. Xing, "H6 transformerless full-bridge PV grid-tied inverters," *IEEE Transactions on Power Electronics*, vol. 29, no. 3, pp. 1229–1238, 2014.

- [24] B. Yang, W. Li, Y. Gu, W. Cui, and X. He, "Improved transformerless inverter with common-mode leakage current elimination for a photovoltaic grid-connected power system," *IEEE Transactions on Power Electronics*, vol. 27, no. 2, pp. 752–762, 2012.

- [25] H. Akagi and S. Tamura, "A passive EMI filter for eliminating both bearing current and ground leakage current from an inverter-driven motor," *IEEE Transactions on Power Electronics*, vol. 21, no. 5, pp. 1459–1468, 2006.

- [26] M. G. Judewicz, S. A. Gonzalez, J. R. Fischer, J. F. Martinez, and D. O. Carrica, "Inverter-side current control of grid-connected voltage source inverters with LCL filter based on generalized predictive control," *IEEE Journal of Emerging and Selected Topics in Power Electronics*, vol. 6, no. 4, pp. 1732–1743, 2018.

- [27] A. Bemporad, F. Borrelli, and M. Morari, "Model predictive control based on linear programming - The explicit solution," *IEEE Transactions on Automatic Control*, vol. 47, no. 12, pp. 1974–1985, 2002.

- [28] R. Guzman, L. Garcia De Vicuna, J. Morales, M. Castilla, and J. Miret, "Model-Based Active Damping Control for Three-Phase Voltage Source Inverters with LCL Filter," *IEEE Transactions on Power Electronics*, vol. 32, no. 7, pp. 5637–5650, 2017.

- [29] J. Böcker, B. Freudenberg, A. The, and S. Dieckerhoff, "Experimental comparison of model predictive control and cascaded control of the modular multilevel converter," *IEEE Transactions on Power Electronics*, vol. 30, no. 1, pp. 422–430, 2015.

- [30] X. Chen, W. Wu, N. Gao, H. S.-H. Chung, M. Liserre, and F. Blaabjerg, "Finite control set model predictive control for lcl-filtered grid-tied inverter with minimum sensors," *IEEE Transactions on Industrial Electronics*, vol. 67, no. 12, pp. 9980–9990, 2020.

- [31] P. Falkowski and A. Sikorski, "Finite control set model predictive control for grid-connected ac–dc converters with lcl filter," *IEEE Transactions on Industrial Electronics*, vol. 65, no. 4, pp. 2844–2852, 2018.

- [32] T. Dragičević, C. Zheng, J. Rodriguez, and F. Blaabjerg, "Robust quasi-predictive control of  $lcl$ -filtered grid converters," *IEEE Transactions on Power Electronics*, vol. 35, no. 2, pp. 1934–1946, 2020.

- [33] T. Dragičević, "Model predictive control of power converters for robust and fast operation of ac microgrids," *IEEE Transactions on Power Electronics*, vol. 33, no. 7, pp. 6304–6317, 2018.

**Liwei Zhou** (S'15) received the B.E. and the M.E., both in Electrical Engineering, from Shandong University, Jinan, China in 2014 and 2017, respectively. He is currently working toward the Ph.D. degree in Motor Drives and Power Electronics Laboratory (MPLab), Columbia University, New York City, NY, USA. Since 2017, he has been a Graduate Research Assistant with MPLab. His current research interests include soft-switching techniques for modular power converter, model predictive control and other advanced control technologies, grid-connected converter and EV battery charging control, inductor design. He received the IEEE Energy Conversion Congress & Expo, 2018 Student Travel Award. He is also the co-recipient of the Best Student Paper Award of the IEEE Transportation Electrification Conference and Expo (ITEC), 2021.

**Matthias Preindl** (S'12-M'15-SM'18) received the B.Sc. degree in electrical engineering (*summa cum laude*) from the University of Padua, Italy, the M.Sc. degree in electrical engineering and information technology from ETH Zurich, Switzerland, and the Ph.D. degree in energy engineering from the University of Padua, in 2008, 2010, and 2014, respectively. He is currently Associate Professor of Power Electronic Systems in the Department of Electrical Engineering at Columbia University, USA. Prior to joining Columbia University in 2016, he was an R&D Engineer of Power Electronics and Drives at Leitwind AG, Italy (2010-2012), a Post Doctoral Research Associate with the McMaster Institute for Automotive Research and Technology, McMaster University, Hamilton, ON, Canada (2014-2015), and a Sessional Professor in the Department of Electrical and Computer Engineering, McMaster University (2015). He serves as the area editor of vehicular electronics and systems at the IEEE Transactions on Vehicular Technology and as the general chair of the 2022 IEEE/AIAA ITEC+EATS. He received several awards and honors including the Horiba Awards Honorable Mention (Japan, 2019), the Futura Foundation Award (Italy, 2017), the NSF CAREER Award (USA, 2017), and he is the co-recipient of several best paper and presentation recognitions including the 2019 IEEE Transactions on Industrial Electronics best paper award.