# Insertion Loss Reduction Using Rounded Corners to Mitigate Surface Roughness Effect in PCB Transmission Lines

Yuandong Guo<sup>1#</sup>, DongHyun Kim<sup>2#</sup>, Yuanzhuo Liu<sup>3#</sup>, Xiaoning Ye<sup>4\*</sup>, Jimmy Hsu<sup>5</sup>^, and Jun Fan<sup>6#</sup>

\*Datacenter Group, Intel Corporation, Portland, Oregon, USA

^Datacenter Group, Intel Corporation, Taipei, Taiwan

\*xiaoning.ye, 5jimmy.hsu@intel.com

Abstract—Signal integrity (SI) can be interpreted as a measure of the distortion of the incident pulse, which is attributed to various contributors, e.g., inter-symbol interference (ISI), crosstalk, jitter, etc. The channel insertion loss is generally the most critical concern in SI designs, since it determines the working bandwidth of a high-speed channel, and the bandlimited channels are known as the root cause of ISI. At the tens of Gigabit rates in use today, PCB transmission lines may have appreciable losses, which can be divided into frequencydependent dielectric loss and conductor loss, and noticeable amount of losses can be generated at high-frequencies due to the skin effect and copper rough surfaces. In order to reduce the additional conductor loss due to the surface roughness, the employment of low-profile copper foils is a common practice in high-speed digital design. However, this existing method is not cost-effective. In this paper, insertion loss reduction using rounded corners are proposed and verified using both 2D and 3D full-wave simulations for the first time. Rounded corners can mitigate the increased insertion loss due to copper surface roughness in PCB transmission lines, and can be applied in highspeed interconnect designs to increase eye margins. The impact of applying rounded corners on far-end crosstalk is also discussed.

Keywords—conductor loss; channel loss; dielectric loss; farend crosstalk; insertion loss; rounded corner; surface roughness; transmission line.

## I. INTRODUCTION

Signal integrity (SI) can be described as simple as the study of incident pulse distortion [1], which can be further attributed to multiple contributors, for instance, inter-symbol interference (ISI) [2], crosstalk [3]-[6], jitter [2], etc. The frequency-dependent insertion loss of a high-speed channel determines the working bandwidth, and a bandlimited channel is unwanted in SI designs since it may cause severe ISI issues and introduce a closed eye at the receiver end [7].

The total channel losses can be divided into dielectric and conductor loss, both of which also demonstrate strong frequency dependency [8][9]. It is known that there is

This work is supported in part by the National Science Foundation under Grant No. IIP-1916535.

additional conductor loss at high frequencies resulted from the rough copper surfaces [10][11]. At the tens of Gigabit rates in use today, channel loss has already become the bottleneck for high-bandwidth and high-data-rate applications.

In order to reduce the channel loss for high-speed data transition, it is currently a common practice in industries to employ low-loss (or even ultra-low-loss) dielectrics and low-profile copper foils. However, these materials are expensive, making the associated design not cost-effective during the high-volume production.

In this paper, insertion loss reduction using "rounded corners" is proposed and verified using both 2D and 3D full-wave simulations. The real testing coupons are under manufacturing, and the measurement-based validations will be reported in future publications. The rounded corners can reduce the increased conductor loss due to copper surface roughness, and we observed more than 10% improvement in the comparison of total insertion loss at 20 GHz. We expect to see more reduction at higher frequencies according to the trends in the comparisons.

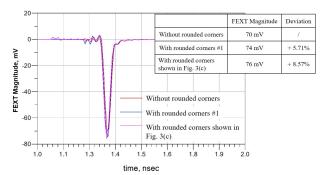

Since the cross-section of a transmission line is changed after applying the rounded corners, the influence on far-end crosstalk (FEXT) is also investigated. It is found that the resulting FEXT may increase by approximately 8% based upon the simulated data, which may necessitate the implementation of FEXT noise mitigation technique described in [3] and [6] in both design and manufacturing phases.

The motivation of introducing rounded corners to PCB transmission lines and various current density distributions are illustrated in Section II. The 3D simulation-based verification is shown in detail in Section III. The impact of applying rounded corners on FEXT is briefly discussed through simulation-based studies in Section IV. Section V concludes the paper.

# II. DISTRIBUTION OF CURRENT DENSITY

The high-frequency currents only flow on the "skin" of a conductor, which is known as the skin effect [2], resulting in

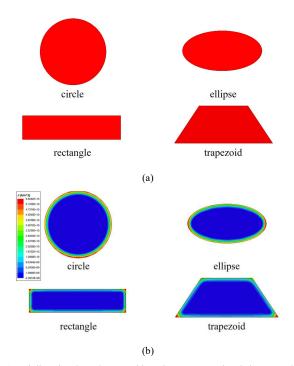

larger AC resistance and conductor loss. Edge effect is another inherent characteristic of eddy current [12]. In order to reveal the impacts of these two effects, several stripline models are constructed in ANSYS Q2D, each of which contains a single-ended signal trace with a different cross-sectional shape, as indicated in Fig. 1(a). All these 2D models adopt the same material properties and smooth coppers, and their characteristic impedance are identical. The complex dielectric constant and geometrical parameters can be found in [13].

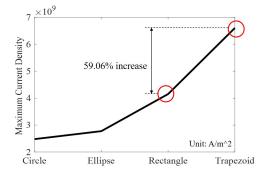

Fig. 1(b) compares the distributions of current density in each 2D model, implying that the current tends to be concentrated at the sharp corners due to the skin and edge effects. The maximum current density obtained from the simulations are plotted in Fig. 2, where a noticeable increase in current density is observed when the signal conductor's cross-section switches from rectangle to trapezoid.

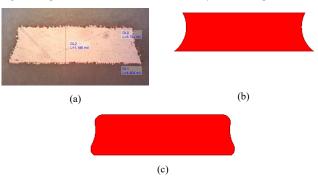

The real cross-section of a PCB stripline trace is given in Fig. 3(a), which is mimicked by using the sketch in Fig. 3(b) in the 2D simulation. It is anticipated that the maximum current density is higher than that of the "trapezoid" case in Fig. 1(b), given that the edges in Fig. 3(b) are sharper. The proposed trace cross-sectional shape with rounded corners is demonstrated in Fig. 3(c).

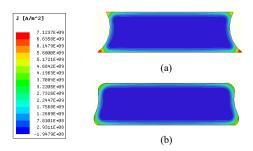

The simulated current density distributions before and after applying the rounded corners are shown in Fig. 4, where it is found evident that rounding the sharp edges can significantly change the current density distribution.

## III. VERIFICATION OF INSERTION LOSS REDUCTION

The frequency-dependent per-unit-length (P.U.L.) resistance and inductance values are obtained through the 2D simulations. The comparison of P.U.L. resistance is exhibited in Fig. 5(a), where an approximate 22% reduction can be identified at around 20 GHz.

The conductor loss  $\alpha_c$  can be calculated using [12]

$$\alpha_c \approx 0.5R / \sqrt{Z_0} \tag{1}$$

where the characteristic impedance  $Z_0 \approx \sqrt{L/C}$ . Fig. 5(b) illustrates the improvement in conductor loss after implementing the rounded corners, and the reduction at 20 GHz is about 20%.

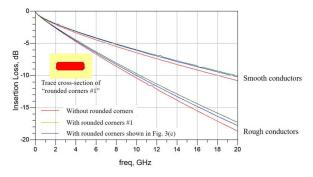

The full-wave simulations are performed in ANSYS HFSS, and the Huray surface roughness model [14] is utilized in order to reveal the impact of rounded corners on total insertion loss. In addition to the trace cross-section with rounded corners in Fig. 3(c), one more trace with larger curvatures around the corners is simulated, and the result is included in the comparison in Fig. 6, where the insertion loss reduction at 20 GHz by using the rounded corners in the "rough conductor" cases is pinpointed to be about 11%, and the insertion loss curves may indicate that more reduction in percentage can be expected at higher frequencies. This will be verified through measurement-based studies and reported in future publications.

Fig. 1. Stripline signal conductors with various cross-sectional shapes are built in ANSYS Q2D to reveal the distribution of current density due to edge and skin effects: (a) cross-sections of different signal conductors in 2D stripline models, (b) the distributions of current density in each model indicating the current tends to be concentrated at the sharp corners.

Fig. 2. Comparison of the maximum current density for each shape.

Fig. 3. The cross-section of PCB signal traces: (a) a signal trace of real PCB stripline, (b) 2D cross-section of modeled PCB trace without rounded corners, (c) 2D cross-section of modeled PCB trace with rounded corners.

Fig. 4. The simulated current density distributions: (a) baseline case, before applying rounded corners, (b) after applying rounded corners.

(b)

Fig. 5. Comparison of P.U.L. resistance and conductor loss: (a) P.U.L. resistance comparison, (b) conductor loss comparison.

10

Frequency, GHz

15

20

-2.5

0

Fig. 6. Comparisons of insertion loss for both "smooth conductor" and "rough conductor" cases.

# IV. THE INFLUENCE ON FEXT

The influence of rounded corners on PCB stripline FEXT is examined through 2D simulations, and the results are manifested in Fig. 7. The maximum increase in the time

Fig. 7. Comparison of FEXT magnitudes in the time domain after implementing the rounded corners.

domain FEXT after applying the rounded corners is 8.57%, which can be readily mitigated using certain FEXT noise cancellation techniques.

#### V. CONCLUSION

Insertion loss reduction using rounded corners is proposed and verified through the full-wave simulation-based studies in this paper. About 20% reduction in the conductor loss and approximately 11% decrease in the total insertion loss are identified. The downside of using the rounded corners is the slight increase in FEXT magnitude, which can be overcome by employing the FEXT noise cancelation techniques.

## REFERENCES

- [1] "Signal integrity basics," by Anritsu Field Application Engineers.

Available at: <a href="https://dl.cdn-anritsu.com/en-us/test-measurement/files/Technical-Notes/White-Paper/Signal IntegrityWP.pdf">https://dl.cdn-anritsu.com/en-us/test-measurement/files/Technical-Notes/White-Paper/Signal IntegrityWP.pdf</a>.

- [2] S. Hall, and H. Heck, Advanced Signal Integrity for High-Speed Digital Designs. John Wiley & Sons, Inc., 2009.

- [3] Y. Liu et al., "Far-End Crosstalk Analysis for Stripline with Inhomogeneous Dielectric Layers (IDL)," 2021 IEEE International Joint EMC/SI/PI and EMC Europe Symposium, 2021, pp. 825-830.

- [4] Y. Guo et al., "Robust Extended Unterminated Line (EUL) Crosstalk Characterization Techniques for High-Speed Interconnect," 2020 IEEE International Symposium on Electromagnetic Compatibility & Signal/Power Integrity (EMCSI), 2020, pp. 155-157.

- [5] Y. Guo, S. Jin, X. Sun and J. Fan, "Noise Coupling Mechanism Analysis and Mitigation Method for Receiver Sensitivity Improvement in an Optical QSFP Transceiver Module," 2020 IEEE International Symposium on Electromagnetic Compatibility & Signal/Power Integrity (EMCSI), 2020, pp. 502-506.

- [6] Y. Guo et al., "Far-End Crosstalk Control Strategy for High-Volume High-Speed PCB Manufacturing: The Concept of Critical Resin Content Percent," 2021 IEEE International Joint EMC/SI/PI and EMC Europe Symposium, 2021, pp. 820-824.

- [7] C. Paul, Analysis of Multiconductor Transmission Lines, 2<sup>nd</sup> Edition. John Wiley & Sons, Inc., 2008.

- [8] Y. Guo, B. Chen, X. Sun, X. Ye, J. Hsu and J. Fan, "Study of TDR Impedance for Better Analysis to Measurement Correlation," 2019 Joint International Symposium on Electromagnetic Compatibility, Sapporo and Asia-Pacific International Symposium on Electromagnetic Compatibility (EMC Sapporo/APEMC), 2019, pp. 88-91.

- [9] Y. Guo et al., "The Simulated TDR Impedance In PCB Material Characterization," 2021 IEEE International Joint EMC/SI/PI and EMC Europe Symposium, 2021, pp. 831-834.

- [10] X. Sun et al., "Causality Analyzing for Transmission Line with Surface Roughness," 2019 IEEE International Symposium on Electromagnetic

- Compatibility, Signal & Power Integrity (EMC+SIPI), 2019, pp. 516-521.

- [11] S. Yong et al., "A Cross-sectional Profile Based Model for Stripline Conductor Surface Roughness," 2020 IEEE International Symposium on Electromagnetic Compatibility & Signal/Power Integrity (EMCSI), 2020, pp. 334-339.

- [12] D. Pozar, Microwave Engineering, 4th Edition. John Wiley & Sons, Inc., 2012.

- [13] Y. Guo et al., "Limitations of First-Order Surface Impedance Boundary Condition and Its Effect on 2D Simulations for PCB Transmission Lines," 2020 IEEE International Symposium on Electromagnetic Compatibility & Signal/Power Integrity (EMCSI), 2020, pp. 422-427.

- [14] J. E. Bracken, "A causal Huray model for surface roughness," DesignCon 2012, Santa Clara, CA, USA, 2012.