Date of publication xxxx 00, 0000, date of current version xxxx 00, 0000.

Digital Object Identifier 10.1109/TQE.2022.Doi Number

# A High-Resolution Single-Photon Arrival-Time Measurement with Self-Antithetic Variance Reduction in Quantum Applications: Theoretical Analysis and Performance Estimation

Tony Wu (Graduate Student Member, IEEE) and Tzu-Chien Hsueh (Senior Member, IEEE)

Department of Electrical and Computer Engineering, University of California, San Diego, La Jolla, CA 92093, USA

Corresponding author: Tzu-Chien Hsueh (email: tzhsueh@eng.ucsd.edu)

This work was supported by the National Science Foundation under Award 2045935.

**ABSTRACT** An almost all-digital time-to-digital converter (TDC) possessing sub-picosecond resolutions, scalable dynamic ranges, high linearity, high noise-immunity, and moderate conversion-rates can be achieved by a random sampling-and-averaging (RSA) approach with the self-antithetic variance reduction (SAVR) technique for time-correlated single-photon counting (TCSPC) quantum measurements. This paper presents detailed theoretical analysis and behavior-model verifications of the SAVR technique to effectively enhance the conversion-rate of an asynchronous RSA-based TDC by more than 62× with 7% power overhead. In addition, the proposed performance estimation methodology for SAVR can greatly improve the computation efficiency during the system-level design and reduce the read-out circuit complexity in the silicon-photonics RSA-based TCSPC realization.

**INDEX TERMS** Antithetic variate, correlated random variable, joint probability density function, Monte Carlo method, quantum probability amplitude, single-photon counting, stochastic random sampling, time-domain modulo operation, time-to-digital converter, variance reduction.

### I. INTRODUCTION

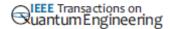

Time-correlated single-photon counting (TCSPC) [1]–[5] has become the key functionality in a variety of emerging quantum technology, including quantum imaging/sensing [6]-[8], quantum-state preparations [9]–[12], quantum cryptography [13]–[15], positron emission tomography (PET) [16], [17], time-resolved spectroscopy [18], fluorescence-lifetime imaging (FLIM) [19], [20], molecular imaging, live-cell/tissue microscopy free-space time-of-flight [2], measurements [21], and light detection-and-ranging (LiDAR) [6], [22]. One example of quantum-state detections shown in Fig. 1 exploits TCSPC to measure the quantum state of a light beam, which is a "vector" but very different from the vector defined in classical physics. Under the Dirac notation, a normalized quantum state,  $|\psi\rangle$ , can be expressed by the superposition of the horizontal polarization-basis vector, |H\>, and vertical polarization-basis vector,  $|V\rangle$ , in the Hilbert space [10]:

$$|\psi\rangle = c_H \cdot |H\rangle + c_V \cdot |V\rangle, \quad |c_H|^2 + |c_V|^2 = 1$$

(1)

where  $c_H$  and  $c_V$  are complex coefficients, and the sum of their squared magnitudes is "1" in this orthonormal basis state-expression. More importantly,  $c_H$  and  $c_V$  are referred to as complex probability amplitudes of the polarization-basis vectors,  $|H\rangle$  and  $|V\rangle$ , respectively. The physical meaning of these coefficients is that the squared magnitude of the coefficient, multiplying a particular polarization-basis vector, is equal to the probability of photons occurring in that polarization after many single-photon measurements, which can be performed by the apparatus with TCSPC shown in Fig. 1(a); whenever TCSPC<sub>H</sub> receives a single photon from the  $|H\rangle$  output of the light polarizer at a certain time of  $\Delta t_H$ , the circuit in TCSPC<sub>H</sub> adds a one on the accumulated number,  $N_H(\Delta t_H)$  and records the quantized  $\Delta t_H$ , i.e., a time-to-digital conversion (TDC) process, for the received photon. Similarly, TCSPC<sub>V</sub>

accumulates  $N_V(\Delta t_V)$  and records the quantized  $\Delta t_V$  for the received photons from the  $|V\rangle$  output of the light polarizer. Thus, the probability of the photon in each polarization can be obtained as follows:

$$P(H||\psi\rangle) = |c_H|^2 = \frac{N_H(\Delta t_H)}{N_H(\Delta t_H) + N_V(\Delta t_V)}$$

$$P(V||\psi\rangle) = |c_V|^2 = \frac{N_V(\Delta t_V)}{N_H(\Delta t_H) + N_V(\Delta t_V)}$$

(2)

Note that the notations of the probabilities are conditioned on the measured quantum state,  $|\psi\rangle$ . Meanwhile, since the quantum state is not affected by the reference phase of its complex coefficients, usually the phase of  $c_H$  can be safely set to zero, and the phase of  $c_V$ ,  $\phi$ , can be obtained by performing two more quantum-state measurements as shown in Fig. 1(b) and 1(c):

$$P(+45||\psi\rangle) = \frac{1}{2} + |c_{H}| \cdot |c_{V}| \cdot cos\phi$$

$$= \frac{N_{+45}(\Delta t_{+45})}{N_{-45}(\Delta t_{-45}) + N_{+45}(\Delta t_{+45})}$$

$$P(L||\psi\rangle) = \frac{1}{2} + |c_{H}| \cdot |c_{V}| \cdot sin\phi$$

$$= \frac{N_{L}(\Delta t_{L})}{N_{L}(\Delta t_{L}) + N_{R}(\Delta t_{R})}$$

(3)

where  $(|-45\rangle, |+45\rangle)$  and  $(|L\rangle, |R\rangle)$  are the other two pairs of the orthonormal polarization-basis vectors. With these three conditional probability measurements, the complex probability amplitudes,  $c_H$  and  $c_V$ , of the quantum state can be fully determined from (2) and (3) [11]. In other words, the probability measurements performed by the TCSPC system are essential in order to determine a quantum state.

Consequently, the TDC specifications in the TCSPC systems are required to achieve pico-seconds fine resolutions, sub-micro-seconds dynamic ranges, high linearity and fast conversion-rates under aggressive silicon-area, voltage, and power constraints of modern CMOS integrated-circuit process technology. The state-of-the-art TDC designs can satisfy some of these specifications, however, with trade-offs among the other performance metrics [1]-[4], [6]-[8], [16]-[44]. To simultaneously accommodate all performance requirements for the majority of quantum applications, a TCSPC system proposed in [45] incorporates the digital random samplingand-averaging (RSA) technique [46]-[49] into a two-step TDC procedure to enable high-resolution time-interval measurements without compromising the performance metrics among accuracy, dynamic range, linearity, and power/area efficiency. However, the slow conversion-rate of the RSA technique has greatly limited the broadness of its applications especially for high frame-rate/fill-factor quantum imaging and ranging systems [6]-[8], [16]-[22]. Fortunately, there is a concept of variance reduction (VR) which has been broadly used in the fields of applied mathematics and financial

FIGURE 1. Three quantum-state measurements using TCSPC for the orthonormal polarization-basis vectors of (a)  $|H\rangle$  and  $|V\rangle$ ; (b)  $|-45\rangle$  and  $|+45\rangle$ ; (c)  $|L\rangle$  and  $|R\rangle$ .

engineering [51], [52] to reduce time consumption of the Monte Carlo methods in derivatives pricing and risk management [52]. Based on the similar concept, this paper proposes a simple circuit implementation for the self-antithetic variance reduction (SAVR) technique [50] to effectively suppress the quantization-noise power or equivalently enhance the conversion-rate of an asynchronous RSA-based TCSPC system by automatically introducing auto-correlations into the sampled random variable during the TDC process.

To comprehensively describe a practical RSA measurement with the SAVR technique, this paper derives the mathematical expressions of the theoretical variance and its approximation form for highly efficient performance-predictions, which are all experimentally verified by the simulations. Meanwhile, the methodology of converting the mathematical models of the RSA with SAVR technique into an almost all-digital and low-power implementation is elaborated by a circuit-level example with a guideline of setting the circuit parameters. Compared to an ordinary RSA measurement [45], enabling the SAVR technique can enhance the conversion-rate by more than 62× with about 7% power overhead based on the simulation results.

The remainder of the paper is organized as follows. The circuit-and-system level overview of an RSA-based TCSPC system with the SAVR technique is introduced in Section II. The required fundamentals of RSA and parameter definitions are summarized in Section III. The probability principles, theoretical variances, performance estimation methodology, and behavior-model simulations of the RSA with SAVR technique are derived and presented in Section IV. The conclusion and future work are summarized in Section V.

### **II. CIRCUIT AND SYSTEM OVERVIEW**

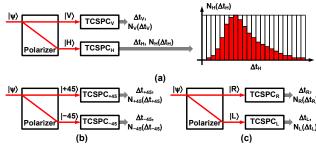

The block diagram of the RSA-based TCSPC system with the SAVR techniques is shown in Fig. 2(a). The silicon-photonics interface is similar to the system described in [45], where each detection pixel includes a single-photon avalanche diode (SPAD) with the quenching/clamping circuits [3], [6]–[8] for the optical-to-electrical power domain transition followed by a silicon-photonics analog front-end (AFE) [53] and high-bandwidth CMOS pulse generator to convert the received single photons to event-triggered electrical voltage pulses. For the high-accuracy

FIGURE 2. (a) The block diagram of the RSA-based TCSPC system with the SAVR technique. (b) The circuit and reconfigurabilities of the DCO for enabling SAVR with low power overhead.

time-interval measurement, the timing of  $T_{START}$  is set by the START pulse from a specific single-photon detection pixel [2] while the multiplexer for the STOP pulse can select the timing of  $T_{STOP}$  from either the other specific single-photon detection pixel [2] or the system input clock,  $CK_{IN}$ , [3], [4], [6]–[8]. In any configuration, the time-interval,  $\Delta t$ , between  $T_{START}$  and  $T_{STOP}$  is the primary quantity under the measurement as shown in Fig. 2(a). The time-to-amplitude conversion (TAC) circuit, containing a current source and capacitor banks with low-resolution static controls for coarse dynamic-range/conversion-gain tunability, converts the time-interval information into a constant DC voltage [45] buffered by the variable-gain amplifier (VGA) offering noise-rejection and driving capabilities with additional tunability.

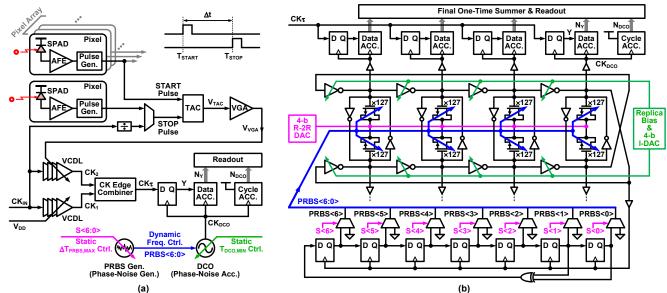

The TDC mechanism, which is the main focus of this paper, is illustrated in the lower-half of Fig. 2(a). The two identical voltage-controlled delay lines (VCDL) are both driven by the input clock, CK<sub>IN</sub>, so the clock periods of CK<sub>1</sub> and CK<sub>2</sub> are equal to the period of CK<sub>IN</sub>, T, but the timedomain delays of CK1 and CK2 are functions of the DC voltages, V<sub>DD</sub> and V<sub>VGA</sub>, respectively; and the periodic delta,  $\tau$ , between their delays represents the scaled version of  $\Delta t$  as described in [45]. After merging CK<sub>1</sub> and CK<sub>2</sub> by the rising clock-edge combiner, the resulting clock, CKτ, maintains the T periodicity while its positive duty-cycle,  $\tau/T$ , is the primary quantity under the RSA measurement as shown in Fig. 3. To perform the random sampling process, a free-running ringbased digitally-controlled oscillator (DCO) generates an asynchronous clock,  $CK_{DCO}$ , to sample the waveform of  $CK\tau$ through a 1-bit D flip-flop (DFF). At the meantime, the randomness of CKDCO sampling-instants is mainly accomplished by a digital pseudo-random-binary-sequence generator (PRBS Gen.) in Fig. 2(a) to dynamically modulate the DCO period and to ensure that the sampling probability density function (PDF) can satisfy the RSA criteria for the sampling outcome, Y, to be the random variable described in [45] or Section III. Finally, the averaging and noise-filtering processes are executed by the data and cycle accumulators (ACC.) to first count the numbers of ones,  $N_Y$  and  $N_{DCO}$ , at the outputs of the DFF and DCO, respectively; then, the final result per measurement,  $\overline{Y}$  (mean value of all sampled Y), is basically the ratio of the counter outputs,  $N_Y/N_{DCO}$  [45]. At this point, the process of an asynchronous RSA-based TDC has been completed.

To enhance the conversion-rate of RSA, the SAVR technique can be realized on the top of asynchronous RSA by simply adding extra static coarse controls for the reconfigurabilities of the DCO frequency and PRBS energy-level. The detailed circuit and reconfigurable schemes of the DCO are shown in Fig 2(b), including a 7-bit PRBS generator at the bottom and a four-stage pseudo-differential inverter-based DCO at the middle with static push-pull resistance-capacitance (RC) controls for SAVR. This PRBS generator produces a pseudo independent and identically distributed (I.I.D.) 7-bit binary control code, PRBS<6:0>, to dynamically modulate the DCO period through the digital-transistor-capacitor banks in the rate of CK<sub>DCO</sub>:

$$T_{DCO,n} = T_{DCO,MIN} + \Delta T_{PRBS,n}$$

$$T_{DCO,MIN} \le T_{DCO,n} \le T_{DCO,MIN} + \Delta T_{PRBS,MAX}$$

(4)

where "n" is the sample index from 1 to  $N_{DCO}$ ;  $T_{DCO,n}$  is the n-th period of the DCO;  $\Delta T_{PRBS,n}$  is the n-th DCO period extension controlled by PRBS<6:0>;  $T_{DCO,MIN}$  is the minimum DCO period when  $\Delta T_{PRBS,n}=0$ ;  $\Delta T_{PRBS,MAX}$  is the maximum DCO period extension which sets the span of the time-domain sampling PDF of a "single"  $CK_{DCO}$  sampling

FIGURE 3. The relationship among  $CK_1$ ,  $CK_2$ ,  $CK_7$ ,  $CK_{DCO}$  and sampling PDFs of the asynchronous RSA technique in the absolute time-domain associated with the nature of the DCO phase-noise accumulation property [45].

edge,  $f_{DCO,I}(t)$ , as shown in Fig. 3. Intuitively, the nonlinearity of the binary-control scheme and only 127 (=  $2^7$  – 1) possible digital-to-period conversion steps would cause poor uniform-distributed sampling PDFs, which are not only discrete but also unequally spaced. Fortunately, because of the phase-noise accumulation property of ring-oscillators [54], inherent circuit/device noise [54], Central Limit Theorem [55], and modulo-T circular Convolution Theorem [55], [56], this low-cost implementation can equivalently offer extremely high resolutions and continuous sampling PDFs as discussed in [45].

The low-power control schemes shown in Fig. 2(b) for enabling SAVR are the static reconfigurabilities of ΔT<sub>PRBS,MAX</sub> and T<sub>DCO,MIN</sub> highlighted in pink and green, respectively. To statically adjust ΔT<sub>PRBS,MAX</sub> (pink), the thermometer code S<6:0> can force the consecutive mostsignificant-bits (MSBs) of PRBS<6:0> to zeros which accordingly shut down the MSB capacitor banks and only leave the residual activated least-significant-bits (LSBs) of PRBS<6:0> to modulate  $\Delta T_{PRBS,n}$ . In other words, the range of the  $\Delta T_{PRBS,n}$ , i.e., 0 to  $\Delta T_{PRBS,MAX}$ , can be scaled down in powers of two based on the number of zeros in S<6:0> with a constant LSB step-size; this coarse scaling approach correspondingly reduces the total number of the digital-toperiod conversion steps. Therefore, the other control knob is employed by universally tuning the common drain-source DC voltage of the capacitor banks through a power/area efficient R-2R resistive ladder digital-to-analog converter [57], i.e., R-2R DAC in Fig. 2(b), without an analog voltage buffer due to the pseudo-differential DCO architecture. Using the digital transistors to perform this varactor-based capacitance tunability [54] can moderately scale down the LSB step-size with negligible power overhead to partially maintain the total number of digital-to-period conversion steps when S<6:0> heavily scales down  $\Delta T_{PRBS,MAX}$ . It is important to note that the reconfigurability of  $\Delta T_{PRBS,MAX}$  is mainly for demonstrating the effect of SAVR; the theoretical and simulation results in Section IV both confirm that a smaller  $\Delta T_{PRBS,MAX}$  offers more SAVR, but this is limited by the achievable minimum LSB capacitance in CMOS process technology. In any case, the gaps among the LSB steps in the DCO sampling PDFs are filled by the accumulation of circuit/device noise as mentioned. On the other hand, to statically adjust T<sub>DCO,MIN</sub> (green in Fig. 2(b)), the primary inverter stages of the DCO are implemented in a cascode structure, so the gate terminals of the partial tail P/N transistors can be biased through the replica of the inverter stage [54] and controlled by a low-power current DAC as shown in Fig. 2(b). At first glance, the implementations of these static reconfigurabilities are simple and ordinary, which indeed indicates the low power/area overhead of this SAVR technique. However, the theory and concept in behind are quite complicated and unintuitive; the detailed analysis is elaborated in Section IV.

All inherent phases of the DCO can be exploited to simultaneously sample the information signal, CKτ, and linearly improve the conversion-rate of each RSA measurement. To minimize the complexity, each DCO clock phase can actually manage its own asynchronous RSA process (DFF and ACC.) with its own clock (or phase) domain as shown at the top of Fig 2(b); once the common cycle accumulator reaches the designated sampling number, N<sub>DCO</sub>, an indicator is asynchronously sent to all data accumulators to stop individual counting processes all together, and then a final summer only needs a one-time operation to add all counter results in total. Note that the theoretical analysis in this paper only focuses on one of these parallel RSA processes since they are basically identical and just occurring simultaneously. More importantly, the correlation induced by SAVR only exists among all sequential samples of each individual random variable, Y (i.e., at each DFF output), generated by its own DCO sampling phase, not among multiple DFF outputs. Therefore, the theoretical analysis only considers one set of Y, CK<sub>DCO</sub>,  $N_Y$  and  $N_{DCO}$  as shown at the top-right corner of Fig. 2(b).

### III. RANDOM SAMPLING-AND-AVERAGING OVERVIEW

This section briefly summarizes the parameter definitions and important results from [45], which are essential information and background for the RSA with SAVR technique.

In the asynchronous RSA-based TCSPC system of this paper, Y is the primary random variable; E[Y] is the expectation of the random variable;  $Y_n$  is the n-th

experimental sample of  $Y;\ N_{DCO}$  is the total number of the samples;  $\overline{Y}$  is the mean of  $Y_n$  and the primary result per RSA measurement, which is also the Monte Carlo estimate [52] of the "ideal" expectation,  $E[Y]=E[\overline{Y}].$  Therefore, the theoretical variance of  $\overline{Y},\ Var[\overline{Y}],$  is the performance metric of the measurement, not Var[Y]. One example of the asynchronous RSA sampling processes is shown in Fig. 3, where the waveforms of  $CK\tau$  and  $CK_{DCO}$  are assumed to have coincident rising edges at t=0 for the sake of simplicity. With the parameter definitions in (4) and the phase-noise accumulation property of ring-oscillators [54], the n-th absolute sampling time,  $t_{SAMP,n},$  illustrated in Fig. 3, can be generalized as follows:

$$t_{SAMP,n} = \sum_{k=1}^{n} T_{DCO,k} = n \cdot T_{DCO,MIN} + \sum_{k=1}^{n} \Delta T_{PRBS,k}$$

(5)

Each t<sub>SAMP,n</sub> contains the deterministic term, n·T<sub>DCO,MIN</sub>, and stochastic term due to the DCO phase-noise accumulation, which describes the uncertainty of each sampling instant and can only be represented by a PDF, f<sub>DCO,n</sub>(t). Therefore, the n-th CK<sub>DCO</sub> rising edge occurs randomly but is confined within the distribution span and density magnitude of its own PDF, i.e., light-red areas in Fig. 3. More importantly, the stochastic term of each  $t_{SAMP,n}$  is the accumulation of "n" samples of an I.I.D. random variable (i.e.,  $\Delta T_{PRBS,k}$ , k = 1 to n) created by the PRBS generator for "n" times as shown in the second term of (5); equivalently, the PDF of the n-th DCO sampling instant,  $f_{DCO,n}(t)$ , is the convolution result of total "n" fundamental PDFs, f<sub>DCO,1</sub>(t), from the PRBS generator based on the Convolution Theorem [55]. Note that the fundamental PDF,  $f_{DCO,1}(t)$ , has a ΔT<sub>PRBS,MAX</sub> distribution span and constant 1/ΔT<sub>PRBS,MAX</sub> density magnitude as shown in Fig. 3. When n >> 1, the Central Limit Theorem guarantees that f<sub>DCO,n</sub>(t) converges to a Gaussian distribution with a wide distribution span,  $n \cdot \Delta T_{PRBS,MAX}$ , as shown at the bottom-right of Fig. 3 and top of Fig. 4(a) regardless of the sampling PDF, f<sub>DCO,1</sub>(t), from the PRBS generator.

Because of the periodicity of  $CK\tau$ , the entire distribution span of  $f_{DCO,n}(t)$  is automatically segmented and compressed into a [0, T) duration and equivalently converted into a modulo-T random sampling PDF,  $f_n(t)$ , which still follows the Convolution Theorem but shall be mathematically expressed by a circular convolution,  $CConv[\cdot]$ , due to the modulo-T operation [56]:

$$f_1(t) = CConv[f_{DCO,1}(t), \delta(t), T]$$

$$f_n(t) = CConv[f_{n-1}(t), f_1(t), T], \qquad n > 1$$

(6)

where  $\delta(t)$  is the unit impulse; the "t" of  $f_1(t)$ ,  $f_{n-1}(t)$ , and  $f_n(t)$  is the modulo-T time-domain variable within [0, T), but the "t" of  $f_{DCO,1}(t)$  and  $\delta(t)$  is the absolute time-domain variable referenced to t=0. Based on (6),  $f_1(t)$  plays as not only the

PDF of the first sampling instant but also the fundamental PDF element to obtain any  $f_n(t)$  from  $f_{n-1}(t)$ . According to both mathematical equation and statistical simulation in [45], as  $f_{DCO,n}(t)$  converges to a Gaussian PDF with increasing "n",  $f_n(t)$  converges to a uniformly distributed PDF with a constant density magnitude 1/T across the [0, T) distribution span. In other words, for all "n" >> 1,  $f_n(t)$  becomes an "identically distributed" PDF and independent from the parameters of  $T_{DCO,MIN}$ ,  $\Delta T_{PRBS,MAX}$ , and even "n" as illustrated in Fig. 4(a) and the top-row of Fig. 4(b). Therefore, the expectation of the asynchronous RSA measurement result also converges and can be expressed by a continuous one-dimensional geometric probability [55] format:

$$E[\overline{Y}] = \lim_{N_{DCO} \to \infty} \overline{Y} = \lim_{N_{DCO} \to \infty} \frac{\sum_{n=1}^{N_{DCO}} Y_n}{N_{DCO}} = \lim_{N_{DCO} \to \infty} \frac{N_Y}{N_{DCO}}$$

$$= E[Y] = \int_0^T y_n(t) \cdot f_n(t) \cdot dt$$

$$= \int_0^\tau \frac{1}{T} \cdot dt + \int_\tau^T \frac{0}{T} \cdot dt = \frac{\tau}{T} = P_1$$

(7)

where  $y_n(t)$  is the modulo-T waveform of  $CK\tau$  sampled by the modulo-T sampling PDF,  $f_n(t)$ , of  $CK_{DCO}$ ;  $P_1$  (= 1 –  $P_0$ ) is the probability of obtaining a  $Y_n$  as Logic-1, and  $P_0$  as Logic-0. Finally, the time-interval under the RSA measurement can be obtained based on (8):

$$\Delta t = \frac{\tau}{K_{TAC} \cdot K_{VGA} \cdot K_{DL}} \approx \frac{T \cdot \bar{Y}}{K_{TAC} \cdot K_{VGA} \cdot K_{DL}}$$

$$= \frac{T}{K_{TAC} \cdot K_{VGA} \cdot K_{DL}} \cdot \frac{N_{Y}}{N_{DCO}}$$

(8)

where  $K_{TAC}$ ,  $K_{VGA}$ , and  $K_{DL}$  are the conversion-gains of the TAC, VGA and VCDL, respectively.

Although all  $f_n(t)$  are identical when n >> 1, the correlation among all  $f_n(t)$  is a complicated function of  $f_1(t)$ . As proven in [45], to implement I.I.D. sampling PDFs, the distribution span of  $f_1(t)$ ,  $\Delta T_{PRBS,MAX}$ , has to satisfy one of the two criteria:  $Mod[\Delta T_{PRBS,MAX}, T] = 0$  or  $\Delta T_{PRBS,MAX} >> T$ , where  $Mod[\cdot]$  is the modulo-T operator, so the samples of the random variable,  $Y_n$ , can be pairwise independent. And, the theoretical variance of the asynchronous RSA measurement under the I.I.D. random sampling condition can be expressed by

$$Var[\bar{Y}] = \sigma_{\bar{Y}}^2 = \frac{\sigma_{Y}^2}{N_{DCO}} = \frac{E[Y^2] - E^2[Y]}{N_{DCO}} = \frac{P_1 \cdot P_0}{N_{DCO}}$$

(9)

In agreement with the weak law of large numbers [55], the theoretical variance,  $Var[\overline{Y}]$ , i.e., the power of the estimation error or quantization noise, in (9) reciprocally degrades with the total number of samples,  $N_{DCO}$ , and additionally it is a

FIGURE 4. (a) The concept of the modulo-T operation and density-magnitude convergence of a random sampling PDF in the asynchronous RSA implementation [45]. (b) The development examples of the conditional joint sampling PDFs of a  $[Y_n, Y_k]$  pair from "n" to "k" = (n + 1), (n + 2) and (n + 3), where  $\tau = T/2$ ,  $Mod[T_{DCO,MIN}, T] \approx T/2$ , and  $\Delta T_{PRBS,MAX} \approx T/4$ .

function of  $P_1$  and  $P_0$ , which matches the variance of a Bernoulli [55] random variable as each  $Y_n$  only has two possible outcomes, Logic-1 or Logic-0. In sum, an asynchronous RSA measurement can trade in a larger number of samples,  $N_{DCO}$ , which is equivalent to a longer measurement time or slower conversion-rate, for achieving a higher accuracy.

In this paper, the experimental variances obtained from simulation data are required to verify the theoretical derivations and can be expressed as follows [45], [52], [58]:

$$Var[\bar{Y}] \approx \frac{\sum_{m=1}^{N_{EXP}} \left( \bar{Y}_m - \frac{1}{N_{EXP} - 1} \cdot \sum_{p=1}^{N_{EXP}} \bar{Y}_m \right)^2}{N_{EXP} - 1} \tag{10}$$

The accuracy of this experimental variance depends on the number of  $\overline{Y}$ ,  $N_{EXP}$ , obtained from experiments or simulations. Note that, in realistic RSA measurements under a certain accuracy requirement with the settings of  $N_{DCO}$ ,  $T_{DCO,MIN}$ ,  $\Delta T_{PRBS,MAX}$  and T, only a single  $\overline{Y}$  is required to represent one measurement result [45].

### IV. SELF-ANTITHETIC VARIANCE REDUCTION

To comprehensively elaborate SAVR and its realization methodology in an asynchronous RSA system, the analysis process can be started from formulating the variance of a Monte Carlo estimate in general:

$$Var[\bar{Y}] = Var\left[\frac{\sum_{n=1}^{N_{DCO}} Y_n}{N_{DCO}}\right] = \frac{Var\left[\sum_{n=1}^{N_{DCO}} Y_n\right]}{N_{DCO}^2}$$

$$= \frac{\sum_{n=1}^{N_{DCO}} \sum_{k=1}^{N_{DCO}} Cov[Y_n, Y_k]}{N_{DCO}^2} = \frac{E\left[\sum_{k=1}^{N_{DCO}} Cov[Y_n, Y_k]\right]}{N_{DCO}}$$

$$= \frac{\sum_{n=1}^{N_{DCO}} Var[Y_n]}{N_{DCO}^2} + \frac{2 \cdot \sum_{n=1}^{N_{DCO}-1} \sum_{k=n+1}^{N_{DCO}-1} Cov[Y_n, Y_k]}{N_{DCO}^2}$$

$$= \frac{P_1 \cdot P_0}{N_{DCO}} + \frac{2 \cdot \sum_{n=1}^{N_{DCO}-1} \sum_{k=n+1}^{N_{DCO}-1} Cov[Y_n, Y_k]}{N_{DCO}^2}$$

(11)

where  $Cov[Y_n, Y_k]$  is the pairwise covariance of any two samples,  $Y_n$  and  $Y_k$ ; both "n" and "k" are the sample indexes. When n = k,  $Cov[Y_n, Y_k] = Var[Y_n]$ , i.e., the variance of the n-th sample, otherwise  $Cov[Y_n, Y_k] = Cov[Y_k, Y_n]$  which is a symmetric covariance matrix. If  $Y_1, Y_2, ...$ , and  $Y_{N_{DCO}}$  are all pairwise independent, then  $Cov[Y_n, Y_k] = 0$  for all  $n \neq k$  in (11), and the pairwise covariance sum (the  $2^{nd}$  term in the  $5^{th}$  line of (11)) is zero, so (11) becomes the I.I.D. situation as shown in (9). The key idea of SAVR is to create non-zero correlations among the samples, i.e.,  $Y_1, Y_2, ...$ , and  $Y_{N_{DCO}}$ , of the random variable, Y, so that the pairwise covariance sum can be negative, and then overall variance,  $Var[\overline{Y}]$ , per

RSA measurement can be effectively less than the variance of the I.I.D. situation in (9).

## A. THEORETICAL CONCEPT AND PERFORMANCE ESTIMATION

According to the detailed analysis about the covariances of the adjacent samples,  $Cov[Y_n, Y_{n+1}]$ , under three  $\Delta T_{PRBS,MAX}$  scenarios (i.e.,  $\Delta T_{PRBS,MAX} <$ , =, or > T) in [45], the conclusion shows  $Cov[Y_n, Y_{n+1}]$  can have pronounced nonzero values when  $Mod[\Delta T_{PRBS,MAX}, T] < T$  due to the nonuniform conditional joint PDFs within their own integral time-intervals,  $[0,\tau)$  and  $[\tau,T)$ . In this paper, the case of nonzero covariances between adjacent samples is further extended to the deduction of any pairwise correlation between  $Y_n$  and  $Y_k$  due to the fact of the DCO phase-noise accumulation property reflected by (5) and (6). Thus, if the technique can take advantage of these non-zero covariances,  $Cov[Y_n, Y_k]$ , and assure the pairwise covariances sum is negative, then VR can be successfully performed.

To find  $Cov[Y_n, Y_k]$ , all conditional joint PDFs of any  $[Y_n, Y_k]$  pair have to be first formulated, where n=1 to  $(N_{DCO}-1)$  and k=(n+1) to  $N_{DCO}$  are sufficient to cover all covariance elements in the symmetric covariance matrix. Though there are only four possible binary combinational outcomes of a certain  $[Y_n, Y_k]$  pair, its conditional joint PDFs shall also cover all possible binary combinational outcomes from  $Y_{n+1}$  to  $Y_{k-1}$  because the accumulation property and Convolution Theorem described in (6) form the chain of correlations from each specific  $Y_n$  through  $Y_{n+1}, Y_{n+2}, ..., Y_{k-2}$ , and  $Y_{k-1}$  all the way to each specific  $Y_k$ . Thus, the conditional joint PDFs of a  $[Y_n, Y_k]$  pair under all possible conditions of  $[Y_n, ..., Y_{k-1}]$  shall be generalized as follows:

$$f_{n,k}(t)\big|_{[Y_n,\dots,Y_{k-1}]=D2B[q]}$$

$$= CConv\left[f_{n,k-1}(t)\big|_{[Y_n,\dots,Y_{k-1}]=D2B[q]}, f_1(t), T\right] \quad (12)$$

where  $q=0,\ 1,\ 2,\ ...,\ (2^{k-n}-1);$  all possible binary combinational conditions of  $[Y_n, ..., Y_{k-1}]$  are represented by the corresponding decimal numbers, "q", and decimal-to-binary operators,  $D2B[\cdot]$ , for the sake of simplicity. In Fig. 4(b), the PDF curves and annotations highlighted in black represent the examples of (12), including k=(n+1), (n+2), and (n+3), which follows the Convolution Theorem under the conditions of  $[Y_n, ..., Y_{k-1}]$ . Since the location of " $\tau$ " within the modulo-T time-interval, [0, T), defines the PDF boundaries for the probability of  $Y_k$  to be Logic-1 or Logic-0, the conditional joint PDF of a  $[Y_n, Y_k]$  pair under all possible conditions of  $[Y_n, ..., Y_k]$  can be obtained by forcing one part, i.e.,  $[0, \tau)$  or  $[\tau, T)$ , of the PDF in (12) to zero to satisfy one of the possible  $Y_k$  conditions:

$$f_{n,k}(t)\Big|_{[Y_n,\dots,Y_{k-1}]=D2B[q]}^{[Y_k]=1}$$

$$\begin{aligned}

&= \begin{cases} f_{n,k}(t) \big|_{[Y_n, \dots, Y_{k-1}] = D2B[q]}, & 0 \le t < \tau \\

0, & \tau \le t < T \end{cases} \\

f_{n,k}(t) \big|_{[Y_n, \dots, Y_{k-1}] = D2B[q]}^{[Y_k] = 0}, & 0 \le t < \tau \\

&= \begin{cases} 0, & 0 \le t < \tau \\

f_{n,k}(t) \big|_{[Y_n, \dots, Y_{k-1}] = D2B[q]}, & \tau \le t < T \end{cases}

\end{aligned} (13)$$

In other words, each conditional joint PDF under the conditions of  $[Y_n, ..., Y_{k-1}]$  in (12) can diversify into two conditional joint PDFs under the conditions of  $[Y_n, ..., Y_k]$  as shown in (13) and (14), which are highlighted in blue and orange, respectively, in Fig. 4(b). Note that the distribution profiles of all conditional joint PDFs are convoluted functions of  $\tau$  and  $f_1(t)$ , and  $f_1(t)$  itself is a function of  $\text{Mod}[T_{\text{DCO,MIN}}, T]$  and  $\Delta T_{\text{PRBS,MAX}}$ . Therefore, the plots shown in Fig. 4(b), where  $\tau = T/2$ ,  $\text{Mod}[T_{\text{DCO,MIN}}, T] = T/2$ , and  $\Delta T_{\text{PRBS,MAX}} = T/4$ , can be very different if the values of these parameters are set differently; i.e., these parameters dominantly affect the behaviors of the pairwise covariances,  $\text{Cov}[Y_n, Y_k]$ , which now can be generalized as follows based on the information of all conditional joint PDF of a  $[Y_n, Y_k]$  pair from (13) and (14):

$$\begin{aligned} &Cov[Y_{n},Y_{k}] \\ &= \int_{0}^{T} (y_{n}(t) - P_{1}) \cdot (y_{k}(t) - P_{1}) \cdot f_{n,k}(t) \cdot dt \\ &= (1 - P_{1})^{2} \cdot \sum_{\substack{q=0 \ 2^{k-n-1}-1 \ T}}^{T} \int_{0}^{T} f_{n,k}(t) \Big|_{[Y_{n},Y_{k}]=[1,1]}^{[Y_{n},Y_{k}]=[1,1]} dt \\ &- (P_{1} - P_{1}^{2}) \cdot \sum_{\substack{q=0 \ 2^{k-n-1}-1 \ T}}^{T} \int_{\tau}^{T} f_{n,k}(t) \Big|_{[Y_{n},Y_{k}]=[1,0]}^{[Y_{n},Y_{k}]=[1,0]} dt \\ &- (P_{1} - P_{1}^{2}) \cdot \sum_{\substack{q=0 \ 2^{k-n-1}-1 \ T}}^{T} \int_{0}^{T} f_{n,k}(t) \Big|_{[Y_{n+1},\dots,Y_{k-1}]=D2B[q]}^{[Y_{n},Y_{k}]=[0,1]} dt \\ &+ (0 - P_{1})^{2} \cdot \sum_{\substack{q=0 \ 2^{k-n-1}-1 \ T}}^{T} \int_{\tau}^{T} f_{n,k}(t) \Big|_{[Y_{n},Y_{k}]=[0,0]}^{[Y_{n},Y_{k}]=[0,0]} dt \ (15) \end{aligned}$$

As shown in (15),  $Cov[Y_n, Y_k]$  can be grouped into four terms based on the binary combinational outcomes of a  $[Y_n, Y_k]$  pair, and each term is the summation of  $2^{k-n-1}$  integrals of the conditional joint PDFs under all possible conditions of  $[Y_{n+1}, ..., Y_{k-1}]$ . Thus, the total number of summation terms or conditional joint PDFs in (15) is  $2^2 \cdot 2^{k-n-1} = 2^{k-n+1}$  for each  $Cov[Y_n, Y_k]$ . In addition, each conditional joint PDF,  $f_{n,k}(t)|_{[Y_n,...,Y_{k-1}]}$ , in (15) is obtained by (k-n) times of the modulo-T circular convolutions shown in (12). Overall, the computation effort of (15) is dominated by total  $(k-n) \cdot 2^{k-n+1}$  modulo-T circular convolutions for each  $Cov[Y_n, Y_k]$ . On top of this, an overall variance,  $Var[\overline{Y}]$ , calculation, requires total  $(N_{DCO}^2 - N_{DCO})/2$  of  $Cov[Y_n, Y_k]$  elements in the whole

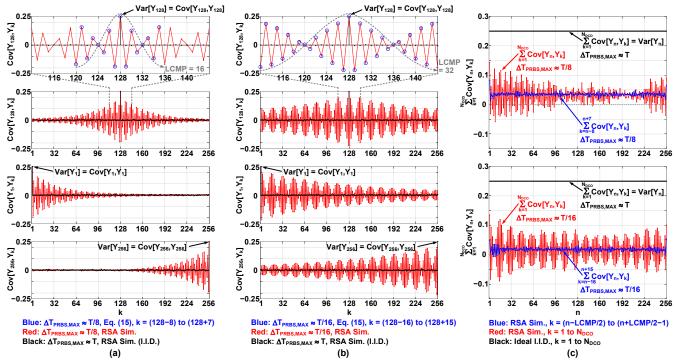

FIGURE 5. Under the asynchronous RSA setting of Mod[ $T_{DCO,MIN}$ , T]  $\approx$  T/2,  $\tau$ /T = 0.5,  $N_{DCO}$  = 256, and  $N_{EXP}$  =  $2^{13}$ , (a) the correlation functions of n = 128, 1, and 256 across k = 1 to  $N_{DCO}$  when  $\Delta T_{PRBS,MAX} \approx T/8$ ; (b) the correlation functions of n = 128, 1, and 256 across k = 1 to  $N_{DCO}$  when  $\Delta T_{PRBS,MAX} \approx T/8$ ; (c) The single-dimensional covariance sums and partial covariance sums of RSA w/o SAVR ( $\Delta T_{PRBS,MAX} \approx T/8$  & T/8 & T/8 & T/8 .

covariance summation as shown in 5<sup>th</sup> line of (11), and usually N<sub>DCO</sub> is in the range of 2<sup>8</sup> to 2<sup>18</sup> even with the VR techniques. In short, the computation effort of the theoretical variance with non-zero pairwise covariance formulated by (15) turns out to be impractical for the performance estimation of the RSA with SAVR technique. This issue reflects the necessity of developing a computation-efficient approach for the overall variance calculation.

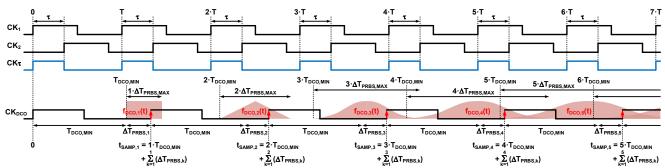

To simplify the analysis process, the mechanism of SAVR is elaborated by specific examples in an asynchronous RSA system, and then general cases can be further summarized. The following two examples have common parameter setups: the time-domain quantity under the RSA measurement,  $\tau/T = 0.5$  (=  $P_1$ ),  $N_{DCO} = 256$ , and  $Mod[T_{DCO,MIN}, T] \approx T/2$ . The only difference is that their ΔT<sub>PRBS,MAX</sub> are set to T/8 and T/16 individually through the static PRBS energy-level control shown in Fig. 2. The correlation function between Y<sub>n</sub> and Y<sub>k</sub> can be observed by plotting Cov[Y<sub>n</sub>, Y<sub>k</sub>] of each "n" across all possible "k" (= 1 to N<sub>DCO</sub>) as shown in Fig. 5(a) and 5(b), where only the cases of n = 1, 128 ( $N_{DCO}/2$ ), and 256 ( $N_{DCO}$ ) are included with  $N_{EXP} = 2^{13}$ . For the purpose of reference, the I.I.D. scenario (i.e.,  $\Delta T_{PRBS,MAX} = T$ ) verified in [45] is also included in Fig. 5, where the I.I.D. correlation functions (black) are basically zero for all  $n \neq k$  and have the non-zero value, 0.25 (=  $P_1 \cdot P_0$ ), at n = k. From these examples of  $\Delta T_{PRBS,MAX} < T$  (red), multiple attributes can be observed: first, Cov[Yn, Yk] of each "n" is self-symmetrical with respect to "k = n", e.g.,  $Cov[Y_{128}, Y_{127}] = Cov[Y_{128}, Y_{129}];$  second, because of the

symmetric covariance matrix and  $Cov[Y_n, Y_k] = Var[Y_n] =$  $P_1 \cdot P_0$  when k = n, all correlation functions have the same profile but shift along the k-axis based on the value of "n", e.g.,  $Cov[Y_1, Y_k]$ ,  $Cov[Y_{128}, Y_k]$ , and  $Cov[Y_{256}, Y_k]$  shift their peaks to k = 1, 128, and 256, respectively, and therefore  $Cov[Y_n, \ Y_k] \ = \ Cov[Y_{N_{DCO}-n+1}, \ Y_{N_{DCO}-k+1}]; \ third, \ the$ correlation is enhanced (longer correlation tails) with decreasing  $\Delta T_{PRBS,MAX}$ ; fourth, the correlation degrades with increasing |k - n|; fifth, more importantly, the Cov[Y<sub>n</sub>, Y<sub>k</sub>] of each "n" has a consistent sign-alternation pattern within each correlation-envelop period which guarantees the cancellation in the total covariance sum, i.e., effective VR, though the amplitude of the correlation-envelop attenuates with |k - n|. The zoom-in versions of the correlation functions at the top of Fig. 5(a) and 5(b) respectively highlight the least-common-multiple periods (LCMP) of the sign-alternation patterns and correlation-envelop periods of the two  $\Delta T_{PRBS,MAX}$  scenarios. The theoretical variance calculation can be greatly simplified by grouping the effect of covariance cancellation into single or multiple LCMPs instead of considering all the covariance elements.

The effect of this SAVR technique can be more comprehensively demonstrated by the single-dimensional covariance sums and the overall (two-dimensional) covariance sum,  $Var[\overline{Y}]$ . The single-dimensional covariance sum is defined as the summation of all  $Cov[Y_n, Y_k]$  from k = 1 to  $N_{DCO}$  with respect to each "n", e.g., the summation of all red data points in the  $Cov[Y_{128}, Y_k]$  plot is the single-dimensional covariance sum at n = 128. The single-

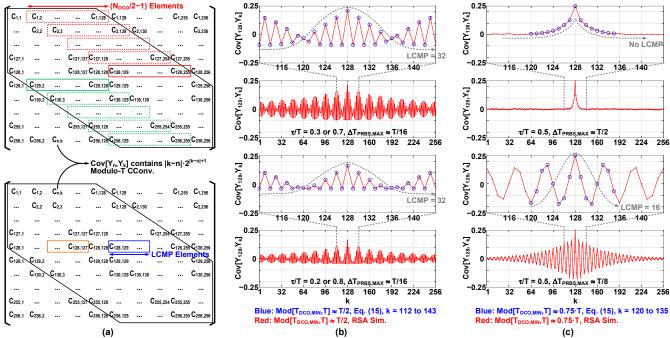

FIGURE 6. Under the asynchronous RSA setting of  $N_{DCO} = 256$  and  $N_{EXP} = 2^{13}$ , (a) the required covariance elements for complete (top) and approximate (bottom) overall variance calculations when  $Mod[T_{DCO,MIN}, T] \approx T/2$  and  $Mod[T_{DCO,MIN}, T] \approx T/2$  and  $Mod[T_{DCO,MIN}, T] \approx T/2$  and  $Mod[T_{DCO,MIN}, T] \approx T/2$ , and  $Mod[T_{DCO,MIN}, T] \approx T/2$ . The correlation functions of  $Mod[T_{DCO,MIN}, T] \approx T/2$ .

dimensional covariance sums of the uncorrelated (I.I.D.) and two correlated examples are shown in Fig. 5(c) whose horizontal-axis variable is "n", and n = 1 to  $N_{DCO}$ . The singledimensional covariance sums of the I.I.D. example (black dots) are always 0.25 for all "n" since each "n" only has its non-zero covariance  $Var[Y_n] = 0.25$  at n = k. On the other hand, the single-dimensional covariance sums of the two correlated examples (red dots) are all smaller than 0.25 across all "n" in Fig. 5(c) because the periodical signalternation patterns of their correlation functions are canceling the power of  $Var[Y_n] = 0.25$  at n = k as shown in Fig. 5(a) and 5(b). This is the reason for naming this technique as self-antithetic VR. Finally, the overall variance of RSA can be obtained by the summation of all singledimensional covariance sums divided by N<sub>DCO</sub> as shown in the 3<sup>rd</sup> line of (11). According to the fact shown in Fig. 5(c), the overall variances (sums of red dots) are reduced from the value of the I.I.D. variance (sums of black dots). Equivalently, the first term in the 5th line of (11), i.e., P<sub>1</sub>·P<sub>0</sub>/N<sub>DCO</sub>, equals the I.I.D. variance without any VR, and the second term in the 5th line of (11) is negative to successfully perform VR.

The analysis results demonstrated in Fig. 5 offer further insights: first, a smaller  $\Delta T_{PRBS,MAX}$ , i.e., a narrower fundamental sampling PDF,  $f_1(t)$ , creates stronger correlations across all sampling points (i.e., longer correlation tails), longer LCMPs (e.g., 16 points for T/8, 32 points for T/16), and eventually more variance reduction; second, though the sign of each single-dimensional covariance sum can be either positive or negative with VR,

the average of all single-dimensional covariance sums is always above zero as shown in Fig. 5(c), which verifies the principles of non-negative variances and finite measurement resolutions; third, more importantly, the computation efficiency of each theoretical single-dimensional covariance sum and overall variance can be greatly improved by only summing the covariances surrounding the "k = n" within a few LCMPs:

$$If \Delta T_{PRBS,MAX} = \frac{2 \cdot T}{LCMP}$$

$$\& \frac{r \cdot LCMP + 2}{2} \le n \le \frac{2 \cdot N_{DCO} - r \cdot LCMP + 2}{2}$$

$$E\left[\sum_{k=1}^{N_{DCO}} Cov[Y_n, Y_k]\right] \approx \sum_{k=n-\frac{r \cdot LCMP}{2}}^{n+\frac{r \cdot LCMP}{2} - 1} Cov[Y_n, Y_k]$$

(16)

where "r" is the number of LCMP included in the approximation of (16). In Fig. 5(c), the red dots represent the accurate one-dimensional covariance sums; the blue dots represent the partial one-dimensional covariance sums formulated by the right-hand side of (16) with r = 1 and k = (n - LCMP/2) to (n + LCMP/2 - 1). Although the red and blue dots at each "n" contain certain amounts of delta, the distribution of the blue dots is relatively constant and basically the average of the red dots except the values of "n" approach 1 or  $N_{DCO}$  since the correlation functions of these "n" have significantly unbalanced correlation-tail lengths, e.g.,  $Cov[Y_1, Y_k]$  and  $Cov[Y_{256}, Y_k]$  in Fig. 5(a) and 5(b).

Therefore, any partial single-dimensional covariance sum (blue dot) at any "n" far away from 1 or  $N_{DCO}$  is sufficient for approximating the average of the accurate one-dimensional covariance sums formulated by the left-hand-side of (16). For example, by plugging (16) into the  $3^{rd}$  line of (11) with "n =  $N_{DCO}/2$ ", the overall variance can be approximated as follows:

$$Var[\bar{Y}] = \frac{E\left[\sum_{k=1}^{N_{DCO}} Cov[Y_n, Y_k]\right]}{\frac{N_{DCO}}{N_{DCO} + r \cdot LCMP}}$$

$$\approx \frac{1}{N_{DCO}} \cdot \sum_{k=\frac{N_{DCO} - r \cdot LCMP}{2}}^{N_{DCO} - r \cdot LCMP} Cov\left[Y_{\left(\frac{N_{DCO}}{2}\right)}, Y_k\right]$$

(17)

Note that the  $Cov[Y_n, Y_k]$  in (16) and (17) is referring to its theoretical definition in (15) and annotated as blue circles in Fig. 5(a) and 5(b), while the all red dots in Fig. 5 are obtained from the statistical simulation results. And, the approximation errors in (16) and (17) can be improved by extending the number of LCMP, i.e., "r", included in the summation operators.

As discussed earlier, if the theoretical computation effort is dominated by the modulo-T circular convolutions, the computation efficiency improvement from (11) to (17) can be evaluated by the ratios between their operation numbers of modulo-T circular convolutions. The covariance matrix in the case of  $\Delta T_{PRBS,MAX} \approx T/8$  (LCMP = 16) with  $N_{DCO} = 256$ is shown in Fig. 6(a). Since the correlation tails of this example are roughly vanished when  $|k - n| > N_{DCO}/2$  as shown in Fig. 5(a), only the covariance elements circled in black need to be considered to estimate the computation efforts for both (11) and (17). For (11), because the  $Cov[Y_n]$  $Y_k$ ] of each "n" is self-symmetrical with respect to "k = n", the covariance elements circled in dashed-red are identical to those circled in solid-red, and covariance elements circled in green are the images of those circled in red. With the property of this symmetric covariance matrix, i.e., Cov[Y<sub>n</sub>,  $Y_k$ ] = Cov[ $Y_k$ ,  $Y_n$ ], all covariance elements circled in black can be fully obtained by only calculating the covariance elements circled in solid-red as shown in the upper-half of Fig. 6(a), and the required number of modulo-T circular convolutions in (11) is expressed in the numerator of (18). On the other hand, to cover two LCMPs for (17), only the covariance elements within one LCMP circled in blue shown in the lower-half of Fig. 6(a) need to be calculated, and the other LCMP circled in orange is again the image of those circled in blue, so the required number of modulo-T circular convolutions in (17) is expressed in the denominator of (18).

$$\frac{\sum_{k=\frac{N_{DCO}-1}{2}+1}^{N_{DCO}-1} \left(k - \frac{N_{DCO}}{2}\right) \cdot 2^{\left(k - \frac{N_{DCO}}{2} + 1\right)}}{\sum_{k=\frac{N_{DCO}}{2}+1}^{\frac{N_{DCO}}{2}+1} \left(k - \frac{N_{DCO}}{2}\right) \cdot 2^{\left(k - \frac{N_{DCO}}{2} + 1\right)}}$$

(18)

The ratio of modulo-T circular convolution numbers between (11) and (17) under this specific example is about 2.18×10<sup>34</sup>. This incredible "computation effort reduction" (NOT variance reduction), even just for  $N_{DCO} = 2^8$  and two LCMPs included, is again mainly because all pairwise covariances theoretically have to be included in (11) due to the inevitable correlations (based on the DCO phase-noise accumulation property and Convolution Theorem) among the majority of N<sub>DCO</sub> samples, but actually only the average of all the covariances matters and can be approximated by summing the theoretical covariances within a few LCMPs of the central correlation function as shown in (17) and Fig. 5(c). In sum, as the zoom-in versions of  $Cov[Y_{128}, Y_k]$  shown at the top of Fig. 5(a) and 5(b), the theoretical calculation results, i.e., blue circles from (15), and the statistical asynchronous RSA simulation results, i.e., red dots, match well, but the computation efficiency of the theoretical variance with SAVR enabled is actually quite low if relying on the equations from (11) to (15). On the other hand, Equation (17) brings the computation efficiency to a reasonable level but losing the accuracy. Only the Monte Carlo approach (red dots from the statistical software/lab experiments) can simultaneously offer the efficiency and accuracy from the analytical point of view.

# B. PRACTICAL CONSIDERATION AND SIMULATION RESULTS

In realistic applications, the SAVR technique has to be effectively applicable to a wide dynamic range of  $\tau/T$ . Four more examples of the correlation functions for the variates of  $\tau/T$  (= 0.2, 0.3, 0.7, and 0.8) are shown in Fig. 6(b) to illustrate the effects of SAVR with respect to the time-intervals under the asynchronous RSA measurements. All parameter settings in Fig. 6(b) are consistent with those in Fig. 5(b) except the different values of  $\tau/T$ , so their correlation functions exhibit similar correlation tails, LCMPs, and sign-alternation patterns; however, in Fig. 6(b), the amplitudes and upper/lower swings of the covariance envelopes are basically attenuated and distorted with  $|\tau/T|$  0.5. Especially, the unbalanced upper/lower envelope swings around the central covariances (at n = k) degrades the efficiency of SAVR when  $\tau/T$  is moving away from 0.5.

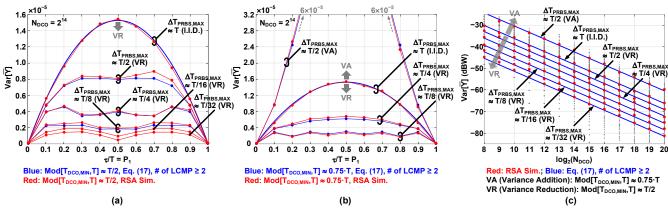

The variance of asynchronous RSA vs. dynamic range with different SAVR settings is shown in Fig. 7(a) where  $Mod[T_{DCO,MIN}, T] \approx T/2$ ,  $N_{DCO} = 2^{14}$ , and  $N_{EXP} = 2^{11}$ . Multiple important conclusions have been verified and demonstrated in this figure. First, a stronger VR can be statically enabled by decreasing the PRBS time-domain noise power (or energy-level), i.e.,  $\Delta T_{PRBS,MAX}$ , (or the PDF span of  $f_1(t)$ ) to extend the covariance cancellation effect (or widening the  $Cov[Y_n, Y_k]$  envelopes and correlation tails) without any extra hardware/circuit cost required to enhance the resolution of the PRBS generator since the infinite phase resolution has been taking care of by the inherent circuit/system noise

FIGURE 7. The theoretical (blue) and simulated (red) variances of asynchronous RSA plotted as functions of  $\tau$ /T under different  $\Delta T_{PRBS,MAX}$  settings with  $N_{DCO} = 2^{14}$  and  $N_{EXP} = 2^{11}$ , when (a) Mod[ $T_{DCO,MIN}$ , T]  $\approx T/2$ ; (b) Mod[ $T_{DCO,MIN}$ , T]  $\approx 0.75 \cdot T$ . (c) The theoretical (blue) and simulated (red) variances of asynchronous RSA plotted as functions of  $N_{DCO}$  with  $\tau$ /T = 0.5 and  $N_{EXP} = 2^8$ , including the I.I.D., VR, and VA scenarios based on the combinational settings of  $T_{DCO,MIN}$ ,  $\Delta T_{PRBS,MAX}$ , and T.

accumulations through the DCO [45], [54]. Second, the efficiency of SAVR degrades with the increase of  $|\tau/T - 0.5|$ as discussed, but the quantization power of the RSA measurement,  $Var[\overline{Y}]$ , stays relatively constant across the entire dynamic range. Third, the blue dots are the theoretical variance approximations based on (17) with covering at least two LCMPs ( $r \ge 2$ ) for different  $\Delta T_{PRBS,MAX}$  scenarios. Even on a linear scale, the theoretical approximations (blue dots) from (17) match well with the statistical results (red dots) from the RSA experimental simulations; this verifies the contribution of (17) which can greatly improve computation efficiency without compromising the estimation accuracy.

In Fig. 7(c), the variances of asynchronous RSA are plotted as functions of  $N_{DCO}$  on the dBW scale with different SAVR settings at  $\tau/T=0.5$  with  $N_{EXP}=2^8$ . Similar to the cases of the oversampling synchronous RSA in [45], the weak law of large numbers still holds for the asynchronous RSA regardless of the VR technique; also, both theoretical approximation (blue lines) and simulation (red dots) results are well aligned and perform consistent variance degradations at -3 dBW per octave of  $N_{DCO}$  or equivalently -6 dBW per octave of ENOB [45]. More importantly, the variances at  $\tau/T=0.5$  exhibit -3 dBW per octave of the  $\Delta T_{PRBS,MAX}$  divisor for all  $N_{DCO}$  in both Fig. 7(a) and 7(c).

The key contribution of SAVR is not only to improve the ENOB, which can be obtained by increasing N<sub>DCO</sub> anyway, but more significantly improves the conversion-rate of the asynchronous RSA measurement. For example, to achieve the same variance of -60 dBW in Fig. 7(c), when  $\Delta T_{PRBS,MAX} \approx T$  (SAVR disabled), it requires N<sub>DCO</sub> =  $2^{18}$  and T<sub>DCO,AVG</sub> =  $(T_{DCO,MIN} + \Delta T_{PRBS,AVG}) \approx (T/2 + T/2) = T$ ; On the other hand, when  $\Delta T_{PRBS,MAX} \approx T/32$  (SAVR enabled), it requires N<sub>DCO</sub> =  $2^{13}$  and T<sub>DCO,AVG</sub> =  $(T_{DCO,MIN} + \Delta T_{PRBS,AVG}) \approx (T/2 + T/64) = 0.516 \cdot T$ , so the conversion-rate, i.e.,  $1/(N_{DCO} \cdot T_{DCO,AVG})$ , is improved by  $62 \times$  when the SAVR technique is enabled. Note that this example is at  $\tau/T = 0.5$ , which has the worst quantization-noise power when SAVR is disabled (I.I.D.)

but maximum variance reduction across the entire  $\tau/T$  dynamic range as shown in Fig. 7(a). Besides, the required setting of Mod[ $T_{DCO,MIN}$ , T]  $\approx 0.5 \cdot T$  gives the flexibility of design options for  $T_{DCO,MIN}$ , including  $0.5 \cdot T$ ,  $1.5 \cdot T$ ,  $2.5 \cdot T$ , and so on. If the DCO frequency has reached the limit due to circuit bandwidth or power limitations, then proportionally extending  $\tau$  and T together can be an alternative way to achieve the fastest sampling option ( $T_{DCO,MIN} \approx 0.5 \cdot T$ ), which can be simply accomplished by statically scaling the conversion gains of the analog circuits, i.e.,  $K_{TAC}$ ,  $K_{VGA}$ , and  $K_{DL}$ , through the inherent calibration capability of the RSA measurement system [50]. Meanwhile, the nonlinearities and offsets due to analog-circuit nonidealities and mismatches can be pre-calibrated by RSA itself without any assistance from extra hardware [45], [49], [50].

Regarding the power overhead, the DCO power consumption with vs. without SAVR includes four major factors in the comparison: first, the DCO average frequency  $(F_{DCO,AVG} \approx 1/T_{DCO,AVG})$  is almost doubled, i.e.,  $1/(0.516 \cdot T)$ vs. 1/T; second, the per-stage capacitance load (C<sub>L</sub>) controlled by the PRBS generator is smaller since it is dominantly scaled with  $\Delta T_{PRBS,MAX}$ , i.e., T/32 vs. T; third, the power of the PRBS digital circuit is doubled with the DCO average frequency, i.e., 0.5 mW vs. 0.25 mW; fourth, additional DC power, i.e., 0.2 mW, of the R-2R and current DACs is required for the DCO static reconfigurations plotted by the green and pink lines in Fig. 2(b). Therefore, according to the simulation results and power estimations above  $(C_L \cdot V_{DD}^2 \cdot F_{DCO,AVG} + PRBS \text{ power} + DC \text{ power})$ , the overall DCO power roughly stays the same with and without SAVR, i.e., (2.4 + 0.5 + 0.2) mW vs. (2.75 + 0.25 + 0) mW = 3.1 mW vs. 3 mW. Meanwhile, the power consumptions of the TAC, VGA, VCDL and edge-combiner are all independent from the SAVR technique, but the dynamic power of the DFF and clock buffers are scaled up with the DCO average frequency. Thus, the TDC power numbers (TAC + VGA + VCDL + edge-combiner + DFF + clock buffer) with and without SAVR are 1.5 mW and 1.3 mW, respectively.

Overall, the total RSA-based TDC power, i.e., DCO + TDC = 4.6 mW vs. 4.3 mW, is increased only by 7% after enabling SAVR for a 62× conversion-rate enhancement since the DCO power is roughly independent from this technique as discussed. Note that the power estimations above include one clock generator (i.e., DCO) and one TDC, but in real TCSPC applications one clock generator with proper clock distribution can support multiple TDCs in the pixel array.

Regarding the area overhead of the SAVR technique, the additional hardware includes the R-2R and current DACs for the DCO static reconfigurations plotted by the green and pink lines in Fig. 2(b), which add an extra 25  $\mu$ m  $\times$  25  $\mu$ m overhead on the top of the DCO active area in a 22-nm CMOS process technology.

Based on the theoretical analysis and experimental simulations of the SAVR technique so far, two practical concerns may be raised. One is about the limitation of SAVR or its conversion-rate enhancement. Because it seems that a smaller  $\Delta T_{PRBS,MAX}$  (or noise energy-level) offers more SAVR, and if the minimum achievable ΔT<sub>PRBS,MAX</sub> is dominated by the single LSB capacitance, which is processtechnology dependent as mentioned in Section II, modulated by a 1-bit PRBS, then the system could simply rely on the noise accumulation of inherent thermal-noise from the DCO circuit. This idea is theoretically valid, but accumulating such low-energy noise meanwhile induces two issues to offset the benefit of SAVR: first, the sampling PDF, f<sub>n</sub>(t), now requires "n" to be extremely large to form a uniform PDF as shown in Fig. 4(a) [45] and satisfy the expectation in (7); second, now the values of LCMP also become extremely large for effective SAVR due to its reciprocal relation with the noise energy-level shown in (16). Both cause each RSA measurement to require a very large number of N<sub>DCO</sub> in total, so SAVR turns out to even slow down the conversion-rate in this case. The other concern is about whether variance addition (VA) can occur due to a combinational setup of  $T_{DCO,MIN}$ ,  $\Delta T_{PRBS,MAX}$ , and T deviating from the one for VR. The answer can be elaborated by an example shown in Fig. 6(c) having the identical parameter settings as those in Fig. 5  $(\tau/T = 0.5, N_{DCO} = 2^8, N_{EXP} = 2^{13})$  except Mod[ $T_{DCO,MIN}, T$ ]  $\approx 0.75 \cdot T$  instead. When  $\Delta T_{PRBS,MAX} \approx T/8$  shown in the lower-half of Fig. 6(c), the correlation function exhibits a different sign-alternation pattern and envelope from these shown in Fig. 5(a), but the single-dimensional covariance sum is still less than that of the I.I.D. case (i.e., 0.25); equivalently this is VR. However, when  $\Delta T_{PRBS,MAX} \approx T/2$ shown in the upper-half of Fig. 6(c), the correlation function contains all positive values, so definitely the singledimensional covariances and overall variance are larger than those of the I.I.D. case; equivalently this is VA. The asynchronous RSA variance vs. dynamic range plots shown in Fig. 7(a) and 7(b) contains identical parameter settings except Mod[ $T_{DCO,MIN}$ , T]  $\approx T/2$  and 0.75·T, respectively, for the purpose of the side-by-side comparison. Any quantization-noise power lower than the I.I.D. variance curve performs VR otherwise VA. The unfavorable VA occurs whenever the coincident interactions between  $Mod[T_{DCO,MIN}, T]$  and  $\Delta T_{PRBS,MAX}$  always generates positive pairwise covariances as the example of simultaneously Mod[T<sub>DCO,MIN</sub>, T]  $\approx 0.75 \cdot \text{T}$  and  $\Delta T_{PRBS,MAX} \approx T/2$  shown in Fig. 6(c) and 7(b). In other words, there could be several possible combinations of Mod[T<sub>DCO,MIN</sub>, T] and ΔT<sub>PRBS,MAX</sub>

TABLE I. TDC Technique Comparison & Summary

| Work                      | [45]                      | [45]                                                         | This Work                                                       | [59]                 | [60]                 | [61]                 | [62]                 | [63]                |

|---------------------------|---------------------------|--------------------------------------------------------------|-----------------------------------------------------------------|----------------------|----------------------|----------------------|----------------------|---------------------|

| m 1 1                     | TCAS-I'22                 | TCAS-I'22                                                    | 22                                                              | JSSC'14              | JSSC'18              | TCAS-I'20            | Access'21            | TCAS-I'22           |

| Technology                | 22 nm                     | 22 nm                                                        | 22 nm                                                           | 90 nm                | 65 nm                | 40 nm                | 28 nm                | 65 nm               |

| Technique                 | Syn. RSA                  | Asyn. RSA                                                    | Asyn. RSA w/<br>SAVR                                            | SRO                  | CT ΔΣ                | Flash ΔΣ             | CCRO                 | URFC &<br>Vernier   |

| Clock Gen.                | PLL & PI                  | DCO                                                          | DCO                                                             | No Info.             | PLL                  | No Info.             | Ring OSC             | DLL                 |

| Clock Power               | 25 mW                     | 3 mW                                                         | 3.1 mW                                                          | No Info.             | No Info.             | No Info.             | No Info.             | No Info.            |

| Sampling<br>Frequency     | 4 GS/s<br>≈ 1/T           | 4 GS/s<br>≈ $1/T_{DCO,AVG}$                                  | 7.8  GS/s<br>$\approx 1/T_{DCO,AVG}$                            | 750 MS/s             | 250 MS/s             | 50 MS/s              | 125 MS/s             | 200 MS/s            |

| Sampling<br>Phases        | 8                         | 8                                                            | 8                                                               | N/A                  | N/A                  | N/A                  | 126                  | 16                  |

| Dynamic                   | 10 ns ~ 1 μs              | 10 ns ~ 1 μs                                                 | 10 ns ~ 1 μs                                                    | 4 ns                 | 2 ns                 | 320 ps               | 7.8 ns               | 2.5 μs              |

| Range (DR)                | (Scaled to T)             | (Scaled to T)                                                | (Scaled to T)                                                   | (Fixed)              | (Fixed)              | (Fixed)              | (Fixed)              | (Fixed)             |

| ENOB                      | 10                        | $12 @ N_{DCO} \approx 2^{24}$                                | $12 @ N_{DCO} \approx 2^{19}$                                   | 13.2                 | 13.1                 | 10.7                 | 9.29                 | 14.74               |

|                           | (Fixed)                   | $14 @ N_{DCO} \approx 2^{28}$                                | $14 @ N_{DCO} \approx 2^{23}$                                   | (Fixed)              | (Fixed)              | (Fixed)              | (Fixed)              | (Fixed)             |

| Effective                 | 9.76 ps ~ 976 ps          | 0.61 ps ~ 61 ps                                              | 0.61 ps ~ 61 ps                                                 | 0.315 ps             | 0.182 ps             | 0.147 ps             | 12.5 ps              | 91.4 ps             |

| Resolution *              | @ 10 ENOB                 | @ 14 ENOB                                                    | @ 14 ENOB                                                       | (Fixed)              | (Fixed)              | (Fixed)              | (Fixed)              | (Fixed)             |

| Conversion-<br>Rate (CVR) | 32 kHz<br>@ 10 ENOB       | 2 kHz<br>@ 12 ENOB                                           | 120 kHz<br>@ 12 ENOB                                            | 2 MHz                | 2 MHz                | 5 MHz                | 125 MHz              | 1 MHz               |

| TDC Power                 | 1.3 mW                    | 1.3 mW                                                       | 1.5 mW                                                          | 1.5 mW               | 8.4 mW               | 1.32 mW              | 12.3 mW              | 51.4 mW             |

| TDC FoM **                | 39.7 pJ/step<br>@ 10 ENOB | 159 pJ/step<br>@ 12 ENOB                                     | 3.1 pJ/step<br>@ 12 ENOB                                        | 0.08 pJ/step         | 0.47 pJ/step         | 0.16 pJ/step         | 0.16 pJ/step         | 1.88 pJ/step        |

| TDC Area                  | 0.01 mm <sup>2</sup>      | 0.01 mm <sup>2</sup>                                         | 0.01 mm <sup>2</sup>                                            | 0.02 mm <sup>2</sup> | $0.055 \text{ mm}^2$ | 0.08 mm <sup>2</sup> | $0.078 \text{ mm}^2$ | $0.15 \text{ mm}^2$ |

| Linearity                 | RSA Self-                 | RSA Self-                                                    | RSA Self-                                                       | Off-Chip             | No Info.             | Off-Chip             | On-Chip              | United Ref.         |

| Calibration               | Calibration               | Calibration                                                  | Calibration                                                     | Correction           |                      | Correction           | Correction           | Correction          |

| Post Noise                | 1-bit Digital             | 1-bit Digital                                                | 1-bit Digital                                                   | Digital Phase        | PLL Loop             | High-order           | No Info.             | No Info.            |

| Filtering                 | Accumulator               | Accumulator                                                  | Accumulator                                                     | Filter               | Filter               | Digital Filter       |                      |                     |

| Expect Eq.                | (10) in [45]              | (15) in [45]                                                 | (7)                                                             | N/A                  | N/A                  | N/A                  | N/A                  | N/A                 |

| Variance Eq.              | (11) in [45]              | (7) in [45]                                                  | (17)                                                            | N/A                  | N/A                  | N/A                  | N/A                  | N/A                 |

| Parameters<br>@ T =250 ps | OSR = 1                   | $T_{DCO,MIN} \approx T/2$<br>$\Delta T_{PRBS,MAX} \approx T$ | $T_{DCO,MIN} \approx T/2$<br>$\Delta T_{PRBS,MAX} \approx T/32$ | N/A                  | N/A                  | N/A                  | N/A                  | N/A                 |

<sup>\*</sup> Effective Resolution =  $DR/(2^{ENOB})$ . \*\* TDC FoM = (TDC Power)/(2·BW·2<sup>ENOB</sup>) = (TDC Power)/(CVR·2<sup>ENOB</sup>).

which can cause severe variance additions. And, this is the primary downside of the SAVR technique associated with the upside of high conversion-rate improvement and negligible extra power cost for an asynchronous RSA measurement system. Fortunately, the approximation, i.e., (17), developed in this research can efficiently predict the quantization-noise power under any combination of the signal and circuit parameters, including all τ/T, N<sub>DCO</sub>, T<sub>DCO,MIN</sub>, ΔT<sub>PRBS,MAX</sub>, and T. In sum, the verified results from both RSA simulation and theoretical approximation conclude that SAVR can offer favorable variance reduction under the minimum requirement of having  $Mod[T_{DCO,MIN}, T] \in [0.25 \cdot T, 0.75 \cdot T]$  with  $\Delta T_{PRBS,MAX} \leq T/4$ . Also, note that  $Mod[T_{DCO,MIN}, T] \approx T/2$ with  $T/32 < \Delta T_{PRBS,MAX} \le T/4$  can offer the maximum flattened variance distribution across the entire τ/T dynamic

Multiple case studies in this section are summarized in Fig. 7(c), including I.I.D., VR, and VA scenarios as discussed. Note that each red dot for a certain  $N_{DCO}$  approximately on the I.I.D. theoretical variance line is obtained from (10) by averaging  $2^8$  (=  $N_{EXP}$ ) grey dots in Fig. 7(c). All theoretical approximation (i.e., blue lines) and simulation (i.e., red dots) results are well aligned and all follow the weak law of large numbers to perform a consistent variance degradation at -3 dBW per octave of  $N_{DCO}$ .

### V. SUMMARY AND FUTURE WORK

The key signal-and-circuit parameters are summarized below for enabling the RSA with SAVR technique:  $\tau$  (converted from  $\Delta t$ ) is the quantity under each measurement; T (converted from  $\Delta t_{MAX}$ ) is the dynamic range under each measurement; T<sub>DCO,MIN</sub> is the deterministic portion of each DCO period;  $\Delta T_{PRBS,MAX}$  is the PDF span of the stochastic portion of each DCO period; the relations among T<sub>DCO,MIN</sub>,  $\Delta T_{PRBS,MAX}$ , and T are the key parameters to perform effective SAVR; N<sub>DCO</sub> is the total number of the samples; N<sub>EXP</sub> is not involved in the circuit implementation but required for the software/lab experiments to statistically verify the theoretical formulas and the performance estimations of the RSA-based technique.

The comparison of the RSA-based TCSPC systems in [45] and this paper is summarized in Table I based on the circuit simulations along with the silicon measurement results of multiple state-of-the-art TDC implementations. Note that the primary focus of this paper is to comprehensively elaborate the probability theories and implementable mathematical models of the SAVR technique, so the intent of this comparison is to cover a bigger picture of the modern TDC evolution in standard CMOS process nodes; not to show unfair competition by taking advantage of simulation results.

Overall, the SAVR technique enhances the conversionrate by 62× (up to 120 kHz) with 7% power overhead compared to those of the ordinary RSA-based TDC in [45]. This improvement is also reflected by the energy efficiency of 3.1 pJ/step. To further broaden the potential of RSA in the quantum applications, a couple of VR related techniques are under investigation. One is to stretch the limit of SAVR, i.e., scaling down the  $\Delta T_{PRBS,MAX}$  and/or LSB capacitance for the DCO frequency modulation toward the limit of advanced CMOS process technology, which can pretty much offer additional  $4\times$  conversion-rate improvement without any extra power consumption. The other is to utilize a well-controlled VR technique with the downside of higher power/area overhead [50]. The forthcoming research and silicon-photonics realization will take the complementary benefits of these VR techniques to boost the conversion-rate of RSA up to the range of MHz and accordingly to achieve sub-pJ/step energy efficiency.

### **REFERENCES**

- [1] W. Becker, Advanced Time-Correlated Single Photon Counting Techniques, Berlin, Germany: Springer, 2005.

- [2] W. Becker, *The bh TCSPC Handbook*, 7th Ed., Berlin, Germany: Becker & Hickl GmbH, 2017.

- [3] B. Markovic, S. Tisa, F. A. Villa, A. Tosi, and F. Zappa, "A high-linearity, 17 ps precision time-to-digital converter based on a single-stage Vernier delay loop fine interpolation," *IEEE Tran. Circuits and Systems I: Regular Papers*, vol. 60, no. 3, pp. 557–569, March 2013.

- [4] N. A. W. Dutton, S. Gnecchi, L. Parmesan, A. J. Holmes, B. Rae, L. A. Grant, and R. K. Henderson, "A time-correlated single-photon-counting sensor with 14GS/s histogramming time-to-digital converter," in *IEEE ISSCC Dig. Tech. Papers*, San Francisco, CA, USA, 2015, pp. 204–205.

- [5] M. Wahl, "Time-correlated single photon counting," PicoQuant GmbH, Berlin, Germany, 2014. [Online]. Available: <a href="https://www.picoquant.com/images/uploads/page/files/7253/technote-tcspc.pdf">https://www.picoquant.com/images/uploads/page/files/7253/technote-tcspc.pdf</a>

- [6] F. Villa, R. Lussana, D. Bronzi, S. Tisa, A. Tosi, F. Zappa, A. D. Mora, D. Contini, D. Durini, S. Weyers, and W. Brockherde, "CMOS imager with 1024 SPADs and TDCs for single-photon timing and 3-D timeof-flight," *IEEE J. Sel. Topics in Quantum Electronics*, vol. 20, no. 6, pp. 364–373, Dec. 2014.

- [7] C. Niclass, C. Favi, T. Kluter, M. Gersbach, and E. Charbon, "A 128 x 128 single-photon image sensor with column-level 10-bit time-to-digital converter array," *IEEE J. Solid-State Circuits*, vol. 43, no. 12, pp. 2977–2989, Dec. 2008.

- [8] D. Tamborini, M. Buttafava, A. Ruggeri, and F. Zappa, "Compact, low-power and fully reconfigurable 10 ps resolution, 160 μs range, time-resolved single-photon counting system," *IEEE Sensors J.*, vol. 16, no. 10, pp. 3827–3833, May 2016.

- [9] M. Beck, "Comparing measurements of g<sup>(2)</sup>(0) performed with different coincidence detection techniques," *J. Optical Society of America B*, vol. 24, no. 12, pp. 2972–2978, Dec. 2007.

- [10] M. Beck, Quantum Mechanics Theory and Experiment, New York, NY, USA: Oxford University Press, 2012.

- [11] U. Leonhard, Measuring the Quantum State of Light, Cambridge, UK: Cambridge University Press, 1997.

- [12] C. Spee, J. I. de Vicente, B. Kraus, "Remote entanglement preparation," *Phys. Rev. A*, vol. 88, 010305, July 2013.

- [13] C. H. Bennett, "Quantum cryptography using any two nonorthogonal states," *Phys. Rev. Lett.*, vol. 68, pp. 3121–3124, May 1992.

- [14] B. Slutsky, R. Rao, P.-C. Sun, and Y. Fainman, "Security of quantum cryptography against individual attacks," *Phys. Rev. A*, vol. 57, pp. 2383–2398, April 1998.

- [15] M. Hillery, V. Bužek, and André Berthiaume, "Quantum secret sharing," Phys. Rev. A, vol. 59, no. 3, pp. 1829–1834, March 1999.

- [16] L. H. C. Braga, L. Gasparini, L. Grant, R. K. Henderson, N. Massari, M. Perenzoni, D. Stoppa, and R. Walker, "A fully digital 8 × 16 SiPM array for PET applications with per-pixel TDCs and real-time energy output," *IEEE J. Solid-State Circuits*, vol. 49, no. 1, pp. 301–314, Jan. 2014.

- [17] A. S. Yousif and J. W. Haslett, "A fine resolution TDC architecture for next generation PET imaging," *IEEE Trans. Nuclear Science*, vol. 54, no. 5, pp. 1574–1582, Oct. 2007.

- [18] L. Gasparini, M. Zarghami, H. Xu, L. Parmesan, M. M. Garcia, M. Unternährer, B. Bessire, A. Stefanov, D. Stoppa, and M. Perenzoni, "A 32×32-pixel time-resolved single-photon image sensor with 44.64µm pitch and 19.48% fill-factor with on-chip row/frame skipping features reaching 800kHz observation rate for quantum physics applications," in *IEEE ISSCC Dig. Tech. Papers*, San Francisco, CA, USA, 2018, pp. 98–99.

- [19] C. Veerappan, J. Richardson, R. Walker, D.-U. Li, M. W. Fishburn, Y. Maruyama, D. Stoppa, F. Borghetti, M. Gersbach, R. K. Henderson, and E. Charbon, "A 160×128 single-photon image sensor with on-pixel 55ps 10b time-to-digital converter," in *IEEE ISSCC Dig. Tech. Papers*, San Francisco, CA, USA, 2011, pp. 312–313.

- [20] R. M. Field, S. Realov, and K. L. Shepard, "A 100 fps, time-correlated single-photon-counting-based fluorescence-lifetime imager in 130 nm CMOS," *IEEE J. Solid-State Circuits*, vol. 49, no. 4, pp. 867–880, April 2014.

- [21] M. Perenzoni, D. Perenzoni, and D. Stoppa, "A 64 × 64-pixels digital silicon photomultiplier direct TOF sensor with 100-MPhotons/s/pixel background rejection and imaging/altimeter mode with 0.14% precision up to 6 km for spacecraft navigation and landing," *IEEE J. Solid-State Circuits*, vol. 52, no. 1, pp. 151–160, Jan. 2017.

- [22] H. Seo, H. Yoon, D. Kim, J. Kim, S.-J. Kim, J.-H. Chun, and J. Choi, "A 36-channel SPAD-integrated scanning LiDAR sensor with multievent histogramming TDC and embedded interference filter," in *IEEE Symposium on VLSI Circuits*, Honolulu, HI, USA, 2020, pp. 1–2.

- [23] T. Rahkonen and J. Kostamovaara, "The use of stabilized CMOS delay lines for the digitization of short time intervals," *IEEE J. Solid-State Circuits*, vol. 28, no. 8, pp. 887–894, Aug. 1993.

- [24] K. Karadamoglou, N. P. Paschalidis, E. Sarris, N. Stamatopoulos, G. Kottaras, and V. Paschalidis, "An 11-bit high-resolution and adjustable-range CMOS time-to-digital converter for space science instruments," *IEEE J. Solid-State Circuits*, vol. 39, no. 1, pp. 214–222, Jan. 2004.

- [25] Y. Liu, U. Vollenbruch, Y. Chen, C. Wicpalek, L. Maurer, Z. Boos, and R. Weigel, "Multi-stage pulse shrinking time-to-digital converter for time interval measurements," in *Proc. Eur. Microwave Integrated Circuits Conf.*, Munich, Germany, 2007, pp. 267–270.

- [26] C. Ljuslin, J. Christiansen, A. Marchioro, and O. Klingsheim, "An integrated 16-channel CMOS time to digital converter," *IEEE Trans. Nuclear Science*, vol. 41, no. 4, pp. 1104–1108, Aug. 1994.

- [27] R. B. Staszewski, S. Vemulapalli, P. Vallur, J. Wallberg, and P. T. Balsara, "1.3 V 20 ps time-to-digital converter for frequency synthesis in 90-nm CMOS," *IEEE Tran. Circuits and Systems II: Express Briefs*, vol. 53, no. 3, pp. 220–224, March 2006.

- [28] Y. Arai and M. Ikeno, "A time digitizer CMOS gate-array with a 250 ps time resolution," *IEEE J. Solid-State Circuits*, vol. 31, no. 2, pp. 212–220, Feb. 1996.

- [29] L. Vercesi, A. Liscidini, and R. Castello, "Two-dimensions Vernier time-to-digital converter," *IEEE J. Solid-State Circuits*, vol. 45, no. 8, pp. 1504–1512, Aug. 2010.

- [30] C.-S. Hwang, P. Chen, and H.-W. Tsao, "A high-precision time-to-digital converter using a two-level conversion scheme," *IEEE Trans. Nuclear Science*, vol. 51, no. 4, pp. 1349–1352, Aug. 2004.

- [31] P. Dudek, S. Szczepanski, and J. V. Haltfield, "A high-resolution CMOS time-to-digital converter utilizing a Vernier delay line," *IEEE J. Solid-State Circuits*, vol. 35, no. 2, pp. 240–247, Feb. 2000.

- [32] M. Zanuso, P. Madoglio, S. Levantino, C. Samori, and A. L. Lacaita, "Time-to-digital converter for frequency synthesis based on a digital bang-bang DLL," *IEEE Trans. Circuits and Systems I: Regular Papers*, vol. 57, no. 3, pp. 548–555, Mar. 2010.

- [33] A. Mantyniemi, T. Rahkonen, and J. Kostamovaara, "A CMOS time-to-digital converter (TDC) based on a cyclic time domain successive approximation interpolation method," *IEEE J. Solid-State Circuits*, vol. 44, no. 11, pp. 3067–3078, Nov. 2009.

- [34] J. P. Jansson, A. Mäntyniemi, and J. Kostamovaara, "A CMOS timeto- digital converter with better than 10 ps single-shot precision," *IEEE J. Solid-State Circuits*, vol. 41, no. 6, pp. 1286–1296, June 2006.

- [35] J. P. Jansson, A. Mäntyniemi, and J. Kostamovaara, "Synchronization in a multilevel CMOS time-to-digital converter," *IEEE Trans. Circuits*

- and Systems I: Regular Papers, vol. 56, no. 8, pp. 1622–1634, Aug. 2009

- [36] E. Raisanen-Ruotsalainen, T. Rahkonen, and J. Kostamovaara, "An integrated time-to-digital converter with 30-ps single-shot precision," *IEEE J. Solid-State Circuits*, vol. 35, no. 10, pp. 1507–1510, Oct. 2000.

- [37] B. K. Swann, B. J. Blalock, L. G. Clonts, D. M. Binkley, J. M. Rochelle, E. Breeding, and K. M. Baldwin, "A 100-ps time-resolution CMOS time-to-digital converter for positron emission tomography imaging applications," *IEEE J. Solid-State Circuits*, vol. 39, no. 11, pp. 1839–1852, Nov. 2004.

- [38] E. Temporiti, C. Weltin-Wu, D. Baldi, M. Cusmai, and F. Svelto, "A 3.5 GHz wideband ADPLL with fractional spur suppression through TDC dithering and feedforward compensation," *IEEE J. Solid-State Circuits*, vol. 45, no. 12, pp. 2723–2736, Dec. 2010.

- [39] M. A. Abas, G. Russell, and D. J. Kinniment, "Embedded highresolution delay measurement system using time amplification," *IET Computers & Digital Techniques*, vol. 1, no. 2, pp. 77–86, Mar. 2007.

- [40] M. Lee and A. A. Abidi, "A 9 b, 1.25 ps resolution coarse-fine time-to-digital converter in 90 nm CMOS that amplifies a time residue," *IEEE J. Solid-State Circuits*, vol. 43, no. 4, pp. 769–777, Apr. 2008.

- [41] B. Tong, W. Yan, and X. Zhou, "A constant-gain time-amplifier with digital self-calibration," in *Proc. IEEE Int. Conf. ASIC*, Changsha, Hunan, China, 2009, pp. 1133–1136.

- [42] J. Kalisz, "Review of methods for time interval measurements with picosecond resolution," *Metrologia*, vol. 41, no. 1, pp. 17–32, Feb. 2004.

- [43] S.-K. Shin, J. C. Rudell, D. C. Daly, C. E. Muñoz, D.-Y. Chang, K. Gulati, H.-S. Lee, and M. Z. Straayer, "A 12 bit 200 MS/s zero-crossing-based pipelined ADC with early sub-ADC decision and output residue background calibration," *IEEE J. Solid-State Circuits*, vol. 49, no. 6, pp. 1366–1382, June 2014.

- [44] S.-H. W. Chiang, H. Sun, and B. Razavi, "A 10-bit 800-MHz 19-mW CMOS ADC," *IEEE J. Solid-State Circuits*, vol. 49, no. 4, pp. 935– 949, April 2014.

- [45] T. Wu, R. Yang, and T.-C. Hsueh, "Random sampling-and-averaging techniques for single-photon arrival-time detections in quantum applications: theoretical analysis and realization methodology," *IEEE Trans. Circuits and Systems I: Regular Papers*, vol. 69, no. 4, pp. 1452–1465, April 2022.