# MoS<sub>2</sub> Synapses with Ultra-low Variability and Their Implementation in Boolean Logic

Adithi Krishnaprasad,<sup>§,#</sup> Durjoy Dev,<sup>§,#</sup> Sang Sub Han,<sup>§,#</sup> Yaqing Shen,<sup>||</sup> Hee-Suk Chung,<sup>†</sup> Tae-Sung Bae,<sup>†</sup> Changhyeon Yoo,<sup>§</sup> Yeonwoong Jung,<sup>§,#,†</sup> Mario Lanza<sup>¶</sup> and Tania Roy<sup>§,#,†,\*</sup>

<sup>§</sup>NanoScience Technology Center, University of Central Florida, Orlando FL 32826, USA

<sup>#</sup>Department of Electrical and Computer Engineering, University of Central Florida, Orlando FL 32816, USA

<sup>†</sup>Department of Materials Science and Engineering, University of Central Florida, Orlando FL 32816, USA

<sup>||</sup>Institute of Functional Nano & Soft Materials, Soochow University, Suzhou, 215123, China

<sup>¶</sup>Analytical Research Division, Korea Basic Science Institute, Jeonju, Jeollabuk-do, 54907, South Korea

<sup>¶</sup>Department of Material Science and Engineering, King Abdullah University of Science and Technology, Thuwal 23955, Saudi Arabia

\*Corresponding author: [tania.roy@ucf.edu](mailto:tania.roy@ucf.edu)

**ABSTRACT:** Brain-inspired computing enabled by memristors has gained prominence over the years due to their nano-scale footprint and reduced complexity for implementing synapses and neurons. The demonstration of complex neuromorphic circuits using conventional materials systems has been limited by high cycle-to-cycle (C-C) and device-to-device (D-D) variability.

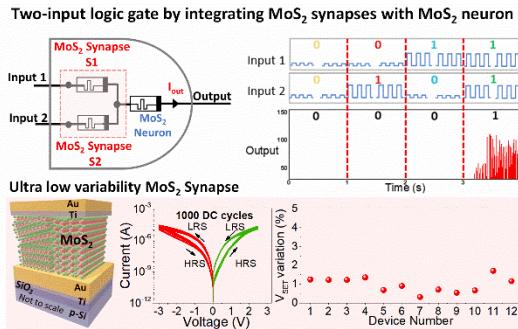

Two-dimensional (2D) materials have been used to realize transparent, flexible, ultra-thin memristive synapses for neuromorphic computing, but with limited knowledge on the statistical variation of devices. In this work, we demonstrate ultra-low variability synapses using chemical vapor deposited 2D MoS<sub>2</sub> as the switching medium with Ti/Au electrodes. These devices, fabricated using a transfer-free process, exhibit ultra-low variability in SET voltage, RESET power distribution and in synaptic weight update characteristics. This ultra-low variability is enabled by the interface rendered by Ti/Au top contact on the Si-rich MoS<sub>2</sub> layers of mixed orientation, corroborated by transmission electron microscopy (TEM), electron energy loss spectroscopy (EELS) and x-ray photoelectron spectroscopy (XPS). TEM images further confirm the stability of the device stack even after subjecting the device to 100 SET-RESET cycles. Additionally, we implement logic gates by monolithic integration of MoS<sub>2</sub> synapses with MoS<sub>2</sub> leaky integrate-and-fire (LIF) neurons to show the viability of these devices for non-von Neumann computing.

KEYWORDS: MoS<sub>2</sub>, low C-C variability, low D-D variability, interface mediated, non-volatile, memristor and threshold logic gate

## INTRODUCTION

Neuromorphic computing, inspired by the human brain's cognitive processing capability has found its applications in artificial neural networks (ANNs) and machine learning. The neuro-inspired algorithms involve large scale vector matrix operations which require parallelism and in-memory computing at the device and architecture levels for improved efficiency. Memristors fabricated in cross-bar configuration drastically decrease the complexity of vector matrix multiplication, thus increasing the computational speed, thereby enabling the realization of high-density circuits.<sup>1</sup> To this end, memristors are preferred over conventional complementary metal oxide semiconductor (CMOS) circuitry for the implementation of synapses, the basic functional

block of neuro-inspired architectures.<sup>2-3</sup> However, a major obstacle hindering the large scale implementation of memristors for the state-of-the-art memory, logic and computing applications is the presence of high C-C variability and D-D variability due to the intrinsic stochasticity of their switching process.<sup>4</sup> This stochasticity causes variations in the conductance for a single switching cycle between different devices (D-D variability) and within an individual device (C-C variability).<sup>5</sup> Various techniques and materials platforms have been explored to obtain low C-C and D-D variability.<sup>6-11</sup> Some demonstrations utilize a transistor connected serially to the memristor to regulate the switching properties.<sup>12-14</sup> Another interesting technique involves the implementation of ratioed memristor, where two memristors represent a single memristor cell and the ratio of the two resistances is used to encode information.<sup>15</sup> However, these techniques limit scalability and increase design complexity. Therefore, it is necessary to design synapses that exhibit low C-C and D-D variability without the complex peripheral circuitry. Electrode engineering can be used as an efficient method to obtain uniform synapses.<sup>10</sup> Yeon *et al.* employed a metallurgical technique where an Ag-Cu alloyed electrode replaces Ag as the top electrode in amorphous Si (a-Si) based electro-chemical metallization (ECM) memristor to obtain high uniformity in DC cycling and analog weight update characteristics.<sup>10</sup> A low C-C and D-D variability in synapses allows reliable circuit level implementations, such as in perceptrons for pattern recognition and in implementations for in-memory computing. One of the first demonstrations of a single layer perceptron employed Pt/TiO<sub>2-x</sub>/Ti crossbars.<sup>16</sup> Due to the high D-D variability in this implementation, off-chip wires were required to disconnect individual memristors from the crossbars during the forming process, which is cumbersome. Researchers have used stack engineering to circumvent D-D variability. For instance, Al<sub>2</sub>O<sub>3</sub>/TiO<sub>2-x</sub> was used as the switching medium for crossbars in a neural network used to perform classification of 3 ×

3-pixel gray-scale image.<sup>17</sup> It is worth noting that the fundamental description of the NNs can be a mathematical model of a functional unit called neuron which operates in all or no spiking fashion when a threshold is reached. This model and its hardware implementation is called as Threshold Logic Gate (TLG).<sup>18</sup> The neuron computes the weighted sum of its inputs (synaptic weights) and produces the spikes when the threshold is reached.<sup>18</sup> Therefore, the TLG can be utilized for implementing either NN applications by realization of single layer perceptron or in-memory computing applications *via* Boolean logic implementations. Realizing in-memory computing architecture with CMOS technology is wrought with unsatisfactory performance, low productivity and high cost when compared with von Neumann computing devices.<sup>19</sup> In contrast, memristive devices allow low-power and low-cost Boolean logic implementations useful for in-memory computing, where the device characteristics are consistent with the requirements of edge computing devices.<sup>19-20</sup> Additionally, the TLGs built with memristors can be utilized for reconfigurable processing architectures. Memristor-based circuits can replace bulky CMOS-based architectures and through precise combination of signals, the basic circuitry can be easily modified to implement various logic gates that is convenient to solve individual computational problems.<sup>21</sup>

Recently, two-dimensional (2D) materials have been considered for electronic and opto-electronic applications due to their low power consumption, flexibility, transparency and thermal stability.<sup>22-23</sup> Semiconducting 2D materials have been used successfully as the active layer in several demonstrations of synaptic devices. Vertical memristive devices have been realized with exfoliated MoS<sub>2</sub> nanosheets and MoS<sub>2</sub>-GO composite structures<sup>24-27</sup>, h-BN<sup>28</sup>, WS<sub>2</sub>,<sup>29-30</sup> and WSe<sub>2</sub>.<sup>31</sup> However, for a potential neuromorphic hardware, it is essential to realize synapses on a wafer scale. In that direction, non-volatile resistive switching is observed in chemical vapor deposition (CVD)-grown 2D materials like MoSe<sub>2</sub>, WS<sub>2</sub>, WSe<sub>2</sub>,<sup>32</sup> h-BN<sup>9, 33-34</sup> and MoS<sub>2</sub>.<sup>32, 35-36</sup>

Although a huge body of literature exists on the demonstration of memristive/synaptic behavior using 2D materials, studies on C-C and D-D variability of 2D materials-based devices are scarce. Chen *et al.* reported low C-C and D-D variability in SET and RESET voltages with CVD h-BN as the switching medium.<sup>9</sup> This report on h-BN based synapses exposes the inherent nature of 2D materials to produce devices with high uniformity, which is necessary for realizing high density electronic circuits. However, for unraveling the true potential of a materials system, it is imperative to not be limited by the demonstration of a single device. Also, it is essential for devices to demonstrate low D-D and C-C variability for reliable circuit implementations. Reports on circuit implementations with 2D materials-based synapses have been limited to the modelling of multi-layer perceptrons wherein the potential of the emerging technology is suggested through simulations.<sup>9</sup>

In this work, we demonstrate MoS<sub>2</sub> based synapses with Ti/Au as the bottom and top electrodes. These devices exhibit ultra-low C-C and D-D variability in SET voltage and RESET power distributions. The synapses exhibit low C-C and D-D variability in weight update characteristics as well, comparable with the industry compatible a-Si based synapses.<sup>10</sup> We demonstrate the existence of 26 distinct conductance states in these devices, with a retention of at least 300 s for each of these states. These devices exhibit excellent endurance by maintaining a consistent ON/OFF ratio for 1000 DC SET-RESET cycles. These exemplary characteristics observed in MoS<sub>2</sub> based devices can be attributed to the underlying switching mechanism which is mediated by the interface between MoS<sub>2</sub> and Ti, corroborated by their area-dependent resistance scaling. Temperature dependent I-V measurements confirm space charge limited current (SCLC) to be the dominant transport mechanism. Further, the TEM images show no degradation in the stressed device indicating the stability of the stack. We integrate these MoS<sub>2</sub> synapses with MoS<sub>2</sub>

LIF neurons<sup>37</sup> to realize AND, OR and NOT logic gates. This demonstration of Boolean logic using 2D materials-based synapses and neurons shows the feasibility of 2D materials for large-scale circuit implementations.

## RESULTS AND DISCUSSION

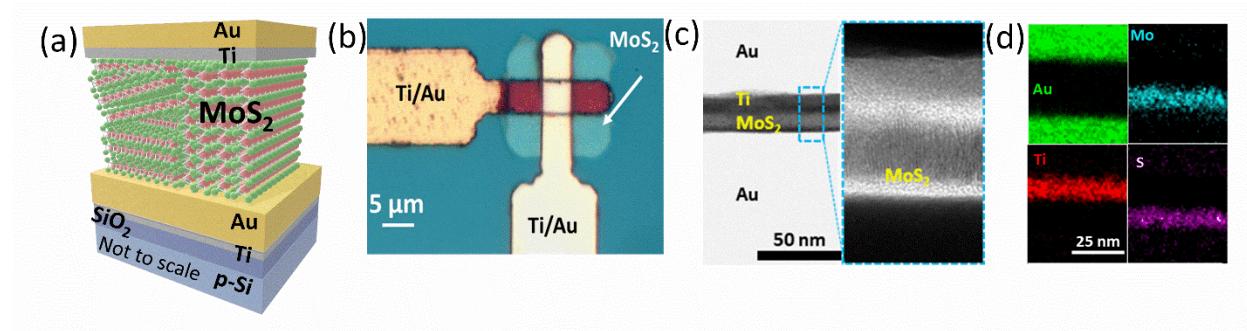

The schematic of the MoS<sub>2</sub> synapse is shown in **Figure 1a**. The devices are fabricated by UV lithography on MoS<sub>2</sub> films grown by chemical vapor deposition (CVD), using a transfer-free process, and the fabrication details are provided in the methods section. The optical microscope image of a typical Ti/Au/MoS<sub>2</sub>/Ti/Au (bottom to top) device is shown in **Figure 1b**. The active area of the fabricated devices is systematically varied from  $2 \times 2 \mu\text{m}^2$  to  $50 \times 50 \mu\text{m}^2$ . Cross-sectional TEM is utilized to assess the device stack as shown in **Figure 1c**. The TEM image shows the layered growth of MoS<sub>2</sub> of thickness  $\sim 10$  nm. Further, the chemical composition of the device stack is analyzed by the elemental energy dispersive X-ray spectroscopy (EDS). The EDS maps clearly reveal the presence of MoS<sub>2</sub>, bottom electrode (Au) and top electrode (Ti/Au) as shown in **Figure 1d**.

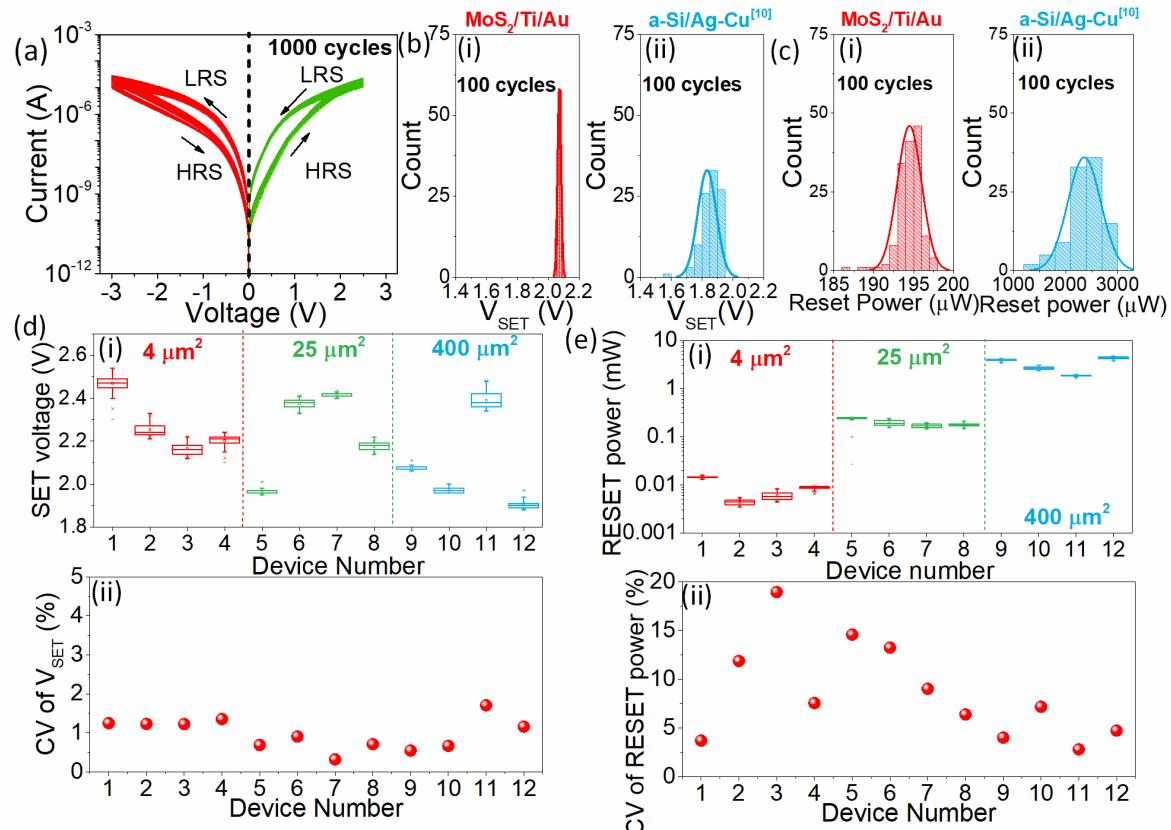

The devices are probed in vacuum at a base pressure of  $10^{-4}$  mBar for electrical characterization. **Figure 2a** shows the DC I-V characteristics, demonstrating the non-volatile switching of the MoS<sub>2</sub> devices with Ti/Au electrodes. Here the I-V characterization is executed on device of area  $5 \times 5 \mu\text{m}^2$ . To perform this experiment, we apply the bias voltage to the bottom electrode while keeping the top electrode at 0 V during these measurements. These devices do not exhibit abrupt transition from the high resistance state (HRS) to low resistance state (LRS), unlike filamentary memristive devices.<sup>28, 33-34, 38-44</sup> Instead, the devices exhibit a smooth transition from HRS to LRS, hinting at the role played by the interface in the non-volatile switching behavior.

Therefore, we apply a voltage compliance (VC) of 2.5 V for SET and -3 V for RESET, in contrast with the current compliance (CC) applied in filamentary memristive devices during SET, to test the endurance of the device through 1000 DC cycles. To evaluate the low variability evident through the 1000 cycles, the OFF and ON states are extracted at  $V_{\text{read}} = 0.25$  V, as shown in the supplementary information (**Figure S1**). The MoS<sub>2</sub> device exhibits constant ON and OFF states throughout the 1000 DC cycles indicating their ultra-low C-C variability and endurance. It should be noted that the endurance of the device is characterized under a harsh DC cycling of 1000 times, as opposed to a milder pulsed cycling. To establish the necessity of MoS<sub>2</sub> in resistive switching, we fabricate a test structure consisting of Ti/Au top electrode deposited on a Ti/Au bottom electrode. **Figure S2** shows the shorted characteristics of the test structure as expected from a metal-on-metal structure. It should be noted that the top Ti/Au electrodes are patterned and deposited after subjecting the bottom Ti/Au electrodes to the exact processing steps that were used for obtaining MoS<sub>2</sub> films for this study. To evaluate the variation in the SET voltage and RESET power, our MoS<sub>2</sub> device is cycled for 100 times by enforcing a CC keeping the maximum current density at 40 A/cm<sup>2</sup>. The voltage at which the current through the device reaches this maximum current density is considered to be the SET voltage. The RESET power is calculated using the formula  $P = V \times I$ , where  $I$  is the maximum RESET current, and  $V$  is the maximum RESET voltage applied. Devices of area  $2 \times 2 \mu\text{m}^2$  are probed for comparing the device performance with industry compatible a-Si/Ag-Cu devices, reported by Yeon *et al.*<sup>10</sup> for SET voltage and RESET power variation as shown in **Figures 2(b-c)**. Recall that the performance of a-Si devices is improved by replacing the Ag top electrode with alloyed Ag-Cu to yield high uniformity in SET and RESET processes.<sup>10</sup> The histogram of the SET voltage variation of our MoS<sub>2</sub> device is shown in **Figure 2b(i)**. The device exhibits a narrow distribution in the SET voltage with a range of only

0.04 V. In contrast, the histogram of SET voltage variation in a-Si/Ag-Cu device (**Figure 2b(ii)**) exhibits a range of 0.45 V, confirming the exemplary ultra-low C-C variability of MoS<sub>2</sub> based devices. Additionally, the RESET power distribution of MoS<sub>2</sub> device and a-Si/Ag-Cu device is shown in **Figure 2c**. Additionally, it is essential to investigate if the narrow distribution in SET voltages and RESET power is consistent over multiple devices. Therefore, a statistical analysis is performed over 12 different devices of areas  $2 \times 2 \mu\text{m}^2$ ,  $5 \times 5 \mu\text{m}^2$  and  $20 \times 20 \mu\text{m}^2$ . Four devices of each area are measured to obtain the SET voltage and RESET power variation. The SET voltage distribution is obtained by enforcing CC that corresponds to a maximum current density of 40 A/cm<sup>2</sup>. Therefore, for the devices with area of  $4 \mu\text{m}^2$ ,  $25 \mu\text{m}^2$  and  $400 \mu\text{m}^2$ , a CC of 1.6  $\mu\text{A}$ , 10  $\mu\text{A}$  and 160  $\mu\text{A}$  is enforced respectively. The individual DC characteristics of these devices are shown in **Figure S3**. The SET voltage distribution for each device is plotted in **Figure 2d**. Similarly, the RESET powers of the 12 devices are plotted in **Figure 2e**. The D-D variability is assessed by extracting the coefficient of variation ( $CV = \text{standard deviation (SD)}/\text{mean } (\mu)$ )<sup>45</sup> for both SET voltage and RESET power distribution over 12 different devices. The minimum C-C variability for SET voltage and RESET power is observed to be 0.32% and 2.79%, indicating ultra-low variability. Extracting  $CV$  over the entire sample set elucidates the low D-D variability observed in MoS<sub>2</sub> devices. The D-D variability increases to only 1.7% in SET voltage variation over the 12 devices. It is worth noting that the  $CV$  in SET voltage variation does not exceed 2% indicating the low D-D variability of MoS<sub>2</sub> devices.

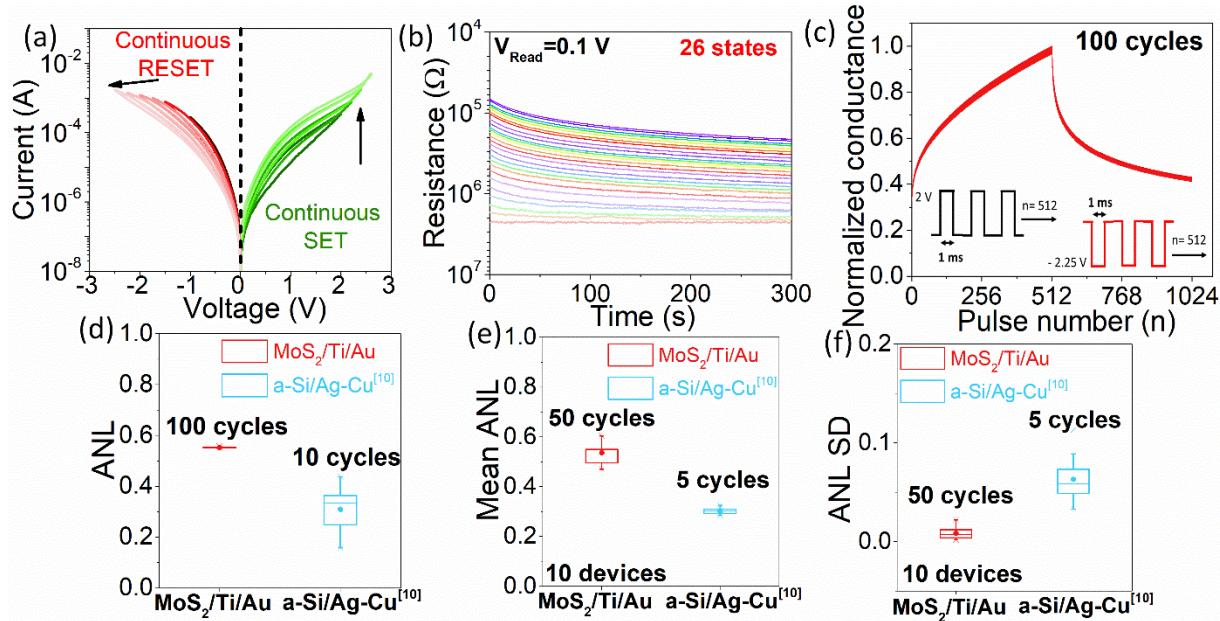

The ultra-low variability MoS<sub>2</sub> devices are further characterized as synapses suitable for use in neural network training. DC potentiation (continuous SET) and depression (continuous RESET) measurements are performed by enforcing VC. A continuous SET process is performed by increasing the VC from 2 V to 2.6 V immediately followed by a continuous RESET by

increasing the magnitude of the negative reset stop voltage from -1 V to -2.5 V. The MoS<sub>2</sub> devices exhibit 4 distinct potentiation states and 5 different depression states, shown in **Figure 3a**, rendering preliminary indication of the ability of MoS<sub>2</sub> device to behave like an analog memory. The MoS<sub>2</sub> synapse exhibits excellent retention of >300 s for 26 distinct conductance states, as shown in **Figure 3b**. For evaluating the retention, the device is SET to a particular conductance state by enforcing a VC while performing a DC I-V sweep. Followed by this, the current through the device is read at a voltage of 0.1 V for 26 distinct states. Next, the conductance weight update is measured on 10 synaptic devices and is compared with the a-Si synapses reported by Yeon *et al.*<sup>10</sup> for C-C and D-D variability. For obtaining potentiation, 512 identical voltage pulses of duration 1 ms and amplitude 2 V are applied. To induce pulsed depression, 512 identical voltage pulses of 1 ms duration and amplitude -2.25 V are applied. The train of potentiation and depression pulses are repeated for 100 cycles, write current is measured, and write conductance is extracted for both potentiation and depression. The write conductance, normalized to the maximum conductance obtained, is plotted as a function of the pulse number (n), as shown in the weight update curve in **Figure 3c** for all 100 cycles, showing extremely low C-C variability. The pulsing scheme is shown as the inset of **Figure 3c**. To assess the C-C variability, asymmetric non-linearity factor (ANL) is extracted by the following equation:<sup>10</sup>

$$ANL = \frac{G_P(\frac{n}{2}) - G_D(\frac{n}{2})}{G_{max} - G_{min}} \dots \dots \dots \quad (1)$$

where  $G_P(\frac{n}{2})$  and  $G_D(\frac{n}{2})$  are the median conductance values along potentiation and depression respectively;  $G_{max}$  and  $G_{min}$  are the maximum and minimum conductances, respectively. It is evident that the  $G_{max}/G_{min}$  ratio of the MoS<sub>2</sub> synapses is low. This can be improved either by increasing the thickness of MoS<sub>2</sub> or by implementing stack engineering which is beyond the scope

of this work. However, to avail the potential of these synapses we have incorporated the MoS<sub>2</sub> synapse in a pseudo-crossbar array of a 2-layer multi-layer perceptron (MLP) network with the support of a circuit-level macro model, NeuroSim.<sup>46</sup> The device parameters like G<sub>max</sub>/G<sub>min</sub> ratio, non-linearity factors in both potentiation and depression regimes along with C-C variability are used to obtain online learning accuracy of 70 %. Next, the ANL variation of 100 cycles in MoS<sub>2</sub> synapse is compared with ANL of 10 cycles in the a-Si/Ag-Cu synapse<sup>10</sup> as shown in **Figure 3d**. The MoS<sub>2</sub> synapse exhibits a tighter distribution in the ANL over 100 cycles in comparison to the modest 10 cycles observed in a-Si/Ag-Cu synapses. The weight update measurements are repeated on 10 distinct synaptic devices for 50 cycles each and the mean ANL is extracted for each device. The mean ANL over 50 cycles for 10 MoS<sub>2</sub> synapses is plotted and compared with the mean ANL obtained for 10 a-Si/Ag-Cu<sup>10</sup> synapses cycled only for 5 times as shown in **Figure 3e**. Further, we present the statistics of the weight update characteristics of MoS<sub>2</sub> synapses. The extraction of SD in ANL over multiple cycles provides the precise estimation of the C-C variability in the devices. Therefore, the SD in ANL is extracted for each synapse over 50 cycles. The extracted SD of the MoS<sub>2</sub> synapses (10 devices, 50 cycles each) is then compared to the SD of the a-Si/Ag-Cu<sup>10</sup> synapses (10 devices, 5 cycles each) as shown in **Figure 3f**. The MoS<sub>2</sub> synapses exhibit compact distribution in SD with a range of 0.02 which is superior to the SD distribution observed in a-Si/Ag-Cu<sup>10</sup> synapses where the range is 0.08. The consolidated table showing the ANL and the corresponding SD over at least 50 cycles for 10 MoS<sub>2</sub> synapses is shown in **Figure S4**. It is worth noting that this is one of the few reports in literature where the statistics (10 devices, at least 50 cycles for each device) on both C-C and D-D variability are provided for weight update characteristics. This statistical analysis of the weight update characteristics in MoS<sub>2</sub> synapses is

essential in establishing the low C-C variability of the technology, which justifies the viability of 2D materials in neuromorphic computing.

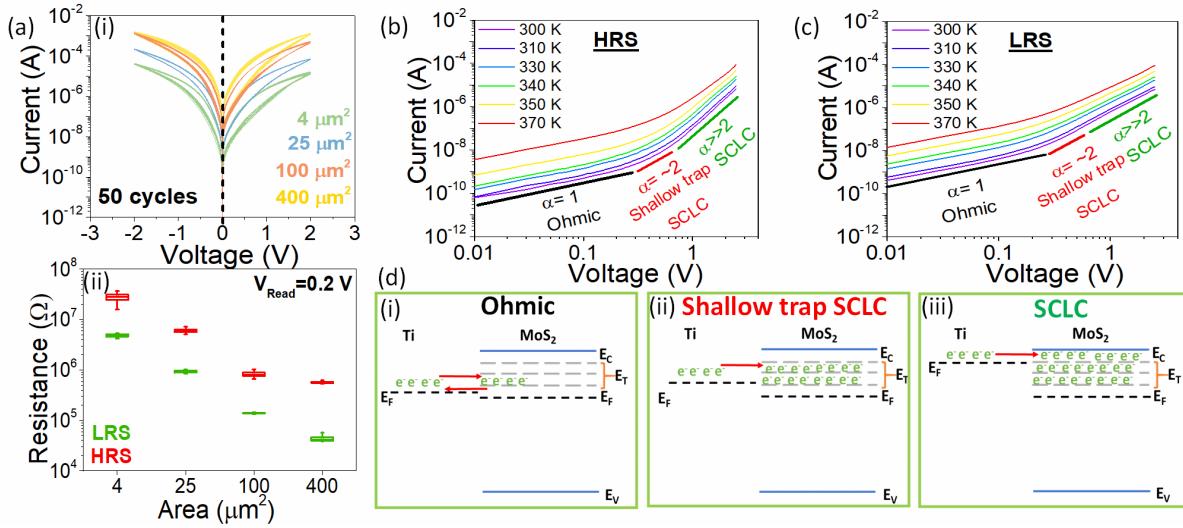

It is necessary to understand the underlying mechanism in  $\text{MoS}_2$  synapses responsible for the low C-C variability. The scaling of resistance with respect to area is considered as a clear indication of the switching mechanism in memristive devices.  $\text{MoS}_2$  synapses of area  $2 \times 2 \mu\text{m}^2$ ,  $5 \times 5 \mu\text{m}^2$ ,  $10 \times 10 \mu\text{m}^2$  and  $20 \times 20 \mu\text{m}^2$  are probed for DC I-V characteristics as shown in **Figure 4a(i)**. Here, each device is measured for 50 DC cycles. From the figure, it is evident that both HRS and LRS scale proportionately to the device area. The HRS and LRS are extracted at  $V_{\text{Read}}=0.2 \text{ V}$  for 50 cycles and the scatter in the resistance values is represented through box plots for each device area in **Figure 4a(ii)**. Clearly, the HRS and LRS scale linearly with the area insinuating that the dominant switching mechanism is not due to the formation of a conductive filament which is independent of device area.<sup>32</sup> **Figure S5** shows the resistance scaling over 3 different device areas (5 devices for each area) measured for 1 DC cycle. The repeatable trend in resistance scaling with area over multiple cycles and multiple devices establishes that the switching mechanism in  $\text{MoS}_2$  devices is interface mediated. However, we note that due to the dependence of LRS and HRS on device area, the variability might increase at nm-scale because of the introduction of edge effects.<sup>47</sup> The presence of Ti as the top electrode is critical for obtaining the low C-C variability. Please note that the Ti adhesion layer for the bottom Au electrode is retained while top electrode (Ti/Au) is replaced by 60 nm Au. In Ti/Au/ $\text{MoS}_2$ /Au (bottom to top) devices where Ti is not present, the device characteristics are gradual, indicating the role of the interface, but the switching is unstable and shows huge variability from one cycle to another (**Figure S6**). Next, I-V measurements are performed on 4 distinct Ti/Au/ $\text{MoS}_2$ /Ti/Au devices as a function of temperature which is varied from 300 K to 370 K. The I-V characteristics of a device, with an area of  $5 \times 5$

$\mu\text{m}^2$ , at both HRS and LRS regions as a function of temperature are shown in **Figure S7(a-b)**. The current in the HRS and LRS increases as the temperature increases for both bottom electrode injection (positive bias on bottom Au electrode) and top electrode injection (negative bias on bottom Au electrode) conditions. The I-V characteristics of the  $\text{MoS}_2$  device are symmetric in spite of the dissimilar work-functions of the top Ti and bottom Au electrodes.<sup>41</sup> This indicates that the conduction in the HRS is not limited by the Schottky barrier at the electrodes. Among various mechanisms suggested to explain interface mediated switching, space charge limited conduction (SCLC) mechanism has been one of the strongest contenders.<sup>48</sup> The I-V curves obtained for various temperatures are fitted to explain the SCLC theory.<sup>48-49</sup> The current through the device is given by  $I \propto V^\alpha$  where  $\alpha$  is the slope extracted by plotting I-V in double logarithmic scale. The conduction in the devices that follow the SCLC theory has three distinct regions which can be distinguished by the extracted slopes. The devices where the transport is dominated by SCLC have an initial ohmic region at low voltages. The  $\text{MoS}_2$  devices exhibit ohmic conduction at voltages  $<0.3$  V, indicated by  $\alpha= 1$ . At voltages  $>0.3$  V, shallow trap SCLC dominates the conduction indicated by  $\alpha \approx 2$ . The transition voltage at which the current follows a higher than quadratic relationship is called  $V_{\text{TFL}}$  where the shallow traps get filled causing the current to increase. The slope at voltages higher than  $V_{\text{TFL}}$  (0.6 V) is observed to be  $>>2$ . The fitting data in both HRS and LRS regions are shown in **Figure 4(b-c)**. The band diagram indicating the underlying mechanism following the SCLC theory is shown in **Figure 4d**. The ohmic region is observed at lower voltage because of the lower concentration of injected carriers compared to the thermally generated carriers and impurities. **Figure 4d(i)** shows the band diagram in ohmic conduction mode. At voltages  $>0.3$  V, shallow trap SCLC and SCLC conduction is observed where the electrode injects a larger number of carriers. **Figures 4d(ii-iii)** shows the band diagrams depicting the shallow-trap

SCLC and the SCLC after the  $V_{TFL}$ . The extracted slopes for each regime as a function of temperature for both HRS and LRS are shown in **Figure S8**. From **Figure S8**, it is worth noting that the I-V fitting for SCLC regime follows the ‘Child’s Law’ due to the trapping/detrapping process at  $\text{MoS}_2/\text{Ti}$  (top) interface. However, the identification of defects contributing to these traps is out of scope of this work. Any atomic-level characterization to understand the contributing defects for the interfacial switching deserves a detailed study of its own. **Figure S9** shows that the I-V characteristics do not agree with the other transport mechanisms, such as Schottky emission, Poole-Frenkel emission and Fowler-Nordheim tunneling. The temperature-dependent I-V characteristics and the extracted slopes for the other three devices are shown in **Figure S10 (A-C)**, confirming similar conduction processes. **Figure S10 (D)** shows the temperature dependent I-V measurements executed on device of area  $400 \mu\text{m}^2$  with the temperature varying from 125 K to 370 K. From the I-V fitting, we observe SCLC conduction mechanism consistent with the high temperature I-V measurements.

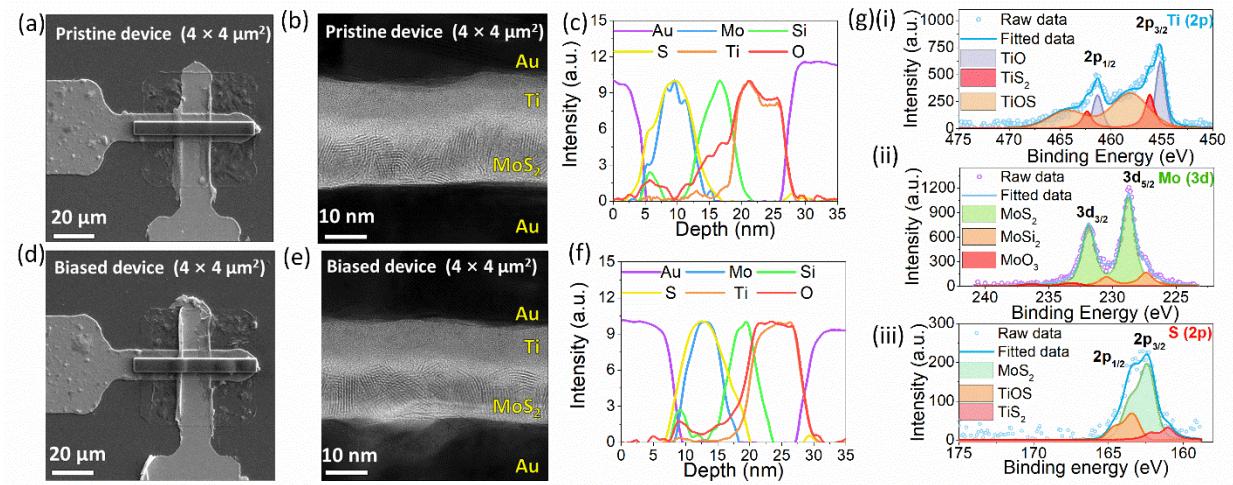

To confirm the layer structure of  $\text{MoS}_2$  and analyze the chemical composition of the sample before and after biasing, high resolution cross-sectional TEM was used. One biased device (100 DC cycles) and one pristine device from the same  $\text{Ti}/\text{Au}/\text{MoS}_2/\text{Ti}/\text{Au}$  sample with the lateral size of  $4 \times 4 \mu\text{m}^2$  were analyzed. **Figure 5a** shows the top-view Scanning Electron Microscope (SEM) image of the pristine device; the location at which the FIB cut was done is marked with a black rectangle (*i.e.*, the protective Cr/C film deposited before the FIB cut). The  $\text{MoS}_2$  stack can be clearly observed at the cross-point region in the SEM image, similar to Figure 1b. From the cross-sectional TEM image and the Electron Energy Loss Spectroscopy (EELS) profiles obtained in the pristine device (**Figures 5b** and **5c**) it is concluded that the structure of the fabricated device is  $\text{Au}/\text{Ti}/\text{Si}/\text{MoS}_2/\text{Au}$  (from up to down). From **Figure 5** two unexpected and critical observations

are made. First, there is an ultra-thin layer of Si in between the MoS<sub>2</sub> and the Ti layer, which most probably migrated from the Si/SiO<sub>2</sub> substrate due to the ~780 °C applied during the sulfurization step adopted for MoS<sub>2</sub> growth. Secondly, while the structure of the MoS<sub>2</sub> is clearly layered, the orientation of its individual 2D layers varies from 0° to 90° with respect to the horizontal substrate plane (**Figures 5b and 5e**). Statistically, we find that this structure remains unaltered for the biased device (**Figures 5d-e**), indicating that the Au/Ti/Si/MoS<sub>2</sub>/Au (up to down) stack is stable to the electrical stresses applied. It is worth noting that, as the switching mechanism is distributed (*i.e.*, shows area dependence and is analog, meaning that it is not based on the formation of local filaments), the observations in Figure 5e correspond to the switching regions. Most memristors employing MoS<sub>2</sub> as the switching medium<sup>22, 50</sup> were based on multilayer stacks of horizontally-aligned 2D MoS<sub>2</sub> planes, and in all cases the switching was filamentary and resulted in high C-C and D-D variability. On the contrary, the unconventional structure of our devices (based on a Si-rich highly crystalline MoS<sub>2</sub> of varying layer orientation) promotes smooth ion migration across it and results in analog resistive switching with ultra-low C-C and D-D variability (Figure 2). Among all mobile species within this Au/Ti/Si/MoS<sub>2</sub>/Au structure, most probably the migration of O is the one responsible for the switching. The reasons that support this claim are: i) the signals of Mo, S, Si and Ti in the EELS profiles do not show significant changes, while the O profile does; ii) the MoS<sub>2</sub> is highly crystalline, meaning that forming S vacancies would require the applications of voltages much higher than those applied in our experiments (*i.e.*, up to 2 V in Figure 2);<sup>51</sup> iii) multiple studies have reported the formation of O-vacancies in memristive devices at low electrical fields;<sup>52</sup> and iv) the low variability is not observed without the Ti film which is known to be a very good O adsorber.

X-ray Photoelectron Spectroscopy (XPS) measurements were performed on a film of Au/Ti/MoS<sub>2</sub> (up to down) deposited using the same process used for the device fabrication. The XPS depth profiling is performed at 10 s intervals on the stacked film, and elemental spectra for Ti (2p), Mo (3d) and S (2p) were obtained after each etch step. From **Figure 5g(i)**, clear signatures of TiS<sub>2</sub>, TiOS and TiO are observed at 456.2 eV, 457.6 eV and 455.1 eV respectively.<sup>53-54</sup> The binding energy peaks for TiO, TiS<sub>2</sub> and TiOS remain consistent for subsequent etch cycles as shown in **Figure S11a**. The presence of TiS<sub>2</sub> and TiOS indicate the migration of sulfur ions from the underlying MoS<sub>2</sub> layer post top electrode deposition. From the EELS spectra (**Figure 5f**), the change in the profile (post biasing) is indicative of the role played by ‘O’ vacancies in switching. Furthermore, XPS spectra (**Figure 5g(i)**) on pristine film reveals the formation TiO and TiOS, indicating the reservoir of ‘O’ vacancies is due to the presence of Ti contact metal. It is noteworthy that the control device with Au contact metal (**Figure S6**) shows high variability. Therefore, the requirement of Ti for obtaining low variability indicates that ‘O’ vacancies can be the dominant defect species that take part in SCLC mechanism. Analysis of the trap states from the contributing defects merit its own study. **Figure 5g(ii)** shows the XPS spectra of Mo (3d) where the binding energy peaks at 228.7 eV, 227.3 eV and 233.1 eV correspond to MoS<sub>2</sub>, MoSi<sub>2</sub> and MoO<sub>3</sub> respectively.<sup>55-57</sup> The presence of MoSi<sub>2</sub> peak corroborates the observation by TEM and EELS. The subsequent etch cycles also show the presence of MoS<sub>2</sub>, MoSi<sub>2</sub> and MoO<sub>3</sub> as shown by the corresponding spectra in **Figure S11b**. **Figure 5g(iii)** shows the XPS spectra of S (2p) where the peak binding energy at 162.4 eV signifies the presence of MoS<sub>2</sub>, the peak at 161.09 eV corresponds to TiS<sub>2</sub>, and the peak at 163.4 eV corresponds to TiOS.<sup>53, 58</sup> **Figure S11c** shows the S (2p) spectra for the subsequent etch cycles.

To establish the viability of these ultra-low variability synapses for circuit implementations, we proceed to connect multiple such synapses to demonstrate Boolean logic gate functionalities through vector matrix multiplication. Recently, we demonstrated LIF neurons using MoS<sub>2</sub> as the switching medium and Ag as the top electrode in a Au/MoS<sub>2</sub>/Ag heterostructure.<sup>37</sup> Here, we integrate the MoS<sub>2</sub> synapses with those MoS<sub>2</sub> LIF neurons. The connection of MoS<sub>2</sub> synapses with MoS<sub>2</sub> neurons highlights the possibility of obtaining a monolithically integrated circuit of synapses and neurons. Typically, for the applications requiring the integration of neurons and synapses, these elements are realized with dissimilar materials necessitating heterogeneous integration. This process is wrought with issues in substrate incompatibility, cost and thermal budget. For the realization of large-scale circuitry, such as deep neural networks, monolithic integration of synapses and neurons is helpful.

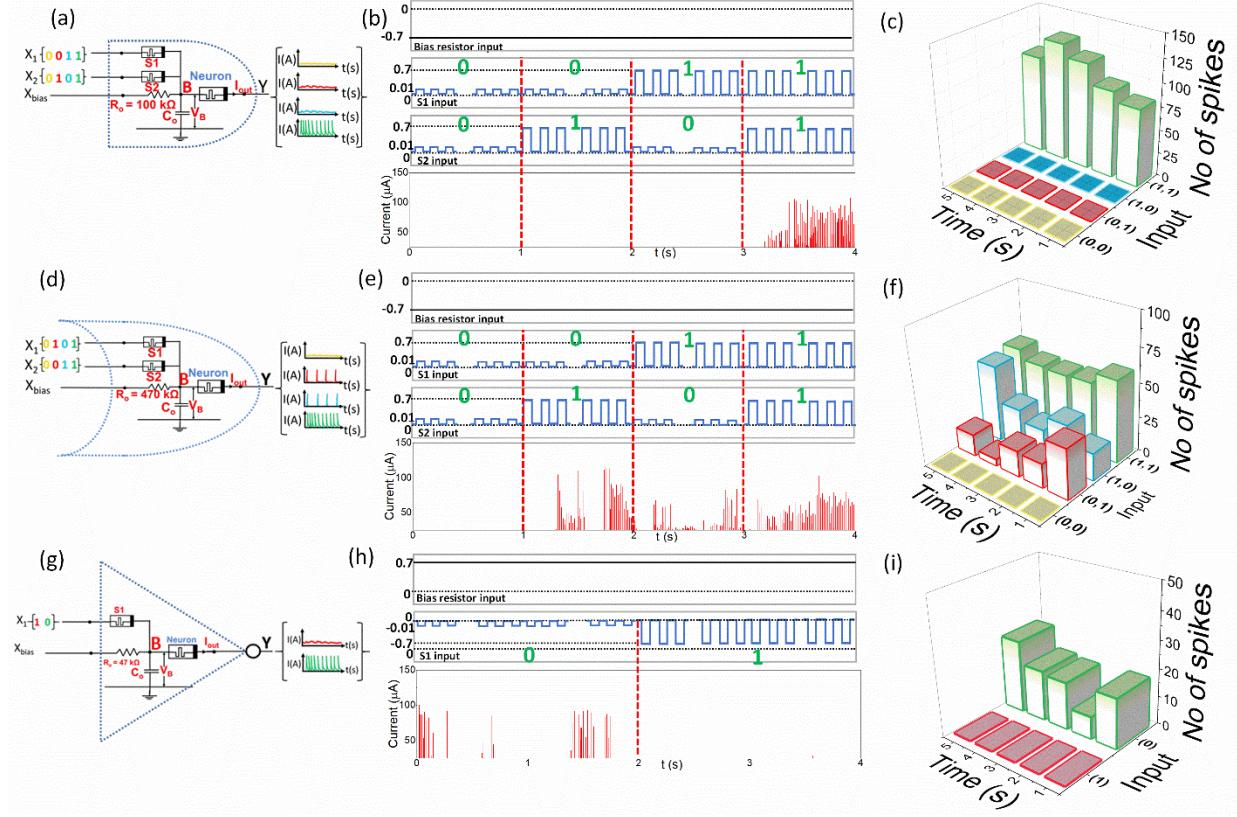

The integration of MoS<sub>2</sub> synapses and neurons to realize AND, OR and NOT logic gates is shown in **Figure 6**. MoS<sub>2</sub> synapses and an external bias resistor are connected to one MoS<sub>2</sub> neuron. For enabling “integrate and fire” behavior of the neuron, a capacitor ( $C_0 = 100$  nF) is connected as an integrator in parallel with the neuron. The individual MoS<sub>2</sub> neuron characteristics are shown **Figure S12**. The MoS<sub>2</sub> synapses are set at a particular resistance state, which acts as the weight of these synapses as shown in **Figure S13a**. For the implementation of logic gates, voltage pulse trains of amplitude  $V_i$  are applied as input to the  $i^{\text{th}}$  synapse bearing a certain weight (conductance)  $W_i$ , which results in current flowing through the path as  $I_i = V_i \times W_i$  by Ohm’s law. Thus, the current through all ‘ $N-1$ ’ synapses and the external bias resistor add up by Kirchoff’s law to  $I = \sum_{i=1}^N V_i W_i$  which essentially is the vector matrix product of the input voltage and weight matrix. This total current at node ‘B’ (shown in Figure 6a) builds the potential across the capacitor  $C_0$ , charging it up. When  $V_B$  (shown in Figure 6a) exceeds the threshold voltage of the TSM, the

TSM switches on, allowing the capacitor  $C_0$  to discharge through it. This causes  $V_B$  to reduce, which in turn switches the TSM back to its HRS. The process of charging and discharging of the capacitor continues, resulting in current spikes at the output of the circuit. To realize AND and OR logic gates, an input of '0' is represented by a train of low voltage pulses (amplitude 0.01 V, pulse width 1 ms), and '1' is represented by a train of high voltage pulses (amplitude 0.7 V, pulse width 1 ms). Similarly for NOT gate implementation, an input of '0' is represented by a train of low voltage pulses (amplitude -0.01 V, pulse width 1 ms), and '1' is represented by a train of high voltage pulses (amplitude -0.7 V, pulse width 1 ms). However, the input to bias resistor is varied since it behaves like a differential resistor. For the bias resistor, a constant voltage of -0.7 V (AND and OR gate) and +0.7 V (NOT gate) is applied. The bias resistance is adjusted for the realization of each logic operation. If the circuit parameters determined by the synapse resistances allows the neuron to fire, the output is recorded as '1', else if the neuron does not fire, the output is considered as '0'. The voltage pulse trains are applied for 5 s. First, the synapses S1 and S2 are SET at particular weights or conductance states as shown by the retention plots in **Figure S13b-d**.

*AND gate:* The circuit used for the two-input AND gate realization is shown in **Figure 6a and S14a**. A bias resistor ( $R_O$ ) of  $100\text{ k}\Omega$  is connected to the  $\text{MoS}_2$  synapses S1 and S2. The truth table corresponding to the AND gate is shown in **Figure S14b**. Further, the output spiking characteristics for each input is shown in **Figure S14c**. The input pulsing scheme and the spiking output from the  $\text{MoS}_2$  neurons for 1 s time period for various input combinations is shown in **Figure 6b**. The voltage pulse trains are applied for 5 s and the number of spikes is extracted and plotted as a function of inputs and time duration as shown in **Figure 6c**. The figure shows the

implementation of AND gate where spikes are obtained for input (1 1) and the absence of spikes is observed for the other input combinations, *viz.* of (0 0), (0 1) and (1 0).

*OR gate:* For the implementation of OR gate, the same measurement methodology as AND is used. The input pulse parameters are the same as those for the AND gate. However, we change the bias resistor ( $R_o$ ) to a higher resistance of 470 k $\Omega$ . The use of a higher resistance effectively reduces the equivalent resistance of the RC circuit, which is necessary to obtain spiking in (0 1), (1 0) and (1 1) conditions. The schematic of the OR gate indicating the various input combinations and their corresponding outputs are shown in **Figure 6d**. Similar to the AND gate, the input pulsing scheme and spiking output for 1 s is shown in **Figure 6e**. The response of the OR gate for 5 s and the spiking output as a function of the input combination and time duration is shown in **Figure 6f**. The figure depicts the implementation of OR gate where output spikes are observed for (0 1), (1 0) and (1 1) input combinations and no spikes are observed for (0 0) condition. The number of spikes is higher for the (1 1) combination in comparison to the (0 1) and (1 0) combinations due to decreased equivalent resistance of the RC circuit. The circuit implementation, truth table and the output spiking characteristics of the OR gate for all input combinations are shown in **Figure S15**.

*NOT gate:* The NOT gate is implemented using one MoS<sub>2</sub> synapse and a bias resistor ( $R_o$ ) of resistance 47 k $\Omega$ . The schematic of the NOT gate is shown in **Figure 6g**. The input pulses corresponding to ‘0’ and ‘1’ states are applied to the MoS<sub>2</sub> synapse. It should be noted that for implementing the NOT gate, the MoS<sub>2</sub> synapse plays the role of a differential resistor. A constant voltage of 0.7 V is applied to the bias resistor. The input pulsing scheme and spiking output is shown in **Figure 6h**. Further, the number of spikes is plotted as a function of time duration and inputs as shown in **Figure 6i**. The circuit diagram, truth table and the spiking characteristics of the NOT gate are shown in **Figure S16**. Output spikes are obtained for the ‘0’ input condition. No

spikes are observed for the ‘1’ condition because of the increased equivalent resistance of the circuit. This integration of MoS<sub>2</sub>-based synapses and neurons exhibits a two-fold impact. First, it shows the viability of the MoS<sub>2</sub> memristors for circuit implementations, including vector matrix multiplication. Secondly, it proves that MoS<sub>2</sub>-based neurons and synapses can be integrated together on the same materials platform, thus establishing the possibility of realizing monolithically integrated neural networks with these devices.

## CONCLUSION

In conclusion, we have demonstrated ultra-low variability synapses using MoS<sub>2</sub> as the switching medium, and Ti/Au as the bottom and top electrodes. These devices exhibit excellent DC endurance characteristics while maintaining low cycle-to-cycle variability. Additionally, a comparison of MoS<sub>2</sub> synapses with a-Si/Ag-Cu synapses establishes even lower C-C variability in their weight update characteristics. The switching is facilitated by the interface between MoS<sub>2</sub> and Ti (top electrode) indicated by the area dependent resistance scaling. TEM images of pristine and biased devices confirm no physical degradation in the devices after cycling. The temperature dependent I-V measurements prove that the dominant conduction mechanism follows the SCLC theory. Finally, the ultra-low variability synapses are integrated with LIF neurons based on the same materials system, *viz.* MoS<sub>2</sub>, to implement Boolean logic. This study clarifies the viability of these devices for future neuromorphic applications and edge computing.

## METHODS

**Device fabrication:** The MoS<sub>2</sub> devices are fabricated using UV lithography. Bottom electrode is patterned, and 100 nm of Au with 5 nm Ti as the adhesion layer is deposited by e-beam evaporation. To obtain the MoS<sub>2</sub> film, 3 nm Mo is patterned and deposited by e-beam evaporation

on the bottom electrodes. Then, the samples containing the bottom electrodes and the patterned 3-nm-thick Mo film are placed in a quartz tube CVD furnace pre-loaded with Sulfur powder in alumina boat. The base pressure of the CVD furnace is brought down to  $\sim 1$  mTorr with a mechanical pump. To remove any residual gases, the quartz tube is purged with Argon (Ar) gas. The furnace temperature is raised to  $\sim 780$  °C in 50 mins and held there for an additional 50 mins. Continuous supply of Argon (Ar) gas flow is provided during the reaction between sulfur and Mo. The furnace is finally allowed to cool down to room temperature naturally. The sulfurization process converts metallic Mo to 2D MoS<sub>2</sub>. Finally, the top electrode is patterned, and 6 nm Ti followed by 50 nm Au is deposited. Note that this fabrication process is free of any transfer step, which is simpler and cleaner than standard processes based on 2D materials transfer *via* polymer scaffolds. It is noteworthy that these devices have cross-point configuration which indicates the potential of the device for implementing cross bars. The synthesized CVD film consists of MoS<sub>2</sub> layers in random orientation as indicated by the TEM images.

**Electrical Characterization:** The MoS<sub>2</sub> devices are characterized using Keysight B1500A Semiconductor parameter analyzer. The devices are probed in Janis cryogenic probe station with a chamber pressure of  $4 \times 10^{-4}$  mBar. The weight update measurements, logic gate implementations were performed using the WGFMU B1530 A modules. For the logic gate realization, the MoS<sub>2</sub> neurons are probed at room temperature using a 6200 Micromanipulator probe station.

### **Material Characterization:**

**XPS:** The XPS characterization is performed using Physical Electronics 5400 ESCA (XPS) system. Depth profiling was performed where the material was etched for total time of 100 s in 10

s interval. After etch cycle (10 s) elemental spectra of Ti (2p), Mo (3d) and S (2p) was obtained. The deconvolution of the peaks was executed using XPS peak 41 software.

**TEM:** For the protection of the samples and a good contrast in TEM images, 15 nm Cr and  $\sim$ 2  $\mu$ m C were deposited on the sample by precision etching and coating system (model Gatan 682, PECS). The high resolution cross-sectional TEM images of the samples were taken as follows: 1) a focused ion beam (FIB, model HELIOS NANOLAB 450S, FEI) was used to cut the samples into  $\sim$ 2  $\mu$ m long and  $\sim$ 40 nm thick lamellas under 30 kV, 7.7 pA; 2) the thin lamellas were placed on a TEM copper grid for inspection using a micromanipulator; 3) the samples were analyzed in a high-resolution TEM (model JEM-2100, FEI) working at 200 kV in high vacuum ( $10^{-6}$  Pa). The chemical composition of the samples was analyzed by EDX (model Bruker super-EDS) and EELS (model Gatan) tools integrated in the TEM.

## ASSOCIATED CONTENT

### Supporting Information

The supporting information if available for free of charge at *ACS Nano* library. DC endurance of MoS<sub>2</sub>/Ti/Au devices, Role of MoS<sub>2</sub> in switching, DC characteristics for SET voltage and RESET power distribution, Weight update statistics consolidated table for C-C variability, Area dependent resistance scaling for demonstrating D-D variability, DC characteristics of MoS<sub>2</sub>/Au devices, Temperature dependent I-V and fitting data for 4 devices, XPS of Ti (2p), Mo (3d), S (2p) with depth profiling, MoS<sub>2</sub> LIF neuron characteristics, Retention of MoS<sub>2</sub>/Ti/Au synapses for logic implementation, Logic gate implementation circuitry, truth table and the spiking outputs.

## Acknowledgment

A.K. conceived the idea and T.R. directed this research. A.K fabricated the devices and performed the device characterization. D.D. performed MoS<sub>2</sub> neuron fabrication, neuron characterization and assisted with the monolithic integration of neuron and synapses. S.S.H. and C. Y. synthesized the MoS<sub>2</sub> films under the guidance of Y. J. H.S.C and T.S.B assisted with the TEM, EDS and FIB characterizations. Y.Q. and M.L. assisted with the TEM, EDS and EELS characterization of pristine and biased devices. All the authors analyzed the data, discussed the results, and contributed to the preparation of the manuscript. A. K., D. D. and T. R. were supported by NSF-ECCS-1845331 (CAREER). T.S.B was supported by the Technology Innovation Program (20010542) funded through the MOTIE, Korea. We acknowledge the NSF Major Research Instrumentation (MRI) Award No. 1726636 for measuring XPS spectra.

## Conflicts of Interest

The authors declare no conflicts of interest

## Data Availability

The data that support the findings of this study are available from the corresponding author upon reasonable request.

## References

1. Yu, S., Neuro-inspired computing with emerging nonvolatile memories. *Proceedings of the IEEE* **2018**, *106* (2), 260-285.

2. Mead, C., Neuromorphic electronic systems. *Proceedings of the IEEE* **1990**, *78* (10), 1629-1636.

3. Merolla, P.; Arthur, J.; Akopyan, F.; Imam, N.; Manohar, R.; Modha, D. S. In *A digital neurosynaptic core using embedded crossbar memory with 45pJ per spike in 45nm*, Custom Integrated Circuits Conference (CICC), 2011 IEEE, IEEE: 2011; pp 1-4.

4. Ielmini, D.; Waser, R., *Resistive switching: from fundamentals of nanoionic redox processes to memristive device applications*. John Wiley & Sons, Chicago, **2015**.

5. Baeumer, C.; Valenta, R.; Schmitz, C.; Locatelli, A.; Mentes, T. O.; Rogers, S. P.; Sala, A.; Raab, N.; Nemsak, S.; Shim, M., Subfilamentary networks cause cycle-to-cycle variability in memristive devices. *ACS nano* **2017**, *11* (7), 6921-6929.

6. Chakrabarti, B.; Chan, H.; Alam, K.; Koneru, A.; Gage, T. E.; Ocola, L. E.; Divan, R.; Rosenmann, D.; Khanna, A.; Grisafe, B., Nanoporous Dielectric Resistive Memories Using Sequential Infiltration Synthesis. *ACS nano* **2021**, *15* (3), 4155-4164.

7. Lu, Y.; Liu, K.; Yang, J.; Zhang, T.; Cheng, C.; Dang, B.; Xu, L.; Zhu, J.; Huang, Q.; Huang, R., Highly Uniform Two-Terminal Artificial Synapses Based on Polycrystalline HfO<sub>2</sub>ZrO<sub>2</sub> for Sparsified Back Propagation Networks. *Advanced Electronic Materials* **2020**, *6* (8), 2000204.

8. Medeiros-Ribeiro, G.; Perner, F.; Carter, R.; Abdalla, H.; Pickett, M. D.; Williams, R. S., Lognormal switching times for titanium dioxide bipolar memristors: origin and resolution. *Nanotechnology* **2011**, *22* (9), 095702.

9. Chen, S.; Mahmoodi, M. R.; Shi, Y.; Mahata, C.; Yuan, B.; Liang, X.; Wen, C.; Hui, F.; Akinwande, D.; Strukov, D. B., Wafer-scale integration of two-dimensional materials in high-density memristive crossbar arrays for artificial neural networks. *Nature Electronics* **2020**, *3* (10), 638-645.

10. Yeon, H.; Lin, P.; Choi, C.; Tan, S. H.; Park, Y.; Lee, D.; Lee, J.; Xu, F.; Gao, B.; Wu, H., Alloying conducting channels for reliable neuromorphic computing. *Nature Nanotechnology* **2020**, *15* (7), 574-579.

11. Kim, K. M.; Yang, J. J.; Strachan, J. P.; Grafals, E. M.; Ge, N.; Melendez, N. D.; Li, Z.; Williams, R. S., Voltage divider effect for the improvement of variability and endurance of TaO<sub>x</sub> memristor. *Scientific reports* **2016**, *6* (1), 1-6.

12. Li, C.; Belkin, D.; Li, Y.; Yan, P.; Hu, M.; Ge, N.; Jiang, H.; Montgomery, E.; Lin, P.; Wang, Z., Efficient and self-adaptive in-situ learning in multilayer memristor neural networks. *Nature communications* **2018**, *9* (1), 1-8.

13. Shi, Y.; Nguyen, L.; Oh, S.; Liu, X.; Koushan, F.; Jameson, J. R.; Kuzum, D., Neuroinspired unsupervised learning and pruning with subquantum CBRAM arrays. *Nature communications* **2018**, *9* (1), 1-11.

14. Ambrogio, S.; Balatti, S.; Milo, V.; Carboni, R.; Wang, Z.-Q.; Calderoni, A.; Ramaswamy, N.; Ielmini, D., Neuromorphic learning and recognition with one-transistor-one-resistor synapses and bistable metal oxide RRAM. *IEEE Transactions on Electron Devices* **2016**, *63* (4), 1508-1515.

15. Lastras-Montano, M. A.; Cheng, K.-T., Resistive random-access memory based on ratioed memristors. *Nature Electronics* **2018**, *1* (8), 466-472.

16. Alibart, F.; Zamanidoost, E.; Strukov, D. B., Pattern classification by memristive crossbar circuits using ex situ and in situ training. *Nature communications* **2013**, *4* (1), 1-7.

17. Prezioso, M.; Merrikh-Bayat, F.; Hoskins, B.; Adam, G. C.; Likharev, K. K.; Strukov, D. B., Training and operation of an integrated neuromorphic network based on metal-oxide memristors. *Nature* **2015**, *521* (7550), 61-64.

18. Beiu, V.; Quintana, J. M.; Avedillo, M. J., VLSI implementations of threshold logic-a comprehensive survey. *IEEE Transactions on Neural Networks* **2003**, *14* (5), 1217-1243.

19. Kim, Y. S.; Son, M. W.; Kim, K. M., Memristive Stateful Logic for Edge Boolean Computers. *Advanced Intelligent Systems* **2021**, 2000278.

20. Borghetti, J.; Snider, G. S.; Kuekes, P. J.; Yang, J. J.; Stewart, D. R.; Williams, R. S., 'Memristive' switches enable 'stateful' logic operations via material implication. *Nature* **2010**, *464* (7290), 873-876.

21. Rothenbuhler, A.; Tran, T.; Smith, E. H. B.; Saxena, V.; Campbell, K. A., Reconfigurable threshold logic gates using memristive devices. *Journal of Low Power Electronics and Applications* **2013**, *3* (2), 174-193.

22. Wang, M.; Cai, S.; Pan, C.; Wang, C.; Lian, X.; Zhuo, Y.; Xu, K.; Cao, T.; Pan, X.; Wang, B., Robust memristors based on layered two-dimensional materials. *Nature Electronics* **2018**, *1* (2), 130-136.

23. Yao, J.; Lin, J.; Dai, Y.; Ruan, G.; Yan, Z.; Li, L.; Zhong, L.; Natelson, D.; Tour, J. M., Highly transparent nonvolatile resistive memory devices from silicon oxide and graphene. *Nature communications* **2012**, *3* (1), 1-8.

24. Cheng, P.; Sun, K.; Hu, Y. H., Memristive behavior and ideal memristor of 1T phase MoS<sub>2</sub> nanosheets. *Nano letters* **2016**, *16* (1), 572-576.

25. Shin, G. H.; Kim, C.-K.; Bang, G. S.; Kim, J. Y.; Jang, B. C.; Koo, B. J.; Woo, M. H.; Choi, Y.-K.; Choi, S.-Y., Multilevel resistive switching nonvolatile memory based on MoS<sub>2</sub> nanosheet-embedded graphene oxide. *2D Materials* **2016**, *3* (3), 034002.

26. Zhao, X.; Fan, Z.; Xu, H.; Wang, Z.; Xu, J.; Ma, J.; Liu, Y., Reversible alternation between bipolar and unipolar resistive switching in Ag/MoS<sub>2</sub>/Au structure for multilevel flexible memory. *Journal of Materials Chemistry C* **2018**, *6* (27), 7195-7200.

27. Choudhary, S.; Soni, M.; Sharma, S. K., Low voltage & controlled switching of MoS<sub>2</sub>-GO resistive layers based ReRAM for non-volatile memory applications. *Semiconductor Science and Technology* **2019**, *34* (8), 085009.

28. Zhao, H.; Dong, Z.; Tian, H.; DiMarzi, D.; Han, M. G.; Zhang, L.; Yan, X.; Liu, F.; Shen, L.; Han, S. J., Atomically thin femtojoule memristive device. *Advanced Materials* **2017**, *29* (47), 1703232.

29. Kumar, M.; Ban, D. K.; Kim, S. M.; Kim, J.; Wong, C. P., Vertically Aligned WS<sub>2</sub> Layers for High-Performing Memristors and Artificial Synapses. *Advanced Electronic Materials* **2019**, *5* (10), 1900467.

30. Yan, X.; Zhao, Q.; Chen, A. P.; Zhao, J.; Zhou, Z.; Wang, J.; Wang, H.; Zhang, L.; Li, X.; Xiao, Z., Vacancy - Induced Synaptic Behavior in 2D WS<sub>2</sub> Nanosheet – Based Memristor for Low - Power Neuromorphic Computing. *Small* **2019**, *15* (24), 1901423.

31. Huh, W.; Jang, S.; Lee, J. Y.; Lee, D.; Lee, D.; Lee, J. M.; Park, H. G.; Kim, J. C.; Jeong, H. Y.; Wang, G., Synaptic Barristor Based on Phase-Engineered 2D Heterostructures. *Advanced Materials* **2018**, *30* (35), 1801447.

32. Ge, R.; Wu, X.; Kim, M.; Shi, J.; Sonde, S. S.; Tao, L.; Zhang, Y.; Lee, J.; Akinwande, D., Atomristor: Non-Volatile Resistance Switching in Atomic Sheets of Transition Metal Dichalcogenides. *Nano letters* **2017**.

33. Shi, Y.; Liang, X.; Yuan, B.; Chen, V.; Li, H.; Hui, F.; Yu, Z.; Yuan, F.; Pop, E.; Wong, H.-S. P., Electronic synapses made of layered two-dimensional materials. *Nature Electronics* **2018**, *1* (8), 458.

34. Yuan, B.; Liang, X.; Zhong, L.; Shi, Y.; Palumbo, F.; Chen, S.; Hui, F.; Jing, X.; Villena, M. A.; Jiang, L., 150 nm × 200 nm Cross-Point Hexagonal Boron Nitride-Based Memristors. *Advanced Electronic Materials* **2020**, 1900115.

35. Krishnaprasad, A.; Choudhary, N.; Das, S.; Dev, D.; Kalita, H.; Chung, H.-S.; Aina, O.; Jung, Y.; Roy, T., Electronic synapses with near-linear weight update using MoS<sub>2</sub>/graphene memristors. *Applied Physics Letters* **2019**, *115* (10), 103104.

36. Xu, R.; Jang, H.; Lee, M.-H.; Amanov, D.; Cho, Y.; Kim, H.; Park, S.; Shin, H.-j.; Ham, D., Vertical MoS<sub>2</sub> Double-Layer Memristor with Electrochemical Metallization as an Atomic-Scale Synapse with Switching Thresholds Approaching 100 mV. *Nano letters* **2019**, *19* (4), 2411-2417.

37. Dev, D.; Krishnaprasad, A.; Shawkat, M. S.; He, Z.; Das, S.; Fan, D.; Chung, H.-S.; Jung, Y.; Roy, T., 2D MoS<sub>2</sub> Based Threshold Switching Memristor For Artificial Neuron. *IEEE Electron Device Letters* **2020**.

38. Lee, S.; Sohn, J.; Jiang, Z.; Chen, H.-Y.; Wong, H.-S. P., Metal oxide-resistive memory using graphene-edge electrodes. *Nature communications* **2015**, *6* (1), 1-7.

39. Qian, K.; Tay, R. Y.; Nguyen, V. C.; Wang, J.; Cai, G.; Chen, T.; Teo, E. H. T.; Lee, P. S., Hexagonal boron nitride thin film for flexible resistive memory applications. *Advanced Functional Materials* **2016**, *26* (13), 2176-2184.

40. Tian, H.; Mi, W.; Zhao, H.; Mohammad, M. A.; Yang, Y.; Chiu, P.-W.; Ren, T.-L., A novel artificial synapse with dual modes using bilayer graphene as the bottom electrode. *Nanoscale* **2017**, *9* (27), 9275-9283.

41. Walczyk, C.; Wenger, C.; Sohal, R.; Lukosius, M.; Fox, A.; Dąbrowski, J.; Wolansky, D.; Tillack, B.; Müssig, H.-J.; Schroeder, T., Pulse-induced low-power resistive switching in Hf O<sub>2</sub> metal-insulator-metal diodes for nonvolatile memory applications. *Journal of Applied Physics* **2009**, *105* (11), 114103.

42. Wong, H.-S. P.; Lee, H.-Y.; Yu, S.; Chen, Y.-S.; Wu, Y.; Chen, P.-S.; Lee, B.; Chen, F. T.; Tsai, M.-J., Metal-oxide RRAM. *Proceedings of the IEEE* **2012**, *100* (6), 1951-1970.

43. Yu, S.; Wu, Y.; Jeyasingh, R.; Kuzum, D.; Wong, H.-S. P., An electronic synapse device based on metal oxide resistive switching memory for neuromorphic computation. *IEEE Transactions on Electron Devices* **2011**, *58* (8), 2729-2737.

44. Yu, S.; Wu, Y.; Wong, H.-S. P., Investigating the switching dynamics and multilevel capability of bipolar metal oxide resistive switching memory. *Applied Physics Letters* **2011**, *98* (10), 103514.

45. Adam, G. C.; Hoskins, B. D.; Prezioso, M.; Merrikh-Bayat, F.; Chakrabarti, B.; Strukov, D. B., 3-D memristor crossbars for analog and neuromorphic computing applications. *IEEE Transactions on Electron Devices* **2016**, *64* (1), 312-318.

46. Chen, P.-Y.; Peng, X.; Yu, S., NeuroSim: A circuit-level macro model for benchmarking neuro-inspired architectures in online learning. *IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems* **2018**, *37* (12), 3067-3080.

47. Zhao, P.; Amani, M.; Lien, D.-H.; Ahn, G. H.; Kiriya, D.; Mastandrea, J. P.; Ager III, J. W.; Yablonovitch, E.; Chrzan, D. C.; Javey, A., Measuring the edge recombination velocity of monolayer semiconductors. *Nano letters* **2017**, *17* (9), 5356-5360.

48. Chakraborty, I.; Panwar, N.; Khanna, A.; Ganguly, U., Space Charge Limited Current with Self-heating in Pr<sub>0.7</sub>Ca<sub>0.3</sub>MnO<sub>3</sub> based RRAM. *2016 arXiv preprint arXiv:1605.08755*.

49. Shang, D.; Wang, Q.; Chen, L.; Dong, R.; Li, X.; Zhang, W., Effect of carrier trapping on the hysteretic current-voltage characteristics in Ag / La 0.7 Ca 0.3 MnO 3 / Pt heterostructures. *Physical Review B* **2006**, *73* (24), 245427.

50. Su, Q.; Wang, S.; Feng, M.; Du, G.; Xu, B., Direct studies on the lithium-storage mechanism of molybdenum disulfide. *Scientific reports* **2017**, *7* (1), 1-10.

51. Das, U.; Bhattacharjee, S.; Sarkar, P. K.; Roy, A., A multi-level bipolar memristive device based on visible light sensing MoS<sub>2</sub> thin film. *Materials Research Express* **2019**, *6* (7), 075037.

52. Lee, J.; Schell, W.; Zhu, X.; Kioupakis, E.; Lu, W. D., Charge transition of oxygen vacancies during resistive switching in oxide-based RRAM. *ACS applied materials & interfaces* **2019**, *11* (12), 11579-11586.

53. Gonbeau, D.; Guimon, C.; Pfister-Guillouzo, G.; Levasseur, A.; Meunier, G.; Dormoy, R., XPS study of thin films of titanium oxysulfides. *Surface Science* **1991**, *254* (1-3), 81-89.

54. Simon, D.; Perrin, C.; Bardolle, J., ESCA study of Nb and Ti oxides. Applications to the determination of the nature of the superficial films formed during the oxidation of Nb-Ti and Nb-Ti alloys. *Electron* **1976**, *1*, 175.

55. Alstrup, I.; Chorkendorff, I.; Candia, R.; Clausen, B. S.; Topsøe, H., A combined X-Ray photoelectron and Mössbauer emission spectroscopy study of the state of cobalt in sulfided, supported, and unsupported Co / Mo catalysts. *Journal of Catalysis* **1982**, *77* (2), 397-409.

56. Brainard, W. A.; Wheeler, D. R., An XPS study of the adherence of refractory carbide silicide and boride rf-sputtered wear-resistant coatings. *Journal of Vacuum Science and Technology* **1978**, *15* (6), 1800-1805.

57. Nefedov, V.; Firsov, M.; Shaplygin, I., Electronic structures of MRhO<sub>2</sub>, MRh<sub>2</sub>O<sub>4</sub>, RhMO<sub>4</sub> and Rh<sub>2</sub>MO<sub>6</sub> on the basis of X-ray spectroscopy and ESCA data. *Journal of Electron Spectroscopy and Related Phenomena* **1982**, *26* (1), 65-78.

## FIGURES

**Figure 1.** (a): Device schematic. (b): Optical microscope image of a representative device. (c): Cross-sectional TEM of the device. (d) EDS spectra showing the signature of MoS<sub>2</sub> and the electrodes; Au (bottom) and Ti/Au (top).

**Figure 2.** (a): DC cycling: 1000 cycles indicating the low C-C variability and endurance of MoS<sub>2</sub> devices. (b): SET voltage comparison of (i) MoS<sub>2</sub>/Ti/Au and (ii) a-Si/Ag-Cu based device where MoS<sub>2</sub> device exhibits a tight distribution of 0.04 V for 100 cycles (c): RESET power distribution of (i) MoS<sub>2</sub>/Ti/Au device and (ii) a-Si/Ag-Cu device. (d). (i): SET voltage distribution observed in 12 MoS<sub>2</sub>/Ti/Au devices for >100 cycles. (ii): Coefficient of variation (CV) in the SET voltages in MoS<sub>2</sub>. (e). (i): RESET power distribution observed in 12 MoS<sub>2</sub>/Ti/Au devices for >100 cycles. (ii): Coefficient of variation (CV) in the RESET power in MoS<sub>2</sub> devices.

**Figure 3.** (a): DC potentiation and depression. (b): Retention of ~300 s for 26 distinct states. (c): Weight update characteristics repeated for 100 times. Inset: Pulsing scheme for each cycle. (d): ANL comparison of MoS<sub>2</sub> synapse (over 100 cycles) with a-Si synapse (over 10 cycles). MoS<sub>2</sub> synapses exhibit a tighter distribution in the ANL over the entire 100 cycles. (e): Mean of the ANL extracted for 50 cycles plotted for 10 MoS<sub>2</sub> devices shows low variation. This is compared with the mean of the ANL extracted for 5 cycles plotted for 10 a-Si devices. (f): The standard deviation (SD) of ANL for 50 cycles in MoS<sub>2</sub> devices is compared with the SD of ANL for 5 cycles in a-Si based devices for 10 devices in each case.

**Figure 4.** (a)(i): Area-dependent current scaling in MoS<sub>2</sub> devices of 4 different areas measured for  $\sim 50$  cycles in each case. (ii): HRS and LRS scaling for the 4 different areas, indicating the role played by the interface at MoS<sub>2</sub>/Ti top electrode. The error bars represent data for 50 cycles. (b): Temperature-dependent I-V at HRS state showing the increase in OFF current with increasing temperature. Ohmic conduction in lower voltage regimes of the HRS states. Shallow trap SCLC, and SCLC conduction mechanisms at higher voltages in HRS. (c): Temperature-dependent I-V at LRS state where the ON current increases with increasing temperature. Ohmic conduction in lower voltage regimes of the LRS states and shallow trap SCLC, and SCLC conduction mechanisms at higher voltages in LRS. (d): Band diagram indicating (i) the ohmic conduction observed for voltage  $< 0.3$  V. (ii) the shallow trap SCLC conduction mechanism at voltages between 0.3 V-0.6 V where the current through the device follows a quadratic relation. (iii) the SCLC conduction mechanism at higher voltages where the shallow traps are filled and the current through the device shows a higher than quadratic relation.

**Figure 5.** (a) SEM image of the pristine device with the FIB cutting location marked. (b) Cross-sectional TEM image of the lateral structure of the same pristine device in (a). (c) EELS map of the pristine device. (d) SEM image of the biased device (cycled 100 times) with the FIB cutting location marked. (e) Cross-sectional TEM image of the lateral structure of the same biased device in (d). (f) EELS map of the biased device. Scale in (a) and (d): 5  $\mu$ m, scale in (b) and (e): 10 nm. (g). XPS spectra of Ti (2p), Mo (3d) and S(2p). (i) The binding energies of the  $2p_{3/2}$  peaks are found at 455.1 eV, 456.2 eV and 457.6 eV correspond to the presence of TiO, TiS<sub>2</sub> and TiOS. (ii) Mo (3d<sub>5/2</sub>) peaks at 228.7 eV, 227.3 eV and 233.1 eV correspond to the presence of MoS<sub>2</sub>, MoSi<sub>2</sub> and MoO<sub>3</sub>. (iii) S (2p) spectra indicating the formation of MoS<sub>2</sub>, TiS<sub>2</sub> and TiOS due to the presence of peak binding energies at 162.4 eV, 161.09 eV and 163.4 eV.

**Figure 6.** **(a)**: Schematic of two-input AND gate implementation. **b**: Spiking output with corresponding inputs applied to the circuit. **(c)**: Number of current spikes obtained from MoS<sub>2</sub> neuron as a function of time for (0,0), (0,1), (1,0) and (1,1) conditions. **(d)**: Schematic of two-input OR gate implementation. **(e)**: Spiking output with corresponding inputs applied to the circuit **(f)**: Number of current spikes obtained from MoS<sub>2</sub> neuron as a function of time for (0,0), (0,1), (1,0) and (1,1) conditions. **(g)**: Schematic of NOT gate implementation. **(h)**: Spiking output with corresponding inputs applied to the circuit **(i)**: Number of current spikes obtained from MoS<sub>2</sub> neuron as a function of time for (0) and (1) conditions.

## TOC