# Activating thick buried p-GaN for device applications

Yunwei Ma, Ming Xiao, Zhonghao Du, Lei Wang, Eric Carlson, Louis Guido, Han Wang, *Senior Member, IEEE*, Lai Wang, Yi Luo, and Yuhao Zhang, *Member, IEEE*

**Abstract**— Many emerging GaN electronic and optoelectronic devices comprise p-GaN layers buried below n-GaN or AlGaN. The activation of these buried p-GaN layers usually relies on the lateral hydrogen diffusion through the etched mesa sidewalls, which is known to induce non-uniform acceptor distributions. However, the acceptor profile, electric field (E-field) blocking capability, and leakage current mechanisms of the sidewall activated p-GaN layer have not been fully understood. This work addresses these knowledge gaps by fabricating vertical GaN p-n diodes with a thick (3.8  $\mu\text{m}$ ) p-GaN. Two activation schemes were performed to allow the hydrogen diffusion through sidewalls and the top surface, respectively. For the sidewall activation, an analytical model was developed to depict the spatial distribution of the activated acceptor and the temporal evolution of this distribution with the increased annealing time. This model was validated using the C-V characteristics of the fabricated diodes with various radii. Under reverse biases, the breakdown E-field and leakage current of the sidewall-activated diodes were found to be determined only by the edge area with the highest activation efficiency. The leakage mechanism agrees with the trap-assisted tunneling model, and the peak junction E-field can exceed 3 MV/cm, both being similar to those of surface-activated diodes. These results provide critical information for the design and processing of advanced GaN devices with the buried p-GaN.

**Index Terms**— Gallium nitride, p-n diode, power electronics, p-GaN, activation, leakage current, breakdown voltage, MOCVD

## I. INTRODUCTION

P-type GaN has become a critical building block in many GaN devices [1], [2], e.g., diodes [3]–[6], high electron mobility transistors (HEMTs) [7]–[11], current-aperture vertical electron transistors (CAVETs) [12], MOSFETs [13], [14], and JFETs [15], [16]. These GaN devices use p-n junctions for electrostatic control [11]–[13], electric field (E-field) management [3]–[7], [12]–[15], and conductivity modulation [16], [17]. While p-GaN is often the topmost layer, it is buried below n-type GaN in many devices, e.g., CAVETs, trench MOSFETs, and tunnel-junction light emitting diodes [18]–[21]. Meanwhile, emerging devices like superjunction transistors [22]–[24] and reduced-surface-field (RESURF) HEMTs [25] require thick p-GaN layers (at least several micron-meters) below n-GaN or AlGaN.

The Virginia Tech work was supported by the Office of Naval Research monitored by Lynn Petersen under Grant N00014-21-1-2183, the National Science Foundation under Grant ECCS-2036740, and the Center for Power Electronics Systems Power Management Consortium. The USC work was supported by the Center of Excellence in NanoBiophysics. (*Corresponding Authors*: Ming Xiao, Han Wang, Lai Wang, Yuhao Zhang).

Y. Ma, M. Xiao, and Y. Zhang are with the Center of Power Electronics Systems, Virginia Polytechnic Institute and State University (Virginia Tech), Blacksburg, VA 24060 USA (email: mxiao@vt.edu, yhzhang@vt.edu)

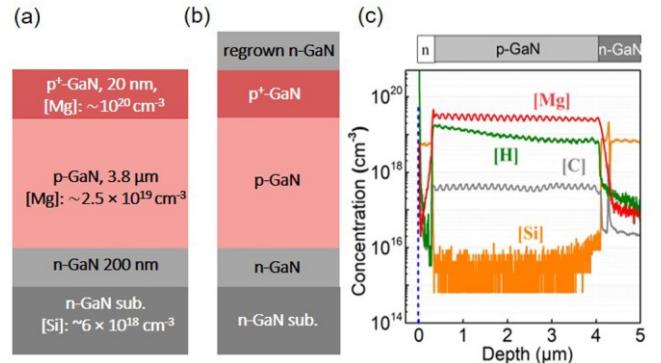

Fig. 1. Schematic of the (a) as-grown epitaxial structure and (b) the structure with a regrown n-GaN layer. (c) SIMS data of [Mg], [H], [Si] and [C] concentrations in the n-p-n structure after the n-GaN regrowth.

P-GaN is usually epitaxially grown by metal organic chemical vapor deposition (MOCVD) using the acceptor magnesium (Mg). However, the hydrogen (H) in MOCVD forms Mg-H complexes and passivates [Mg] acceptors [26]. A post-growth annealing is routinely used to activate p-GaN, which breaks Mg-H bonds, allowing the [H] to diffuse to the ambient through the top p-GaN surface. However, this through-surface activation is not viable for buried p-GaN due to a very high [H] diffusion barrier in n-GaN [26]. Even after p-GaN is activated, any further MOCVD epitaxy will re-passivate it [27]. As a solution, molecular beam epitaxy was used for regrowing the top layers after p-GaN activation [19]. However, the sample transfer between multiple chambers has been widely reported to introduce impurities [28]–[30].

A more popular solution for the buried p-GaN activation is the lateral [H] diffusion through the etched mesa sidewalls [10], [17], [23], [27], [28]. Li *et al.* found that the full activation can only be achieved in a small device area with a dimension of 10–20  $\mu\text{m}$  [27]. This suggests that the buried p-GaN in large-area devices is likely to be partially activated. Recently, Narita *et al.* studied the [H] diffusion dynamics in larger-area buried p-GaN [31]. However, vast knowledge gaps persist on the acceptor profile, E-field blocking capability, and leakage current mechanisms of this partially-activated, non-uniform p-GaN. Addressing these gaps is critical to any GaN device comprising the buried p-GaN, particularly for power electronic devices.

Eric Carlson and Louis Guido are with the Bradley Department of Electrical and Computer Engineering, Virginia Polytechnic Institute and State University, Blacksburg, VA 24060 USA

Z. Du and H. Wang are with the Ming Hsieh Department of Electrical and Computer Engineering, University of Southern California, Los Angeles, California 90086, USA.

Lei Wang, Lai Wang and Yi Luo are with Beijing National Research Center for Information Science and Technology (BNRist), Department of Electronic Engineering, Tsinghua University, Beijing 100084, China (email: wanglai@mail.tsinghua.edu.cn)

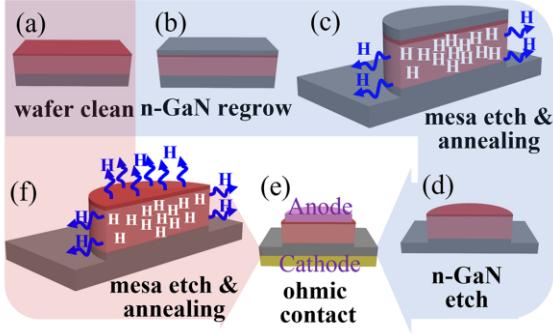

Fig. 2. Major fabrication steps of GaN diodes (a)-(e) with sidewall activation (blue background arrow) and (f) with surface and sidewall activations (red background arrow).

This work probes the dopant profile and electrical characteristics of a sidewall-activated buried p-GaN layer, by characterizing vertical GaN p-n diodes comprising it. Different from prior works [27], [31], [32], a thick p-GaN is employed to avoid its punch-through and allow the study of its leakage mechanisms. Thick buried p-GaN is also essential for future superjunction and RESURF devices. The surface potential mapping by the Kelvin probe force microscopy (KPFM) was used to confirm the partial activation. A model for the activation profile was established and calibrated by C-V characteristics of the fabricated diodes with various radii. The reverse breakdown and leakage mechanisms of the diodes with non-, sidewall-, and surface- (i.e., fully) activated p-GaN layers are also unveiled.

## II. FABRICATION PROCESS

The epitaxial structure consists of a 20 nm p<sup>+</sup>-GaN layer ([Mg]:  $1 \times 10^{20} \text{ cm}^{-3}$ ), a 3.8  $\mu\text{m}$  p-GaN layer ([Mg]:  $\sim 2.5 \times 10^{19} \text{ cm}^{-3}$ ) and a 200 nm n-GaN layer ([Si]:  $7.5 \times 10^{18} \text{ cm}^{-3}$ ) grown on GaN substrates by MOCVD [Fig. 1(a)]. On top of some samples, a 300 nm n-GaN layer ([Si]:  $5 \times 10^{18} \text{ cm}^{-3}$ ) was regrown in MOCVD, which prevents the [H] diffusion through top surfaces [Fig. 1(b)]. Fig. 1(c) shows the concentrations of [Mg], [H], [Si] and [C] in a sample with the regrown n-GaN cap measured by secondary-ion mass spectrometry (SIMS). A high [H] concentration of  $\sim 10^{19} \text{ cm}^{-3}$  is exhibited in the p-GaN layer after the n-GaN regrowth.

Fig. 2 shows the major fabrication steps of vertical GaN p-n diodes. After the wafer cleaning (Fig. 2(a)) and n-GaN regrowth (Fig. 2(b)), a 5  $\mu\text{m}$  deep mesa etch was performed using a Cr/Ni hard mask and Cl<sub>2</sub> gas, in which 10 nm Cr is used to enhance the adhesion and reduce the stress, followed by a rinse in 5% TMAH to remove the etch damages [33]. The activation annealing was at 800 °C in N<sub>2</sub> for 0.5-1 hours (Fig. 2(c)). Then the n-GaN cap layer was etched (Fig. 2(d)), followed by the formation of the anode by Pd/Ni/Au with a 600 °C annealing in N<sub>2</sub> for 5 minutes. The cathode was formed by Ti/Al/Ni/Au (Fig. 2(e)). A control diode was fabricated without n-GaN caps during the p-GaN activation, allowing the via-surface [H] release and thus a full activation (Fig. 2(f)). Another control diode without p-GaN activation was also fabricated. The radii of all three types of diodes range from 5  $\mu\text{m}$  to 100  $\mu\text{m}$ .

## III. MATERIAL AND DEVICE CHARACTERIZATIONS

The activated acceptor ( $N_A$ ) profile in the sidewall-activated p-GaN was first probed by KPFM, which enables nanometer-

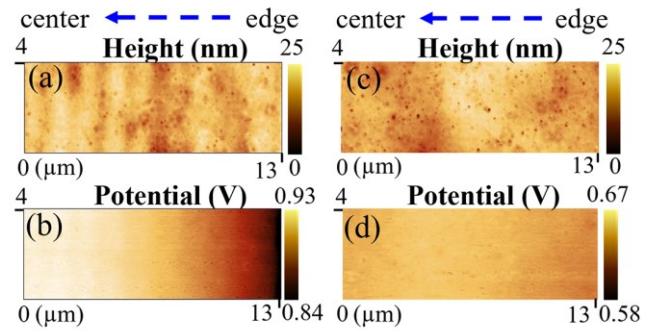

Fig. 3. (a) Surface morphology and (b) potential on a sidewall-activated p-GaN. (c) Surface morphology and (d) potential on a fully-activated (i.e., surface-activated) p-GaN.

scale mapping of surface potentials [34] and has been recently employed to map the dopant profiles in GaN p-n junctions [35], [36]. The KPFM measurement was performed in a Bruker DIMENSION system with a SCM-PIT-V2 tip. The n-GaN substrate was grounded. The cantilever measured the surface topography in the first scan and followed the stored surface topography at a certain lift height (100 nm) during the second interleave scan to record the electrostatic force that reflects the surface potential under an ac bias applied to the tip. The ac bias frequency was set to be the tip resonant frequency, and a DC bias was applied on the feedback loop to compensate the work function difference between the tip and the sample surface. Before the KPFM characterization, the p<sup>+</sup>-GaN cap layer and Ohmic metal were etched, followed by a long TMAH treatment to reduce the etch damage [30].

Fig. 3(a) and (b) show the p-GaN surface morphology and potential, respectively, after the sidewall activation for 0.5 hours. The surface potential increases from the diode edge towards the center without correlations to morphology features, suggesting a non-uniform  $N_A$  distribution that decreases from the edge towards the center. Note that, due to the impact of surface states and surface band bending,  $N_A$  gradients can only be qualitatively reflected but difficult to be quantitatively derived from the surface potential profile [35]. Fig. 3(c) and (d) show the surface morphology and potential of a fully activated p-GaN (i.e., by surface activation), revealing a nearly uniform surface potential with a magnitude lower than that shown in Fig. 3(b). This suggests a uniform and higher  $N_A$  in the fully activated p-GaN as compared to the sidewall-activated one.

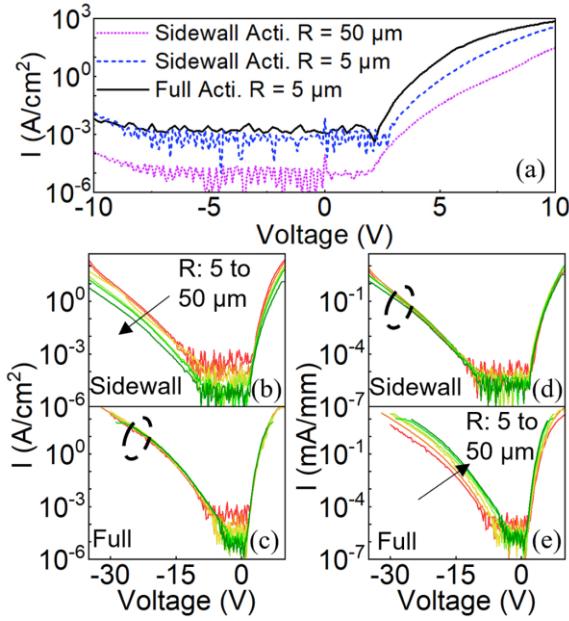

Fig. 4(a) shows the I-V characteristics of the sidewall activated diodes with a radius ( $R$ ) of 5  $\mu\text{m}$  and 50  $\mu\text{m}$  as well as the fully (surface) activated diode with a  $R$  of 5  $\mu\text{m}$ . All three diodes show good rectifying behaviors. The forward current of the two diodes with  $R = 5 \mu\text{m}$  are similar, while that of the sidewall-activated diodes with  $R = 50 \mu\text{m}$  is much lower. This suggests a strong radius dependence on the average activation ratio in the sidewall-activated diodes. The slightly higher turn-on voltage in the sidewall activated diode is due to the inferior Ohmic contact formed on the etched p-GaN surface.

Fig. 4(b)-(e) show the I-V characteristics of the fully (surface)- and sidewall-activated diodes with  $R$  of 5~50  $\mu\text{m}$ . As the leakage current along the etched sidewall is a concern in some GaN devices [37], [38], the fully-activated diodes are examined first. The current densities of fully-activated diodes are proportional to the area instead of perimeter, validating that

Fig. 4. (a) I-V characteristics of fully- and sidewall-activated diodes with a radius of 5 and 50  $\mu\text{m}$ . The lower noise current density for  $R = 50 \mu\text{m}$  diode is due to the same noise floor of the curve tracer normalized to a larger area. I-V characteristics of the (b) sidewall and (c) fully activated diodes with radii from 5 to 50  $\mu\text{m}$ , normalized to the anode area. The same I-V curves for (d) sidewall and (e) fully activated diodes normalized to the perimeter.

the leakage current is dominated by the bulk junction, and that along the etched sidewall is minimal. By contrast, the current densities of the sidewall-activated diodes normalized to the area show a large discrepancy, while those normalized to the perimeter overlap. These results further confirm the non-uniform  $N_A$  with a high activation efficiency near the sidewall.

#### IV. ACCEPTOR MODEL AND CALIBRATION

In this section, we establish a [H] diffusion model in the buried p-GaN to quantify the spatial and temporal profile of the activation ratio ( $\eta$ ), i.e., the ratio between the activated acceptor  $N_A$  and the total ionizable acceptor concentration ( $N_A^0$ ). Here  $N_A^0$  was extracted to be  $1 \times 10^{19} \text{ cm}^{-3}$  from the C-V data of the fully-activated diodes. Note that,  $N_A^0 < [\text{Mg}]$  is commonly observed in p-GaN with  $[\text{Mg}] > 10^{19} \text{ cm}^{-3}$ . This is because there are two types of Mg-H complexes: the metastable one leading to the Mg acceptor after annealing (i.e., corresponding to  $N_A^0$ ), the other one being stable and electrically inactive [39].

In circular diodes, the [H] concentration can be depicted by a generic diffusion equation in the cylindrical coordinate [26]:

$$D \frac{1}{r} \frac{\partial}{\partial r} \left( r \frac{\partial [H]}{\partial r} \right) = \frac{\partial [H]}{\partial t} \quad (1)$$

where  $r$  is the radial distance,  $t$  is the annealing time, and  $D$  is the [H] diffusion coefficient. The diffusion along the axial direction can be ignored due to a much lower  $D$  for [H] in n-GaN as compared to that in p-GaN [31]. A boundary condition in the center that describes the zero [H] concentration gradient and the other one depicting the sidewall diffusion barrier as well as the initial [H] concentration can be written as [26]:

$$\frac{\partial [H]}{\partial r} \Big|_{r=0,t=0} = 0 \quad (2)$$

$$\frac{d}{dt} \left( \frac{[H]_{r=R,t=0}}{[H]_{r=R,t}} \right) = A \quad (3)$$

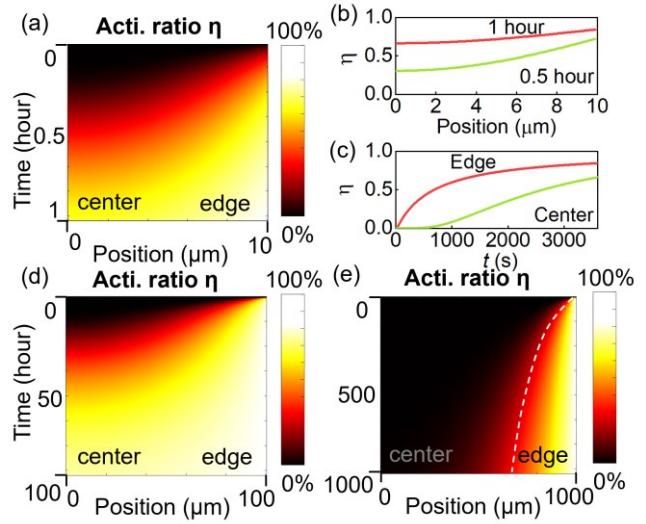

Fig. 5. (a) Spatial-temporal contour of  $\eta$  for a sidewall-activated p-GaN with  $R = 10 \mu\text{m}$ . (b) Extracted  $\eta$  profile along a radius direction after 0.5- and 1-hour activation. (c) Temporal evolution of  $\eta$  at the device edge and center. Spatial-temporal contour of  $\eta$  for (d)  $R = 0.1 \text{ mm}$  p-GaN up to 100 hours of activation and (e)  $R = 1 \text{ mm}$  p-GaN up to 1000 hours of activation.

$$[H]_{r,t=0} \approx N_A^0 = 1 \times 10^{19} \text{ cm}^{-3} \quad (4)$$

where  $A$  is a constant related to the sidewall surface barrier for [H] desorption. The model calibration (will be detailed soon) produces a  $D$  of  $1.4 \times 10^{-10} \text{ cm}^2 \text{s}^{-1}$  and an  $A$  of  $1.5 \times 10^{-3} \text{ s}^{-1}$  for our samples. In (4), we assume that almost all  $N_A^0$  is initially passivated by [H]. This assumption was validated by the C-V measurements of a non-activated diode, in which an acceptor concentration of  $1 \sim 2 \times 10^{17} \text{ cm}^{-3}$  was extracted. This suggests an initial  $\eta$  of only  $1 \sim 2\%$ . The SIMS profile in Fig. 1 also reveals an average [H] concentration of  $\sim 1 \times 10^{19} \text{ cm}^{-3}$ , which is similar to  $N_A^0$ , further supporting (4).

Fig. 5(a) shows the modeled  $\eta$  as a function of  $r$  and  $t$  in a sidewall-activated p-GaN with  $R$  of  $10 \mu\text{m}$ . Fig. 5(b) shows two cutlines of the  $\eta$  spatial distribution after 0.5 and 1 hours annealing. After 1 hour annealing,  $\eta$  is close to 84% near the edge and  $\sim 66\%$  in the center. Fig. 5(c) shows two cutlines of the  $\eta$  temporal evolution at the edge and center. The activation first occurs at the edge and saturates early there; the activation in the center shows an initial delay and ramps up later.

Fig. 5(d) and (e) show the modeled spatial-temporal distribution of  $\eta$  for two larger p-GaN regions with a  $R$  of  $0.1$  and  $1 \text{ mm}$ . A 100-hour annealing is predicted to fully activate the former p-GaN, while a 1000-hour annealing is still insufficient for the latter p-GaN. As shown in Fig. 5(e), for a large  $R$ , the contour of the activation boundary in the cylindrical coordinate roughly follows a  $t \propto d^2$  relation, where  $d$  is the radial distance to the sidewall. This suggests a fast increase in  $t$  that is required to fully activate a larger p-GaN area.

To calibrate our model, C-V characteristics were measured for the sidewall-activated diodes with various radii after 1 hour activation, which were then compared with the modeled C-V curve using the profile of the ionized acceptor concentration ( $N_A$ ) extracted above. Note that the C-V measurement directly extracts  $N_A$ ; by contrast, I-V characteristics are usually affected by incomplete ionization and contact resistance and thereby less suitable for model calibration.

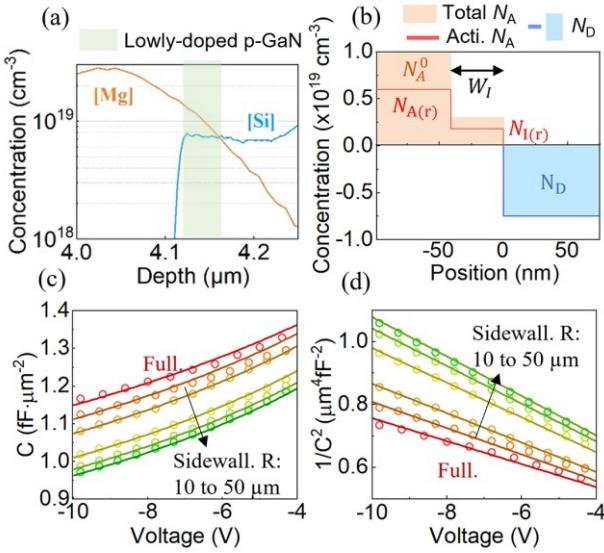

Fig. 6. (a) Zoom-in view of the [Mg] and [Si] profile near the p-n junction. (b) Simplified model for the interfacial p-GaN region, consisting of a lowly doped region with an effective acceptor concentration  $N_{A(r)}$  and a width  $W_I$ ; the ionized acceptor (red line) is lower than the total acceptor concentration due to the non-100% activation efficiency. (c) C-V characteristics and (d)  $1/C^2$ -V plot of the fully activated diodes (red) and sidewall activated device with  $R$  from 10 to 50  $\mu\text{m}$  (orange to green) after 1 hour activation. The solid lines are modeling results and circular symbols are experimental results.

If the dopant profile near the p-n junction is scrutinized, one can find that the junction may not be best described as an abrupt junction. As shown in Fig. 6(a), while [Si] increase is sharp, [Mg] shows a tailing effect, producing a  $\sim 50$  nm wide region with  $[\text{Mg}] > [\text{Si}]$ . As the interface is not our main focus, for the capacitance modeling, we used a lowly doped p-GaN region with an effectively average  $N_A$  to represent this gradient p-GaN region close to the p-n junction. As shown in Fig. 6(b), the acceptor/donor concentration along the vertical axis ( $Z$  axis with  $Z = 0$  at the p-n junction) can be written as

$$N_{A(r)} = N_A^0 - [H]_{(r)} = \eta_{(r)} \cdot N_A^0 \quad (Z < W_I) \\ N_{I(r)} \quad (W_I < Z < 0) \\ N_{D(r)} = N_D \quad (Z > 0) \quad (5)$$

where  $N_{A(r)}$  and  $\eta_{(r)}$  are the  $N_A$  and  $\eta$  at the radius  $r$ ;  $N_{I(r)}$  and  $W_I$  are the effective  $N_A$  and width of the interfacial region with gradient doping;  $N_D$  is the donor concentration in n-GaN.

The model in (5) was first applied to fit the C-V data of the fully-activated diodes (Fig. 6(c)), the model of which is based on a 100%  $\eta_{(r)}$ . The fitting gives a  $N_I = 0.3 \cdot N_A^0$  and  $W_I = 41$  nm, which generally accord with the SIMS data shown in Fig. 6(a). For sidewall-activated diodes with the  $N_A$  dependent on  $r$ , we assume the same  $W_I$  and a  $r$ -dependent  $N_I$  that follows  $N_{I(r)} = 0.3 \cdot N_{A(r)}$ . Note that, at a reverse bias  $V$ , the  $N_{A(r)}$  profile will produce a depletion width dependent on  $r$  and a non-planar depletion front in p-GaN, and the total depletion capacitance ( $C_{(V)}$ ) can be calculated by integrating the specific capacitance ( $c_{(r,V)}$ ) along  $r$  up to  $r = R$ :

$$c_{(r,V)} = \frac{\epsilon}{W_{\text{dep}}} = \sqrt{\frac{\epsilon^2 q N_{A(r)} N_D}{2\epsilon (N_{A(r)} + N_D) (\phi_{bi} - V) + \delta_{(r)}}} \quad (6)$$

$$C_{(V)} = \int_0^R 2\pi r c_{(r,V)} dr \quad (7)$$

where  $W_{\text{dep}}$  is the local depletion width,  $\phi_{bi}$  is the built-in potential of the GaN p-n junction, and  $\epsilon$  is GaN's permittivity.  $\delta_{(r)}$  is a term related to the lowly-doped p-GaN close to the junction. Based on the Poisson equation as well as the E-field and potential continuity,  $\delta_{(r)}$  can be calculated as

$$\delta_{(r)} = q W_I^2 (N_{A(r)} N_D + N_{A(r)} N_{I(r)} - N_{I(r)}^2) - N_D N_{I(r)} \quad (8)$$

The modeled C-V characteristics based on (1)-(8) for fully-activated diodes and sidewall-activated diodes with various radii show a good agreement with the experimental C-V data of the counterpart devices (Fig. 6(c)). The aforementioned  $D$  and  $A$  values that provide the best fitting are also consistent with prior reports ( $D = 10^{-8}\sim 10^{-11} \text{ cm}^2/\text{s}$  [21], [27], [31],  $A \sim 10^{-3} / \text{s}$  [26], [31]). Here the C-V calibration was performed at reverse biases below -4 V to ensure that the depletion region has extended beyond the junction region into the bulk p-GaN region, i.e., the region of our interest in this work.

For these diodes that comprise the p-GaN with non-uniform  $N_{A(r)}$ , interestingly, their  $1/C^2 \sim V$  data shows a good linearity similarly to the uniformly-doped diodes, as shown in Fig. 6(d). This suggests the viability to extract a radius-average  $N_A$  that will give rise to the same  $C$  as  $N_{A(r)}$  does for a  $r$  range from 0 to  $R$ . Note that, despite the feasibility of such extraction using the slope of  $1/C^2 \sim V$  data, their x-axis intercept is  $R$  dependent and larger than  $\phi_{bi}$  of GaN p-n junction, due to the  $\delta_{(r)}$  term.

## V. BREAKDOWN AND LEAKAGE MECHANISM

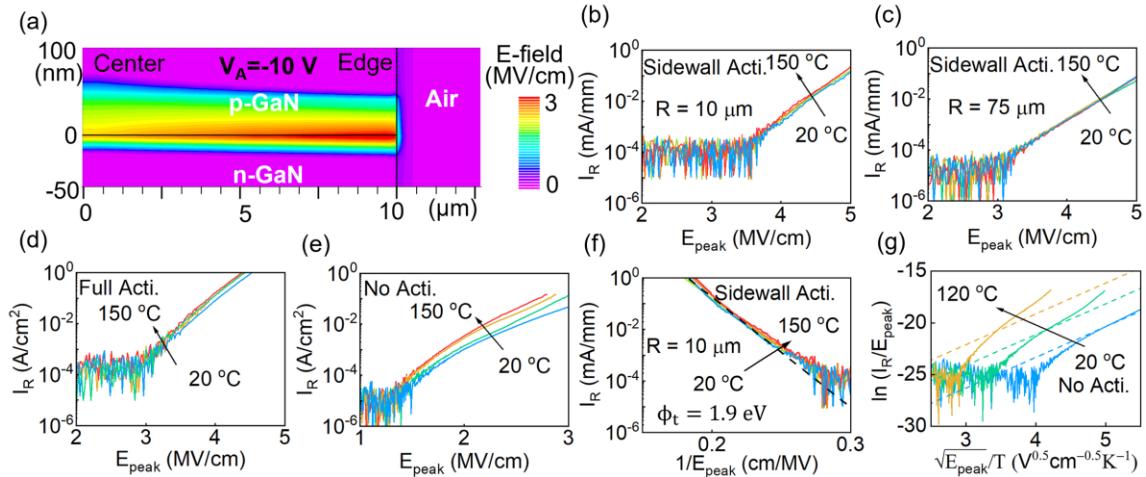

Despite the knowledge of the  $N_{A(r)}$  profile, the breakdown and leakage mechanisms of the partially activated p-GaN remain unclear. TCAD simulations were performed in Silvaco Atlas for GaN p-n diodes with such a  $N_{A(r)}$  profile. The device models are based on our prior reports [24], [40], and the  $N_{A(r)}$  profile is implemented through fine meshing. Fig. 7(a) shows the simulated E-field in a sidewall-activated GaN p-n diode with  $R = 10 \mu\text{m}$  and  $t = 0.5$  hour at a reverse bias of -10 V, revealing a peak E-field at the device edge.

To probe the leakage mechanisms, the reverse leakage current ( $I_R$ ) normalized to device perimeter is plotted against the peak E-field at the edge ( $E_{\text{peak}}$ ). Similar to the capacitance derivation,  $E_{\text{peak}}$  can be derived using the modeled  $N_{A(R)}$ :

$$E_{\text{peak}} = \frac{q W_I N_D (N_{I(R)} - N_{A(R)}) + \epsilon q N_{A(R)} N_D / c_{(R,V)}}{(N_{A(R)} + N_D) \epsilon} \quad (9)$$

where  $c_{(R,V)}$  is calculated from (6). Fig. 7(b) and (c) show the  $I_R$  v.s.  $E_{\text{peak}}$  characteristics converted from the experimental I-V characteristics for two sidewall-activated diodes with  $R$  of 10 and 75  $\mu\text{m}$  at various temperatures from 20  $^{\circ}\text{C}$  to 150  $^{\circ}\text{C}$ . The annealing time of two diodes are both 0.5 hours. Note that p-GaN in both diodes are partially activated.  $N_{A(R)}$  is determined by our model to be  $7.2 \times 10^{18} \text{ cm}^{-3}$  for  $R = 10 \mu\text{m}$  after 0.5 hour activation [see Fig. 5(b)].

Although most area of the 75  $\mu\text{m}$  diode is not activated, its  $I_R$  characteristics is almost identical to that of the 10  $\mu\text{m}$  diode. This suggests that the leakage current is dominated by the edge area with the highest  $\eta$ . Note that, as the activation first occurs at the edge area [see Fig. 5(c)], the local  $\eta$  is modeled to be similar in the diodes with different  $R$ .

Fig. 7(d) and (e) show the  $I_R$  v.s.  $E_{\text{peak}}$  characteristics of the fully(surface)-activated and non-activated diodes. Here  $I_R$  is

Fig. 7. (a) Simulated E-field contours in a sidewall-activated p-n diode with  $R = 10 \mu\text{m}$  at a reverse bias of  $-10 \text{ V}$ .  $I_R$  v.s.  $E_{\text{peak}}$  characteristic of the sidewall-activated diodes with  $R$  of (b)  $10 \mu\text{m}$  and (c)  $75 \mu\text{m}$  as well as the (d) fully- and (e) non-activated p-n diodes at temperatures of  $20, 70, 120$  and  $150 \text{ }^{\circ}\text{C}$ . (f)  $I_R$  v.s.  $1/E_{\text{peak}}$  plot and fitting for the sidewall-activated diodes. (g)  $\ln(I_R/E_{\text{peak}})$  v.s.  $\sqrt{E_{\text{peak}}/T}$  plot and fitting for the non-activated diodes. Note that the difference in the noise current density is due to the same noise floor of the curve tracer normalized to a different area/perimeter.

normalized to device area due to the uniform  $N_A$ , and  $E_{\text{peak}}$  represents the junction E-field that is calculated using the  $N_A$  extracted from C-V data. The  $I_R$ - $E_{\text{peak}}$ - $T$  characteristics of fully- and partially-activated diodes are similar, both showing little  $T$  dependence, while the  $I_R$ - $E_{\text{peak}}$  characteristics of non-activated diodes are quite different and show a strong  $T$  dependence. Both fully- and partially-activated diodes can sustain a  $E_{\text{peak}}$  of at least  $3 \text{ MV/cm}$  before the leakage current ramps up beyond the noise floor. Note that the critical E-field of GaN at a similar  $N_A$  and  $N_D$  levels (i.e.,  $10^{18}$ – $10^{19} \text{ cm}^{-3}$ ) is predicted to be  $\sim 5 \text{ MV/cm}$  [41]. In comparison, the non-activated diode can only sustain a  $E_{\text{peak}}$  of  $\sim 1.3 \text{ MV/cm}$  before the rise of leakage current.

The E-field and temperature dependence of  $I_R$  in fully- and partially-activated diodes were found to be consistent with the trap-assisted tunneling (TAT) across the barrier of the p-n junction [42], [43]. This TAT current is weakly dependent on  $T$  and can be modeled as [42], [43]

$$J_{\text{TAT}} \propto \exp\left(\frac{-8\pi\sqrt{2qm_n^*}}{3hE}\phi_t^3\right) \quad (10)$$

where  $m_n^*$  is the electron effective mass,  $h$  is the Planck's constant, and  $\phi_t$  is the trap energy level. Fig. 7(f) shows the good linearity between  $\ln(I_R)$  and  $1/E_{\text{peak}}$  for a typical sidewall-activated diode, confirming the TAT model. A  $\phi_t \sim 1.9 \text{ eV}$  below conduction band is extracted from the fitting, which may correlate to threading dislocations [44].

Finally, the leakage mechanism of non-activated diodes was found to agree with the Poole-Frenkel (PF) emission model, i.e., the E-field assisted trap ionization and carrier emission to the conduction band [16], [45]. The PF model features a linear relation between  $\ln(I_R/E)$  and  $\sqrt{E}/T$  [16], [45], which agrees with the experimental  $I_R$ - $E_{\text{peak}}$ - $T$  characteristics of the non-activated diodes (Fig. 7(g)). This PF mechanism, in conjunction with the lower sustainable  $E_{\text{peak}}$ , are consistent with the expectation from a high trap concentration in the non-activated p-GaN. At  $70$  and  $120 \text{ }^{\circ}\text{C}$ ,  $I_R$  shows a faster increase with  $E_{\text{peak}}$  than the prediction by the PF model, implying contributions from other leakage mechanism at elevated temperatures, which could be the variable-range-hopping along trap states [45], [46].

## VI. SUMMARY AND DISCUSSION

In summary, this work unveils the  $N_A$  activation efficiency profile, E-field distribution, and leakage mechanisms of a thick buried p-GaN activated through the etched sidewalls. Our model reveals the spatial  $N_A$  distribution and its evolution with the annealing time. The partially activated GaN p-n junction was found to be able to block a high E-field over  $3 \text{ MV/cm}$  with a leakage current mechanism similar to that in the fully activated counterpart. Whereas its breakdown field and leakage current are only determined by the edge area.

These results can provide two major implications for the buried p-GaN activated at different annealing conditions. First, our model contains two fitting parameters,  $D$  and  $A$ , which are processing-related. For example,  $D$  and  $A$  may be altered by the annealing temperature and ambient atmosphere, respectively. Second, as the edge area dominates the breakdown field and leakage current, the blocking characteristics of the sidewall activated p-n junction can be insensitive to the annealing condition, given a sufficient annealing time. This is because the  $\eta$  at the edge region can approach 100% for a sufficient annealing time, regardless of the activation temperature, ambient atmosphere and device size.

These results and implications provide key information for the future design and processing of large-area, advanced GaN devices comprising the buried p-GaN (e.g., GaN superjunction devices).

## ACKNOWLEDGEMENT

We thank collaborations with Silvaco for device simulations.

## REFERENCES

- [1] S. Nakamura, M. S. M. Senoh, and T. M. T. Mukai, "P-GaN/N-InGaN/N-GaN Double-Heterostructure Blue-Light-Emitting Diodes," *Jpn. J. Appl. Phys.*, vol. 32, no. 1A, p. L8, Jan. 1993, doi: 10.1143/JJAP.32.L8.

- [2] K. Hoo Teo, Y. Zhang, N. Chowdhury, S. Rakheja, R. Ma, Q. Xie, E. Yagyu, K. Yamanaka, K. Li, and T. Palacios, "Emerging GaN technologies for power, RF, digital, and quantum computing

applications: Recent advances and prospects," *J. Appl. Phys.*, vol. 130, no. 16, p. 160902, Oct. 2021, doi: 10.1063/5.0061555.

[3] Y. Zhang, Z. Liu, M. J. Tadjer, M. Sun, D. Piedra, C. Hatem, T. J. Anderson, L. E. Luna, A. Nath, A. D. Koehler, H. Okumura, J. Hu, X. Zhang, X. Gao, B. N. Feigelson, K. D. Hobart, and T. Palacios, "Vertical GaN Junction Barrier Schottky Rectifiers by Selective Ion Implantation," *IEEE Electron Device Lett.*, vol. 38, no. 8, pp. 1097–1100, Aug. 2017, doi: 10.1109/LED.2017.2720689.

[4] I. C. Kizilayli, A. P. Edwards, H. Nie, D. Disney, and D. Bour, "High Voltage Vertical GaN p-n Diodes With Avalanche Capability," *IEEE Trans. Electron Devices*, vol. 60, no. 10, pp. 3067–3070, Oct. 2013, doi: 10.1109/TED.2013.2266644.

[5] M. Xiao, Y. Ma, K. Cheng, K. Liu, A. Xie, E. Beam, Y. Cao, and Y. Zhang, "3.3 kV Multi-Channel AlGaN/GaN Schottky Barrier Diodes With P-GaN Termination," *IEEE Electron Device Lett.*, vol. 41, no. 8, pp. 1177–1180, Aug. 2020, doi: 10.1109/LED.2020.3005934.

[6] M. Xiao, Y. Ma, K. Liu, K. Cheng, and Y. Zhang, "10 kV, 39 mΩ·cm<sup>2</sup> Multi-Channel AlGaN/GaN Schottky Barrier Diodes," *IEEE Electron Device Lett.*, vol. 42, no. 6, pp. 808–811, Jun. 2021, doi: 10.1109/LED.2021.3076802.

[7] M. Xiao, Y. Ma, Z. Du, V. Pathirana, K. Cheng, A. Xie, E. Beam, Y. Cao, F. Udrea, H. Wang, and Y. Zhang, "Multi-Channel Monolithic-Cascode HEMT (MC2-HEMT): A New GaN Power Switch up to 10 kV," in *2021 IEEE International Electron Devices Meeting (IEDM)*, Dec. 2021, p. 5.5.1-5.5.4, doi: 10.1109/IEDM19574.2021.9720714.

[8] Y. Zhang, A. Zubair, Z. Liu, M. Xiao, J. A. Perozek, Y. Ma, and T. Palacios, "GaN FinFETs and trigate devices for power and RF applications: review and perspective," *Semicond. Sci. Technol.*, vol. 36, no. 5, p. 054001, Mar. 2021, doi: 10.1088/1361-6641/abde17.

[9] Y. Ma, M. Xiao, Z. Du, X. Yan, K. Cheng, M. Clavel, M. K. Hudait, I. Kravchenko, H. Wang, and Y. Zhang, "Tri-gate GaN junction HEMT," *Appl. Phys. Lett.*, vol. 117, no. 14, p. 143506, Oct. 2020, doi: 10.1063/5.0025351.

[10] Y. Ma, M. Xiao, Z. Du, H. Wang, and Y. Zhang, "Tri-Gate GaN Junction HEMTs: Physics and Performance Space," *IEEE Trans. Electron Devices*, vol. 68, no. 10, pp. 4854–4861, Oct. 2021, doi: 10.1109/TED.2021.3103157.

[11] H. Amano *et al.*, "The 2018 GaN power electronics roadmap," *J. Phys. Appl. Phys.*, vol. 51, no. 16, p. 163001, 2018, doi: 10.1088/1361-6463/aaaf9d.

[12] S. Chowdhury, B. L. Swenson, and U. K. Mishra, "Enhancement and Depletion Mode AlGaN/GaN CAVET With Mg-Ion-Implanted GaN as Current Blocking Layer," *IEEE Electron Device Lett.*, vol. 29, no. 6, pp. 543–545, Jun. 2008, doi: 10.1109/LED.2008.922982.

[13] T. Oka, Y. Ueno, T. Ina, and K. Hasegawa, "Vertical GaN-based trench metal oxide semiconductor field-effect transistors on a free-standing GaN substrate with blocking voltage of 1.6 kV," *Appl. Phys. Express*, vol. 7, no. 2, p. 021002, Jan. 2014, doi: 10.7567/APEX.7.021002.

[14] C. Gupta, C. Lund, S. H. Chan, A. Agarwal, J. Liu, Y. Enatsu, S. Keller, and U. K. Mishra, "In Situ Oxide, GaN Interlayer-Based Vertical Trench MOSFET (OG-FET) on Bulk GaN substrates," *IEEE Electron Device Lett.*, vol. 38, no. 3, pp. 353–355, Mar. 2017, doi: 10.1109/LED.2017.2649599.

[15] Y. Zhang and T. Palacios, "(Ultra)Wide-Bandgap Vertical Power FinFETs," *IEEE Trans. Electron Devices*, vol. 67, no. 10, pp. 3960–3971, Oct. 2020, doi: 10.1109/TED.2020.3002880.

[16] J. Liu, M. Xiao, R. Zhang, S. Pidaparthi, H. Cui, A. Edwards, M. Craven, L. Bauburt, C. Drowley, and Y. Zhang, "1.2-kV Vertical GaN Fin-JFETs: High-Temperature Characteristics and Avalanche Capability," *IEEE Trans. Electron Devices*, vol. 68, no. 4, pp. 2025–2032, Apr. 2021, doi: 10.1109/TED.2021.3059192.

[17] Y. Uemoto, M. Hikita, H. Ueno, H. Matsuo, H. Ishida, M. Yanagihara, T. Ueda, T. Tanaka, and D. Ueda, "Gate Injection Transistor (GIT)—A Normally-Off AlGaN/GaN Power Transistor Using Conductivity Modulation," *IEEE Trans. Electron Devices*, vol. 54, no. 12, pp. 3393–3399, 2007, doi: 10.1109/TED.2007.908601.

[18] T. Takeuchi, G. Hasnain, S. Corzine, M. Hueschen, J. Richard P. Schneider, C. Kocot, M. Blomqvist, Y. Chang, D. Lefforge, M. R. Krames, L. W. Cook, and S. A. Stockman, "GaN-Based Light Emitting Diodes with Tunnel Junctions," *Jpn. J. Appl. Phys.*, vol. 40, no. 8B, p. L861, Aug. 2001, doi: 10.1143/JJAP.40.L861.

[19] E. C. Young, B. P. Yonkee, F. Wu, S. H. Oh, S. P. DenBaars, S. Nakamura, and J. S. Speck, "Hybrid tunnel junction contacts to III-nitride light-emitting diodes," *Appl. Phys. Express*, vol. 9, no. 2, p. 022102, Jan. 2016, doi: 10.7567/APEX.9.022102.

[20] H. Kurokawa, M. Kaga, T. Goda, M. Iwaya, T. Takeuchi, S. Kamiyama, I. Akasaki, and H. Amano, "Multijunction GaInN-based solar cells using a tunnel junction," *Appl. Phys. Express*, vol. 7, no. 3, p. 034104, Mar. 2014, doi: 10.7567/APEX.7.034104.

[21] Y. Kuwano, M. Kaga, T. Morita, K. Yamashita, K. Yagi, M. Iwaya, T. Takeuchi, S. Kamiyama, and I. Akasaki, "Lateral Hydrogen Diffusion at p-GaN Layers in Nitride-Based Light Emitting Diodes with Tunnel Junctions," *Jpn. J. Appl. Phys.*, vol. 52, no. 8S, p. 08JK12, Aug. 2013, doi: 10.7567/JJAP.52.08JK12.

[22] F. Udrea, G. Deboy, and T. Fujihira, "Superjunction Power Devices, History, Development, and Future Prospects," *IEEE Trans. Electron Devices*, vol. 64, no. 3, pp. 720–734, Mar. 2017, doi: 10.1109/TED.2017.2658344.

[23] Z. Li and T. P. Chow, "Design and Simulation of 5-20-kV GaN Enhancement-Mode Vertical Superjunction HEMT," *IEEE Trans. Electron Devices*, vol. 60, no. 10, pp. 3230–3237, Oct. 2013, doi: 10.1109/TED.2013.2266544.

[24] M. Xiao, R. Zhang, D. Dong, H. Wang, and Y. Zhang, "Design and Simulation of GaN Superjunction Transistors With 2-DEG Channels and Fin Channels," *IEEE J. Emerg. Sel. Top. Power Electron.*, vol. 7, no. 3, pp. 1475–1484, Sep. 2019, doi: 10.1109/JESTPE.2019.2912978.

[25] W. Huang, Z. Li, T. P. Chow, Y. Niizuma, T. Nomura, and S. Yoshida, "Enhancement-mode gan hybrid mos-hemts with ron,sp of 20 mΩ·cm<sup>2</sup>," in *2008 20th International Symposium on Power Semiconductor Devices and IC's*, May 2008, pp. 295–298, doi: 10.1109/ISPSD.2008.4538957.

[26] S. M. Myers, A. F. Wright, G. A. Petersen, W. R. Wampler, C. H. Seager, M. H. Crawford, and J. Han, "Diffusion, release, and uptake of hydrogen in magnesium-doped gallium nitride: Theory and experiment," *J. Appl. Phys.*, vol. 89, no. 6, pp. 3195–3202, Mar. 2001, doi: 10.1063/1.1347410.

[27] W. Li, K. Nomoto, K. Lee, S. M. Islam, Z. Hu, M. Zhu, X. Gao, J. Xie, M. Pilla, D. Jena, and H. G. Xing, "Activation of buried p-GaN in MOCVD-regrown vertical structures," *Appl. Phys. Lett.*, vol. 113, no. 6, p. 062105, Aug. 2018, doi: 10.1063/1.5041879.

[28] K. Fu, H. Fu, H. Liu, S. R. Alugubelli, T.-H. Yang, X. Huang, H. Chen, I. Baranowski, J. Montes, F. A. Ponce, and Y. Zhao, "Investigation of GaN-on-GaN vertical p-n diode with regrown p-GaN by metalorganic chemical vapor deposition," *Appl. Phys. Lett.*, vol. 113, no. 23, p. 233502, Dec. 2018, doi: 10.1063/1.5052479.

[29] M. Xiao, Z. Du, J. Xie, E. Beam, X. Yan, K. Cheng, H. Wang, Y. Cao, and Y. Zhang, "Lateral p-GaN/2DEG junction diodes by selective-area p-GaN trench-filling-regrowth in AlGaN/GaN," *Appl. Phys. Lett.*, vol. 116, no. 5, p. 053503, Feb. 2020, doi: 10.1063/1.5139906.

[30] M. Xiao, X. Yan, J. Xie, E. Beam, Y. Cao, H. Wang, and Y. Zhang, "Origin of leakage current in vertical GaN devices with nonplanar regrown p-GaN," *Appl. Phys. Lett.*, vol. 117, no. 18, p. 183502, Nov. 2020, doi: 10.1063/5.0021374.

[31] T. Narita, K. Tomita, S. Yamada, and T. Kachi, "Quantitative investigation of the lateral diffusion of hydrogen in p-type GaN layers having NPN structures," *Appl. Phys. Express*, vol. 12, no. 1, p. 011006, Jan. 2019, doi: 10.7567/1882-0786/aaf418.

[32] S. Yan, M. Feng, S. Fan, R. Zhou, Y. Tang, T. Jiang, J. Liu, Y. Zhou, Q. Sun, and H. Yang, "Activation of buried p-GaN through nanopipes in large-size GaN-based tunnel junction LEDs," *Nanotechnology*, vol. 32, no. 30, p. 30LT01, May 2021, doi: 10.1088/1361-6528/abf969.

[33] Y. Zhang, M. Sun, Z. Liu, D. Piedra, J. Hu, X. Gao, and T. Palacios, "Trench formation and corner rounding in vertical GaN power devices," *Appl. Phys. Lett.*, vol. 110, no. 19, p. 193506, May 2017, doi: 10.1063/1.4983558.

[34] W. Melitz, J. Shen, A. C. Kummel, and S. Lee, "Kelvin probe force microscopy and its application," *Surf. Sci. Rep.*, vol. 66, no. 1, pp. 1–27, Jan. 2011, doi: 10.1016/j.surfrep.2010.10.001.

[35] T. Nakamura, N. Ishida, K. Sagisaka, and Y. Koide, "Surface potential imaging and characterizations of a GaN p-n junction with Kelvin probe force microscopy," *AIP Adv.*, vol. 10, no. 8, p. 085010, Aug. 2020, doi: 10.1063/5.0007524.

[36] T.-H. Kim, K. Fu, C. Yang, Y. Zhao, and E. T. Yu, "Electronic structure of epitaxially grown and regrown GaN pn junctions characterized by scanning Kelvin probe and capacitance microscopy," *J. Appl. Phys.*, vol. 131, no. 1, p. 015704, Jan. 2022, doi: 10.1063/5.0071422.

[37] A. Stockman, E. Canato, A. Tajalli, M. Meneghini, G. Meneghesso, E. Zanoni, P. Moens, and B. Bakeroor, "On the origin of the leakage current in p-gate AlGaN/GaN HEMTs," in *2018 IEEE International*

*Reliability Physics Symposium (IRPS)*, Mar. 2018, p. 4B.5-1-4B.5-4, doi: 10.1109/IRPS.2018.8353582.

[38] Y. Zhang, M. Sun, H. Wong, Y. Lin, P. Srivastava, C. Hatem, M. Azize, D. Piedra, L. Yu, T. Sumitomo, N. A. de Braga, R. V. Mickevicius, and T. Palacios, "Origin and Control of OFF-State Leakage Current in GaN-on-Si Vertical Diodes," *IEEE Trans. Electron Devices*, vol. 62, no. 7, pp. 2155–2161, Jul. 2015, doi: 10.1109/TED.2015.2426711.

[39] A. Castiglia, J.-F. Carlin, and N. Grandjean, "Role of stable and metastable Mg–H complexes in p-type GaN for cw blue laser diodes," *Appl. Phys. Lett.*, vol. 98, no. 21, p. 213505, May 2011, doi: 10.1063/1.3593964.

[40] Y. Zhang, M. Sun, Z. Liu, D. Piedra, H.-S. Lee, F. Gao, T. Fujishima, and T. Palacios, "Electrothermal Simulation and Thermal Performance Study of GaN Vertical and Lateral Power Transistors," *IEEE Trans. Electron Devices*, vol. 60, no. 7, pp. 2224–2230, Jul. 2013, doi: 10.1109/TED.2013.2261072.

[41] J. A. Cooper and D. T. Morissette, "Performance Limits of Vertical Unipolar Power Devices in GaN and 4H-SiC," *IEEE Electron Device Lett.*, vol. 41, no. 6, pp. 892–895, Jun. 2020, doi: 10.1109/LED.2020.2987282.

[42] Z. H. Liu, G. I. Ng, S. Arulkumaran, Y. K. T. Maung, and H. Zhou, "Temperature-dependent forward gate current transport in atomic-layer-deposited Al<sub>2</sub>O<sub>3</sub>/AlGaN/GaN metal-insulator-semiconductor high electron mobility transistor," *Appl. Phys. Lett.*, vol. 98, no. 16, p. 163501, Apr. 2011, doi: 10.1063/1.3573794.

[43] K. Fu, H. Fu, X. Huang, T.-H. Yang, C.-Y. Cheng, P. R. Peri, H. Chen, J. Montes, C. Yang, J. Zhou, X. Deng, X. Qi, D. J. Smith, S. M. Goodnick, and Y. Zhao, "Reverse Leakage Analysis for As-Grown and Regrown Vertical GaN-on-GaN Schottky Barrier Diodes," *IEEE J. Electron Devices Soc.*, vol. 8, pp. 74–83, 2020, doi: 10.1109/JEDS.2020.2963902.

[44] J. Elsner, R. Jones, M. I. Heggie, P. K. Sitch, M. Haugk, Th. Frauenheim, S. Öberg, and P. R. Briddon, "Deep acceptors trapped at threading-edge dislocations in GaN," *Phys. Rev. B*, vol. 58, no. 19, pp. 12571–12574, Nov. 1998, doi: 10.1103/PhysRevB.58.12571.

[45] Y. Zhang, H. Y. Wong, M. Sun, S. Joglekar, L. Yu, N. A. Braga, R. V. Mickevicius, and T. Palacios, "Design space and origin of off-state leakage in GaN vertical power diodes," in *2015 IEEE International Electron Devices Meeting (IEDM)*, Dec. 2015, p. 35.1.1-35.1.4, doi: 10.1109/IEDM.2015.7409830.

[46] M. Xiao, X. Gao, T. Palacios, and Y. Zhang, "Leakage and breakdown mechanisms of GaN vertical power FinFETs," *Appl. Phys. Lett.*, vol. 114, no. 16, p. 163503, Apr. 2019, doi: 10.1063/1.5092433.