# Dynamic Gate Breakdown of p-Gate GaN HEMTs in Inductive Power Switching

Bixuan Wang, Student Member, IEEE, Ruizhe Zhang, Student Member, IEEE, Hengyu Wang, Quanbo He, Qihao Song, Student Member, IEEE, Qiang Li, Senior Member, IEEE, Florin Udrea, Member, IEEE, and Yuhao Zhang, Senior Member, IEEE

Abstract—We employ a new circuit method to characterize the gate dynamic breakdown voltage ( $BV_{dyn}$ ) of Schottky-type p-gate GaN HEMTs in power converters. Different from prior pulse I-V and DC stress tests, this method features a resonance-like gate ringing with the pulse width down to 20 ns and an inductive switching concurrently in the drain-source loop. At the increased pulse width, the gate  $BV_{\rm dyn}$  shows a decrease and then saturation at 21~22 V. Moreover, the gate  $BV_{\rm dyn}$  increases with temperature and is higher under the hard switching than that under the drainsource grounding condition. In the 400 V hard switching at 150 °C, the gate  $BV_{\rm dyn}$  reaches 27.5 V. Such impact of the drain switching locus and temperature on the gate  $BV_{dyn}$  is not seen in Si and SiC power transistors tested in the same setup. These results are explained by a physics model that accounts for the electrostatics in the p-GaN gate stack in hard switching and at high temperatures. This work unveils new physics critical to the gate robustness of pgate GaN HEMTs and manifest the necessity of the gate robustness evaluation in inductive switching conditions.<sup>1</sup>

Index Terms—GaN, HEMT, power electronics, hard switching, gate, breakdown voltage, overvoltage, ruggedness, reliability.

#### I. INTRODUCTION

Gallium nitride (GaN) high-electron-mobility transistors (HEMTs) enable power electronics at very high frequency. Schottky-type p-gate GaN HEMTs (SP-HEMTs) are recently adopted by many device vendors and foundries as a common device platform [1]–[3]. A critical issue in their driver design is to suppress the gate-voltage ( $V_G$ ) overshoot induced by the parasitic gate loop inductance or commutation crosstalk, as the margin between the typical drive voltage and the maximum allowable voltage of SP-HEMT can be as low as 1 V [4].

For SP-HEMT applications and protection circuit designs, in addition to the long-term gate lifetime, it is equally crucial to quantify the single-pulse gate overvoltage boundary, i.e., gate dynamic breakdown voltage  $(BV_{\rm dyn})$ , in switching conditions that best resemble practical power converters. This information is important to evaluate the transient gate bias limit, which is being added to some SP-HEMT's datasheet, and the gate robustness against the single-event overvoltage stress. For example, resonant gate drivers comprise an inductor connected in series with the device gate [5], which could induce considerable surge energy and overvoltage to be withstood by the device gate under fault events.

Over the last several years, many groups used the DC tests with a constant-voltage stress or step-stress stress to study the

<sup>1</sup>This work is supported in part by the Power Management Consortium of the Center for Power Electronics Systems at Virginia Tech and in part by the National Science Foundation under the Grants ECCS-2045001 and ECCS-2036740. B. Wang, R. Zhang, Q. Song, Q. Li, and Y. Zhang are with the Center of Power Electronics Systems, Virginia Polytechnic Institute and State University, Blacksburg, VA 24060 USA (e-mail: yhzhang@vt.edu).

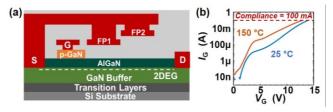

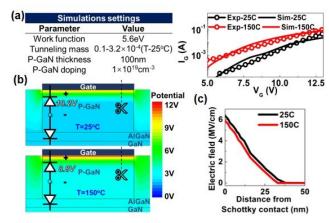

Fig. 1. (a) Schematic of the DUT. (b) Static  $I_{G^-}V_{G^-}T$  characteristics measured with a 0.1 A compliance on Keysight B1505 Power Device Analyzer.

gate breakdown of SP-HEMTs [6]–[13]. Recently, the square-wave pulse I-V test was used to study the gate breakdown and reliability [14]–[17]. The pulse I-V test identified the switching instead of DC phase to account for the gate overvoltage failure [14], [16], suggesting the need for switching tests.

Despite the suitability for physics studies, DC and pulse I-V tests do not resemble the device operation in power converters: 1) the  $V_{\rm G}$  overshoot in converters is usually resonance-like with a waveform different from square-wave and a dv/dt higher than the pulse I-V test [18], [19]; 2) in inductive switching, e.g., hard switching (HSW), sharp changes in drain-source voltage ( $V_{\rm DS}$ ) and current ( $I_{\rm DS}$ ) occur concurrently with the  $V_{\rm G}$  overshoot, while most prior gate breakdown studies were performed under the drain-source grounding (DSG) condition. Recently, a pulse I-V test with the switching  $V_{\rm DS}$  produced by a resistive load was used for gate study [17]. This condition still differs from the usual converters with inductive loads.

While the drain  $BV_{\rm dyn}$  was recently revealed for GaN HEMTs [20], [21], the gate  $BV_{\rm dyn}$  under inductive switching has not been reported before. This work addresses this gap by developing a new circuit to mimic the  $V_{\rm G}$  overshoot in inductive converters, allowing for evaluating the gate  $BV_{\rm dyn}$  under the DSG and HSW conditions. The gate  $BV_{\rm dyn}$  of GaN SP-HEMTs is found to be higher under the HSW than that under the DSG and increase with temperature; these dependences are not observed in Si and SiC FETs tested under the same circuit.

### II. DUT AND CIRCUIT DESIGN

The device under test (DUT) is a commercial 650V/30A GaN SP-HEMT [22] (Fig. 1(a)). Over 70 devices are tested, showing good statistical significance. Fig. 1(b) shows the static  $I_G$ - $V_G$  characteristics with 0.1 A compliance at 25 and 150 °C. DUT shows no failure or degradation after characterization.

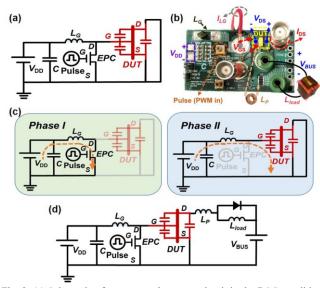

Fig. 2 shows the design, working principles, and prototype of our circuit. The gate overvoltage study is performed in the DUT

H. Wang, Q. He, and F. Udrea are with the Department of Engineering, University of Cambridge, Cambridge, UK (email: ful0000@cam.ac.uk).

Fig. 2. (a) Schematic of gate overvoltage test circuit in the DSG condition. (b) Photo and (c) working principle of the test circuit. (d) Test schematic under hard-switching condition with the inductive load.

turn-on process. The inductor  $L_{\rm G}$  mimics the gate loop parasitics. A low-voltage GaN HEMT (EPC2214 [23]) is used to create  $V_{\rm G}$  overshoot. In *phase I*, the EPC device is turned on, allowing  $L_{\rm G}$  to be charged by  $V_{\rm DD}$ . In *phase II*, the EPC device is turned off, and the energy stored in  $L_{\rm G}$  creates an *RLC*-resonance-like  $V_{\rm G}$  overshoot at the DUT gate (R and C are the DUT's gate resistance and capacitance). This design is similar to the unclamped inductive switching used to create  $V_{\rm DS}$  overshoot and study the drain  $BV_{\rm dyn}$  [20], [21], [24].

The  $V_{\rm DD}$  (0.5 V) is lower than the DUT's threshold voltage to prevent the false turn-on. Several  $L_{\rm G}$  with inductances from 50 nH to 300  $\mu$ H are used to tune the dv/dt and pulse width of the  $V_{\rm G}$  overshoot. For each  $L_{\rm G}$ , the on-time of the EPC device is used to modulate the peak  $V_{\rm G}$  in the overshoot ( $V_{\rm G(PK)}$ ).

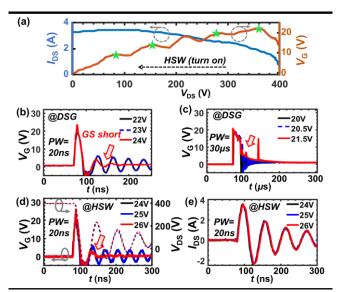

The circuit tests are first performed under the DSG condition for a direct comparison with the prior static/pulse I-V results (Fig. 2(a)). Then the gate  $BV_{\rm dyn}$  is measured under the HSW. As shown in Fig. 2(d), the loop comprises a load inductor (24 mH), a free-wheeling diode [25], a 400 V bus voltage, and a capacitor bank. Another inductor ( $L_{\rm P}=1~\mu{\rm H}$ ) is added to mimic the main loop parasitics, suppress the peak  $I_{\rm DS}$ , and avoid the thermal runaway. Fig. 3(a) shows the experimental  $I_{\rm DS}$ - $V_{\rm DS}$  and  $V_{\rm G}$ - $V_{\rm DS}$  switching locus, revealing a concurrence of high  $V_{\rm G}$ ,  $V_{\rm DS}$  and  $I_{\rm DS}$ , thus verifying the HSW condition.

The DUT temperature is controlled by a power resistor attached to its case and calibrated by a thermal camera. Based on the switching loss and the datasheet's transient thermal impedance, the junction temperature is < 1 °C higher than the case temperature in the single-pulse switching test.

## III. CIRCUIT TEST RESULTS

Gate  $BV_{\rm dyn}$  tests are performed with a 0.5 V step increase in  $V_{\rm G(PK)}$ . Under the DSG, the failure and two survival waveforms of  $V_{\rm G}$  are shown in Fig. 3(b) and (c) for two pulse widths (20 ns and 30 µs). In the 20 ns pulse, the  $V_{\rm G}$  overshoot exhibits a dv/dt over 2 V/ns, which is slightly higher than the typical dv/dt (1~2

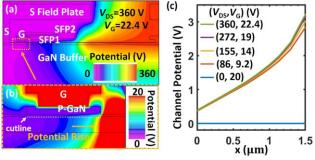

Fig. 3. (a) Switching locus in the gate overvoltage tests during hard turn on. The green symbols correspond to simulation conditions in Fig. 6. The failure and two survival  $V_{\rm G}$  waveforms under the DSG at pulse width (PW) of (b) 20 ns and (c) 30  $\mu$ s. The failure and two survival waveforms of (d)  $V_{\rm G}$  (solid lines),  $V_{\rm DS}$  (dashed line), and (e)  $I_{\rm DS}$  under the HSW.

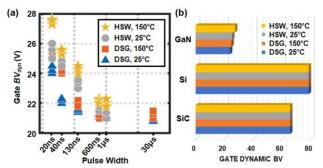

Fig. 4. (a) Gate  $BV_{\rm dyn}$  of GaN SP-HEMT as a function of pulse width under the DSG and HSW and at 25 and 150 °C. Three devices are tested for each condition. (b) Gate  $BV_{\rm dyn}$  of Si IGBT, SiC MOSFET and GaN SP-HEMT under the DSG and HSW and at 25 and 150 °C, all at a pulse width of 20 ns. Multiple Si and SiC devices are tested, showing nearly no variation.

V/ns) in high-frequency GaN converters. In the failure waveform, the  $V_G$  ringing damps fast after  $V_{G(PK)}$ , suggesting a gate-source (G-S) short. Post-test characterizations reveal a destructive failure with the G-S resistance ranging from 0 to 1 M $\Omega$ . Devices after all the tests with  $V_{G(PK)} < BV_{dyn}$  show no noticeable degradation. The gate  $BV_{dyn}$  is over 20 V and higher than those reported in DC and pulse I-V tests [14], suggesting a higher  $V_G$  headroom in ns~ $\mu$ s switching.

Fig. 3(d) and (e) show the failure and survival waveforms of  $V_{\rm G}$ ,  $V_{\rm DS}$  and  $I_{\rm DS}$  under the HSW with 20 ns pulse width. The destructive failure shows a similar G-S short, while no shorting is present between source and drain. These failure signatures are confirmed by static I-V of the failed devices.

Fig. 4(a) shows the gate  $BV_{\rm dyn}$  of GaN SP-HEMTs as a function of pulse width (ns~ $\mu$ s range) under the DSG and HSW at 25 and 150 °C. At least 3 DUTs are measured in each condition, exhibiting a small  $BV_{\rm dyn}$  variation below 0.3 V.

Under the DSG at 25 °C,  $BV_{\rm dyn}$  decreases with the pulse width from 24 V to 21 V and then saturates; at 150 °C,  $BV_{\rm dyn}$  is 1~1.5 V higher than that at 25 °C in short pulses and also saturates to

Fig. 5. (a) Key simulation parameters in the p-GaN gate simulation, and calibration of the simulated  $I_{\rm G}$ - $V_{\rm G}$  curve. (b) Simulated potential contours in the gate stack at  $V_{\rm G}$ =12V at 25 and 150 °C. (c) Extracted electric field distribution along the cutline shown in (b).

Fig. 6. Simulated potential contour in the (a) device and (b) gate region at the peak  $V_{\rm G}$  along the HSW locus. (c) Simulated potential in the channel below gate at four bias conditions along the HSW locus and under the DSG.

21 V. Under the HSW, the gate  $BV_{\rm dyn}$  is 2~2.5 V higher than that under the DSG. The highest  $BV_{\rm dyn}$  (27.5 V) is observed under the HSW with a 20 ns pulse at 150 °C.

The gate  $BV_{\rm dyn}$  of 650 V Si IGBT [26] and SiC MOSFET [27] are also measured using the same circuit setup, as shown in Fig. 4(b). The gate  $BV_{\rm dyn}$  of both devices show no dependence on temperature or the drain switching scheme, suggesting minimal impact of the drain stimuli on their MOS gate breakdown.

## IV. PHYSICAL ANALYSIS AND SIMULATION

The stronger impacts of temperature and switching locus on the gate  $BV_{\rm dyn}$  in GaN SP-HEMT originate from the non-insulating nature of the p-GaN gate as compared to the MOS gate. Its positive temperature coefficient ( $\eta_T$ ) and saturation in long pulses cannot be explained by the thermal failure or the percolation-induced breakdown, which has a negative  $\eta_T$  [7], [8]. We expand a model proposed in [14] to explain these dependences and give simulation validations. The simulation model is based on [28] with the DUT's structure on [24].

The SP-HEMT gate at high  $V_{\rm G}$  comprises a reverse-biased pGaN/gate Schottky junction in series with a forward-biased p-GaN/AlGaN/GaN pin junction. At high  $V_{\rm G}$ , the pin junction injects electrons from the 2DEG into p-GaN, which then diffuse to the depleted p-GaN region, get accelerated by high electric field, and bombard the Schottky interface. This may degrade the local Schottky contact and turn it into Ohmic-like, leading to the crowded electric field and punch-through [14].

The gate  $BV_{\rm dyn}$ 's saturation with the pulse width implies a threshold in the electric field or electron bombardment energy for the Schottky degradation. Such threshold is not reached at  $V_{\rm G} < 21$  V. Above this threshold, the local Schottky degradation may progressively accumulate until the destructive gate failure occurs. This progressive process can be accelerated by a higher electron bombardment energy, which explains the higher gate  $BV_{\rm dyn}$  under shorter pulses.

The temperature and switching locus impact the peak electric field at the p-GaN Schottky junction at a certain  $V_G$ , thus changing the gate  $BV_{\rm dyn}$ . To explain the positive  $\eta_T$ , TCAD simulation with the models in [29] is calibrated with  $I_G$ - $V_G$  data (Fig. 5(a)). In the p-GaN gate, the reverse Schottky current  $(I_R^{Sch})$  sets the forward pin current  $(I_F^{pn})$ . Simulation considers the  $I_R^{Sch}$  at high  $V_G$  to be induced by carrier tunneling across the Schottky barrier; the tunneling is thermally assisted [10] possibly due to dislocations. As shown in Fig. 5(b) and (c), at a certain  $V_G$ , as temperature rises, higher  $I_R^{Sch}$  and  $I_F^{pn}$  induce larger voltage drops in the non-depleted p-GaN and pin junction, decreasing the Schottky voltage drop and the junction electric field. The reduced field suppresses the electron bombardment, leading to a higher gate  $BV_{\rm dyn}$ .

Some additional mechanisms can also contribute to the gate  $BV_{\rm dyn}$ 's positive  $\eta_T$ , including the avalanche in the depleted p-GaN [14] and the hot electron transport in the non-depleted p-GaN. As the mean free path of hot electrons is small (~14 nm [30], [31]), only a portion of them can reach the depleted region. At higher temperatures, the mean free path reduces; a smaller number of hot electrons is accelerated in the depletion region and bombard the Schottky contact.

In the HSW, large  $V_{\rm DS}$  and  $I_{\rm DS}$  occur during the  $V_{\rm G}$  overshoot. The high  $V_{\rm DS}$  drives the DUT into saturation, expand the pinch-off region in the channel, and raise the potential along the channel. This is strengthened by channel voltage drop due to high  $I_{\rm DS}$ . Fig. 6(a) and (b) show the simulated potential contour at  $V_{\rm DS} = 360$  V and  $V_{\rm G} = 22.4$  V, the peak  $V_{\rm G}$  condition on the switching locus [see Fig. 3(a)]. Fig. 6(c) shows the simulated channel potential at four bias conditions along the switching locus and under the DSG condition. The channel potential increase under the HSW condition reduces the actual voltage drop across the gate stack and makes the pin junction reverse-biased at the drain end of the gate, suppressing the electron injection into p-GaN and increasing the gate  $BV_{\rm dyn}$ .

# V. SUMMARY

This work characterizes the gate  $BV_{\rm dyn}$  of GaN SP-HEMTs using the converter-like  $V_{\rm G}$  overshoot. This new circuit method allows for the study of gate robustness in inductive switching that is not accessible via DC and pulse I-V tests. The gate  $BV_{\rm dyn}$  of GaN SP-HEMTs is found to be higher in hard switching and at higher temperatures. Such dependences are not observed in Si IGBTs and SiC MOSFETs. This distinction originates from the non-insulating gate stack in GaN SP-HEMTs, which leads to an interplay between the gate and channel electrostatics. These results provide direct references for GaN converter applications and reveal new physical insights for the evaluation and qualification of GaN HEMT gate ruggedness.

#### REFERENCES

- [1] K. J. Chen, O. Häberlen, A. Lidow, C. 1 Tsai, T. Ueda, Y. Uemoto, and Y. Wu, "GaN-on-Si Power Technology: Devices and Applications," *IEEE Trans. Electron Devices*, vol. 64, no. 3, pp. 779–795, Mar. 2017, doi: 10.1109/TED.2017.2657579.

- [2] Y. Zhang, F. Udrea, and H. Wang, "Multidimensional device architectures for efficient power electronics," *Nat. Electron.*, vol. 5, no. 11, pp. 723–734, Nov. 2022, doi: 10.1038/s41928-022-00860-5.

- [3] K. Hoo Teo, Y. Zhang, N. Chowdhury, S. Rakheja, R. Ma, Q. Xie, E. Yagyu, K. Yamanaka, K. Li, and T. Palacios, "Emerging GaN technologies for power, RF, digital, and quantum computing applications: Recent advances and prospects," *J. Appl. Phys.*, vol. 130, no. 16, p. 160902, Oct. 2021, doi: 10.1063/5.0061555.

- [4] S. K. Murray, W. L. Jiang, M. S. Zaman, H. De Vleeschouwer, P. Moens, J. Roig, and O. Trescases, "Transient Overvoltage Detection Technique for GaN HEMTs Integrated in a 200-V GaN-on-SOI Process," in 2022 IEEE Applied Power Electronics Conference and Exposition (APEC), Mar. 2022, pp. 1400–1405, doi: 10.1109/APEC43599.2022.9773399.

- [5] B. Sun, Z. Zhang, and M. A. E. Andersen, "A Comparison Review of the Resonant Gate Driver in the Silicon MOSFET and the GaN Transistor Application," *IEEE Trans. Ind. Appl.*, vol. 55, no. 6, pp. 7776–7786, Nov. 2019, doi: 10.1109/TIA.2019.2914193.

- [6] T.-L. Wu, D. Marcon, S. You, N. Posthuma, B. Bakeroot, S. Stoffels, M. Van Hove, G. Groeseneken, and S. Decoutere, "Forward Bias Gate Breakdown Mechanism in Enhancement-Mode p-GaN Gate AlGaN/GaN High-Electron Mobility Transistors," *IEEE Electron Device Lett.*, vol. 36, no. 10, pp. 1001–1003, Oct. 2015, doi: 10.1109/LED.2015.2465137.

- [7] M. Ťapajna, O. Hilt, E. Bahat-Treidel, J. Würfl, and J. Kuzmík, "Gate Reliability Investigation in Normally-Off p-Type-GaN Cap/AlGaN/GaN HEMTs Under Forward Bias Stress," *IEEE Electron Device Lett.*, vol. 37, no. 4, pp. 385–388, Apr. 2016, doi: 10.1109/LED.2016.2535133.

- [8] I. Rossetto, M. Meneghini, O. Hilt, E. Bahat-Treidel, C. De Santi, S. Dalcanale, J. Wuerfl, E. Zanoni, and G. Meneghesso, "Time-Dependent Failure of GaN-on-Si Power HEMTs With p-GaN Gate," *IEEE Trans. Electron Devices*, vol. 63, no. 6, pp. 2334–2339, Jun. 2016, doi: 10.1109/TED.2016.2553721.

- [9] S. Stoffels, B. Bakeroot, T. L. Wu, D. Marcon, N. E. Posthuma, S. Decoutere, A. N. Tallarico, and C. Fiegna, "Failure mode for p-GaN gates under forward gate stress with varying Mg concentration," in 2017 IEEE International Reliability Physics Symposium (IRPS), Monterey, CA, USA, Apr. 2017, pp. 4B-4.1-4B-4.9, doi: 10.1109/IRPS.2017.7936310.

- [10] A. Stockman, F. Masin, M. Meneghini, E. Zanoni, G. Meneghesso, B. Bakeroot, and P. Moens, "Gate Conduction Mechanisms and Lifetime Modeling of p-Gate AlGaN/GaN High-Electron-Mobility Transistors," *IEEE Trans. Electron Devices*, vol. 65, no. 12, pp. 5365–5372, Dec. 2018, doi: 10.1109/TED.2018.2877262.

- [11] A. N. Tallarico, S. Stoffels, P. Magnone, N. Posthuma, E. Sangiorgi, S. Decoutere, and C. Fiegna, "Investigation of the p-GaN Gate Breakdown in Forward-Biased GaN-Based Power HEMTs," *IEEE Electron Device Lett.*, vol. 38, no. 1, pp. 99–102, Jan. 2017, doi: 10.1109/LED.2016.2631640.

- [12] L. Zhang, Z. Zheng, S. Yang, W. Song, J. He, and K. J. Chen, "p-GaN Gate HEMT With Surface Reinforcement for Enhanced Gate Reliability," *IEEE Electron Device Lett.*, vol. 42, no. 1, pp. 22–25, Jan. 2021, doi: 10.1109/LED.2020.3037186.

- [13] M. Millesimo, C. Fiegna, N. Posthuma, M. Borga, B. Bakeroot, S. Decoutere, and A. N. Tallarico, "High-Temperature Time-Dependent Gate Breakdown of p-GaN HEMTs," *IEEE Trans. Electron Devices*, vol. 68, no. 11, pp. 5701–5706, Nov. 2021, doi: 10.1109/TED.2021.3111144.

- [14] J. He, J. Wei, S. Yang, Y. Wang, K. Zhong, and K. J. Chen, "Frequency-and Temperature-Dependent Gate Reliability of Schottky-Type p-GaN Gate HEMTs," *IEEE Trans. Electron Devices*, vol. 66, no. 8, pp. 3453–3458, Aug. 2019, doi: 10.1109/TED.2019.2924675.

- [15] J. He, J. Wei, Y. Li, Z. Zheng, S. Yang, B. Huang, and K. J. Chen, "Characterization and analysis of low-temperature time-to-failure behavior in forward-biased Schottky-type p -GaN gate HEMTs," Appl. Phys. Lett., vol. 116, no. 22, p. 223502, Jun. 2020, doi: 10.1063/5.0007763.

- [16] M. Millesimo, B. Bakeroot, M. Borga, N. Posthuma, S. Decoutere, E. Sangiorgi, C. Fiegna, and A. N. Tallarico, "Gate Reliability of p-GaN Power HEMTs Under Pulsed Stress Condition," in 2022 IEEE International Reliability Physics Symposium (IRPS), Mar. 2022, p. 10B.2-1-10B.2-6, doi: 10.1109/IRPS48227.2022.9764592.

- [17] Y. Cheng, J. He, H. Xu, K. Zhong, Z. Zheng, J. Sun, and K. J. Chen, "Gate Reliability of Schottky-Type p-GaN Gate HEMTs Under AC Positive Gate Bias Stress With a Switching Drain Bias," *IEEE Electron Device Lett.*, vol. 43, no. 9, pp. 1404–1407, Sep. 2022, doi: 10.1109/LED.2022.3188555.

- [18] J. P. Kozak, A. Barchowsky, M. R. Hontz, N. B. Koganti, W. E. Stanchina, G. F. Reed, Z.-H. Mao, and R. Khanna, "An Analytical Model for Predicting Turn-ON Overshoot in Normally-OFF GaN HEMTs," *IEEE J. Emerg. Sel. Top. Power Electron.*, vol. 8, no. 1, pp. 99–110, Mar. 2020, doi: 10.1109/JESTPE.2019.2947152.

- [19] W. J. Zhang, J. Yu, W. T. Cui, Y. Leng, J. Liang, Y.-T. Hsieh, H.-H. Tsai, Y.-Z. Juang, W.-K. Yeh, and W. T. Ng, "A Smart Gate Driver IC for GaN Power HEMTs With Dynamic Ringing Suppression," *IEEE Trans. Power Electron.*, vol. 36, no. 12, pp. 14119–14132, Dec. 2021, doi: 10.1109/TPEL.2021.3089679.

- [20] R. Zhang, J. P. Kozak, Q. Song, M. Xiao, J. Liu, and Y. Zhang, "Dynamic Breakdown Voltage of GaN Power HEMTs," in 2020 IEEE International Electron Devices Meeting (IEDM), p. 23.3.1-23.3.4.

- [21] J. P. Kozak, R. Zhang, Q. Song, J. Liu, W. Saito, and Y. Zhang, "True Breakdown Voltage and Overvoltage Margin of GaN Power HEMTs in Hard Switching," *IEEE Electron Device Lett.*, vol. 42, no. 4, pp. 505– 508, Apr. 2021, doi: 10.1109/LED.2021.3063360.

- [22] "GS66508T," GaN Systems. https://gansystems.com/gantransistors/gs66508t/ (accessed Sep. 06, 2022).

- [23] "EPC2214: Automotive 80 V, 47 A Enhancement-Mode GaN Power Transistor." https://epc-co.com/epc/Products/eGaNFETsandICs/EPC2214.aspx (accessed Sep. 06, 2022).

- [24] R. Zhang, J. P. Kozak, M. Xiao, J. Liu, and Y. Zhang, "Surge-Energy and Overvoltage Ruggedness of P-Gate GaN HEMTs," *IEEE Trans. Power Electron.*, vol. 35, no. 12, pp. 13409–13419, Dec. 2020, doi: 10.1109/TPEL.2020.2993982.

- [25] "ES1JFL: Surface Mount Superfast Rectifier." https://www.onsemi.com/products/discrete-power-modules/rectifiers/es1jfl (accessed Sep. 06, 2022).

- [26] "rgt8ns65d-e.pdf." Accessed: Sep. 11, 2022. [Online]. Available: https://fscdn.rohm.com/en/products/databook/datasheet/discrete/igbt/r gt8ns65d-e.pdf.

- [27] "C3M0120065D.pdf." Accessed: Sep. 11, 2022. [Online]. Available: https://assets.wolfspeed.com/uploads/2021/05/C3M0120065D.pdf.

- [28] Y. Zhang, M. Sun, Z. Liu, D. Piedra, H.-S. Lee, F. Gao, T. Fujishima, and T. Palacios, "Electrothermal Simulation and Thermal Performance Study of GaN Vertical and Lateral Power Transistors," *IEEE Trans. Electron Devices*, vol. 60, no. 7, pp. 2224–2230, Jul. 2013, doi: 10.1109/TED.2013.2261072.

- [29] L. Efthymiou, G. Longobardi, G. Camuso, T. Chien, M. Chen, and F. Udrea, "On the physical operation and optimization of the p-GaN gate in normally-off GaN HEMT devices," *Appl. Phys. Lett.*, vol. 110, no. 12, p. 123502, Mar. 2017, doi: 10.1063/1.4978690.

- [30] D. J. Suntrup, G. Gupta, H. Li, S. Keller, and U. K. Mishra, "Measurement of the hot electron mean free path and the momentum relaxation rate in GaN," *Appl. Phys. Lett.*, vol. 105, no. 26, p. 263506, Dec. 2014, doi: 10.1063/1.4905367.

- [31] A. Minetto, B. Deutschmann, N. Modolo, A. Nardo, M. Meneghini, E. Zanoni, L. Sayadi, G. Prechtl, S. Sicre, and O. Häberlen, "Hot-Electron Effects in AlGaN/GaN HEMTs Under Semi-ON DC Stress," *IEEE Trans. Electron Devices*, vol. 67, no. 11, pp. 4602–4605, Nov. 2020, doi: 10.1109/TED.2020.3025983.