#### **PROGRESS REVIEW • OPEN ACCESS**

# Recent progress of $Ga_2O_3$ power technology: large-area devices, packaging and applications

To cite this article: Yuan Qin et al 2023 Jpn. J. Appl. Phys. 62 SF0801

View the article online for updates and enhancements.

## You may also like

- <u>Third quadrant overvoltage ruggedness of p-gate GaN HEMTs</u>

Lifeng Yuan, Feng Zhou, Yulei Jin et al.

- (Invited) Ruggedness of SiC and GaN Power Transistors in Switching Based Tests

Ruizhe Zhang, Joseph Kozak, Jingcun Liu

- Analyzing Surface Ruggedness Inside and Outside of Ice Stability Zones at the Lunar Poles

Ariel N. Deutsch, Jennifer L. Heldmann, Anthony Colaprete et al.

https://doi.org/10.35848/1347-4065/acb3d3

# Recent progress of Ga<sub>2</sub>O<sub>3</sub> power technology: large-area devices, packaging and applications

Yuan Qin<sup>1†</sup>, Zhengpeng Wang<sup>2†</sup>, Kohei Sasaki<sup>3</sup>, Jiandong Ye<sup>2\*</sup>, and Yuhao Zhang<sup>1\*</sup>

<sup>1</sup>Center for Power Electronics Systems, Virginia Polytechnic Institute and State University, Blacksburg, 24060, VA, United States of America

Received December 21, 2022; revised January 11, 2023; accepted January 17, 2023; published online February 9, 2023

Benefitted from progress on the large-diameter  $Ga_2O_3$  wafers and  $Ga_2O_3$  processing techniques, the  $Ga_2O_3$  power device technology has witnessed fast advances toward power electronics applications. Recently, reports on large-area (ampere-class)  $Ga_2O_3$  power devices have emerged globally, and the scope of these works have gone well beyond the bare-die device demonstration into the device packaging, circuit testing, and ruggedness evaluation. These results have placed  $Ga_2O_3$  in a unique position as the only ultra-wide bandgap semiconductor reaching these indispensable milestones for power device development. This paper presents a timely review on the state-of-the-art of the ampere-class  $Ga_2O_3$  power devices (current up to >100 A and voltage up to >2000 V), including their static electrical performance, switching characteristics, packaging and thermal management, and the overcurrent/overvoltage ruggedness and reliability. Exciting research opportunities and critical technological gaps are also discussed. © 2023 The Author(s). Published on behalf of The Japan Society of Applied Physics by IOP Publishing Ltd

#### 1. Introduction

Power semiconductor devices are key to delivering high-efficiency energy conversion in power electronics applications such as electric vehicles, data centers, electric grids, renewable energy processing, and consumer electronics. The market size of power semiconductor devices has reached \$40 billion and is fast growing. The advances in power devices hinge on innovations in semiconductor materials and device architectures. From the material perspective, power devices based on silicon (Si), silicon carbide (SiC), and gallium nitride (GaN) have been commercialized. Several emerging materials with bandgaps larger than SiC and GaN, i.e. ultra-wide bandgap (UWBG) semiconductors, are being extensively researched, including gallium oxide (Ga<sub>2</sub>O<sub>3</sub>), aluminum nitride, aluminum gallium nitride, diamond, and boron nitride.

Among these UWBG materials, Ga<sub>2</sub>O<sub>3</sub> has shown particular promise as the Ga<sub>2</sub>O<sub>3</sub> device technology has recently achieved several critical milestones for power applications. Power devices are used as solid-state switches to modulate considerable power flow in applications. Despite the wide range of specifications, industrial power devices are all packaged; they usually can conduct at least several amperes of current in the on-state, block at least tens or hundreds of volts in the off-state, and switch at a frequency of at least tens of kilohertz. During these operations, the junction temperature has to maintain below a safety limit (e.g. 150 °C-175 °C). In addition, power devices are required to possess good robustness against fault events (e.g. overvoltage, overcurrent, and surge energy<sup>5)</sup>). These requirements define critical development milestones for any power device technology, i.e. the demonstration of (1) ampere-class devices with decent breakdown voltage  $(V_{\rm br})$ , (2) packaging and thermal management, (3) switching operation in converter applications, and (4) reliability and robustness.

Ga<sub>2</sub>O<sub>3</sub> is featured by a high critical electric-field (projected to be up to 8 MV cm $^{-1}$ ), controllable n-type doping with shallow dopants ( $10^{14} \sim 10^{20}\,\mathrm{cm}^{-3}$ ), and the availability of large-diameter wafers by the melt growth. 6-10) Low-cost beta-phase gallium oxide (β-Ga<sub>2</sub>O<sub>3</sub>) wafers have recently reached the 4-inch commercial milestone and are on track for the 6-inch wafer scale production by 2027. 11) This has paved the road for developing ampere-class devices. Since the first report of Ga<sub>2</sub>O<sub>3</sub> transistors by Higashiwaki et al. in 2012-2013, 12,13) Ga<sub>2</sub>O<sub>3</sub> power devices have witnessed fast progress not only in the innovation of device architectures but also in the scaling of power levels. Recently, large-area  $Ga_2O_3$  power devices with a current of up to 135 A<sup>14)</sup> or  $V_{br}$ of up to over 2000 V<sup>15)</sup> have been demonstrated. Beyond the die-level, packaging has been applied to large-area Ga<sub>2</sub>O<sub>3</sub> devices and enabled a junction-to-case thermal resistance down to 0.5 °C W<sup>-1</sup>. 16) Excellent switching characteristics such as fast switching speed<sup>17,18)</sup> and minimal reverse recovery<sup>19)</sup> have been achieved in power converters. Impressive surge-current<sup>20)</sup> and overvoltage ruggedness<sup>15)</sup> have been reported in large-area Ga<sub>2</sub>O<sub>3</sub> devices.

To the best of our knowledge, Ga<sub>2</sub>O<sub>3</sub> is the only UWBG material that has made the above critical milestones for power applications. This suggests that the commercialization and application of Ga<sub>2</sub>O<sub>3</sub> power devices are within reach. This prospect is well supported by the development of a reference power device technology slightly ahead of Ga<sub>2</sub>O<sub>3</sub>, the vertical GaN technology. Its development shows a similar trajectory from small-area devices to large-area diodes<sup>21,22)</sup> and transistors<sup>23–28)</sup> fabricated on large-diameter wafers. After a further breakthrough in avalanche<sup>29–32)</sup> and short-circuit robustness,<sup>33–35)</sup> vertical GaN devices rapidly evolve into industrial manufacturing and start to be deployed in various power applications.<sup>36)</sup>

This article presents a timely review of the recent progress on large-area Ga<sub>2</sub>O<sub>3</sub> power devices, with the scope covering

<sup>&</sup>lt;sup>2</sup>School of Electronic Science and Engineering, Nanjing University, 210008, Nanjing, People's Republic of China

<sup>&</sup>lt;sup>3</sup>Novel Crystal Technology, Inc., Sayama, Saitama, 350-1528, Japan

<sup>\*</sup>E-mail: yejd@nju.edu.cn; yhzhang@vt.edu

<sup>&</sup>lt;sup>†</sup>Yuan Qin and Zhengpeng Wang contributed equally to this work.

their electrical performance, packaging and thermal management, converter operations, as well as robustness. This review also assists in identifying the gaps and immediate research needs. To date, despite several review papers on  $Ga_2O_3$  devices, <sup>7,37)</sup> such a review on the application prospects is lacking for  $Ga_2O_3$  power devices. The literature is vast, and space is limited. For a tight focus, only ampereclass  $Ga_2O_3$  power devices with a conduction current over 1 A are discussed in this paper.

This article is organized as follows. Section 2 discusses the static performance of large-area  $Ga_2O_3$  devices. Section 3 presents their packaging and thermal management. Sections 4 and 5 discuss their switching characteristics in power converters and circuit-level robustness, respectively. Section 6 identifies the immediate research needs and concludes the paper.

#### 2. Electrical performance

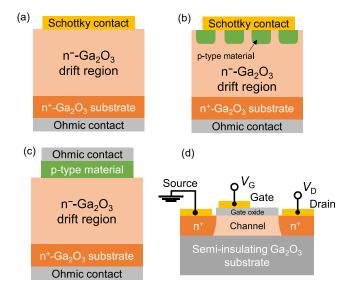

Currently, the reported ampere-class  $Ga_2O_3$  rectifiers all deploy the vertical architecture with various junction structures including the Schottky barrier diodes (SBD), junction barrier Schottky (JBS) diodes, and p-n heterojunction diodes (HJD). As compared to the conventional p-n diode, the HJD relies on the p-n junction formed by n-type  $Ga_2O_3$  and a distinct p-type material. The progress of these vertical  $Ga_2O_3$  rectifiers is fast, and various edge termination designs have been reported to achieve high  $V_{\rm br}$ . For transistors, the only ampere-class  $Ga_2O_3$  power transistor reported in the literature is the lateral  $Ga_2O_3$  MOSFET with a saturation current over 2.5 A and  $V_{\rm br}$  over  $400~\rm V.^{17,18}$  Schematics of the  $Ga_2O_3$  vertical SBD, JBS diode and HJD, as well as lateral MOSFET, are shown in Fig. 1.

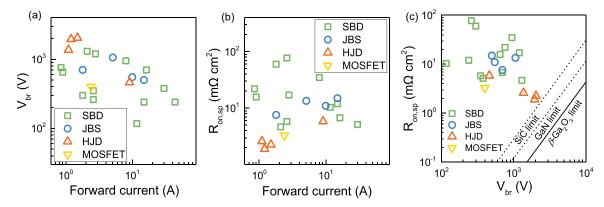

Figures 2(a)–2(c) benchmark the forward current versus  $V_{\rm br}$ , the forward current versus the differential specific onresistance ( $R_{\rm on,sp}$ ), and the  $R_{\rm on,sp}$  versus  $V_{\rm br}$  of these amperclass  ${\rm Ga_2O_3}$  power rectifiers and transistors.  $^{14,15,17,19,20,38-49)}$  A more complete set of performance parameters of the representative devices are summarized in Table I. For power diodes, the forward current is extracted at a forward voltage ( $V_{\rm F}$ ) equal to 1.5 V higher than the turn-on voltage ( $V_{\rm on}$ );

**Fig. 1.** (Color online) The schematic diagram of Ga<sub>2</sub>O<sub>3</sub>-based vertical (a) SBD, (b) JBS diode, (c) HJD, and (d) lateral MOSFET device.

$R_{

m on,sp}$  is the differential resistance after the diode is fully turned on. It is observed that both  $V_{

m br}$  and  $R_{

m on,sp}$  show a decreasing trend as the forward current increases. This suggests that the non-uniformity in material properties and fabrication process, as well as a considerable defect density, are still the dominant performance limiting factors of  $V_{

m br}$  in large-area  $Ga_2O_3$  devices. On the other hand, the smaller  $R_{

m on,sp}$  achieved at high current levels is a positive sign that implies the superior conduction capability in large-area devices.

For the trade-off between the differential  $R_{\rm on,sp}$  and  $V_{\rm br}$  in  ${\rm Ga_2O_3}$  unipolar rectifiers, the  ${\rm Ga_2O_3}$  HJDs generally outperform the SBD counterparts, with some devices approaching the unipolar limit of SiC devices. This superior trade-off between the differential  $R_{\rm on,sp}$  and  $V_{\rm br}$  does not necessarily lead to a superior trade-off between the conduction and switching loss, as the turn-on voltage of the HJD devices (2–2.5 V) is usually 1–1.5 V larger than that of SBDs and JBS diodes. Show the inferior  $V_{\rm br}$  with nearly no large-area devices exceeding 600 V. These comparisons reflect the pros and cons of using p-n junction in power diodes. Developing more advanced devices is necessary to simultaneously deliver the forward characteristics of SBDs and the reverse blocking capability of HJDs.

It is also interesting to scrutinize the max junction E-field  $(E_{\rm max})$  in these devices at their  $V_{\rm br}$ , which may suggest if the high critical E-field  $(E_{\rm C})$  in  ${\rm Ga_2O_3}$  has been exploited in large-area devices. Here  $E_{\rm max}$  can be calculated from the 1-D Poisson equations for the non-punch-through (NPT) and punch-through (PT) designs,  $^{52,53)}$  which represents the average junction field

NPT

$$E_{\text{max}} = \sqrt{2qN_{\text{D}}(V_{\text{hi}} + V_{\text{hr}})/(\varepsilon_n \varepsilon_0)}$$

(1)

PT

$$E_{\text{max}} = V_{\text{br}}/W_{\text{D}} + (qN_{\text{D}}W_{\text{D}})/(2\varepsilon_n\varepsilon_0),$$

(2)

where  $W_{\rm D}$  and  $N_{\rm D}$  are the thickness and net donor concentration of the drift region, respectively, q and  $\varepsilon_0$  are electronic charge and permittivity of vacuum, respectively,  $\varepsilon_{\rm n}=12.4$  is the dielectric constant of  $\beta\text{-Ga}_2\text{O}_3$  with the orientation of (001).

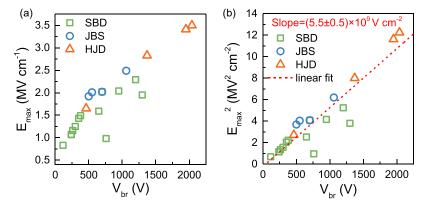

Figure 3(a) shows the  $V_{\rm br}$  versus the calculated  $E_{\rm max}$  for the reported large-area vertical Ga<sub>2</sub>O<sub>3</sub> rectifiers. Most of the reported  $Ga_2O_3$  SBDs and JBS diodes show an  $E_{max}$  below 3 MV cm<sup>-1</sup>, which is below the  $E_{\rm C}$  of GaN and SiC as well as the  $E_{\rm max}$  of the state-of-the-art GaN/SiC devices. A few  $Ga_2O_3$  HJDs show an  $E_{max}$  above 3.4 MV cm<sup>-1</sup>, suggesting the promise of the Ga<sub>2</sub>O<sub>3</sub>/NiO heterojunction junction to exceed the blocking field limit of GaN/SiC devices. Figure 3(b) plots the  $V_{\rm br}$  as a function of  $E_{\rm max}^2$  for large-area Ga<sub>2</sub>O<sub>3</sub> diodes reported so far. The data points are found to roughly align with a linear relation with a slope of  $(5.5 \pm$ 0.5)× $10^9$  V cm<sup>-2</sup>, suggesting that most large-area devices (even with the PT design) have not significantly surpassed the NPT limit. Interestingly, this slope agrees with the calculated  $2qN_{\rm D}/\varepsilon_{\rm n}\varepsilon_0 = 5.8 \times 10^9 \, {\rm V \, cm}^{-2}$  with an  $N_{\rm D} \sim 2 \times 10^{-2}$ 10<sup>16</sup> cm<sup>-3</sup>, which is consistent with the usual epitaxy from the commercial vendor Novel Crystal Technology.

Among the ampere-class  $Ga_2O_3$  diodes, the highest  $V_{br}$  is 2040 V, which is obtained in the beveled-mesa NiO/ $Ga_2O_3$  HJD reported by Zhou et al. <sup>40)</sup> This device has a large on- $\bigcirc$  2023 The Author(s). Published on behalf of

**Fig. 2.** (Color online) Benchmark of (a) forward current versus  $V_{\rm br}$ , (b) forward current versus  $R_{\rm on,sp}$ , and (c)  $V_{\rm br}$  versus  $R_{\rm on,sp}$  for the reported ampere-class vertical  $\beta$ -Ga<sub>2</sub>O<sub>3</sub>-based SBD,  $^{14,20,38,42-48)}$  JBS diode,  $^{39,41,49)}$  HJD,  $^{15,19,40)}$  and lateral MOSFET.  $^{17)}$

**Table I.** Summary of the key performance parameters of large-area  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> power devices.

| Device            |                      | References | Active area (mm <sup>2</sup> ) | Current at $V_{\rm F} = V_{\rm on}$<br>+ 1.5 V (A) | Differential $R_{\text{on,sp}}$ $(\text{m}\Omega\cdot\text{cm}^2)$ | $V_{\rm br}$ (V) | Surge current (A) | t <sub>rr</sub> (ns) | Converter tests and efficiency |

|-------------------|----------------------|------------|--------------------------------|----------------------------------------------------|--------------------------------------------------------------------|------------------|-------------------|----------------------|--------------------------------|

| SBD               | Normal               | 14         | 115                            | 44                                                 | _                                                                  | 240              | _                 | _                    | _                              |

|                   |                      | 19         | 1                              | 2.6                                                | 5.8                                                                | 350              | _                 | _                    | _                              |

|                   |                      |            | 9                              | 11.7                                               | 10.35                                                              | 117              | 38                | 11                   | _                              |

|                   | FP-SBD               | 38,46,47   | 1                              | 0.9                                                | 15.8                                                               | 650              | _                 | 30                   | _                              |

|                   |                      |            | 1.44                           | 0.85                                               | 22                                                                 | 760              | _                 |                      | _                              |

|                   |                      |            | 9                              | 15                                                 | 12                                                                 | 240              | _                 | _                    | _                              |

|                   |                      | 45         | 1.8                            | 1.8                                                | 60                                                                 | 300              | _                 |                      | _                              |

|                   |                      |            | 2.6                            | 2.6                                                | 77.3                                                               | 261              | _                 | _                    | _                              |

|                   |                      | 20         | 9                              | 16.3                                               | 6.75                                                               | 700              | 68                |                      | _                              |

|                   |                      | 48         | 9                              | 30                                                 | 5.13                                                               | 378              | 59                |                      | 98.9% <sup>b)</sup>            |

|                   | FP-                  | 42,44      | 2.89                           | 2.8                                                | 17.1                                                               | 1200             | _                 |                      | _                              |

|                   | MOSSBD               |            |                                |                                                    |                                                                    |                  |                   |                      |                                |

|                   |                      |            | 16.81                          | 8                                                  | 34.9                                                               | 948              |                   | _                    | _                              |

|                   | NiO JTE-             | 43         | 0.78                           | 2.1                                                | 4.68                                                               | 1300             | _                 |                      | _                              |

|                   | SBD                  |            |                                |                                                    |                                                                    |                  |                   |                      |                                |

| JBS               | Normal               | 49         | 1                              | 1.8                                                | 7.6                                                                | 700              | _                 |                      | _                              |

|                   | FP-JBS               | 41         | 9                              | 10                                                 | 11                                                                 | 550              |                   |                      |                                |

|                   |                      |            | 16                             | 15                                                 | 15                                                                 | 500              | _                 |                      | _                              |

|                   | Beveled              | 39         | 9                              | 5.1                                                | 13.5                                                               | 1060             |                   | 26.8                 | 86.07% <sup>b)</sup>           |

|                   | FP-JBS               |            |                                |                                                    |                                                                    |                  |                   |                      |                                |

| HJD               | Normal               | 19         | 1                              | 1.1                                                | 2.6                                                                | 1370             | _                 | _                    | _                              |

|                   |                      |            | 9                              | 9.1                                                | 5.85                                                               | 462              | 45                | 11                   | _                              |

|                   | Beveled-<br>mesa HJD | 15,40      | 1                              | 1.5                                                | 2.26                                                               | 2040             | _                 | 16.4                 | _                              |

|                   |                      |            | 1                              | 1.2                                                | 1.9                                                                | 1950             | _                 | _                    | 98.5% <sup>b)</sup>            |

| Lateral<br>MOSFET |                      | 17         | 0.07                           | 2.4 <sup>a)</sup>                                  | 3.29                                                               | 400              | _                 | _                    | DPT                            |

a) Saturation drain current. b) Power-conversion efficiency tested by PFC circuit.

**Fig. 3.** (Color online) Benchmark of (a)  $V_{\rm br}$  versus  $E_{\rm max}$ , and (b)  $V_{\rm br}$  versus  $E_{\rm max}^2$  for large-sized Ampere-class vertical β-Ga<sub>2</sub>O<sub>3</sub>-based SBD, <sup>14,20,38,42–48</sup>) JBS diode, <sup>39,41,49</sup> and HJD. <sup>15,19,40</sup>)

state current of 20 A at  $\sim 10.5 \, \mathrm{V}$  (1.5 A at  $V_{\mathrm{F}} = V_{\mathrm{on}} + 1.5 \, \mathrm{V}$ ) and also exhibits the lowest  $R_{\mathrm{on,sp}}$  of 2.26 m $\Omega \cdot \mathrm{cm}^2$  with a record Baliga's figure-of-merit of 1.84 (2.87) GW·cm<sup>-2</sup> from DC (pulse) measurements. On the other hand, the highest current demonstrated in vertical Ga<sub>2</sub>O<sub>3</sub> diodes exceeds 100 A. Ribhu et al. <sup>14)</sup> reported the 115 mm<sup>2</sup> vertical Ga<sub>2</sub>O<sub>3</sub> SBD with the highest on-state current of 135 A at 6 V (44 A at  $V_{\mathrm{F}} = V_{\mathrm{on}} + 1.5 \, \mathrm{V}$ ) with a relatively low  $V_{\mathrm{br}}$  of around 240 V.

The JBS diodes hold the potential to combine the SBD's advantage of low turn-on voltage and the HJD's advantage of the enhanced reverse blocking capability. To date, p-NiO is a favorable p-type material for the HJD. Wu et al.<sup>39)</sup> have fabricated 9 mm<sup>2</sup> beveled field-plate (FP) JBS diodes, showing the largest  $V_{\rm br}$  of 1060 V with the forward current of 5.1 A at  $V_{\rm F} = V_{\rm on} + 1.5$  V. Wei et al.<sup>41)</sup> have reported a novel FP vertical Ga<sub>2</sub>O<sub>3</sub> JBS diode with periodically distributed NiO/Ga<sub>2</sub>O<sub>3</sub> heterojunction. The large-area 9 mm<sup>2</sup> (16 mm<sup>2</sup>) devices exhibit the largest forward current of 37 A (51 A) at 6 V and 10 A (15 A) at  $V_F = V_{on} + 1.5 \text{ V}$ , the  $R_{\rm on,sp}$  of  $11 \,\mathrm{m}\Omega \cdot \mathrm{cm}^2$  ( $15 \,\mathrm{m}\Omega \cdot \mathrm{cm}^2$ ), and  $V_{\rm br}$  of  $550 \,\mathrm{V}$ (500 V). Even though, the reverse leakage current level in JBS diodes is still much higher than that of the HJDs, especially under low reverse bias. Thus, advanced designs are needed to further improve the electrical performance of JBS diodes.

#### 3. Thermal management and packaging

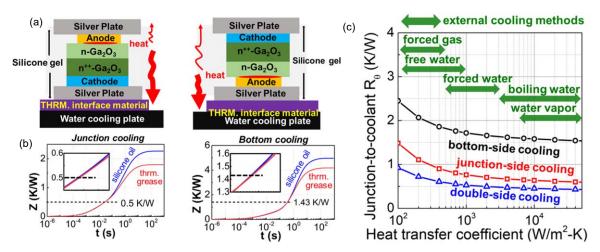

For Ga<sub>2</sub>O<sub>3</sub> power devices, an inevitable by-product of the superior electrical performance is the need to dissipate a higher density of heat due to the smaller device area. In addition, the concurrence of high current density and E-field could produce very high local heat flux, leading to nonuniform temperature distributions and local thermal runaway. What makes heat dissipation more challenging is the low thermal conductivity  $(k_T)$  of  $Ga_2O_3$ , i.e. 11–27 W m<sup>-1</sup>·K<sup>-1</sup>. <sup>56,57</sup>) To address these challenges, thermal management at both the device and package levels is essential.<sup>58)</sup> At the device-level, substrate thinning and hetero-integration with high- $k_{\rm T}$  substrates, such as SiC and diamond, have been reported. <sup>59–62)</sup> Improved device characteristics up to 230 °C were demonstrated in Ga<sub>2</sub>O<sub>3</sub> devices on SiC.<sup>60)</sup> At the packaging level, junction- and double-side heat extraction with advanced cooling are essential for Ga<sub>2</sub>O<sub>3</sub> devices. 63,64) Regardless of these thermal management approaches, their effectiveness has to be evaluated in packaged, large-area power devices as characterized by indispensable datasheet parameters such as the junction-to-case thermal resistance  $(R_{\theta JC})$ .

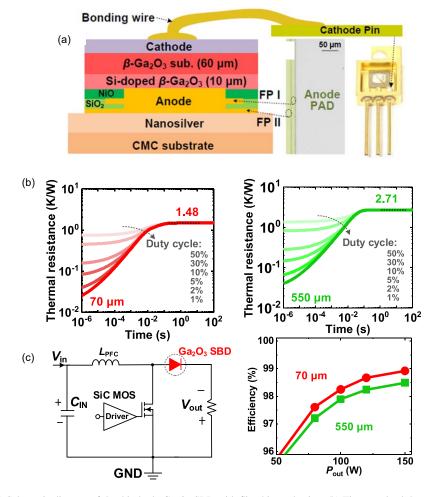

Wang et al.<sup>16)</sup> first demonstrated the double-side packaging of 600 V/15 A Ga<sub>2</sub>O<sub>3</sub> SBDs with nanosilver sintering as the die attach and then employed the packaged devices to evaluate the  $R_{\theta JC}$  under the junction- and bottom-side cooling [Fig. 4(a)]. The junction-side cooling allows for heat extraction directly from the device junction instead of through the Ga<sub>2</sub>O<sub>3</sub> chip. From the thermal impedance curves obtained under two thermal interface materials, the  $R_{\theta JC}$  of the packaged device was extracted to be 1.4 K W<sup>-1</sup> and 0.5 K W<sup>-1</sup> for the bottom-and junction-side-cooling, respectively [Fig. 4(b)]. The  $R_{\theta JC}$  of the junction-side-cooled Ga<sub>2</sub>O<sub>3</sub> SBD is smaller than similarly-rated, TO-packaged

commercial SiC SBDs, manifesting the effectiveness of the junction-side cooling to overcome the low  $k_T$  of Ga<sub>2</sub>O<sub>3</sub>.

Building on  $R_{\theta JC}$ , the authors also simulated the junction to ambient thermal resistance ( $R_{\theta JA}$ ) of Ga<sub>2</sub>O<sub>3</sub> SBDs under different external cooling strategies [Fig. 4(c)]. The results confirmed the need for junction-side cooling and suggested deployment of the external cooling with a heat transfer coefficient (HTC) over  $10^3$  W m<sup>-2</sup>·K<sup>-1</sup>, which can be achieved by the forced water. Double-side cooling can further reduce the  $R_{\theta JA}$  by 30%–40% at the price of the increased complexity, cost, and thermomechanical stress.

For device-level thermal management, despite many simulation studies,  $^{65)}$  experimental works on the large-area, packaged  $Ga_2O_3$  devices have not been reported until very recently. Willhelmi et al. measured the  $R_{\theta JC}$  of large-area  $Ga_2O_3$  SBDs with a substrate thickness thinned down to  $200~\mu m$ .  $^{66)}$  These  $Ga_2O_3$  SBDs were assembled in standard TO-247 packages by soldering and wire bonding and were cathode-side cooled. The thermal measurements and simulations show that the substrate thinning reduces the device  $R_{\theta JC}$  by more than half as compared to the standard substrate thickness ( $500~\mu m$ ). Later simulation results by the same authors  $^{67)}$  revealed the flip-chip assembly for junction-side cooling could further reduce  $R_{\theta JC}$  to be comparable to commercial SiC devices. These results supported the experimental results from Wang and Xiao et al.  $^{16)}$

By combining the junction-side-cooling package and substrate thinning, Gong et al. <sup>48)</sup> demonstrated low  $R_{\theta JC}$  in a 335 V/20 A Ga<sub>2</sub>O<sub>3</sub> SBD [Fig. 5(a)]. Under the junction-side-cooling, the flip-chip Ga<sub>2</sub>O<sub>3</sub> SBD with the thinned substrate (70  $\mu$ m) showed a  $R_{\theta JC}$  (1.48 K W<sup>-1</sup>) lower than the device with the 550  $\mu$ m Ga<sub>2</sub>O<sub>3</sub> substrate (2.71 K W<sup>-1</sup>) [Fig. 5(b)]. In addition to the steady-state  $R_{\theta JC}$ , the transient  $R_{\theta JC}$  of two devices was measured down to a  $\mu$ s-level time scale. This result suggests that, even with an effective junction-side heat extraction, the substrate thinning may still enhance thermal management by boosting heat extraction through the other side of the chip. The package-level and dielevel thermal management need to be co-designed and cooptimized for Ga<sub>2</sub>O<sub>3</sub> power devices. <sup>63)</sup>

A challenge for the package-die thermal co-design is the lack of a modeling framework that interfaces the packageand device-level simulations. (63) Typical package-level finite element analysis (FEA) simulations assume a uniform power dissipation over the device junction neglecting the electrothermal effects (e.g. lattice heating in the sub-micron device structure). Conversely, the typical physics-based device simulations simplify the packaging into a normal boundary thermal resistance or HTC. Recently, Albano et al. <sup>68)</sup> investigated a series of models to integrate the physics-based TCAD model with a package-level FEA model for the packaged Ga<sub>2</sub>O<sub>3</sub> power devices, which demonstrated a superior trade-off between the simulation accuracy and computation load. This paves the road for package-die, electrothermal co-design, and co-optimization for Ga<sub>2</sub>O<sub>3</sub> power devices.

#### 4. Switching performance and circuit applications

Switching performance evaluation and converter demonstrations are key to identifying the market value of the  $Ga_2O_3$  power device technology. Up to now, the relevant switching © 2023 The Author(s). Published on behalf of

**Fig. 4.** (Color online) (a) Measurement setup for the junction-to-case thermal resistance of a double-side-packaged Ga<sub>2</sub>O<sub>3</sub> SBD under the bottom-side cooling (left) and junction-side cooling (right). The measurement results are shown in (b). (c) The simulated junction-to-ambient thermal resistance of the bottom-side-, junction-side- and double-side-cooled Ga<sub>2</sub>O<sub>3</sub> SBD with different external cooling approaches [Reprinted from *IEEE Electron Device Lett.* **42** 1132 (2021). <sup>16</sup>]

**Fig. 5.** (Color online) (a) Schematic diagram of the thin-body  $Ga_2O_3$  SBD with flip-chip packaging. (b) Time-resolved thermal resistance curves of 70  $\mu$ m thin-body  $Ga_2O_3$  SBD (left) and 550  $\mu$ m normal body thickness  $Ga_2O_3$  SBD (right). (c) Circuit schematic of the boost PFC (left) and system efficiency as a function of the output power ( $P_{out}$ ) at a switching frequency of 0.1 MHz [Reprinted from *IEEE Electron Device Lett.* **43** 773 (2022). (48)]

studies have been reported in both vertical  $Ga_2O_3$  diodes and lateral  $Ga_2O_3$  MOSFETs.

Vertical  $Ga_2O_3$  diodes have good potential for various applications such as power factor correction (PFC) and active clamp flyback circuits. An essential test for power diodes is the reverse recovery measurements, as the reverse recovery time  $(t_{\rm rr})$  is a key limiting factor for the switching speed and

loss. It should be mentioned that serious reverse recovery tests should be performed on large-area devices. Otherwise, the waveform could be dominated by the *RC* discharging time; the large resistance of small-area devices could blind the true reverse recovery process. To date, several research groups have made progress in the switching characterization of large-area vertical Ga<sub>2</sub>O<sub>3</sub> diodes.

© 2023 The Author(s). Published on behalf of The Japan Society of Applied Physics by IOP Publishing Ltd

Yang et al.<sup>38)</sup> reported that the  $t_{\rm rr}$  of 1 mm<sup>2</sup> Ga<sub>2</sub>O<sub>3</sub> SBD was ~30 ns for switching from +2 V to a relatively small reverse voltage (-5 V). They later reported a 0.785 mm<sup>2</sup> Ga<sub>2</sub>O<sub>3</sub> rectifier with  $V_{\rm br}$  of 760 V.<sup>69)</sup> The device showed a  $t_{\rm rr}$  of 64 ns when switched from 1 A to -300 V with a minimal temperature dependence of  $t_{\rm rr}$  up to 150 °C. This temperature independence is expected for unipolar conduction.

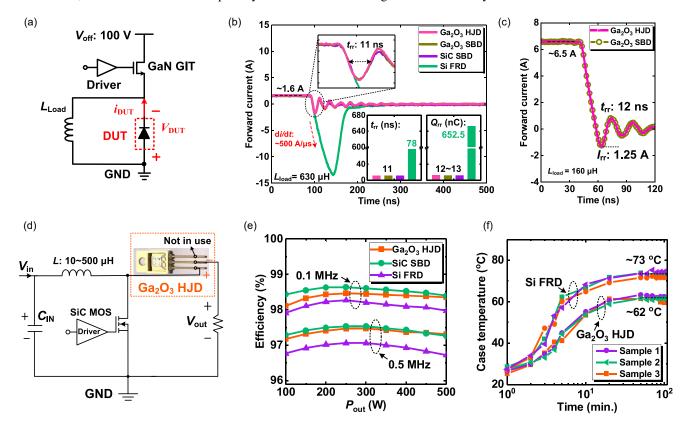

Gong et al. 19) evaluated the dynamic switching performance of 9 mm<sup>2</sup> Ga<sub>2</sub>O<sub>3</sub> HJD and SBD by utilizing the double-pulse-test (DPT) measurements [Fig. 6(a)]. When switched from a forward current of 1.6 A to a reverse bias of 100 V with a fast di/dt of 500 A  $\mu$ s<sup>-1</sup>, the HJD and SBD exhibit similar switching performance with a  $t_{rr}$  of 11 ns and a reverse recovery charge  $(Q_{rr})$  of 13 nC, which is comparable to commercial SiC SBD and far outperforms the Si fastrecovery diode (FRD) [Fig. 6(b)]. Even when the device is switched from a high forward current of  $\sim$ 6.5 A, the HJD still shows almost zero reverse-recovery with a low  $t_{rr}$  of 12.0 ns [Fig. 6(c)]. This is attributed to the short minority carrier lifetime (4.5 ns) in n-Ga<sub>2</sub>O<sub>3</sub> even at high-level injection. A similar nearly-zero reverse recovery was also reported in GaN native p-n junctions. 35) The small  $t_{rr}$  suggests that the Ga<sub>2</sub>O<sub>3</sub> HJD could possess the benefits of the bipolar conduction, such as higher current capability and superior robustness, but do not suffer from the  $t_{rr}$  increase, i.e. the adverse consequence of the bipolar conduction in Si and SiC.

Similarly, Zhou et al.  $^{15,40)}$  reported a short  $t_{\rm rr}$  of 16.4 ns and a reverse recovery charge of 34 nC in the 1 mm<sup>2</sup> beveledmesa  ${\rm Ga_2O_3}$  HJD assembled in the TO-220 package. Furthermore, the overall correction capability of this device

was evaluated in a 500 W PFC converter with long-term continuous operation [Fig. 6(d)]. This device showed good stability in continuous operation and enabled a high power-conversion efficiency of 98.5% and 97.4% at the switching frequency of 0.1 and 0.5 MHz, respectively, which outperformed Si FRDs [Fig. 6(e)]. Figure 6(f) demonstrates that the HJD exhibited a low case temperature of 62 °C at 0.3 MHz/500 W steady-state operation, approximately 11 °C lower than that of commercial Si FRD. Similar converter tests were also performed by Gong et al. 480 on the thin-substrate Ga<sub>2</sub>O<sub>3</sub> SBD as described in Sect. 3 (see Fig. 5). A record high power efficiency of 98.9% at a switching frequency of 0.1 MHz was achieved by the device, which is higher than the device with the standard substrate thickness (and inferior thermal performance) [Fig. 5(c)].

Guo et al. demonstrated a DC-DC converter with the 2 A/ 467 V Ga<sub>2</sub>O<sub>3</sub> SBDs assembled in a TO-220 package. The  $t_{\rm rr}$  of 8.8 ns with a  $Q_{\rm rr}$  of 8.33 nC was achieved when the device was switched from 1 A to -100 V with a di/dt of  $400 \text{ A} \ \mu \text{s}^{-1}$ . The converter showed a high conversion efficiency of up to 95.62% at the input voltage of 200 V and an operating frequency of 100 kHz, which is comparable to that based on a similarly-rated commercial SiC SBD. Later, the same group reported a  $t_{\rm rr}$  of 26.8 ns in a 5 A/1060 V Ga<sub>2</sub>O<sub>3</sub> JBS diode. They further used this device to demonstrate a four-stage hybrid half-wave Cockcroft-Walton voltage multiplier. The hybrid circuit using the Ga<sub>2</sub>O<sub>3</sub> JBS and SiC SBD showed a multiplication factor of 3.81, being comparable to the factor of all SiC SBD circuits. A high circuit efficiency of 86.07% was also demonstrated.

Fig. 6. (Color online) (a) Schematic of the DPT circuit. The fast-speed commercial GaN gate injection transistor (GIT) has been used as a control switch. (b) Reverse recovery characteristics of different diodes. (c) Reverse recovery waveforms with a high forward current of  $\sim$ 6.5 A. (d) Schematic of the PFC circuit ( $V_{in}$ : 0–310 V,  $V_{out}$ :  $\sim$ 390 V) with the packaged Ga<sub>2</sub>O<sub>3</sub> HJD. (e) System power-conversion efficiency versus output power ( $P_{out}$ ) of a 500 W PFC circuit at switching frequencies of 0.1 and 0.5 MHz. (f) The extracted cast temperature of the 3 samples at 0.3 MHz/500 W [(a)–(c) Reprinted from *IEEE Trans. Power Electron.* 36 12213 (2021). (d)–(f) Reprinted from *IEEE Trans. Power Electron.* 37 1223 (2021). (e)

The above results show the gigantic potential of vertical  $Ga_2O_3$  power diodes for low switching loss, high conversion efficiency, and high-temperature power electronics applications.

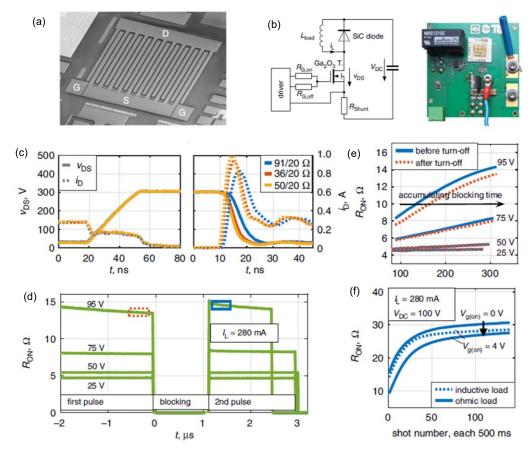

Static characteristics and switching performance of lateral Ga<sub>2</sub>O<sub>3</sub> MOSFET have also been investigated. <sup>17,18)</sup> J. Böcker et al. reported a large-area lateral Ga<sub>2</sub>O<sub>3</sub> MOSFET with a R<sub>on</sub> of 5  $\Omega$  and forward saturation current up to 2.5 A, as shown in Fig. 7(a). 18) DPT setup shown in Fig. 7(b) is employed to evaluate the high-voltage switching dynamics. Figure 7(c) shows the hard-switching performance under different gate resistances. The voltage slope during turn-on increased from 35 to 50 V ns<sup>-1</sup> by reducing the gate resistance from 91 to 36  $\Omega$  at an input voltage of 300 V. The dynamics  $R_{\rm on}$  under different DC voltages, load currents and load conditions, as well as the increased blocking time, were investigated to determine the impact and origin of the charge trapping effect [Figs. 7(d)–7(f)]. The  $R_{\rm on}$  was found to increase obviously by applying a DC voltage for 1 s before the DPT. Only a small further increase was observed after 1  $\mu s$  blocking and the following turn-on process [Fig. 7(d)]. The increased blocking time also resulted in  $R_{\rm on}$  increase during the repetitive DPT [Fig. 7(e)]. Figure 7(f) showed that the  $R_{\rm on}$  dynamic increase could be mitigated by increasing the turn-on driver voltage. These results suggested that the charge trapping during the blocking process in the gate region mainly resulted in the dynamics  $R_{\rm on}$  increase.

Afterward, the same group reported the hard-switching characteristics of large-area lateral MOSFET with a bus

voltage increased up to  $400 \,\mathrm{V}.^{17)}$  A higher turn-on speed of  $78 \,\mathrm{V}\,\mathrm{ns}^{-1}$  was demonstrated by utilizing the FP structure and improving the fabrication process. Similar dynamics  $R_{\mathrm{on}}$  issues were found during the hard-switching operation. Hence, device innovation and process improvement should be focused on future research to mitigate the current dispersion and dynamics  $R_{\mathrm{on}}$  increase under the dynamic switching.

### 5. Ruggedness

Power devices are required to possess ruggedness against abnormal operations outside the safe operating area for a sufficient time before the protection circuitry intervenes. Such abnormal operations involve overvoltage and overcurrent far exceeding the rated values. The corresponding ruggedness for power diodes mainly includes (1) the avalanche or overvoltage ruggedness, 5,72,73) which measures the device capability to withstand transient surge energy or overvoltage in the off-state, and (2) the surge current ruggedness, 35) which measures the device capability to withstand transient overcurrent in the on-state. For power transistors, in addition to the avalanche/overvoltage ruggedness, the short-circuit ruggedness measures the device capability to withstand the transient overcurrent not only in the on-state but also in the high-bias blocking state.<sup>34)</sup> Meanwhile, gate ruggedness is also important for power transistors.<sup>74)</sup>

The ruggedness is a critical concern for  $Ga_2O_3$  power devices due to the high junction E-field and low  $k_T$  of  $Ga_2O_3$ .

Fig. 7. (Color online) (a) A photograph of the lateral  $Ga_2O_3$  MOSFET. (b) Circuit test setup for the DPT. (c) Switching characteristics of the lateral  $Ga_2O_3$  MOSFET with different gate resistance.  $R_{on}$  dynamics during DPT (d) at different DC voltages, (e) before and after the blocking period for rising load currents, and (f) with ohmic and inductive load, as well as different turn-on driver voltages. [Reprinted from *Electron. Lett.* **56** 838 (2020). [8]

SF0801-7

As most ruggedness involves the electrothermal, transient, non-equilibrium process, it has to be characterized on largearea, packaged devices in circuit tests. The measurement results for on-wafer, small-area devices are usually less meaningful, as there are no straightforward scaling laws to use these results to project the ruggedness of practical devices. Very recently, thanks to the progress on Ga<sub>2</sub>O<sub>3</sub> large-area devices, a few groups have experimentally investigated the surge current and overvoltage ruggedness of Ga<sub>2</sub>O<sub>3</sub> diodes. Meanwhile, simulation investigations have been reported on the short-circuit ruggedness of Ga<sub>2</sub>O<sub>3</sub> transistors.

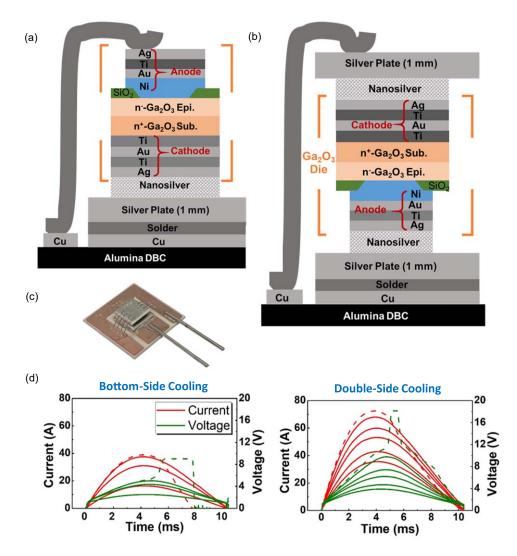

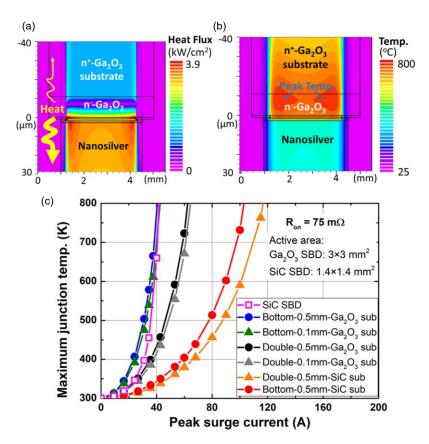

Surge current is an essential ruggedness metric listed in any power diode's datasheet. A surge-current test circuit usually produces a 10 ms wide half-sinusoidal current waveform based on the JEDEC standard. Buttay et al.<sup>75)</sup> first studied the surge current capability of Ga<sub>2</sub>O<sub>3</sub> diodes using the device model and the SPICE network model; junction-side cooling was identified to be an effective pathway to boost the surge ruggedness. Following this theoretical study, Xiao and Wang et al.<sup>20)</sup> reported the first experimental studies of the surge current ruggedness of Ga<sub>2</sub>O<sub>3</sub> SBDs assembled in the bottom-side and double-side cooling package. As shown in Figs. 8(a)–8(c), a 1 mm thick Ag plate was deployed to confine the heat diffusion during the 10 ms transient and thus eliminate the impact of the outer solder, DBC, and wire bonds. The surge-current tests revealed a critical surge current of 37.5 A for the bottomside-packaged Ga<sub>2</sub>O<sub>3</sub> SBD and 68 A for the double-sidepackaged Ga<sub>2</sub>O<sub>3</sub> SBD [Fig. 8(d)].

The higher surge current capability of the double-sidepackaged Ga<sub>2</sub>O<sub>3</sub> SBD is attributable to the effective heat removal through the junction and the resultant migration of the peak temperature location. This was illustrated by the results of the electrothermal, device-circuit, mixed-mode TCAD simulations.<sup>20)</sup> At the high surge current transient, in a double-side-packaged Ga<sub>2</sub>O<sub>3</sub> SBDs, the simulated heat flux contour reveals that most heat is removed through the junction [Fig. 9(a)], and the peak temperature location moves from the Schottky junction into the bulk Ga<sub>2</sub>O<sub>3</sub> [Fig. 9(b)]. As the bulk semiconductor is usually more thermally robust as compared to the heterogenous interface, a higher peak temperature (and higher surge current capability) can be accommodated.

The other interesting finding in Ref. 20 is that the packaged Ga<sub>2</sub>O<sub>3</sub> SBDs show a superior surge current capability as compared to the similarly-rated commercial SiC SBDs. In addition to the effective junction-side heat removal, a key enabling mechanism is the smaller temperature coefficient of the differential on-resistance ( $\alpha$ ) in Ga<sub>2</sub>O<sub>3</sub> SBDs ( $\alpha \sim 0.73$ ) as compared to that in SiC SBDs ( $\alpha > 2.5$ ), which suppress the positive feedback of the increase in onresistance and junction temperature. The critical role of  $\alpha$  on the surge current capability was also confirmed in GaN, where the negative  $\alpha$  of GaN p-n diodes enables a high surge current.<sup>35)</sup> The physical mechanism of the low  $\alpha$  of Ga<sub>2</sub>O<sub>3</sub> SBDs could be related to the deep donors but requires further investigation.<sup>20)</sup> The authors in Ref. 20 also used the calibrated simulation models to explore the approaches to further improve the surge current capability of Ga<sub>2</sub>O<sub>3</sub> SBDs [Fig. 9(c)]. The  $Ga_2O_3$  integration with the high- $k_T$  substrate,

in the combination with the double-side-cooling package, is predicted to be the most effective way.

Gong et al. 19) recently reported the surge current ruggedness of Ga<sub>2</sub>O<sub>3</sub> HJDs and SBDs assembled in the TO-220 package. The Ga<sub>2</sub>O<sub>3</sub>/NiO HJDs exhibit a higher surge current capability than SBD, possibly due to the negative  $\alpha$  observed in HJDs. These results suggest the Ga<sub>2</sub>O<sub>3</sub>/NiO p-n junction possesses the functionality to boost the surge current ruggedness similar to the homogenous p-n junction in GaN and SiC. Later, the authors<sup>48)</sup> reported the surge current capability of the junction-side-packaged Ga<sub>2</sub>O<sub>3</sub> SBDs with the thinned substrate [see Fig. 5(a)]. A critical surge current (59 A) much higher than the TO-packaged Ga<sub>2</sub>O<sub>3</sub> SBD (38 A)<sup>19)</sup> was demonstrated, further manifesting the importance of packaging on the surge current ruggedness of Ga<sub>2</sub>O<sub>3</sub> devices.

Avalanche is a desirable capability for power devices to withstand overvoltage stresses, as it relies on impact ionization and multiplication to allow devices to pass a high current at the non-destructive  $V_{\rm br}$ . However, not all power devices come with the avalanche capability: it is absent in commercial GaN high-electron mobility transistors<sup>5)</sup> but equipped in most Si and SiC devices as well as some other GaN bipolar devices. 21,29-32) As the avalanche in Si, SiC and GaN devices all rely on native p-n junctions, it could be very difficult to realize the avalanche-capable Ga<sub>2</sub>O<sub>3</sub> devices due to the lack of the p-type Ga<sub>2</sub>O<sub>3</sub>. Hence, for the overvoltage ruggedness of Ga<sub>2</sub>O<sub>3</sub> devices, a very good reference is the GaN HEMT. Recent studies of the GaN HEMT overvoltage ruggedness converge on several key conclusions: (1) the device relies on the overvoltage margin and output capacitance to withstand the overvoltage stress without the capability to dissipate the surge energy, 5,73,76) (2) the overvoltage ruggedness can be characterized by the unclamped inductive switching (UIS) circuit,  $^{5}$  and (3) the  $V_{\rm br}$  in short switching transient (i.e. dynamic  $V_{\rm br}$ ) could be very different from (usually larger) that measured on the curve tracer (i.e. static  $V_{\rm br}$ ). <sup>76–78)</sup>

Recently, Zhou et al. 15) reported the overvoltage ruggedness of large-area Ga<sub>2</sub>O<sub>3</sub>/NiO HJDs using single-pulse and repetitive UIS circuits. The  $Ga_2O_3$  HJD exhibits a static  $V_{br}$ of 1.95 kV and a dynamic  $V_{\rm br}$  of 2.23 kV, suggesting an increased overvoltage margin in dynamic switching. In addition, the Ga<sub>2</sub>O<sub>3</sub> HJD shows no parametric shifts after 1 million cycles if UIS stresses with a peak overvoltage of 1.2 kV. This result demonstrates the good overvoltage ruggedness with a withstanding physics similar to GaN HEMTs in Ga<sub>2</sub>O<sub>3</sub> power devices.

Very recently, Lu et al. <sup>79)</sup> reported a numerical simulation on the short-circuit ruggedness of a kV-class vertical Ga<sub>2</sub>O<sub>3</sub> power FinFET at the blocking voltage of 800 V. The FinFET is an emerging power transistor first developed in GaN<sup>1,23,24)</sup> and later demonstrated in Ga<sub>2</sub>O<sub>3</sub><sup>80,81)</sup> with state-of-the-art performance in Ga<sub>2</sub>O<sub>3</sub> power transistors. The forward conduction and breakdown mechanism both hinge on the fin channel design, 82-84) and switching performance also depends on the inter-fin designs.<sup>85)</sup> The short-circuit analysis of vertical Ga<sub>2</sub>O<sub>3</sub> FinFETs suggests the strong impact of the inter-fin architectures on the device short-circuit withstanding time (SCWT).<sup>79)</sup> The full-gate structure has the worst SCWT due to electrostatics; the split-gate structure can increase the SCWT at the price of  $V_{\rm br}$  degradation. The simulation predicts that the split-gate design with the inter-fin source © 2023 The Author(s). Published on behalf of

**Fig. 8.** (Color online) (a) Schematics of Ga<sub>2</sub>O<sub>3</sub> SBDs assembled in the (a) bottom-side cooling package and (b) double-side cooling package. (c) Photo of the prototyped double-side packaged Ga<sub>2</sub>O<sub>3</sub> SBDs. (d) Surge current test waveforms of the two packaged Ga<sub>2</sub>O<sub>3</sub> SBDs with the increased surge current magnitude. [Reprinted from *IEEE Trans. Power Electron.* **36** 8565 (2021).<sup>20)</sup>]

coverage could provide the best trade-off between the short-circuit ruggedness and  $V_{\rm br}$  in vertical  $Ga_2O_3$  power FinFETs.

#### 6. Summary and research needs

This paper provides a timely review of the state-of-the-art of the large-area  $Ga_2O_3$  power devices. The key takeaways include:

- 1) Ampere-class  $Ga_2O_3$  power diodes (SBDs, JBS diodes, and HJDs) and MOSFETs have been widely reported with  $V_{\rm br}$  up to >2 kV and 400 V for diodes and MOSFETs, respectively. The performance of most devices is superior to the Si counterparts but still inferior to the SiC and GaN ones. The junction field of several large-area  $Ga_2O_3$  HJDs has surpassed the  $E_{\rm C}$  of SiC or GaN, fulfilling the superior electrical properties of  $Ga_2O_3$ .

- 2) Junction-side packaging and cooling are essential for the thermal management of  $Ga_2O_3$  power devices, and they can overcome the low- $k_T$  limitations of the  $Ga_2O_3$  material to deliver a low device  $R_{\theta JC}$ . Die-level thermal management such as heterogenous integration and substrate thinning are desirable to be further combined with the junction-side or double-side packaging.

- 3) Ga<sub>2</sub>O<sub>3</sub> SBDs and HJDs have shown minimal reverse recovery and have been applied in a variety of power converters to achieve high power-conversion efficiency. Ga<sub>2</sub>O<sub>3</sub> MOSFETs have exhibited fast switching speed in inductive power switching.

- 4) The surge current capability and overvoltage ruggedness of Ga<sub>2</sub>O<sub>3</sub> SBDs and HJDs have been demonstrated to be comparable or even superior to some SiC and GaN counterparts. Device architectures (e.g. channel design), packaging and cooling, and material properties (e.g. deep dopants) all impact the ruggedness of Ga<sub>2</sub>O<sub>3</sub> devices in an interdependent way.

- 5) The NiO/Ga<sub>2</sub>O<sub>3</sub> heterogenous p-n junction exhibits promising characteristics for power devices, including good current and voltage scalability, minimal reverse recovery, and excellent surge-current and overvoltage ruggedness. It could become an important building block for many advanced Ga<sub>2</sub>O<sub>3</sub> diodes and transistors.

Despite the exciting progress, the research of large-area  $Ga_2O_3$  power devices is still in the early stage. We envision the following immediate research gaps that need to be addressed for advancing  $Ga_2O_3$  into industrial power electronics applications.

© 2023 The Author(s). Published on behalf of The Japan Society of Applied Physics by IOP Publishing Ltd

**Fig. 9.** (Color online) The simulated contours of (a) heat flux and (b) temperature in the  $Ga_2O_3$  SBD junction region at the surge current transient. (c) Projected peak temperature as a function of peak surge current for the  $Ga_2O_3$  SBDs with different thermal management techniques (bottom/double-side package, 0.1/0.5 mm substrate thickness, transfer to SiC substrate) and a reference SiC SBD. [Reprinted from *IEEE Trans. Power Electron.* **36** 8565 (2021).<sup>20)</sup>]

- 1) P-n junctions form the blocking block for nearly all power devices with avalanche capability and over-current robustness. Despite the numerous advantages offered by the UWBG material, the absence of p-type Ga<sub>2</sub>O<sub>3</sub> conductivity may make it difficult to fully utilize these advantages. Although Ga<sub>2</sub>O<sub>3</sub> p-n heterojunction has emerged as an alternative bipolar design to deliver superior performance than the SBD counterparts, the fundamental challenge is the mismatch of bandgap and critical electrical field strength that may hinder the electric-field handling capability. Another important consideration is the interface engineering in such heterojunctions, where interfacial traps and impurities would degrade the electrical performance and reliability robustness.

- 2) Defect reduction is key to boosting the performance of large-area devices. Deep-level defects/traps within Ga<sub>2</sub>O<sub>3</sub> bulk and interfacial regions generally act as carrier generation-recombination (G-R) centers, which are the dominant sources to degrade device performance and reliability. Defects may be unintentionally-introduced impurities or intrinsic crystalline defects (dislocations or stacking faults) that are energetically formed and inhomogeneously distributed during material growth. Therefore, the fundamental challenge in the material aspect, reducing defects and dislocations, is crucial to enhance carrier transport and improve device performance.

- 3) Junction capacitance and switching charges are critical for power devices; to enable advantages in practical

- power devices, the low  $R_{\rm on,sp}$  has to be converted to the realization of smaller capacitances and charges. However, the relevant studies are quite scarce in  $\rm Ga_2O_3$ . Very recent work reported the capacitance, charges, and switching figure-of-merits (FOMs) of  $\rm Ga_2O_3$  SBDs for the first time,  $^{86)}$  while the switching FOM is still inferior to the commercial SiC SBDs. A rigorous study of the impact of the low carrier mobility in  $\rm Ga_2O_3$  on the switching FOMs of  $\rm Ga_2O_3$  devices for different applications (e.g. soft-switching, hard-switching) is highly desirable to understand  $\rm Ga_2O_3$ 's true application space in power electronics.

- 4) Device innovations are highly desirable to further improve the junction E-field in large-area Ga<sub>2</sub>O<sub>3</sub> devices and ensure it would not compromise in devices with the upscaled current and voltage ratings. While the average junction E-field calculated in many papers of small-area Ga<sub>2</sub>O<sub>3</sub> devices could be a good indicator of the material limit, it does not mean any true advantage in power device performance, particularly for devices with low V<sub>br</sub>. Currently, the junction E-field in ampereclass, high-voltage Ga<sub>2</sub>O<sub>3</sub> devices is still much lower than that reported in small-area Ga<sub>2</sub>O<sub>3</sub> devices with low V<sub>br</sub>.

- 5) The fundamentals of the Ga<sub>2</sub>O<sub>3</sub> heterogeneous p-n junction in power switching, particularly the carrier dynamics under the non-equilibrium, transient switching conditions, are important for understanding the device switching and ruggedness characteristics. In addition, the feasibility of avalanche in heterogeneous

p-n junction remains an open question. The avalanche capability, if achievable in heterogeneous junctions, could be a strong boost to not only the ruggedness but also the performance of  $Ga_2O_3$  power devices (as the  $V_{\rm br}$  margin required for a specific voltage rating could be much smaller for avalanche-capable power devices).

We envision that Ga<sub>2</sub>O<sub>3</sub> power devices hold tremendous potential for penetration into power electronics applications if these gaps can be addressed in the next few years.

#### **Acknowledgments**

We appreciate the in-person discussions with  $Ga_2O_3$  researchers in IWGO2022. The work at Virginia Tech is in part supported by National Science Foundation under Grants ECCS-2100504 and ECCS-2230412 and in part by the Center for Power Electronics Systems High Density Integration Industry Consortium.

#### **ORCID iDs**

Yuhao Zhang https://orcid.org/0000-0001-6350-4861

- 1) Y. Zhang, F. Udrea, and H. Wang, Nat. Electron. 5, 723 (2022).

- K. Hoo Teo, Y. Zhang, N. Chowdhury, S. Rakheja, R. Ma, Q. Xie, E. Yagyu, K. Yamanaka, K. Li, and T. Palacios, J. Appl. Phys. 130, 160902 (2021).

- 3) X. She, A. Q. Huang, O. Lucia, and B. Ozpineci, IEEE Trans. Ind. Electron. 64, 8193 (2017).

- 4) S. C. J. Y. Tsao et al., Adv. Electron. Mater. 4, 1600501 (2018).

- R. Zhang, J. P. Kozak, M. Xiao, J. Liu, and Y. Zhang, IEEE Trans. Power Electron. 35, 13409 (2020).

- J. A. Spencer, A. L. Mock, A. G. Jacobs, M. Schubert, Y. Zhang, and M. J. Tadjer, Appl. Phys. Rev. 9, 011315 (2022).

- M. Higashiwaki, K. Sasaki, H. Murakami, Y. Kumagai, A. Koukitu, A. Kuramata, T. Masui, and S. Yamakoshi, Semicond. Sci. Technol. 31, 034001 (2016).

- A. J. Green, J. Speck, G. Xing, P. Moens, F. Allerstam, K. Gumaelius, T. Neyer, A. Arias-Purdue, V. Mehrotra, and A. Kuramata, APL Mater. 10, 029201 (2022).

- 9) M. Higashiwaki and G. H. Jessen, Appl. Phys. Lett. 112, 060401 (2018).

- S. Pearton, J. Yang, P. H. Cary IV, F. Ren, J. Kim, M. J. Tadjer, and M. A. Mastro, Appl. Phys. Rev. 5, 011301 (2018).

- 11) M. J. Tadjer, Science 378, 724 (2022).

- M. Higashiwaki, K. Sasaki, T. Kamimura, M. Hoi Wong, D. Krishnamurthy,

A. Kuramata, T. Masui, and S. Yamakoshi, Appl. Phys. Lett. 103, 123511 (2013).

- M. Higashiwaki, K. Sasaki, A. Kuramata, T. Masui, and S. Yamakoshi, Appl. Phys. Lett. 100, 013504 (2012).

- 14) R. Sharma, M. Xian, C. Fares, M. E. Law, M. Tadjer, K. D. Hobart, F. Ren, and S. J. Pearton, J. Vac. Sci. Technol. A 39, 013406 (2021).

- 15) F. Zhou et al., IEEE Trans. Power Electron. 37, 1223 (2021).

- 16) B. Wang, M. Xiao, J. Knoll, C. Buttay, K. Sasaki, G. Q. Lu, C. Dimarino, and Y. Zhang, IEEE Electron Device Lett. 42, 1132 (2021).

- 17) C. Kuring, K. Tetzner, A. Popp, S. Heucke, O. Hilt, S. B. Anooz, J. Würfl, and S. Dieckerhoff, IEEE 8th Workshop Wide Bandgap Power Devices Appl. 2021, 52 (2021).

- 18) J. Böcker, K. Tetzner, S. Heucke, O. Hilt, E. Bahat-Treidel, S. Dieckerhoff, and J. Würfl, Electron. Lett. 56, 838 (2020).

- 19) H. Gong et al., IEEE Trans. Power Electron. 36, 12213 (2021).

- 20) M. Xiao et al., IEEE Trans. Power Electron. 36, 8565 (2021).

- J. Liu, M. Xiao, R. Zhang, S. Pidaparthi, C. Drowley, L. Baubutr,

A. Edwards, H. Cui, C. Coles, and Y. Zhang, IEEE Electron Device Lett. 41, 1328 (2020).

- I. C. Kizilyalli, A. P. Edwards, H. Nie, P. Bui-Quang, D. Disney, and D. Bour, IEEE Electron Device Lett. 35, 654 (2014).

- 23) Y. Zhang, A. Zubair, Z. Liu, M. Xiao, J. Perozek, Y. Ma, and T. Palacios, Semicond. Sci. Technol. 36, 054001 (2021).

- 24) Y. Zhang and T. Palacios, IEEE Trans. Electron Devices 67, 3960 (2020).

- 25) H. Nie, Q. Diduck, B. Alvarez, A. P. Edwards, B. M. Kayes, M. Zhang, G. Ye, T. Prunty, D. Bour, and I. C. Kizilyalli, IEEE Electron Device Lett. 35, 939 (2014).

- 26) D. Shibata, R. Kajitani, M. Ogawa, K. Tanaka, S. Tamura, T. Hatsuda, M. Ishida, and T. Ueda, 2016 IEEE Int. Electron Devices Meet. 10.1.

- 27) Y. Zhang, M. Sun, J. Perozek, Z. Liu, A. Zubair, D. Piedra, N. Chowdhury, X. Gao, K. Shepard, and T. Palacios, IEEE Electron Device Lett. 40, 75 (2018).

- 28) T. Oka, T. Ina, Y. Ueno, and J. Nishii, 2019 31st IEEE Int. Symp. Power Semicond. Devices ICs 2019, p. 303.

- R. Zhang, J. Liu, Q. Li, S. Pidaparthi, A. Edwards, C. Drowley, and Y. Zhang, IEEE Electron Device Lett. 43, 366 (2022).

- 30) J. Liu, R. Zhang, M. Xiao, S. Pidaparthi, H. Cui, A. Edwards, C. Drowley, and Y. Zhang, IEEE Trans. Power Electron. 37, 5433 (2021).

- J. Liu, M. Xiao, R. Zhang, S. Pidaparthi, H. Cui, A. Edwards, M. Craven, L. Baubutr, C. Drowley, and Y. Zhang, IEEE Trans. Electron Devices 68, 2025 (2021).

- 32) J. Liu, M. Xiao, Y. Zhang, S. Pidaparthi, H. Cui, A. Edwards, L. Baubutr, W. Meier, C. Coles, and C. Drowley, 2020 IEEE Int. Electron Devices Meet., 23.2, 10.1109/IEDM13553.2020.9372048.

- 33) R. Zhang, J. Liu, Q. Li, S. Pidaparthi, A. Edwards, C. Drowley, and Y. Zhang, 2022 IEEE Int. Reliab. Phys. Symp., .

- 34) R. Zhang, J. Liu, Q. Li, S. Pidaparthi, A. Edwards, C. Drowley, and Y. Zhang, IEEE Trans. Power Electron. 37, 6253 (2021).

- 35) J. Liu, R. Zhang, M. Xiao, S. Pidaparthi, H. Cui, A. Edwards, L. Baubutr, C. Drowley, and Y. Zhang, IEEE Trans. Power Electron. 36, 10959 (2021).

- 36) D. Ramanathan, PCIM Europe 2022 Int. Exhib. Conf. Power Electron. Intell. Motion Renewable Energy Energy Manage. 2022, p. 1.

- 37) C. Wang, J. Zhang, S. Xu, C. Zhang, Q. Feng, Y. Zhang, J. Ning, S. Zhao, H. Zhou, and Y. Hao, J. Phys. D: Appl. Phys. 54, 243001 (2021).

- 38) J. Yang, F. Ren, M. Tadjer, S. Pearton, and A. Kuramata, AIP Adv. 8, 055026 (2018).

- 39) F. Wu, Y. Wang, G. Xu, Y. Lv, and S. Long, The 4th Int. Workshop on Gallium Oxide Related Mater. 2022, p. 274.

- 40) F. Zhou et al., Appl. Phys. Lett. 119, 262103 (2021).

- 41) J. Wei, Y. Wei, J. Lu, X. Peng, Z. Jiang, K. Yang, and X. Luo, IEEE 34th Int. Symp. Power Semicond. Devices ICs 2022, 97 (2022).

- 42) F. Otsuka, H. Miyamoto, K. Sasaki, and A. Kuramata, The 4th Int. Workshop on Gallium Oxide Related Mater. 2022, p. 336.

- 43) W. Hao et al., IEEE Int. Electron Devices Meet. 2022, 210 (2022).

- 44) F. Otsuka, H. Miyamoto, A. Takatsuka, S. Kunori, K. Sasaki, and A. Kuramata, Appl. Phys. Express 15, 016501 (2021).

- 45) M. Ji, N. R. Taylor, I. Kravchenko, P. Joshi, T. Aytug, L. R. Cao, and M. P. Paranthaman, IEEE Trans. Power Electron. 36, 41 (2020).

- 46) J. Yang et al., Appl. Phys. Lett. 114, 232106 (2019).

- 47) J. Yang, C. Fares, R. Elhassani, M. Xian, F. Ren, S. Pearton, M. Tadjer, and A. Kuramata, ECS J. Solid State Sci. Technol. 8, Q3159 (2019).

- 48) H. Gong, F. Zhou, X. Yu, W. Xu, F. F. Ren, S. Gu, H. Lu, J. Ye, and R. Zhang, IEEE Electron Device Lett. 43, 773 (2022).

- 49) Y. Lv et al., IEEE Trans. Power Electron. 36, 6179 (2020).

- 50) H. Gong, X. Chen, Y. Xu, Y. Chen, F. Ren, B. Liu, S. Gu, R. Zhang, and J. Ye, IEEE Trans. Electron Devices 67, 3341 (2020).

- 51) Z. Wang et al., IEEE Trans. Electron Devices 69, 981 (2022).

- 52) N. Allen, M. Xiao, X. Yan, K. Sasaki, M. J. Tadjer, J. Ma, R. Zhang, H. Wang, and Y. Zhang, IEEE Electron Device Lett. 40, 1399 (2019).

- 53) H. Gong, X. Chen, Y. Xu, F.-F. Ren, S. Gu, and J. Ye, Appl. Phys. Lett. 117, 022104 (2020).

- 54) P. Gopalan et al., Appl. Phys. Lett. 117, 252103 (2020).

- A. Fiedler, R. Schewski, Z. Galazka, and K. Irmscher, ECS J. Solid State Sci. Technol. 8, Q3083 (2019).

- 56) Z. Guo, A. Verma, X. Wu, F. Sun, A. Hickman, T. Masui, A. Kuramata, M. Higashiwaki, D. Jena, and T. Luo, Appl. Phys. Lett. 106, 111909 (2015).

- 57) M. Slomski, N. Blumenschein, P. Paskov, J. Muth, and T. Paskova, J. Appl. Phys. 121, 235104 (2017).

- 58) A. Iradukunda, D. R. Huitink, and F. Luo, IEEE J. Emerg. Sel. Topics Power Electron. 8, 256 (2019).

- 59) Y. Song et al., ACS Appl. Mater. Interfaces 13, 40817 (2021).

- W. Xu et al., 2019 IEEE Int. Electron Devices Meet., 10.1109/ IEDM19573.2019.8993501.

- 61) W. Xu et al., Fundam. Res. 1, 691 (2021).

- 62) Z. Cheng, L. Yates, J. Shi, M. J. Tadjer, K. D. Hobart, and S. Graham, APL Mater. 7, 031118 (2019).

- 63) Y. Qin, B. Albano, J. Spencer, J. S. Lundh, B. Wang, C. Buttay, M. J. Tadjer, C. DiMarino, and Y. Zhang, J. Phys. D: Appl. Phys. accepted (2023).

- 64) J. A. Spencer, A. L. Mock, and Y. Zhang, "Thermal management of gallium nitride electronics," *Heating Issues in Wide-Bandgap Semiconductor Devices* (Elsevier, Amsterdam, 2022) p. 1.

- 65) B. Chatterjee, K. Zeng, C. D. Nordquist, U. Singisetti, and S. Choi, IEEE Trans. Compon., Packag., Manuf. Technol. 9, 2352 (2019).

- 66) F. Wilhelmi, Y. Komatsu, S. Yamaguchi, Y. Uchida, R. Nemoto, and A. Lindemann, CIPS 2022; 12th Int. Conf. Integr. Power Electron. Syst. 2022, p. 1.

- 67) F. Wilhelmi, Y. Komatsu, S. Yamaguchi, Y. Uchida, R. Nemoto, and A. Lindemann, Int. Conf. Electron. Package 2022, 145 (2022).

- B. Albano, B. Wang, Y. Zhang, and C. DiMarino, 2002 IEEE Energy Convers. Congr. Expo. (ECCE), 10.1109/ECCE50734.2022.9948059.

- 69) J. Yang, F. Ren, Y.-T. Chen, Y.-T. Liao, C.-W. Chang, J. Lin, M. J. Tadjer, S. Pearton, and A. Kuramata, IEEE J. Electron Devices Soc. 7, 57 (2018).

- 70) W. Guo et al., IEEE J. Electron Devices Soc. 10, 933 (2022).

- 71) F. Wu et al., IEEE Trans. Electron Devices under review (2023).

- 72) J. P. Kozak, R. Zhang, J. Liu, K. D. Ngo, and Y. Zhang, IEEE J. Emerg. Sel. Topics Power Electron. 10, 5027 (2021).

- 73) J. P. Kozak, Q. Song, R. Zhang, Y. Ma, J. Liu, Q. Li, W. Saito, and Y. Zhang, IEEE Trans. Power Electron. 38, 435 (2022).

- 74) B. Wang, R. Zhang, H. Wang, Q. He, Q. Song, Q. Li, F. Udrea, and Y. Zhang, IEEE Electron Device Lett. 44, 217 (2023).

- C. Buttay, H.-Y. Wong, B. Wang, M. Xiao, C. Dimarino, and Y. Zhang, Microelectron, Reliab, 114, 113743 (2020).

- 76) Q. Song, R. Zhang, J. P. Kozak, J. Liu, Q. Li, and Y. Zhang, IEEE Trans. Power Electron. 37, 4148 (2021).

- 77) R. Zhang, J. Kozak, Q. Song, M. Xiao, J. Liu, and Y. Zhang, 2020 IEEE Int. Electron Devices Meet., 10.1109/IEDM13553.2020.9371904.

- 78) J. P. Kozak, R. Zhang, Q. Song, J. Liu, W. Saito, and Y. Zhang, IEEE Electron Device Lett. 42, 505 (2021).

- 79) A. Lu, A. Elwailly, Y. Zhang, and H. Y. Wong, ECS J. Solid State Sci. Technol. 11, 115001 (2022).

- 80) W. Li, K. Nomoto, Z. Hu, T. Nakamura, D. Jena, and H. Xing, IEEE Int. Electron Devices Meet. 2019, 12.4 (2019).

- 81) Z. Hu, K. Nomoto, W. Li, N. Tanen, K. Sasaki, A. Kuramata, T. Nakamura, D. Jena, and H. G. Xing, IEEE Electron Device Lett. 39, 869 (2018).

- 82) M. Xiao, X. Gao, T. Palacios, and Y. Zhang, Appl. Phys. Lett. 114, 163503 (2019).

- 83) Z. Hu et al., Appl. Phys. Lett. 113, 122103 (2018).

- 84) M. Xiao, T. Palacios, and Y. Zhang, IEEE Trans. Electron Devices 66, 3903 (2019).

- 85) H. Wang, M. Xiao, K. Sheng, T. Palacios, and Y. Zhang, IEEE J. Emerg. Sel. Topics Power Electron. 9, 2235 (2020).

- 86) B. Wang, M. Xiao, J. Spencer, Y. Qin, K. Sasaki, M. J. Tadjer, and Y. Zhang, IEEE Electron Device Lett. 44, 221 (2023).