## Article

## Extraordinary tunnel electroresistance in layer-by-layer engineered van der Waals ferroelectric tunnel junctions

Conventional ferroelectric tunnel junctions (FTJs) comprising metal/oxide heterostructures suffer from a relatively low tunneling electroresistance (TER; usually  $<10^6$ ) due to the unavoidable defect states and interfacial states. Here, we constructed van der Waals FTJs consisting of 2D ferroelectrics  $\text{CuInP}_2\text{S}_6$  and 2D electronic materials (e.g., graphene and  $\text{MoS}_2$ ) and demonstrated a record-high TER of  $>10^{10}$  at room temperature. We also demonstrated an unprecedented layer-by-layer engineering of giant TER, largely strengthening the ability to manipulate electrons' tunneling behaviors for advanced tunneling devices.

**Benchmark**

First qualification/assessment of material properties and/or performance

Qinqin Wang, Ti Xie, Nicholas A. Blumenschein, ..., Jian-Ping Wang, Adam L. Friedman, Cheng Gong

gongc@umd.edu

**Highlights**

Demonstrated van der Waals (vdW) ferroelectric tunnel junctions (FTJs)

Achieved layer-by-layer engineering of tunneling electroresistance (TER) of  $>10^{10}$

Enhanced TER by 10 $\times$  via adding monolayer  $\text{MoS}_2$  or  $\text{WSe}_2$  into Cr/  $\text{CuInP}_2\text{S}_6$ /graphene FTJs

Demonstrated the gate tunability of the on-state tunneling current in vdW FTJs

## Article

# Extraordinary tunnel electroresistance in layer-by-layer engineered van der Waals ferroelectric tunnel junctions

Qinqin Wang,<sup>1,11</sup> Ti Xie,<sup>1,11</sup> Nicholas A. Blumenschein,<sup>2,11</sup> Zhihao Song,<sup>1,11</sup> Jimmy C. Kotsakidis,<sup>2</sup> Aubrey T. Hanbicki,<sup>2</sup> Michael A. Susner,<sup>3</sup> Benjamin S. Conner,<sup>4,5</sup> Qishuo Tan,<sup>6</sup> Seng Huat Lee,<sup>7</sup> Zhiqiang Mao,<sup>7</sup> Xi Ling,<sup>6,8,9</sup> Tony Low,<sup>10</sup> Jian-Ping Wang,<sup>10</sup> Adam L. Friedman,<sup>2</sup> and Cheng Gong<sup>1,12,\*</sup>

## SUMMARY

The ability to engineer potential profiles of multilayered materials is critical for designing high-performance tunneling devices such as ferroelectric tunnel junctions (FTJs). FTJs comprise asymmetric electrodes and a ferroelectric spacer, promising semiconductor-platform-compatible logic and memory devices. However, traditional FTJs consist of metal/oxide/metal multilayered structures with unavoidable defects and interfacial trap states, which often cause compromised tunneling electroresistance (TER). Here, we constructed van der Waals (vdW) FTJs by a layered ferroelectric  $\text{CuInP}_2\text{S}_6$  (CIPS) and graphene. Owing to the gigantic ferroelectric modulation of the chemical potentials in graphene by as large as  $\sim 1$  eV, we demonstrated a giant TER of  $10^9$ . While inserting just a monolayer  $\text{MoS}_2$  between CIPS/graphene, the off state is further suppressed, leading to  $>10^{10}$  TER. Our discovery opens a new solid-state paradigm where potential profiles can be unprecedently engineered in a layer-by-layer fashion, fundamentally strengthening the ability to manipulate electrons' tunneling behaviors and design advanced tunneling devices.

## INTRODUCTION

Among all the bizarre phenomena governed by quantum mechanics, the tunneling behavior is clearly beyond any classical theory's comprehension when it comes to the penetration of matter waves and the transmission of particles through a high potential barrier—that is, the classically forbidden region.<sup>1–3</sup> Fundamentally differing from diffusive transport, electrons' quantum tunneling through the classically forbidden region leads to a wide spectrum of remarkable phenomena such as Klein tunneling and pivotal devices such as magnetic and ferroelectric tunnel junctions. Quantum tunneling efficiency sensitively depends on the details of the potential barriers including heights and widths.<sup>4,5</sup> Given such a dependence is an exponential function, the tunneling can be turned on and off with stark contrast, thereby leading to the development of a broad range of important devices such as nonvolatile memories and steep-slope tunneling field-effect transistors.<sup>6–9</sup>

When ferroelectric layers are implemented between a pair of asymmetric electrodes, the tunneling transmission can be toggled with ferroelectric polarizations because the relative potential files are altered by the opposite electric dipoles, leading to a

## PROGRESS AND POTENTIAL

Ferroelectric tunnel junctions (FTJs) promise electrically switchable memories, sensors, and logic devices. However, traditional FTJs comprising metal/oxide heterostructures only exhibit modest tunneling electroresistance (TER; usually  $<10^6$ ), which is limited by defect states and interface trap states. Here, we demonstrated an emerging class of FTJs by employing 2D van der Waals (vdW) ferroelectrics and 2D electronic materials (e.g., graphene and  $\text{MoS}_2$ ). A giant TER of  $>10^{10}$  is achieved due to the gigantic ferroelectric modulation of band alignments of vdW stacks. In our FTJ multilayered structures, inserting a monolayer  $\text{MoS}_2$  or  $\text{WSe}_2$  in between ferroelectrics/graphene effectively enhances TER by ten times. Our discovery of the giant TER in vdW FTJs opens up a new solid-state paradigm in which electrons' potential profiles can be tailored in an unprecedented layer-by-layer fashion, enhancing the ability to control electrons' tunneling behaviors for emerging tunneling devices.

tunneling resistance contrast defined as tunneling electroresistance (TER) of a ferroelectric tunnel junction (FTJ).<sup>6,10–12</sup> However, in practical multilayered material systems such as metal-oxide-metal trilayer structures, defect states and interfacial trap states are inevitable, sometimes entangled with metal-induced gap states<sup>13</sup> and the associated Fermi-level pinning. The defect states complicate the intermediate tunneling channels and thus tend to deteriorate the TER, and Fermi-level pinning sets roadblocks for the efficient ferroelectric alternation of the relative potential profiles, suppressing the TER.<sup>14–16</sup>

The recently emerged two-dimensional (2D) layered van der Waals (vdW) materials, and in particular the vdW ferroelectrics (e.g., CuInP<sub>2</sub>S<sub>6</sub> [CIPS] and In<sub>2</sub>Se<sub>3</sub>),<sup>17,18</sup> promise a giant TER owing to the negligible defects, absence of interfacial states in vdW heterojunctions, and the easy tunability of the chemical potentials of 2D materials.<sup>19–24</sup> The high crystallinity of 2D vdW materials retains at the atomic level and even at the wafer scale, which holds unprecedented prospects for next-generation high-performance, energy-efficient FTJs considering that the ultrathin, defect-free ferroelectrics can allow low-voltage writing operations. Here, we constructed the vdW heterostructure-based FTJs primarily consisting of 2D ferroelectric CIPS and 2D electronic materials (i.e., graphene, MoS<sub>2</sub>, and WSe<sub>2</sub>) and demonstrated a record-high TER of  $>10^{10}$  at room temperature. This giant TER arises from the gigantic ferroelectric modulation of the tunneling barrier height and the band positions of 2D electronic materials. Remarkably, we achieved an order-of-magnitude-enhanced TER in Cr/CIPS/graphene (CrCG) tunnel junctions by simply adding a monolayer MoS<sub>2</sub> or WSe<sub>2</sub> in between CIPS and graphene. Our discovery of the giant TER in vdW FTJs and the demonstration of the effectiveness of the layer-by-layer engineering of FTJs open the door to an emerging class of vdW heterostructures for studying fundamental tunneling physics and exploring tunneling devices such as nonvolatile memories, logics, and logic-in-memory technologies.

## RESULTS AND DISCUSSION

### Device structures and band diagrams for CrCG FTJs

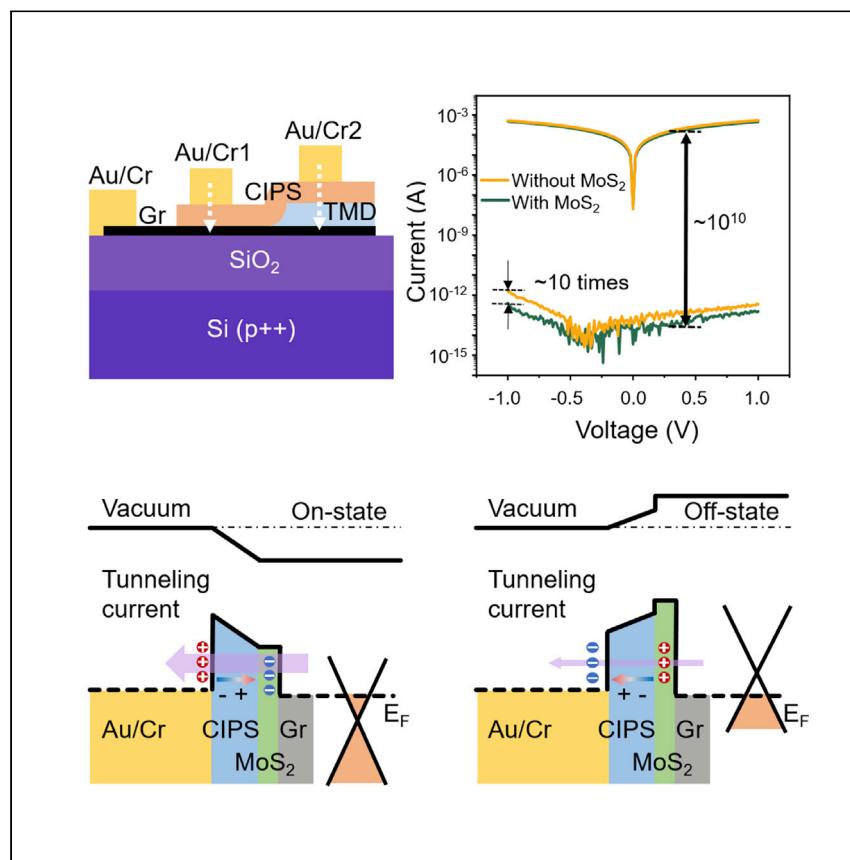

Figures 1A and 1B illustrate the Au/Cr/CIPS/graphene multilayer stack of FTJ with CIPS polarized oppositely. Under opposite polarizations, the positions of Cu<sup>+</sup> ions (red balls) differ in vertical positions: for the on state, Cu<sup>+</sup> ions are pushed by the positive electric field toward the CIPS/graphene interface, and for the off state, Cu<sup>+</sup> ions are dragged away from the CIPS/graphene interface. Figure 1C shows a representative optical image of the core heterostructure of CIPS/graphene fabricated by mechanical exfoliation and dry-transfer process. The thin graphene flake is covered by a CIPS flake with two regions of different thicknesses. Specifically, Figure 1F shows the Raman spectra of the exfoliated CIPS and graphene thin flakes, measured by an excitation laser of 532 nm wavelength at room temperature. The intensities of the 2D band (2,685 cm<sup>-1</sup>) and the G band (1,580 cm<sup>-1</sup>) of the graphene flake are comparable, suggesting that the graphene consists of two atomic layers.<sup>25</sup> As for CIPS, the vibration of anion (P<sub>2</sub>S<sub>6</sub><sup>4-</sup>) corresponds to the peak at  $\sim$ 100 cm<sup>-1</sup>, and the S-P-S vibration corresponds to the peak at 262 cm<sup>-1</sup>.<sup>26</sup> Cu<sup>+</sup> ions and P-P stretching are responsible for the peaks located at 316 and 373 cm<sup>-1</sup>, respectively.<sup>26–28</sup> These well-defined Raman peaks agree with the previous work on high-quality CIPS crystals, indicating the high crystalline quality of our CIPS flake with low defect density, which is critical for achieving a very large TER. The thickness of the CIPS flake of the thinner region in Figure 1C is  $\sim$ 3.5 nm, as estimated by optical contrast first and confirmed by atomic force microscopy (AFM) measurement (Figure S1).

<sup>1</sup>Department of Electrical and Computer Engineering and Quantum Technology Center, University of Maryland, College Park, MD 20742, USA

<sup>2</sup>Laboratory for Physical Sciences, College Park, MD 20740, USA

<sup>3</sup>Materials and Manufacturing Directorate, Air Force Research Laboratory, 2179 12<sup>th</sup> Street, Wright-Patterson Air Force Base, OH 45433, USA

<sup>4</sup>Sensors Directorate, Air Force Research Laboratory, 2241 Avionics Circle, Wright-Patterson Air Force Base, OH 45433, USA

<sup>5</sup>National Research Council, 500 Fifth St. N.W., Washington DC 20001, USA

<sup>6</sup>Department of Chemistry, Boston University, Boston, MA 02215, USA

<sup>7</sup>Department of Physics, Pennsylvania State University, University Park, PA 16801, USA

<sup>8</sup>Division of Materials Science and Engineering, Boston University, Boston, MA 02215, USA

<sup>9</sup>The Photonics Center, Boston University, Boston, MA 02215, USA

<sup>10</sup>Department of Electrical and Computer Engineering, University of Minnesota, Minneapolis, MN 55455, USA

<sup>11</sup>These authors contributed equally

<sup>12</sup>Lead contact

\*Correspondence: gongc@umd.edu

<https://doi.org/10.1016/j.matt.2022.10.014>

**Figure 1. The device structures and band diagrams for the on state and off state of the CrCG tunneling device**

(A) Schematic of the CrCG tunneling device in on state.

(B) Schematic of the CrCG tunneling device in off state. The built-in polarization fields in the CIPS are indicated by the blue-to-red arrows.

(C) Optical image of the fabricated CIPS/graphene heterostructure on a 260-nm-thick SiO<sub>2</sub>/Si chip. The thin graphene and CIPS flakes are circled by white and black dashed lines, respectively. Scale bar, 10  $\mu$ m.

(D) Band diagram for the on-state FTJ.

(E) Band diagram for the off-state FTJ. The built-in polarization fields in the CIPS are indicated by the blue-to-red arrows, and the tunneling currents are indicated by the purple arrows.

(F) Corresponding Raman spectra of graphene (blue) and CIPS (red) of the heterostructure shown in (C), indicating the high crystalline quality of these vdW flakes. The comparable peak intensities of the 2D and G peaks in graphene suggest it is a bilayer graphene.<sup>25</sup> The CIPS thickness is estimated to be 3.5 nm by atomic force microscopy (AFM) measurement, as shown in Figure S1. The thinness of the CIPS flake agrees with its shallow optical contrast<sup>6</sup> and sizable on-state tunneling current.

The ferroelectric polarization with built-in electric field can cause the effective modulation of the energy levels in graphene and the height of the tunneling barrier. Specifically, the positive polarization (pointing through CIPS toward the CIPS/graphene interface) causes the lowering of energy levels in both CIPS and graphene along the CIPS-graphene direction, as illustrated in Figure 1D. Conversely, the negative polarization gradually lifts up the energy levels of CIPS and graphene along the CIPS-graphene direction, as illustrated by Figure 1E. There is a fundamental difference between the vdW heterostructure and the oxide/metal heterojunctions in traditional FTJs. It has been well known that the metal/insulator heterojunctions easily produce mid-gap states due to the evanescent wavefunction of metals decaying into the insulators, which produces the gap states that potentially pin the Fermi level.<sup>13</sup> The mid-gap states themselves complicate the tunneling channels that often cause the compromised TER, and Fermi-level pinning largely undermines the effectiveness of the ferroelectric modulation of the band alignments across the stacks. In stark contrast, CIPS/graphene heterojunctions are free from defects and Fermi-level pinning and can thus allow the effective ferroelectric modulation of chemical potentials in graphene by as large as  $\sim$ 1 eV (see density functional theory [DFT] calculation results in Note S1 and Figures S2 and S3)<sup>6</sup> and thus the effective ferroelectric toggling between two contrasting band alignments (Figures 1D and 1E), potentially leading to a giant TER.

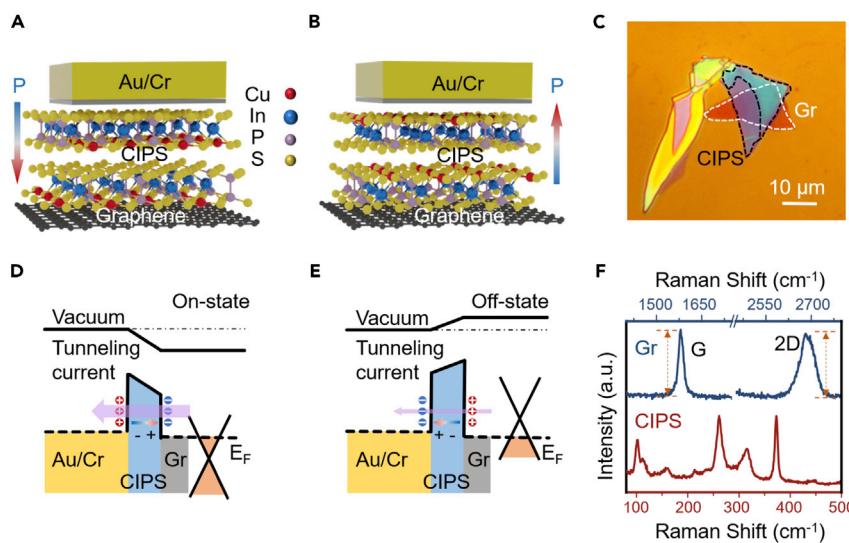

**Figure 2. The device structures and current-voltage characteristics of the CrCG and CrCMG tunneling devices**

(A) Schematic of the CrCG tunneling device. The ultrathin CIPS flake serves as the tunneling layer here.

(B) Optical image of a CrCG tunneling device with a top electrode (TE) and bottom electrode (BE). Areas of graphene and CIPS are circled by white and black dashed lines, respectively. Scale bar, 10  $\mu$ m.

(C) Current-voltage characteristics of the on (red) and off (blue) states of the CrCG tunneling device. TER is measured using -0.4 V reading voltage.

(D) Schematic of the CrCMG tunneling device.

(E) Optical image of the CrCMG tunneling device, showing three sub-devices with three different TEs, TE1 (CrCMG), TE2 (CrCMG), and TE3 (CrCG), sharing the common BE. Areas of graphene, MoS<sub>2</sub>, and CIPS are circled by white, red, and black dashed lines, respectively. Scale bar, 20  $\mu$ m.

(F) Current-voltage characteristics of the CrCMG tunneling device with TE1. TER is measured using -0.4 V reading voltage.

### Device structures and electrical characteristics of CrCG and Cr/CIPS/MoS<sub>2</sub>/graphene (CrCMG) FTJs

We fabricated and electrically characterized CrCG tunneling devices. Figure 2A is the schematic of the CrCG tunneling device structure, where a thin CIPS flake serves as the tunneling layer and the bottom and top electrodes are graphene and Cr, respectively. Figure 2B shows a representative optical image of the CrCG tunneling device. As discussed in detail later, we apply a pulse voltage to flip the ferroelectric polarization. After the writing operation, we sweep the voltage and measure the tunneling current. Both on- and off-state current-voltage characteristics displayed in Figure 2C have typical tunneling features with a slight asymmetry between positive and negative bias voltages, which is caused by the asymmetric device structure (i.e., top and bottom electrodes adopt different metals). Under the -0.4 V reading voltage, the on-state current and off-state current of this device are  $2.5 \times 10^{-4}$  and  $1.1 \times 10^{-13}$  A, respectively, leading to a gigantic on/off ratio of  $2.2 \times 10^9$ , which is three orders of magnitude higher than the maximum TER reported in conventional FTJs (primarily using oxide ferroelectrics).<sup>6,29,30</sup> To the best of our knowledge, this is the record-high TER in FTJs at room temperature reported to date.

The vdW heterojunctions not only provide unique platforms that could enable a giant TER but also open up unprecedented opportunities to engineer band alignment in a layer-by-layer fashion. Here, we inserted monolayer transition metal

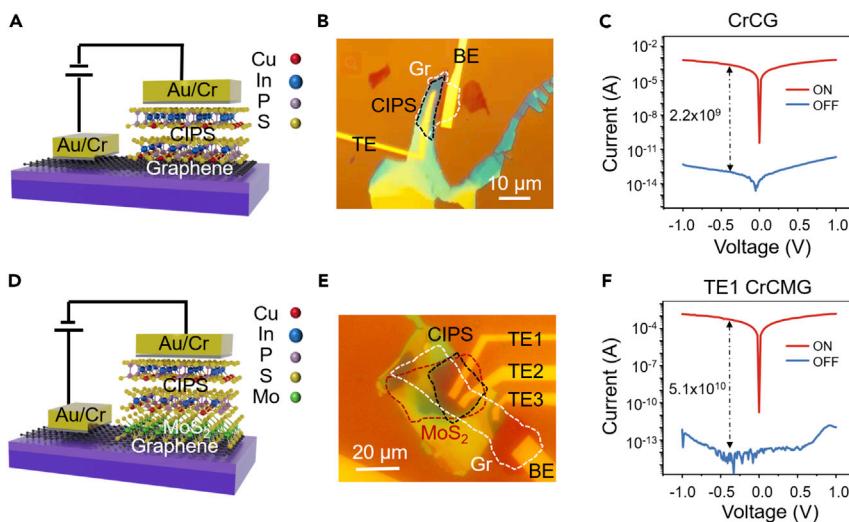

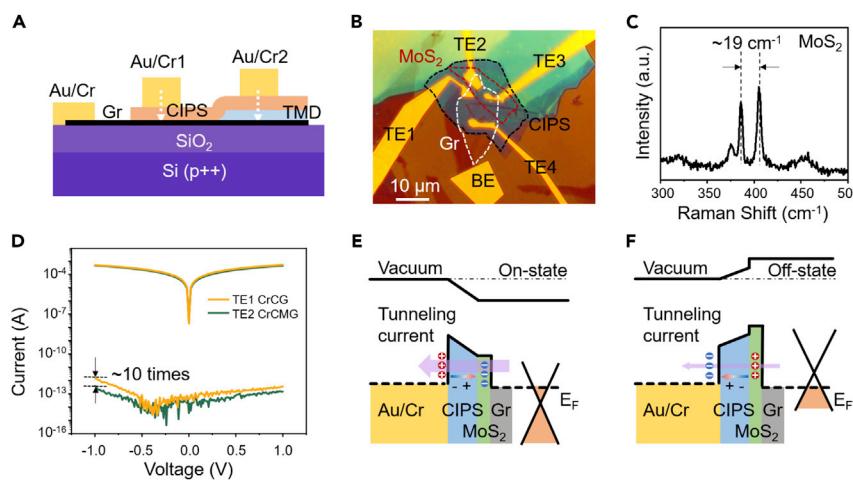

**Figure 3. Layer engineering of the TER in CrCG tunneling device by inserting a monolayer MoS<sub>2</sub> in between CIPS/graphene**

(A) Schematic of the device structure. Au/Cr1 and Au/Cr2 refer to TE1 (CrCG) and TE2 (CrCMG) in the optical image in (B).

(B) Optical image of the CrCG and CrCMG tunnel junctions. There is a monolayer MoS<sub>2</sub> flake under the TEs labeled with TE2 and TE3, while the graphene directly contacts the top CIPS under the TEs labeled with TE1 and TE4. Graphene, MoS<sub>2</sub>, and CIPS are circled by white, red, and black dashed lines, respectively. Scale bar, 10 μm.

(C) Raman spectrum of the MoS<sub>2</sub> in the device shown in (B). The distance between two peaks is ~19 cm<sup>-1</sup>, demonstrating that the MoS<sub>2</sub> flake is monolayer.<sup>31,32</sup>

(D) Current-voltage characteristics of the CrCG and CrCMG tunnel junctions. The largest difference between the two off-state currents is around 10 times.

(E) Band diagram for the CrCMG tunnel junction in on state.

(F) Band diagram of the CrCMG tunnel junction in off state. In (E) and (F), the built-in polarization fields in the CIPS are indicated by the blue-to-red arrows, and the tunneling currents are indicated by the purple arrows. The difference between the vacuum levels of MoS<sub>2</sub> and graphene is not the focus and thus is not specified in the illustrations in (E) and (F).

dichalcogenides (TMDs) in these tunnel junctions to further tune the band alignments. Figure 2D shows the schematic of the CrCMG tunneling device, and Figure 2E shows the optical image of a fabricated CrCMG device. Remarkably, in the CrCMG device, we observed an even higher TER of  $5.1 \times 10^{10}$  (Figure 2F). This device exhibits a very low off-state current of  $1.1 \times 10^{-14}$  A, while it can reach a  $5.6 \times 10^{-4}$  A on-state current, measured by the reading voltage of  $-0.4$  V. Compared with the CrCG results shown in Figure 2C, it appears that the monolayer MoS<sub>2</sub> promotes the tunneling device with one-order-of-magnitude-higher TER.

#### Layer engineering of the TER in vdW FTJs

The giant TER of  $>10^{10}$  achieved in CrCMG tunnel junctions is remarkable not only because of the giant TER itself but also because it indicates a promising prospect of layer-by-layer engineering of the band alignments and thus the resultant fine design and engineering of TER. To confirm that our experimentally observed one-order-of-magnitude enhancement in the CrCMG device with respect to the CrCG device is not because of sample variance but indeed is caused by the presence of the monolayer MoS<sub>2</sub>, we designed the control experiments based on two directly comparative devices, between which the only difference is the monolayer MoS<sub>2</sub>. As shown in Figure 3A, the CrCG and CrCMG devices share the same graphene flake and the same uniform CIPS flake (see Figure S4 for details of the fabrication process). By doing so, the thickness of graphene (and also CIPS) in these two types of devices is identical. Figure 3B presents the optical image of the fabricated devices. There are four

devices on this chip, sharing the same bottom electrode labeled as BE, and there is a monolayer MoS<sub>2</sub> flake under the top electrodes labeled with top electrode 2 (TE2) and TE3 while the graphene directly contacts the top CIPS under the TEs labeled with TE1 and TE4. As shown in [Figure 3C](#), the Raman E<sub>2g</sub> and A<sub>1g</sub> peaks of MoS<sub>2</sub> are located at 385 and 404 cm<sup>-1</sup>, respectively, with the peak frequency separation 19 cm<sup>-1</sup>, confirming it is a monolayer MoS<sub>2</sub>.<sup>31,32</sup>

[Figure 3D](#) shows the current-voltage characteristics of the CrCG and CrCMG tunnel junctions. The on-state currents of these two devices are similar, while the CrCMG tunnel junction exhibits a one-order-of-magnitude-lower off-state current than the CrCG tunnel junction, which causes a higher TER in the CrCMG tunnel junction. Band diagrams of the on and off states of the CrCMG tunnel junction are shown schematically in [Figures 3E](#) and [3F](#) (see [Note S2](#) and [Figures S5–S7](#) for additional details), based on the calculated band alignment of CIPS/MoS<sub>2</sub> by DFT. As shown in [Figure 3E](#), for the on state, the conduction band minimum (CBM) of MoS<sub>2</sub> is close to the CBM of CIPS. The positive polarization in the on state tends to n-type dope MoS<sub>2</sub>. Given that freshly exfoliated MoS<sub>2</sub> typically exhibits n-type behavior, the positive polarization will keep MoS<sub>2</sub> n-type doped. Therefore, in this on state, the monolayer MoS<sub>2</sub> serves as a thin conductive material in this structure and will not have obvious effects on the on-state tunneling currents. In stark contrast, for the off state, the CBM of MoS<sub>2</sub> is lifted higher than the CBM of CIPS. In other words, the negative polarization tends to deplete the originally n-type doped MoS<sub>2</sub>, making it more intrinsic (i.e., more insulating). In this scenario, the MoS<sub>2</sub> serves as an insulating layer to effectively increase the width of the barrier. The band diagram in [Figure 3F](#) implies that the presence of MoS<sub>2</sub> with higher CBM than the CBM of CIPS increases the tunneling barrier height as well. Thus, in the off state, the monolayer MoS<sub>2</sub> will effectively block the electron tunneling, leading to the further suppressed off-state current.

The effective suppression of the off-state current by one order of magnitude through adding a monolayer MoS<sub>2</sub> highlights the effective strategy of layer-by-layer engineering of the potential profiles in the tunneling pathway. As an important control experiment, we decide to insert a monolayer WSe<sub>2</sub> in the CrCG device. The reason for choosing WSe<sub>2</sub> is because of its contrasting property from MoS<sub>2</sub>: the as-exfoliated MoS<sub>2</sub> is typically n-type doped, while the as-exfoliated WSe<sub>2</sub> is typically p-type doped. The p-type doped WSe<sub>2</sub> has a large work function, and its valence band can directly serve to receive the electrons that tunnel through CIPS. In other words, WSe<sub>2</sub> in the p-type doping region can serve as the conductive electrode to receive the tunneling electrons. Note that the relatively flat band of the covalently bonded semiconductor WSe<sub>2</sub> has a much larger density of states than graphene, thereby potentially allowing a higher tunneling transmission than graphene.

To confirm this scenario, we fabricated the devices in a directly comparative manner. [Figure 4A](#) shows the optical image of the Cr/CIPS/WSe<sub>2</sub>/graphene (CrCWG) tunneling device, in which the regions surrounded by the blue and white dashed lines represent the monolayer WSe<sub>2</sub> and the few-layer graphene underneath, respectively. Device 1 under TE1 is the CrCWG structure, while device 2 under TE2 is the CrCG structure. Again, between these two devices, the only difference is the presence and the absence of the monolayer WSe<sub>2</sub>. [Figure 4B](#) shows the well-defined Raman peaks of WSe<sub>2</sub> (e.g., the E<sub>2g</sub> mode of WSe<sub>2</sub> at 244 cm<sup>-1</sup>), and the strong photoluminescence peak at the energy ~1.66 eV demonstrates the monolayer nature of the WSe<sub>2</sub> flake.<sup>33,34</sup>

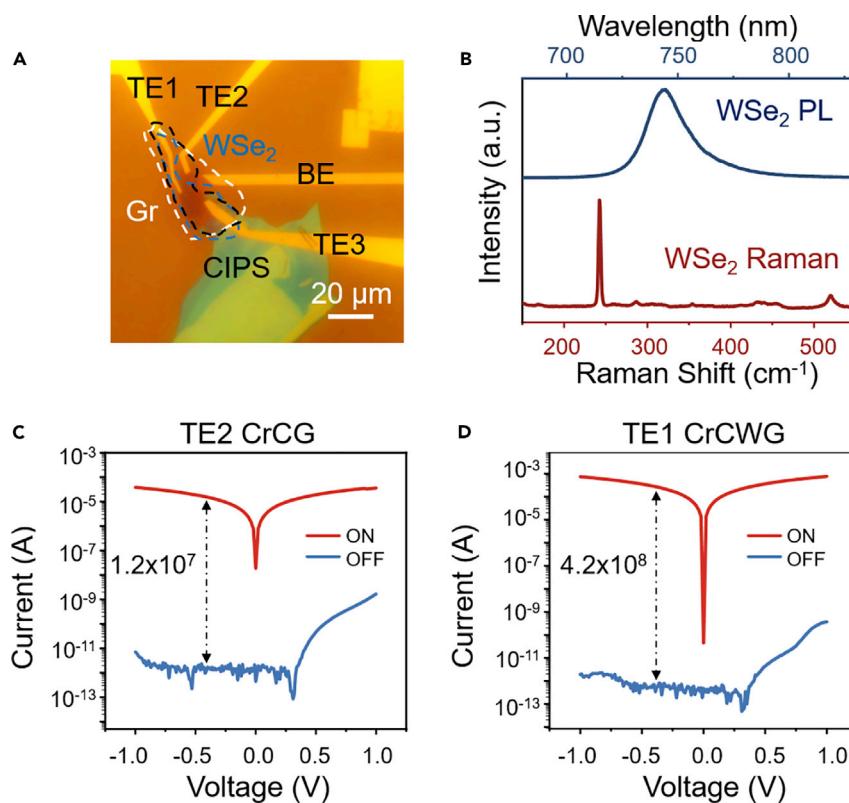

**Figure 4. Layer engineering of the TER in CrCG tunneling device by inserting a monolayer WSe<sub>2</sub> in between CIPS/graphene**

(A) Optical image of the CrCWG tunneling device. There is a monolayer WSe<sub>2</sub> flake under the TEs labeled with TE1 and TE3, while the graphene directly contacts the top CIPS under the TE labeled with TE2. Graphene, WSe<sub>2</sub>, and CIPS are circled by white, blue, and black dashed lines, respectively. Scale bar, 20 μm.

(B) Raman and photoluminescence (PL) spectra of the monolayer WSe<sub>2</sub>.

(C) Current-voltage characteristics of the CrCG tunneling device with TE2, showing an on/off ratio of  $1.2 \times 10^7$  at -0.4 V reading voltage.

(D) Current-voltage characteristics of the CrCWG tunneling device with TE1, showing an on/off ratio of  $4.2 \times 10^8$  at -0.4 V reading voltage.

Indeed, we experimentally observed the one-order-of-magnitude-enhanced TER with the one-order-of-magnitude-enhanced on-state current in the CrCWG device with respect to the CrCG device. Figure 4C shows the current-voltage characteristics of the CrCG tunneling structure with TE2, exhibiting a low off-state current of  $1.2 \times 10^{-12}$  A and a high on-state current of  $1.5 \times 10^{-5}$  A with a reading voltage of -0.4 V, leading to the TER of  $1.2 \times 10^7$ . In the device with TE1, which has an additional WSe<sub>2</sub> layer in the structure, using the same reading voltage with the TE1 device, the off-state current can be as low as  $6.7 \times 10^{-13}$  A, and the on-state current can reach  $2.8 \times 10^{-4}$  A, an order of magnitude higher than the on-state current of the CrCG device (Figure 4D). Thus, a higher TER of  $4.2 \times 10^8$  is achieved with respect to the TER of  $1.2 \times 10^7$  in the CrCG device. These results clearly show that the insertion of monolayer TMDs can enhance the TER effectively. Interestingly, as discussed, the inserted MoS<sub>2</sub> enhances the TER primarily by suppressing the off-state current, while the inserted WSe<sub>2</sub> enhances the TER primarily by enhancing the on-state current. Such layer-by-layer engineering of the potential profiles opens up the new avenues to study the fundamental tunneling physics and explore novel tunneling devices for memories and logic applications.

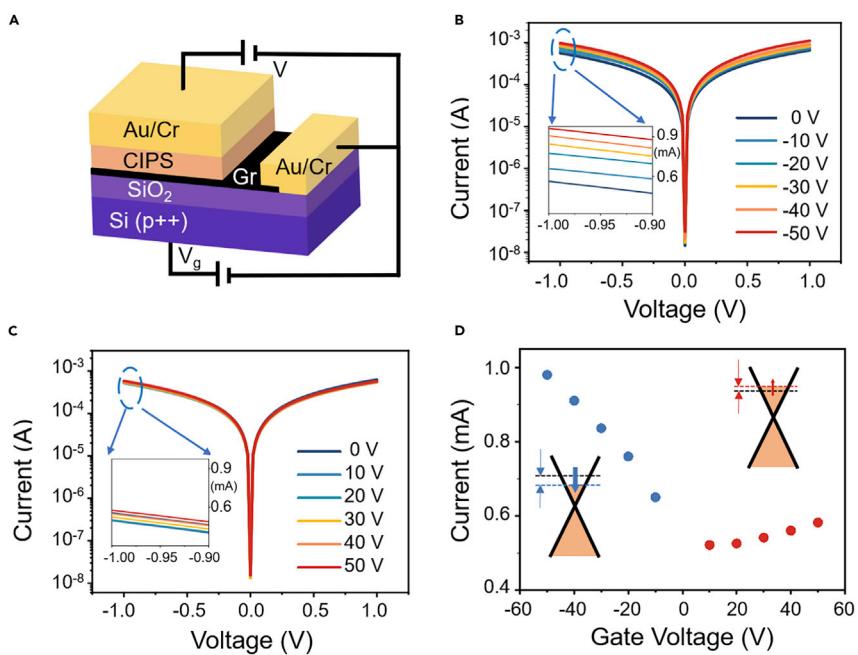

**Figure 5. Asymmetric gate tunability in CrCG tunneling junction**

(A) Schematic of the gate-tunable FTJ structure. The 260-nm-thick SiO<sub>2</sub> serves as the dielectric layer, and the bottom Si (p++) serves as the back-gate electrode.

(B and C) On-state current-voltage characteristics for FTJs under different negative (B) and positive (C) gate voltages. The difference in the on-state currents is highlighted in the inset. The on-state current increased more obviously with the varying negative gate voltages than with the varying positive gate voltages.

(D) On-state currents (with -1 V reading voltage) under different gate voltages. This asymmetric gate-tunable on-state current under positive and negative gate voltages arises from the initial n-type doping of graphene. As illustrated by the inset, when graphene is initially n-type doped, the negative voltages will move the Dirac point close to the Fermi level, but the positive voltages will move the Dirac point away from the Fermi level. The energy levels are easier to be modulated when the Dirac point is moved close to the Fermi level with respect to the scenario when the Dirac point is moved away from the Fermi level.

### Asymmetric gate tunability in CrCG FTJs

Given the remarkable tunability of 2D materials in general, we further utilize the Si substrate and SiO<sub>2</sub> dielectric to supply a back gate to tune the TER of the CrCG FTJs with the device structure shown in Figure 5A. Figures 5B and 5C show the on-state current-voltage characteristics of our FTJ devices with different positive gate voltages (Figure 5B) and negative gate voltages (Figure 5C), respectively. The insets of Figures 5B and 5C show that the on-state current increased more obviously under negative gate voltages with respect to those under positive gate voltages. Figure 5D summarizes the on-state current values under different gate voltages with a reading voltage of -1 V, confirming that the on-state current changes faster with the varying negative gate voltages than with varying positive gate voltages.

The asymmetric gate tunability of on-state currents is related to the initial doping scenario of the graphene. Specifically, when a FTJ is in on state, the Fermi level of the graphene is above the Dirac point (Figure 5D). Applying the gate voltages of the same amplitude but of opposite signs will cause the same amount of charge increase or decrease. When applying a negative voltage, Fermi level will move downward at a faster pace with respect to moving upward under a positive voltage. This is

simply because the density of states near the Dirac point is lower but the density of states away from the Dirac point is higher.

### Conclusions

In summary, we constructed vdW heterostructures based FTJs consisting of 2D ferroelectrics CIPS and 2D electronic materials (i.e., graphene and TMDs) and demonstrated a giant TER of  $>10^{10}$  at room temperature. The record-high TER arises from the giant ferroelectric modulation of the band alignments through the vdW stacks. The insertion of both monolayer MoS<sub>2</sub> and monolayer WSe<sub>2</sub> can effectively enhance the TER of CrCG tunnel junction by an order of magnitude yet with different underlying band realignment behaviors. Furthermore, the 2D vdW FTJs allow the fine gate tunability of the on-state tunneling current, which endows vdW FTJs with extra electrical controllability for enhanced functions. Our discovery of the giant TER in vdW FTJs and the demonstration of the effectiveness of the layer-by-layer engineering of FTJs open the door to the emerging class of vdW heterostructures for studying the fundamental tunneling physics and exploring tunneling devices such as nonvolatile memories, logics, and logic-in-memory devices.

## EXPERIMENTAL PROCEDURES

### Resource availability

#### Lead contact

Further information and requests for resources and reagents should be directed to and will be fulfilled by the lead contact, Cheng Gong ([gongc@umd.edu](mailto:gongc@umd.edu)).

#### Materials availability

This study did not generate new unique materials.

#### Data and code availability

Any additional information required to reanalyze the data reported in this paper is available from the [lead contact](#) upon request.

### Synthesis of CIPS crystals

We grew CIPS via a flux-based method.<sup>35</sup> First, we synthesized P<sub>2</sub>S<sub>5</sub> via reaction of the elements P (Alfa Aesar, Puratronic, 99.999%) and S (Alfa Aesar, Puratronic, 99.999%) in a stoichiometric ratio at 300°C in a sealed, thick-walled quartz ampoule. The metal elements Cu (Alfa Aesar, powder, ~100 mesh, 99.999%, reduced in H<sub>2</sub> gas at 300°C prior to reaction) and In (Alfa Aesar, ingot, 99.999%) were mixed with the flux in a molar ratio Cu:In:P<sub>2</sub>S<sub>5</sub> of 1:1:3 and placed in a 5-mL Canfield crucible set (LSP Industrial Ceramics). The crucible set, including frit and catch crucible, was sealed in quartz under partial Ar atmosphere. The sealed ampoule was then placed in a muffle furnace, heated to 650°C at 30°C/h, held at that temperature for 36 h, and then cooled to 250°C at 6°C/h. At 250°C, the sample was removed from the furnace and centrifuged to decant the P<sub>2</sub>S<sub>5</sub> flux, leaving crystals behind of a maximum size of 8 × 8 mm. We performed energy-dispersive X-ray spectroscopy (EDS) analysis and found compositions of CIPS, within error. We also used CIPS synthesized via a chemical vapor transport method<sup>6</sup> in some testing experiments.

### Device fabrication

For the Cr/CIPS/TMD/graphene FTJs, we first mechanically exfoliated thin-layer graphene on a 260-nm-thick SiO<sub>2</sub>/Si substrate. Then, monolayer TMD and thin CIPS film were exfoliated on polydimethylsiloxane (PDMS) and transferred onto the graphene flake in sequence, using the all-dry viscoelastic stamping procedure through a

transfer stage under the optical microscope. The polymethyl methacrylate (PMMA) was spin coated on the graphene/CIPS or graphene/TMD/CIPS heterostructure as photoresist and annealed in air at 120°C for 2 min. Finally, electron-beam lithography was used to lay out the TE, and the bilayer metallic electrodes (Cr/Au, 5/50 nm) were deposited by thermal evaporation (Figure S4).

### Electrical characterization

A pulse writing voltage with a period of 200 ms was used to flip the ferroelectric polarization of the tunneling devices by Keithley 4200A-SCS semiconductor parameter analyzer. Depending on the specific measurement modes, a series of sweeping voltages were applied to collect the current-voltage data or a single reading voltage (e.g., -0.4 V) was applied to record the tunneling current. To avoid the ferroelectric-paraelectric phase transition undesirably caused by the Joule heating effect arising from the tunneling current, a low duty cycle (0.5%) was used to keep the device temperature lower than the ferroelectric Curie temperature ( $T_c$ ) of CIPS (~315 K).<sup>17</sup> The pulse writing voltage was tested from a relatively low amplitude (2 V) with an increasing step of 0.2 V to avoid unwanted device damage.

### Raman spectroscopy

The measurement was based on an Andor spectrometer with a Newton 970 series camera at room temperature. The 532-nm laser was focused on the samples via a 50 $\times$  objective lens with a numerical aperture of 0.5. We used one band-pass filter to clean up the laser spectral noise and three Bragg notch filters to suppress the Rayleigh line bandwidth down to  $\sim 8$  cm $^{-1}$ . A 1,200 grooves mm $^{-1}$  grating was used to achieve a spectral resolution of 0.79 cm $^{-1}$  per pixel. The integration time was 15 s for each spectrum acquisition.

### DFT calculations

The *ab initio* calculations were performed by DFT using the Vienna Ab initio Simulation Package (VASP) code.<sup>36,37</sup> The exchange and correlation functionals were implemented by the generalized gradient approximation (GGA) of the Perdew-Burke-Ernzerhof (PBE) functional. The monolayer-MoS<sub>2</sub>/bilayer-CIPS heterostructure was constructed with a vacuum layer larger than 15 Å, in order to avoid interactions between adjacent super cells. The lattice constants for pristine MoS<sub>2</sub> and CIPS were 3.16 and 6.05 Å, respectively. Here, we fixed the lattice constant of CIPS and deposited the 2  $\times$  2 MoS<sub>2</sub> supercell on the bilayer CIPS unit cell. The lattice mismatch was  $\sim 4.3\%$ . All structures were fully relaxed until the force converged on each atom less than 10 $^{-2}$  eV/Å, and the energy criterion was set to 10 $^{-6}$  eV. The plane-wave cutoff energy was set to 420 eV. Brillouin zone was sampled using  $\Gamma$ -centered 14  $\times$  14  $\times$  1 Monkhorst-Pack k mesh. The vdW interaction was corrected by the DFT-D3 Grimme method.

### SUPPLEMENTAL INFORMATION

Supplemental information can be found online at <https://doi.org/10.1016/j.matt.2022.10.014>.

### ACKNOWLEDGMENTS

C.G. acknowledges the grant support from Air Force Office of Scientific Research under the award number FA9550-22-1-0349, Naval Air Warfare Center Aircraft Division under the award number N00421-22-1-0001, and Army Research Laboratory under the cooperative agreement number W911NF-19-2-0181. J.-P.W. acknowledges the support of the Robert F. Hartmann Endowed Chair Professorship. M.A.S. and B.S.C.

acknowledge support through the United States Air Force Office of Scientific Research (AFOSR) LRIR 18RQCOR100 and AOARD-MOST grant number F4GGA21207H002. B.S.C. further acknowledges the National Research Council Senior Fellowship award. Financial support for WSe<sub>2</sub> sample preparation was provided by the National Science Foundation through the Penn State 2D Crystal Consortium-Materials Innovation Platform (2DCC-MIP) under National Science Foundation cooperative agreement DMR-2039351. Q.W. acknowledges DFT support from Dr. Qirui Cui.

### AUTHOR CONTRIBUTIONS

C.G. conceived and supervised the project. Q.W., T.X., and Z.S. fabricated tunneling devices and carried out the Raman characterizations under the supervision of C.G. Q.W., T.X., and N.A.B. conducted the electrical measurements with assistance from A.T.H., under the supervision of C.G. and A.L.F. J.C.K. carried out AFM measurements under the supervision of A.L.F. M.A.S. and B.S.C. synthesized CIPS crystals via a flux-based method. Q.T. and X.L. synthesized CIPS crystals via a chemical vapor transport method. S.H.L. and Z.M. synthesized WSe<sub>2</sub> crystals. J.-P.W. and T.L. participated in the development of the device concept of vdW FTJs. Q.W. and C.G. analyzed the data. Q.W. and C.G. wrote the manuscript with assistance from Z.S. All authors commented on the manuscript.

### DECLARATION OF INTERESTS

The authors declare no competing interests.

Received: June 13, 2022

Revised: July 29, 2022

Accepted: October 17, 2022

Published: November 9, 2022

### REFERENCES

1. Ramos, R., Spierings, D., Racicot, I., and Steinberg, A.M. (2020). Measurement of the time spent by a tunnelling atom within the barrier region. *Nature* 583, 529–532. <https://doi.org/10.1038/s41586-020-2490-7>.

2. Katsnelson, M.I. (2007). Graphene: carbon in two dimensions. *Mater. Today* 10, 20–27. [https://doi.org/10.1016/S1369-7021\(06\)71788-6](https://doi.org/10.1016/S1369-7021(06)71788-6).

3. Satya Sainadh, U., Sang, R.T., and Litvinyuk, I.V. (2020). Attoclock and the quest for tunnelling time in strong-field physics. *J. Phys. Photonics* 2, 042002. <https://doi.org/10.1088/2515-7647/aba009>.

4. Das, S., Wang, B., Paudel, T.R., Park, S.M., Tsybaly, E.Y., Chen, L.-Q., Lee, D., and Noh, T.W. (2019). Enhanced flexoelectricity at reduced dimensions revealed by mechanically tunable quantum tunnelling. *Nat. Commun.* 10, 537. <https://doi.org/10.1038/s41467-019-10842-0>.

5. Qin, Q.H., Äkäslompolo, L., Tuomisto, N., Yao, L., Majumdar, S., Vijayakumar, J., Casiraghi, A., Inkinen, S., Chen, B., Zugaramurdi, A., et al. (2016). Resistive switching in all-oxide ferroelectric tunnel junctions with ionic interfaces. *Adv. Mater.* 28, 6852–6859. <https://doi.org/10.1002/adma.201504519>.

6. Wu, J., Chen, H.-Y., Yang, N., Cao, J., Yan, X., Liu, F., Sun, Q., Ling, X., Guo, J., and Wang, H. (2020). High tunnelling electroresistance in a ferroelectric van der Waals heterojunction via giant barrier height modulation. *Nat. Electron.* 3, 466–472. <https://doi.org/10.1038/s41928-020-0441-9>.

7. Wang, Q., Xie, T., Blumenschein, N.A., Song, Z., Hanbicki, A.T., Susner, M.A., Conner, B.S., Low, T., Wang, J.-P., Friedman, A.L., et al. (2022). Gate-tunable giant tunnelling electroresistance in van der Waals ferroelectric tunneling junctions. *Mater. Sci. Eng., B* 283, 115829. <https://doi.org/10.1016/j.mseb.2022.115829>.

8. Kang, L., Jiang, P., Hao, H., Zhou, Y., Zheng, X., Zhang, L., and Zeng, Z. (2020). Giant tunnelling electroresistance in two-dimensional ferroelectric tunnel junctions with out-of-plane ferroelectric polarization. *Phys. Rev. B* 101, 014105. <https://doi.org/10.1103/PhysRevB.101.014105>.

9. Xi, Z., Ruan, J., Li, C., Zheng, C., Wen, Z., Dai, J., Li, A., and Wu, D. (2017). Giant tunnelling electroresistance in metal/ferroelectric/semiconductor tunnel junctions by engineering the Schottky barrier. *Nat. Commun.* 8, 15217. <https://doi.org/10.1038/ncomms15217>.

10. Luo, X., Wang, B., and Zheng, Y. (2011). Tunable tunneling electroresistance in ferroelectric tunnel junctions by mechanical loads. *ACS Nano* 5, 1649–1656. <https://doi.org/10.1021/nn1031438>.

11. Wang, X., Song, B., Tao, L.L., Wen, J., Zhang, L., Zhang, Y., Lv, Z., Tang, J., Sui, Y., Song, B., and Han, X.F. (2016). Effect of a semiconductor electrode on the tunneling electroresistance in ferroelectric tunneling junction. *Appl. Phys. Lett.* 109, 163501. <https://doi.org/10.1063/1.4965708>.

12. Shen, X.-W., Fang, Y.-W., Tian, B.-B., and Duan, C.-G. (2019). Two-dimensional ferroelectric tunnel junction: the case of monolayer In:SnSe/SnSe/Sb:SnSe Heterostructure. *ACS Appl. Electron. Mater.* 1, 1133–1140. <https://doi.org/10.1021/acsaem.9b00146>.

13. Tersoff, J. (1985). Schottky barriers and semiconductor band structures. *Phys. Rev. B Condens. Matter* 32, 6968–6971. <https://doi.org/10.1103/PhysRevB.32.6968>.

14. Luo, Z.D., Yang, M.M., Liu, Y., and Alexe, M. (2021). Emerging opportunities for 2D semiconductor/ferroelectric transistor-structure devices. *Adv. Mater.* 33, e2005620. <https://doi.org/10.1002/adma.202005620>.

15. Zhao, M., Gou, G., Ding, X., and Sun, J. (2020). An ultrathin two-dimensional vertical ferroelectric tunneling junction based on  $\text{CuInP}_2\text{S}_6$  monolayer. *Nanoscale* 12, 12522–12530. <https://doi.org/10.1039/d0nr01475c>.

16. Kang, L., Jiang, P., Cao, N., Hao, H., Zheng, X., Zhang, L., and Zeng, Z. (2019). Realizing giant tunnelling electroresistance in two-dimensional graphene/BiP ferroelectric tunnel junction. *Nanoscale* 11, 16837–16843. <https://doi.org/10.1039/c9nr01656b>.

17. Liu, F., You, L., Seyler, K.L., Li, X., Yu, P., Lin, J., Wang, X., Zhou, J., Wang, H., He, H., et al. (2016). Room-temperature ferroelectricity in  $\text{CuInP}_2\text{S}_6$  ultrathin flakes. *Nat. Commun.* 7, 12357. <https://doi.org/10.1038/ncomms12357>.

18. Ding, W., Zhu, J., Wang, Z., Gao, Y., Xiao, D., Gu, Y., Zhang, Z., and Zhu, W. (2017). Prediction of intrinsic two-dimensional ferroelectrics in  $\text{In}_2\text{Se}_3$  and other  $\text{III}_2\text{-VI}_3$  van der Waals materials. *Nat. Commun.* 8, 14956. <https://doi.org/10.1038/ncomms14956>.

19. Zhou, Y., Wu, D., Zhu, Y., Cho, Y., He, Q., Yang, X., Herrera, K., Chu, Z., Han, Y., Downer, M.C., et al. (2017). Out-of-plane piezoelectricity and ferroelectricity in layered alpha- $\text{In}_2\text{Se}_3$  nanoflakes. *Nano Lett.* 17, 5508–5513. <https://doi.org/10.1021/acs.nanolett.7b02198>.

20. Belianinov, A., He, Q., Dziaugys, A., Makrymovych, P., Eliseev, E., Borisevich, A., Morozovska, A., Banys, J., Vysotskii, Y., and Kalinin, S.V. (2015).  $\text{CuInP}_2\text{S}_6$  room temperature layered ferroelectric. *Nano Lett.* 15, 3808–3814. <https://doi.org/10.1021/acs.nanolett.5b00491>.

21. Guan, Z., Hu, H., Shen, X., Xiang, P., Zhong, N., Chu, J., and Duan, C. (2019). Recent progress in two-dimensional ferroelectric materials. *Adv. Electron. Mater.* 6, 1900818. <https://doi.org/10.1002/aelm.201900818>.

22. Jiang, X., Wang, X., Wang, X., Zhang, X., Niu, R., Deng, J., Xu, S., Lun, Y., Liu, Y., Xia, T., et al. (2022). Manipulation of current rectification in van der Waals ferroionic  $\text{CuInP}_2\text{S}_6$ . *Nat. Commun.* 13, 574. <https://doi.org/10.1038/s41467-022-28235-6>.

23. Jin, X., Zhang, Y.Y., Pantelides, S.T., and Du, S. (2020). Integration of graphene and two-dimensional ferroelectrics: properties and related functional devices. *Nanoscale Horiz.* 5, 1303–1308. <https://doi.org/10.1039/d0nh00255k>.

24. Yang, J., Zhou, J., Lu, J., Luo, Z., Yang, J., and Shen, L. (2022). Giant tunnelling electroresistance through 2D sliding ferroelectric materials. *Mater. Horiz.* 9, 1422–1430. <https://doi.org/10.1039/d2mh00080f>.

25. Kumar, V., Kumar, A., Lee, D.J., and Park, S.S. (2021). Estimation of number of graphene layers using different methods: a focused review. *Materials* 14, 4590. <https://doi.org/10.3390/ma14164590>.

26. Chen, J., Zhu, C., Cao, G., Liu, H., Bian, R., Wang, J., Li, C., Chen, J., Fu, Q., Liu, Q., et al. (2021). Mimicking neuroplasticity via ion migration in van der Waals layered copper thiophosphate. *Adv. Mater.* 34, e2104676. <https://doi.org/10.1002/adma.202104676>.

27. Si, M., Liao, P.Y., Qiu, G., Duan, Y., and Ye, P.D. (2018). Ferroelectric field-effect transistors based on  $\text{MoS}_2$  and  $\text{CuInP}_2\text{S}_6$  two-dimensional van der Waals heterostructure. *ACS Nano* 12, 6700–6705. <https://doi.org/10.1021/acsnano.8b01810>.

28. Vysotskii, Y.M., Stephanovich, V.A., Molnar, A.A., Cajipe, V.B., and Bourdon, X. (1998). Raman spectroscopy study of the ferrielectric-paraelectric transition in layered  $\text{CuInP}_2\text{S}_6$ . *Phys. Rev. B* 58, 9119–9124. <https://doi.org/10.1103/PhysRevB.58.9119>.

29. Li, J., Li, N., Ge, C., Huang, H., Sun, Y., Gao, P., He, M., Wang, C., Yang, G., and Jin, K. (2019). Giant electroresistance in ferroionic tunnel junctions. *iScience* 16, 368–377. <https://doi.org/10.1016/j.isci.2019.05.043>.

30. Poh, S.M., Tan, S.J.R., Wang, H., Song, P., Abidi, I.H., Zhao, X., Dan, J., Chen, J., Luo, Z., Pennycook, S.J., et al. (2018). Molecular-beam epitaxy of two-dimensional  $\text{In}_2\text{Se}_3$  and its giant electroresistance switching in ferroresistive memory junction. *Nano Lett.* 18, 6340–6346. <https://doi.org/10.1021/acs.nanolett.8b02688>.

31. Wang, Q., Li, N., Tang, J., Zhu, J., Zhang, Q., Jia, Q., Lu, Y., Wei, Z., Yu, H., Zhao, Y., et al. (2020). Wafer-scale highly oriented monolayer  $\text{MoS}_2$  with large domain sizes. *Nano Lett.* 20, 7193–7199. <https://doi.org/10.1021/acs.nanolett.0c02531>.

32. Lee, C., Yan, H., Brus, L.E., Heinz, T.F., Hone, J., and Ryu, S. (2010). Anomalous lattice vibrations of single- and few-layer  $\text{MoS}_2$ . *ACS Nano* 4, 2695–2700. <https://doi.org/10.1021/nn1003937>.

33. Zhao, W., Ghorannevis, Z., Chu, L., Toh, M., Kloc, C., Tan, P.-H., and Eda, G. (2013). Evolution of electronic structure in atomically thin sheets of  $\text{WS}_2$  and  $\text{WSe}_2$ . *ACS Nano* 7, 791–797. <https://doi.org/10.1021/nm305275h>.

34. Huang, J.-K., Pu, J., Hsu, C.-L., Chiu, M.-H., Juang, Z.-Y., Chang, Y.-H., Chang, W.-H., Iwasa, Y., Takenobu, T., and Li, L.-J. (2014). Large-area synthesis of highly crystalline  $\text{WSe}_2$  monolayers and device applications. *ACS Nano* 8, 923–930. <https://doi.org/10.1021/nn405719x>.

35. Chica, D.G., Iyer, A.K., Cheng, M., Ryan, K.M., Krantz, P., Laing, C., Dos Reis, R., Chandrasekhar, V., Dravid, V.P., and Kanatzidis, M.G. (2021).  $\text{P}_2\text{S}_5$  reactive flux method for the rapid synthesis of mono- and bimetallic 2D thiophosphates  $\text{M}_{2-x}\text{M}'_x\text{P}_2\text{S}_6$ . *Inorg. Chem.* 60, 3502–3513. <https://doi.org/10.1021/acs.inorgchem.0c03577>.

36. Kresse, G., and Hafner, J. (1994). Ab initio molecular-dynamics simulation of the liquid-metal-amorphous-semiconductor transition in germanium. *Phys. Rev. B Condens. Matter* 49, 14251–14269. <https://doi.org/10.1103/PhysRevB.49.14251>.

37. Kresse, G., and Joubert, D. (1999). From ultrasoft pseudopotentials to the projector augmented-wave method. *Phys. Rev. B* 59, 1758–1775. <https://doi.org/10.1103/PhysRevB.59.1758>.