# Impact of Large Gate Voltages and Ultrathin Polymer Electrolytes on Carrier Density in Electric-Double-Layer-Gated Two-Dimensional Crystal Transistors

Shubham Sukumar Awate, Brendan Mostek, Shalini Kumari, Chengye Dong, Joshua A. Robinson, Ke Xu, and Susan K. Fullerton-Shirey\*

Cite This: *ACS Appl. Mater. Interfaces* 2023, 15, 15785–15796

Read Online

ACCESS |

Metrics & More

Article Recommendations

Supporting Information

**ABSTRACT:** Electric-double-layer (EDL) gating can induce large capacitance densities ( $\sim 1\text{--}10 \mu\text{F cm}^{-2}$ ) in two-dimensional (2D) semiconductors; however, several properties of the electrolyte limit performance. One property is the electrochemical activity which limits the gate voltage ( $V_G$ ) that can be applied and therefore the maximum extent to which carriers can be modulated. A second property is electrolyte thickness, which sets the response speed of the EDL gate and therefore the time scale over which the channel can be doped. Typical thicknesses are on the order of micrometers, but thinner electrolytes (nanometers) are needed for very-large-scale-integration (VLSI) in terms of both physical thickness and the speed that accompanies scaling. In this study, finite element modeling of an EDL-gated field-effect transistor (FET) is used to self-consistently couple ion transport in the electrolyte to carrier transport in the semiconductor, in which density of states, and therefore quantum capacitance, is included. The model reveals that 50 to 65% of the applied potential drops across the semiconductor, leaving 35 to 50% to drop across the two EDLs. Accounting for the potential drop in the channel suggests that higher carrier densities can be achieved at larger applied  $V_G$  without concern for inducing electrochemical reactions. This insight is tested experimentally via Hall measurements of graphene FETs for which  $V_G$  is extended from  $\pm 3$  to  $\pm 6$  V. Doubling the gate voltage increases the sheet carrier density by an additional  $2.3 \times 10^{13} \text{ cm}^{-2}$  for electrons and  $1.4 \times 10^{13} \text{ cm}^{-2}$  for holes without inducing electrochemistry. To address the need for thickness scaling, the thickness of the solid polymer electrolyte, poly(ethylene oxide) (PEO): $\text{CsClO}_4$ , is decreased from 1  $\mu\text{m}$  to 10 nm and used to EDL gate graphene FETs. Sheet carrier density measurements on graphene Hall bars prove that the carrier densities remain constant throughout the measured thickness range (10 nm–1  $\mu\text{m}$ ). The results indicate promise for overcoming the physical and electrical limitations to VLSI while taking advantage of the ultrahigh carrier densities induced by EDL gating.

**KEYWORDS:** electric double layer, finite element modeling, polymer electrolyte, two-dimensional materials, Nernst–Planck–Poisson, drift diffusion, thin electrolyte, quantum capacitance

## INTRODUCTION

Iontronic devices use ions to control the electronic properties of semiconducting materials,<sup>1,2</sup> with large capacitance densities demonstrated in two-dimensional (2D)<sup>3</sup> and organic semiconductors<sup>4</sup> ( $\sim 1\text{--}10 \mu\text{F cm}^{-2}$ ). The mechanisms that govern iontronics can be broadly divided into two categories: electrochemical and electrostatic. Devices that rely on *electrochemistry* involve redox reactions at the electrolyte/channel interface, or inside the semiconductor, to modulate the carrier density in the channel materials.<sup>4,5</sup> These include organic electrochemical transistors (OECTs),<sup>6,7</sup> conductive-bridge memory (CBRAM),<sup>8,9</sup> electrochemical random access memory (ECRAM),<sup>10</sup> and ion intercalation devices.<sup>11–13</sup> In contrast, iontronic devices rely on *electrostatic* interactions to modulate the carrier density by forming an EDL at the

electrode/electrolyte and electrolyte/channel interfaces with no transfer of electrons (i.e., no electrochemistry). Included in this category are electric-double-layer transistors (EDLTs), which are FETs in which the gate oxide is replaced by an electrically insulating but ionically conductive electrolyte. While such a device could also undergo electrochemical reaction under sufficiently large gate voltage,<sup>11,14–16</sup> in this study we consider EDLTs as ionically gated FETs for which

Received: July 22, 2022

Accepted: February 24, 2023

Published: March 16, 2023

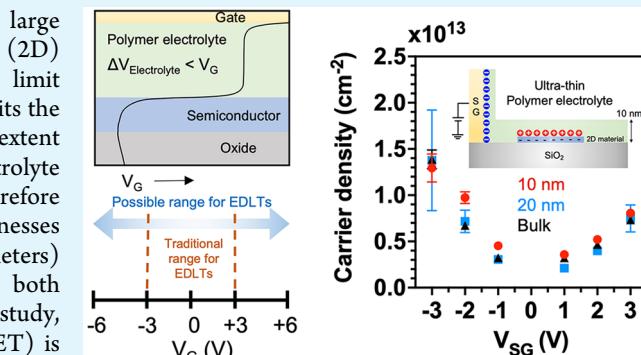

**Figure 1.** Device schematics and calculated net ion and carrier densities. EDL formation at the interfaces at (a)  $V_G > 0$  and (b)  $V_G < 0$ . Net normalized ion concentration  $(n_c - n_a)/n_b$  at the interfaces at (c)  $V_G = +3$  V and (d)  $-3$  V. Stern layers are indicated in gray at the top and bottom of the electrolyte. Sheet carrier densities and net ion densities at (e)  $V_G = +3$  V and (f)  $-3$  V.  $WSe_2$  thickness = 5 nm and  $E_{gap} = 1.25$  eV.

electrochemical reactions are absent. As Leighton et al. highlights, this tends to be true for densely packed channel materials that are nonpermeable to ions.<sup>5</sup> EDLTs and electric-double-layer capacitors (EDLCs) are widely studied for their applications as supercapacitors, sensors, flexible and printed electronics, and nonvolatile and resistive switching devices.<sup>17,18</sup> EDLTs have also been employed to explore ferromagnetism, superconductivity, metal–insulator transition and light–matter interactions in 2D layered materials, organic semiconductors, and oxide semiconductors.<sup>3,19–23</sup>

In an EDLT, when no gate voltage is applied, the cations and anions are uniformly distributed in the electrolyte. When a positive gate voltage is applied ( $V_G > 0$ ), anions drift toward the gate and cations to the semiconductor, forming an anionic EDL at the electrolyte/gate interface and cationic EDL at the electrolyte/semiconductor interface. The accumulation of cations at the semiconductor surface results in n-type doping, as shown in Figure 1a. When the polarity of the gate voltage is reversed (i.e.,  $V_G < 0$ ), the semiconductor is doped p-type, as shown in Figure 1b. The doping density in the channel is proportional to the applied gate voltage, where most of the

potential drops across the two EDLs and very little potential drops across the charge neutral bulk of the electrolyte.

The primary motivation for using EDL gating is the large capacitance density ( $\sim 1\text{--}10 \mu\text{F cm}^{-2}$ ), which is  $\sim 5\text{--}10$  times higher than the traditional high  $\kappa$  dielectrics.<sup>4,24,25</sup> Essentially, the EDL at the semiconductor surface acts as an extremely thin capacitor (thickness  $< 1$  nm), giving rise to high capacitance densities. This gating mechanism induces high sheet carrier densities ( $10^{13}\text{--}10^{14} \text{ cm}^{-2}$ ) in various organic and inorganic semiconductors.<sup>3,26</sup> EDL gating is also used in fundamental research of low-dimensional materials. For example, this technique has been effective in controlling light scattering and emission,<sup>27,28</sup> surface plasmon resonance,<sup>22,23,29</sup> and the transition temperature for superconductivity<sup>19,30,31</sup> in layered materials including graphene, 2D metals, and transition-metal dichalcogenides (TMDs).

The EDL capacitance and carrier densities in the semiconductor depend on the applied gate voltage. Because the electrolyte contains mobile ions, it can undergo electrochemical reactions when the voltage produces a field that is large enough to induce a redox reaction. Electrochemical reactions can be undesirable in EDLTs because they can

induce heteroatom intercalation or change the composition of the electrolyte—both of which would interfere with investigating the fundamental properties of a chemically well-defined material.

In metal–insulator–metal (MIM) structures, all of the applied potential drops between two metals. However, in a FET structure, the applied voltage drops across a metal–insulator–semiconductor stack where the field distribution will be different than an MIM. Nonetheless, the maximum gate voltage applied to EDLTs is typically limited to  $\pm 3$  V (i.e., electrochemical window<sup>2</sup>) as the standard reduction potentials ( $E_0$ ) for the components in the electrolyte is around 3 V (e.g.,  $E_{0,\text{Li}/\text{Li}^+}$  is  $-3.05$  V vs standard hydrogen electrode (SHE)).<sup>32–35</sup> The electrochemical window limits the maximum gate voltage that can be applied, thereby limiting the maximum extent to which carriers can be modulated. Surprisingly, there are reports of EDLTs with  $V_G$  extending to 5 V<sup>13,36</sup> and even 7 V<sup>19</sup> at room temperature, with no electrochemical signatures reported, which is 2 to 4 V beyond the commonly assumed electrochemical window. Such observations require further investigation to understand how the voltage changes with distance across the electrolyte and semiconductor in an ion-gated FET.

In addition to the performance constraints imposed by  $V_G$ , another constraint—this one impacting the speed of the EDL response—is the ionic mobility of solid polymer electrolytes, which is orders of magnitude lower than electrons and holes.<sup>37–39</sup> The polarization response time is quantified as  $R_B C_E$ , where  $R_B$  is the electrical resistance of the electrolyte and  $C_E$  is the EDL capacitance. Because  $R_B$  is proportional to the thickness of the electrolyte, decreasing the thickness will decrease the time constant which corresponds to faster polarization.<sup>41</sup> The thickness of commonly studied polymer electrolytes are in the range of 0.2–1  $\mu\text{m}$ ,<sup>40</sup> which is at least 2 orders of magnitude higher than traditional gate oxides.<sup>40</sup> Thus, the polarization response is slow—on the order of few hundreds of milliseconds to a few seconds for  $\sim 1 \mu\text{m}$  PEO:CsClO<sub>4</sub>.<sup>42–45</sup> Decreasing the electrolyte thickness from 1  $\mu\text{m}$  to 10 nm will decrease the  $R_B C_E$  time constant by  $\sim 100\times$ , making electrolytes potentially more suitable for high-speed applications. However, it is essential to first show whether or not polymer electrolytes scaled to tens of nanometers can induce large carrier densities ( $10^{13}$ – $10^{14} \text{ cm}^{-2}$ ) in semiconductors. Without such high doping densities, speed becomes less relevant.

Although computational approaches have been employed to better understand EDLTs, only a few studies account for the coupled physics between the ion and carrier transport.<sup>46,47</sup> Paletti et al. used finite element modeling to demonstrate an EDL Esaki diode by simulating the voltage-dependent equilibrium ion and carrier density profiles.<sup>48</sup> Fathipour et al. demonstrated the formation of a p–i–n junction and quantified the ion and carrier concentrations near the contact regions.<sup>49</sup> In both studies, the devices had a FET structure but were operated as p–i–n<sup>49</sup> and Esaki<sup>48</sup> diodes by applying a lateral electric field between source and drain. Also, both studies focused on steady-state carrier distributions under a fixed voltage and, as such, used the ion concentration at the electrolyte/semiconductor interface as a fixed charge input to calculate the steady-state carrier density in the channel. Ueda et al. simulated an EDLT by self-consistently coupling ion and carrier transport using finite difference method, and their work

focused on explaining ambipolar behavior in WSe<sub>2</sub> using a gate voltage comparable to the band gap energy.<sup>47</sup>

In this study, we use finite element modeling to simulate the dynamic response of ion and carrier transport in an EDLT to solve for (1) the voltage distributions across the electrolyte and the semiconductor and (2) ion and carrier densities as a function electrolyte thickness. By self-consistently coupling ion and charge transport, a more accurate estimate of FET charge density is achieved compared to assuming an MIM structure for which no potential drops across the metal electrodes. Importantly, the results show that 50 to 65% of the applied potential drops across the semiconductor, leaving 35 to 50% to drop across the two EDLs. This result suggests that higher charge densities can be achieved with larger gate voltages while avoiding electrochemistry. We verify this experimentally by measuring the carrier densities via Hall effect on graphene FETs at gate voltages up to  $\pm 6$  V. In addition, the thickness scalability of solid polymer electrolytes is modeled down to 10 nm in both top- and side-gated geometries, showing that carrier density is independent of thickness—as expected. The results are validated experimentally using a graphene FET with PEO:CsClO<sub>4</sub> thinned to 10 nm. No significant change is observed between the carrier densities using ultrathin and bulk electrolytes, suggesting the possibility of scaling electrolytes to VLSI-relevant thicknesses.

## RESULTS AND DISCUSSION

**Carrier Density at Large ( $\pm 6$  V) Gate Voltages.** To model the voltage distribution across both the electrolyte and semiconductor, the concentration distribution of all charged species (i.e., ions in the electrolyte and carriers in the semiconductor) is calculated self-consistently. Here, a top-gated FET structure (Figures 1a,b) is modeled, where few-layer WSe<sub>2</sub> (thickness = 5 nm and  $E_{\text{gap}} = 1.25$  eV) is gated using a solid electrolyte (dielectric constant  $\epsilon_{\text{PEO}} = 10$  and ion concentration  $n_b = 1000 \text{ mol/m}^3$ ). Note that  $n_b$  and  $\epsilon_{\text{PEO}}$  used for modeling (see the Methods section, Table 1) are chosen to

**Table 1. Electronic and Physical Properties Used for Finite Element Simulations**

| parameter                                 | symbol                    | value                          | ref |

|-------------------------------------------|---------------------------|--------------------------------|-----|

| electron affinity of WSe <sub>2</sub>     | $\chi_{\text{WSe}_2}$     | 3.7 eV                         | 66  |

| band gap                                  | $E_{\text{gap}}$          | 1.25 eV                        | 67  |

| electron mobility                         | $\mu_n$                   | $43 \text{ cm}^2/(\text{V s})$ | 47  |

| hole mobility                             | $\mu_p$                   | $84 \text{ cm}^2/(\text{V s})$ | 47  |

| relative permittivity of WSe <sub>2</sub> | $\epsilon_{\text{WSe}_2}$ | 7.25                           | 68  |

| relative permittivity of electrolyte      | $\epsilon_{\text{PEO}}$   | 10                             | 69  |

| relative permittivity of SiO <sub>2</sub> | $\epsilon_{\text{SiO}_2}$ | 8                              | 70  |

| Stern layer thickness                     | a                         | 0.2 nm                         |     |

| bulk ion concentration                    | $n_b$                     | $1000 \text{ mol/m}^3$         |     |

match experimental values.<sup>41</sup> The modified Poisson–Nernst–Planck (mPNP) equations are solved simultaneously with the drift-diffusion equations to numerically calculate the concentration of ions within the EDL, the distribution of electrons and holes in the semiconductor, and the distribution of electric potential throughout the device geometry (see the Methods section). A Fermi–Dirac distribution of the energy states and the parabolic dispersion relation is used to account for the density of states in the carrier density calculations (i.e., quantum capacitance is accounted for in this model). The

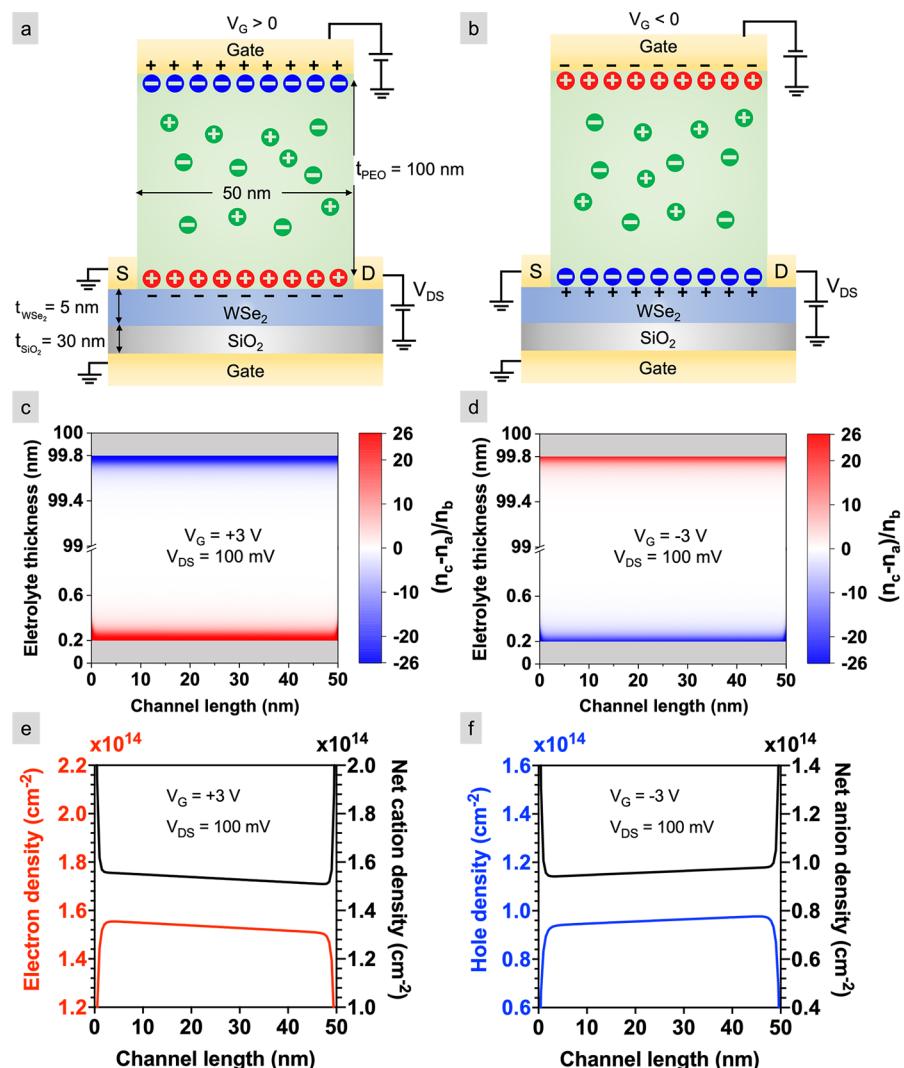

**Figure 2.** Calculations and measurements of electron and hole densities. (a) Charge densities calculated using the mPNP model and the mPNP+drift-diffusion model for WSe<sub>2</sub> and measured by the Hall effect for WSe<sub>2</sub> gated by an ionic liquid<sup>51</sup> and QFEG gated using PEO:CsClO<sub>4</sub>.  $V_{\text{ref}}$  is zero except for the mPNP+drift-diffusion model where it represents the work function difference of  $-0.5 \text{ V}$  between the Au contacts and WSe<sub>2</sub> and Zhang et al.<sup>51</sup> where it equals the threshold voltage of  $-1 \text{ V}$ . The error bars for QFEG represent propagation of error in the measurement of Hall voltage. (b) SEM image of the Hall bar device before electrolyte deposition; the scale bar is  $6 \mu\text{m}$ , and the length and width of the channel are  $35 \mu\text{m}$  and  $8 \mu\text{m}$ , respectively. The side gate is  $5 \mu\text{m}$  wide and located  $20 \mu\text{m}$  from the channel. (c) AFM topology scan of the lateral interface between graphene and SiC. The roughness ( $R_q$ ) is averaged over five  $500 \times 500 \text{ nm}^2$  scans. Note that the SiC etched with oxygen plasma creates SiO<sub>x</sub> which is less dense than SiC; therefore, the etched region is topographically higher than the unetched region.

concentration of ions and carriers at two gate voltages,  $V_G = +3$  and  $-3 \text{ V}$ , are calculated for  $V_D = 100 \text{ mV}$ . Surface plots of the net normalized ion concentration ( $n_c - n_a$ )/ $n_b$  as a function of channel length ( $x$ ) and electrolyte thickness ( $y$ ) for  $V_G = +3$  and  $-3 \text{ V}$  are shown in Figures 1c and 1d, respectively, where  $n_c$ ,  $n_a$ , and  $n_b$  are cation, anion, and bulk ion concentrations, respectively. In the regions less than  $1 \text{ nm}$  from the electrolyte/semiconductor and gate/electrolyte interfaces, the ions accumulate  $\sim 26$  times more than the bulk concentration, creating subnanometer gap capacitors.

In addition to surface plots in Figures 1c,d, the net ion densities and charge carrier densities are shown in Figures 1e,f as a function of channel length. The average electron and hole densities are  $\sim 1.5$  and  $\sim 0.9 \times 10^{14} \text{ cm}^{-2}$  at  $V_G = +3$  and  $-3 \text{ V}$ , respectively, the same order of magnitude ( $10^{13}$ – $10^{14} \text{ cm}^{-2}$ ) as previously reported experimentally using ionic liquids and solid polymer electrolytes.<sup>42,45,47,50</sup> Moving from source to drain, the observed decrease (increase) in the electron (hole) density arises from the lateral electric field caused by a nonzero  $V_{DS}$  ( $100 \text{ mV}$ ). The generation of the carriers in the channel as a result of ion accumulation confirms that the ions in the electrolyte and the carriers in the semiconductor are electrostatically coupled by means of the electric potential. We refer to this as the mPNP+drift-diffusion model. Here, WSe<sub>2</sub> is chosen as a representative 2D semiconductor; however, the model can be extended to other types of semiconductors including other 2D crystals, oxide semiconductors, and organic semiconductors by modifying the

material properties listed in Table 1. We use an ion radius of  $0.2 \text{ nm}$ , which well approximates Cs<sup>+</sup>; carrier densities for additional ionic radii of  $0.08$  and  $0.4 \text{ nm}$  are reported in the Supporting Information, Part 1.

The sheet carrier densities calculated using the mPNP+drift-diffusion model on WSe<sub>2</sub> are compared to experimental measurements via the Hall effect by Zhang et al.<sup>51</sup> on monolayer WSe<sub>2</sub> gated with ionic liquid and by us on quasi-free-standing epitaxial graphene (QFEG)<sup>52,53</sup> gated using PEO:CsClO<sub>4</sub> (Figure 2a). The model is in reasonable agreement with the experimental measurements by Zhang et al. on monolayer WSe<sub>2</sub>. Although it would be straightforward to attribute the difference between the model predictions for WSe<sub>2</sub> and the experimental results on QFEG purely to the difference between the channel materials, we note that sheet carrier densities measured by the Hall effect spanning this entire range ( $10^{12}$ – $10^{14} \text{ cm}^{-2}$ ) have been reported in the literature for both graphene and TMDs<sup>19,20,45,51,54–59</sup> (Supporting Information, Part 2). These data are compiled in Figure S2 and Table S1.

Among all the data, our PEO:CsClO<sub>4</sub>-gated QFEG measurements give the smallest sheet densities. We cannot attribute this to device geometry because the sheet density increases with increasing gate-to-channel size ratio,<sup>60–62</sup> and in our side-gated geometry, this ratio is already greater than one. One possible explanation relates to the  $1 \text{ nm}$  of resist residue that covers the graphene channel from the lithography process, as measured by AFM (Figure 2c). Removing this residue will

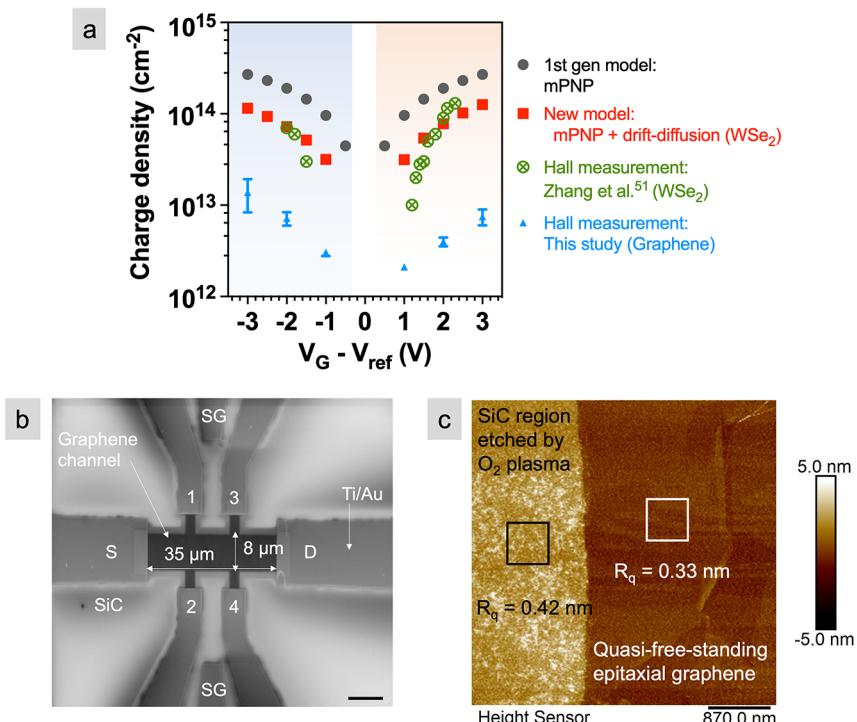

**Figure 3.** Voltage distribution in an EDLT: Voltage drop across (a) a MIM stack using the mPNP model and (b) a metal/electrolyte/semiconductor (MIS) stack using the mPNP+drift-diffusion model, both at  $V_G = +3$  V. For clarity, the potential drop in the electrolyte is shown only in the region where it changes (i.e., nm from the semiconductor and the gate). The equivalent circuits show capacitors in series for the MIM and MIS stacks.  $C_{E1}$  and  $C_{E2}$  are the EDL capacitances.  $C_B$ ,  $C_Q$ , and  $C_{OX}$  are the bulk electrolyte, quantum, and oxide capacitances, respectively. (c)  $\Delta V$  across the EDLs as a function applied gate voltage for mPNP and mPNP+drift-diffusion model. The shaded region represents the voltage dropped across the semiconductor.

increase the gating strength of EDL-gated FETs by 247%, as we showed previously.<sup>63</sup>

The sheet carrier densities calculated using the new model are also compared to other models where the electrolyte is modeled within an MIM structure.<sup>48–50,64,65</sup> In the MIM, only the modified Nernst–Planck and Poisson’s equations are used to calculate the ion density inside the EDL (referred here as mPNP model), which can then be used as a fixed-charge input to calculate the carrier density inside the semiconductor. The MIM approximates the metal/electrolyte/semiconductor stack by assuming that the dense sheet of ions at the electrolyte/semiconductor interface acts like a metal and blocks the field from the semiconductor. However, the mPNP model overestimates the carrier densities by approximately 1 order of magnitude compared to the mPNP+drift-diffusion model at the same applied gate voltage (Figure 2a). The difference can be accounted for by considering the voltage distributions between the mPNP model applied to an MIM structure versus the mPNP+drift-diffusion model applied to the FET structure. As shown in Figure 3a, all the applied gate voltage,  $V_G = +3$  V, drops across the EDLs (1.5 V at the top EDL and 1.5 V at the bottom EDL when the electrode areas are equal, i.e.,  $C_{E1} = C_{E2}$  in Figure 3a) in the MIM configuration as described by the mPNP model. Irrespective of the electrode areas, the total voltage drop across the EDLs will always be equal to the total applied voltage in an MIM configuration.

In contrast, for the mPNP+drift-diffusion model with a semiconductor channel, the total voltage drop across the EDLs is smaller than the total applied voltage (Figure 3b) because part of the applied voltage drops across the generated carriers inside the semiconductor. Recall that quantum capacitance is included by accounting for the DOS in the mPNP+drift-diffusion model, as indicated by  $C_Q$  in the equivalent circuit (Figure 3b). To quantify the difference between the two models, we apply  $V_G$  in the range of  $-3$  to  $+3$  V in 0.5 V intervals and predict the voltage distribution across the entire geometry using both the models. The  $\Delta V$  across the EDLs as a function of  $V_G$  is shown in Figure 3c. For mPNP+drift-diffusion model on WSe<sub>2</sub>, the  $\Delta V$  across the EDLs is  $\sim 50$  to 65% smaller than the applied  $V_G$ , highlighted by the shaded region in Figure 3c. Note that in the mPNP+drift-diffusion model (Figure 3b), the voltage in the bottom region of the

semiconductor reaches  $\sim -0.5$  V because of the built-in potential as a result of the work function difference ( $\Delta\Phi$ ) between the contact metal (Au) and the semiconductor. This means that the overall voltage drop across the EDLs and the semiconductor is 0.5 V more than applied  $V_G = +3$  V. Similarly, for  $V_G = -3$  V, the voltage at the bottom of the semiconductor reaches  $\sim -2.5$  V, thereby making the total potential drop across the EDLs and semiconductor less than the applied  $V_G = -3$  V. Thus, the  $\Delta V$  across the EDLs becomes zero at  $V_G = \sim -0.5$  V in Figure 3c (data in triangles) because of the built-in potential. Also note that the voltage through the back gate oxide goes to zero because the back gate is set to  $V_{BG} = 0$  V.

The extent to which the potential drops in the electrolyte is critical to EDL-gated FETs because it dictates the maximum applied voltage that can be used to modulate the carrier density without inducing electrochemistry. As mentioned in the **Introduction**, there are several reports where the electrolyte gate voltage far exceeds what we know to be the electrochemical window. For example, Heidarloo and co-workers reported EDL gating of WSe<sub>2</sub> FETs with PEO:CsClO<sub>4</sub> using a gate voltage up to  $\pm 5$  V.<sup>36</sup> Shi and co-workers used a  $V_G = 7$  V to gate WS<sub>2</sub> using poly(ethylene glycol) (PEG):KClO<sub>4</sub>.<sup>19</sup> Efetov and Kim et al. gated graphene using PEO:LiClO<sub>4</sub> at gate voltages up to  $\pm 15$  V for  $T < 250$  K.<sup>54</sup> The low temperature was used to kinetically arrest the Li<sup>+</sup> and ClO<sub>4</sub><sup>-</sup> ions in the electrolyte to avoid electrochemical reactions. These studies report electrical characteristics that do not indicate electrochemistry, even though this voltage is large compared to the electrode potential of Li<sup>+</sup> ( $-3.05$  V vs SHE). Our modeling provides insight as to why this seemingly contradictory result can be true: the voltage drop across the electrolyte (i.e., the electrochemically active material) is smaller than the applied voltage. The implication is that it could be possible to create stronger than expected EDLs without inducing electrochemistry because larger applied voltages may not correspond to voltage differences across the electrolyte that are sufficient to induce redox reactions.

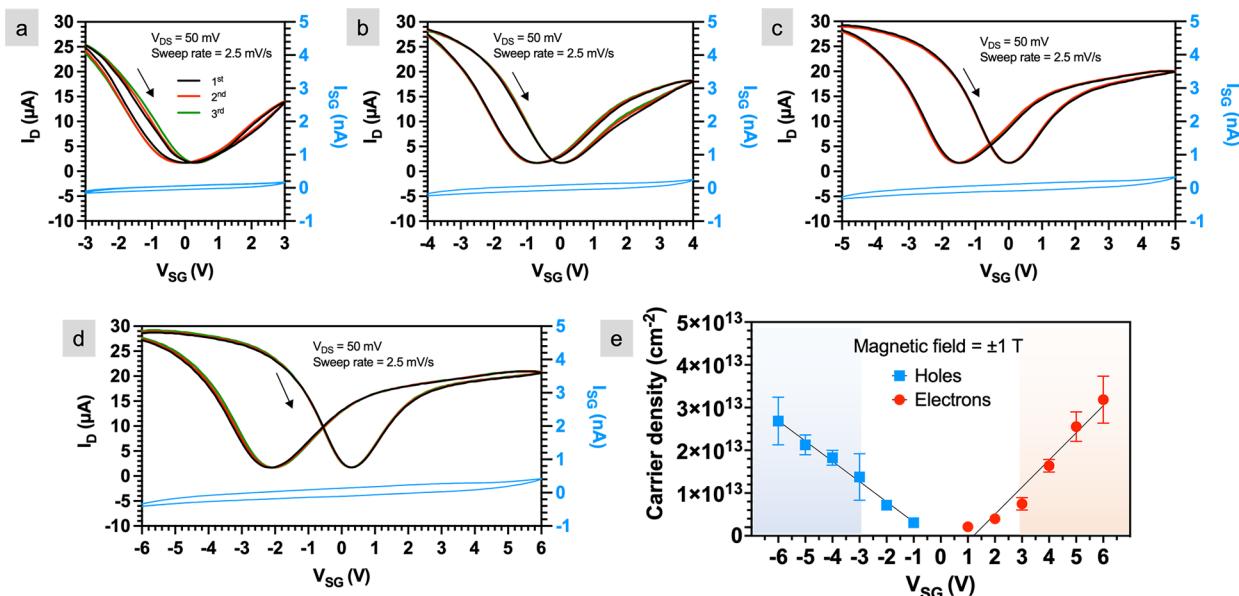

To experimentally check if it is possible to create stronger EDLs without inducing electrochemistry, the drain current ( $I_D$ ) and gate leakage current ( $I_{SG}$ ) were measured on a QFET with  $\sim 1$   $\mu$ m thick PEO:CsClO<sub>4</sub>, while the side gate was

**Figure 4.** Electrical measurements at larger gate voltages. Drain current ( $I_D$ ) and gate leakage current ( $I_{SG}$ ) as a function of side gate voltage ( $V_{SG}$ ) of quasi-free-standing epitaxial graphene (QFEG) gated using bulk ( $\sim 1 \mu\text{m}$  thick) PEO:CsClO<sub>4</sub> in gate voltage ( $V_{SG}$ ) range of (a)  $\pm 3$ , (b)  $\pm 4$ , (c)  $\pm 5$ , and (d)  $\pm 6$  V. (e) Electron and hole densities as a function of  $V_{SG}$  measured via Hall effect measurements on a QFEG Hall bar structure using the same electrolyte. The error bar represents uncertainty as a result of propagation of error in the measurement of Hall voltage.

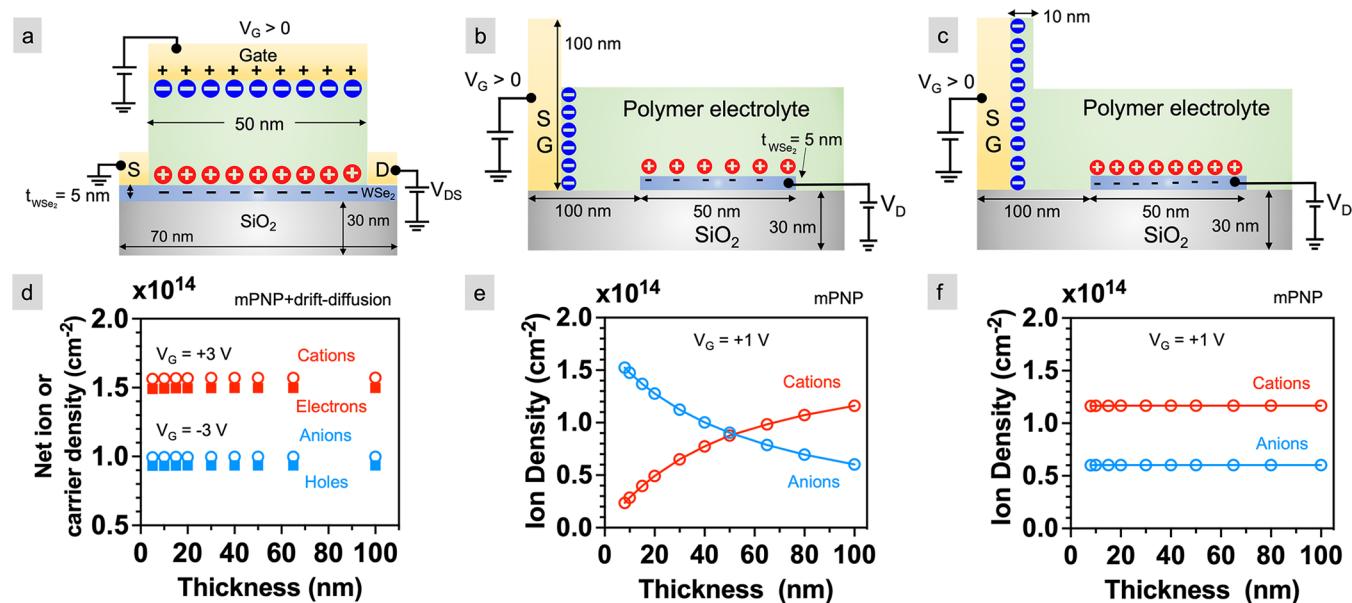

**Figure 5.** Calculated ion and carrier densities as a function of electrolyte thickness. Schematics of (a) top gate, (b) partially covered side gate, and (c) fully covered side gate COMSOL geometries. (d) Net ion density (empty circles) and sheet carrier density (filled squares) for  $V_G = \pm 3$  V and  $V_{DS} = 100$  mV for the model represented in (a). (e, f) Net ion density near the semiconductor/electrolyte interface (red empty circles) and gate/electrolyte interface (blue empty circles) at  $V_G = +1$  V for the models represented in (b, c), respectively. Note that for the side gate geometry, the semiconductor channel is held at a constant potential of 100 mV, corresponding to the maximum voltage applied across the channel in experiments.

increased from  $\pm 3$  to  $\pm 6$  V. When electrochemical reactions occur,  $I_D$  will suddenly increase as  $V_G$  is swept.<sup>13</sup> There can also be side reactions at the Au/electrolyte interface detectable by  $I_{SG}$ , which may not significantly effect the transport properties of the channel.<sup>13</sup> Specifically,  $I_{SG}$  will suddenly increase and slowly decay as the reaction transitions from a kinetically controlled regime to a transport-limited one. Before starting the measurement, a steady-state EDL was created by holding the gate voltage constant for 10 min, which far exceeds the time required to build the EDL.<sup>42,45</sup> As expected, for  $V_{SG}$  in

the range of  $\pm 3$  V (Figure 4a), the starting value of the drain current and the hysteresis are similar for all three sweeps, and  $I_{SG}$  remains below  $\pm 5$  nA. Both observations support electrostatic gating only.

Figures 4b, 4c, and 4d represent the  $I_D$  and  $I_{SG}$  when the gate voltage range is increased to  $\pm 4$ ,  $\pm 5$ , and  $\pm 6$  V, respectively. Similar to  $\pm 3$ , the transfer measurements are identical for all three repeats, and the gate leakage current remains below  $\pm 5$  nA, suggesting primarily electrostatic interactions for  $V_{SG}$  up to  $\pm 6$  V. In addition, no abrupt current changes are observed

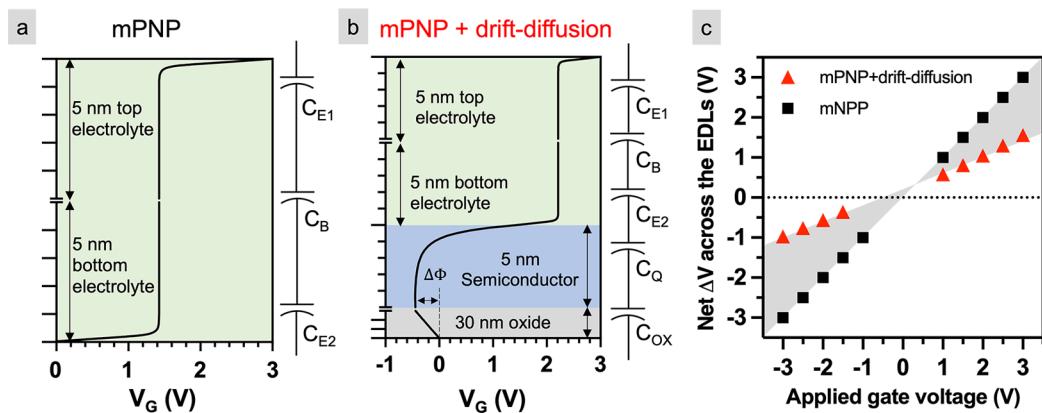

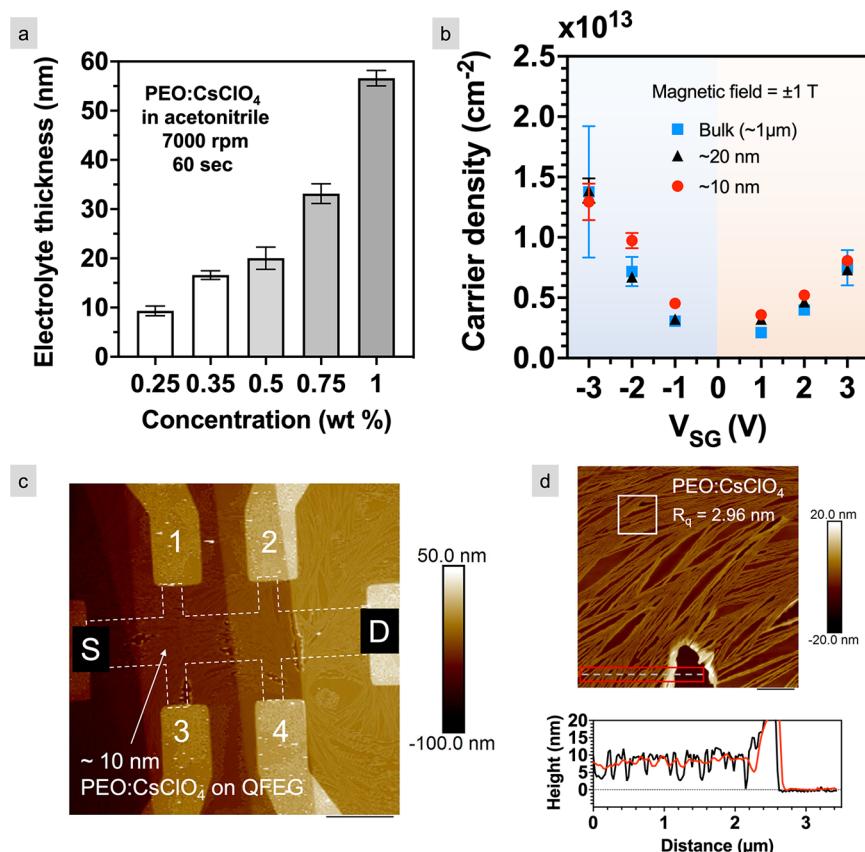

**Figure 6.** Electric-double-layer gating using an ultrathin polymer electrolyte. (a) Electrolyte thickness as a function of wt % of PEO:CsClO<sub>4</sub> in acetonitrile. Error bars represents one standard deviation from the mean height of five measurements. (b) Graphene FET sheet carrier density as a function of gate voltage using ~10, 20, and 1 μm thick PEO:CsClO<sub>4</sub>. The error bar represents uncertainty as a result of propagation of error in the measurement of Hall voltage. (c) AFM topography image of the ~10 nm film on QFEG Hall structure. The dashed lines outline the channel shape underneath PEO:CsClO<sub>4</sub>. The scale bar is 8 μm. (d) Thickness characterization using magnified AFM image on the QFEG channel. A line scan (solid black line) and step height (solid red line) confirm an electrolyte thickness of ~10 nm. The scale bar is 1 μm.

during the 10 min hold time—these data are reported in the [Supporting Information](#), Part 3. This large voltage range for EDL-gated graphene FETs is not unexpected. Bediako and co-workers measured the electrochemical response of graphene sandwiched between h-BN using a Pt pseudoreference electrode and reported that the voltage required to intercalate lithium into graphene/h-BN interface using PEO:LiTFSI was >5 V (−2.75 vs Pt).<sup>13</sup> Thus, on both the epitaxial graphene studied here and graphene on h-BN, these results show an electrochemical onset voltage larger than expected.

Hall effect measurements are made on QFEG to quantify the carrier densities at larger gate voltages. The Hall structures were gated using ~1 μm PEO:CsClO<sub>4</sub>. Under the gate voltage range of V<sub>SG</sub> = ±3 V, which is conventionally considered as the electrochemical limit in the absence of a reference electrode, the measured electron density was ~0.75 × 10<sup>13</sup> cm<sup>-2</sup> and hole density was ~1.4 × 10<sup>13</sup> cm<sup>-2</sup> (Figure 4e). At the largest gate voltages measured (V<sub>SG</sub> = ±6 V), both the electron and hole densities increased to ~3.1 × 10<sup>13</sup> and ~2.7 × 10<sup>13</sup> cm<sup>-2</sup>, respectively. Thus, applying ±6 V enabled carrier density modulation by an additional  $\Delta n_e = 2.3 \times 10^{13}$  cm<sup>-2</sup> (~250%) for electrons and  $\Delta n_h = 1.4 \times 10^{13}$  cm<sup>-2</sup> (~100%) for holes compared to V<sub>SG</sub> = ±3 V. Although mobility is not measured here, we previously reported the mobility of electrons (holes) in epi-graphene gated using PEO:LiClO<sub>4</sub> as 480 (200) cm<sup>2</sup>/(V s) near the Dirac point at room temperature.<sup>45</sup>

#### EDL Gating Using an Ultrathin Polymer Electrolyte.

As mentioned in the [Introduction](#), the thicknesses commonly used for EDL gating are in the range of 0.2–1 μm, which are incompatible with VLSI electronics—both due to physical thickness and speed. To improve the polarization response speed, the scalability of solid polymer electrolyte thickness and its impact on the carrier density are studied using numerical simulations and experimental measurements. EDLTs in three geometries are studied: one top-gated and two side-gated (Figure 5). In the side-gated structure, two arrangements are chosen to represent two possible scenarios of electrolyte films on the gate. In first side-gated geometry, the amount of gate in contact with the electrolyte is equal to the electrolyte thickness as shown in Figure 5b (referred to as partially covered side gate). In the second geometry, the amount of gate in contact with the electrolyte is a constant that is equal to height of the side gate as shown in Figure 5c (referred to as fully covered side gate). The results for the fully covered side gate geometry are validated experimentally by measuring the carrier density using an ultrathin solid polymer electrolyte.

Calculated ion and carrier densities at the electrolyte/semiconductor interface for a top-gated geometry (Figure 5a) for electrolyte thicknesses ranging from 5 to 100 nm at V<sub>G</sub> = ±3 and V<sub>D</sub> = 100 mV are shown in Figure 5d. The accumulated net ion density is essentially constant for all the thicknesses: ~1.55 × 10<sup>14</sup> and ~1 × 10<sup>14</sup> cm<sup>-2</sup> for V<sub>G</sub> = +3 and -3 V, respectively. Similarly, the induced electron and hole

densities in the channel are also independent of the electrolyte thickness.

For the partially and fully covered side gate geometries (Figures 5b,c), only the mPNP equations are solved to numerically calculate the concentration of ions without the drift-diffusion equations. This is a limitation of modeling a side-gated geometry in 2D because the  $V_D$  and  $V_S$  cannot be applied simultaneously. The semiconductor channel is held at a constant potential of 100 mV, corresponding to the maximum voltage applied across the channel in experiments. In the partially covered side gate geometry, the cation density at the electrolyte/semiconductor interface decreases nonlinearly by  $0.93 \times 10^{14} \text{ cm}^{-2}$  as the electrolyte thickness decreases from 100 to 5 nm (Figure 5e). Similarly, the anion density at the gate/electrolyte interface increases by the same amount. The trend in ion density can be explained by the change in the gate-to-channel length ratio. With the decrease in thickness, the gate-to-channel ratio decreases. When the channel is larger than the gate, the amount of charge buildup at the channel must be smaller than at the gate to maintain equivalent capacitance at both.<sup>50</sup> A complementary trend occurs where the channel is smaller than gate. Because the channel length in our model is 50 nm, this dependence of ion density on the gate-to-channel ratio results in favoring ion buildup at the gate at thicknesses  $< 50$  nm and at the channel for thicknesses  $> 50$  nm. This is reflected in Figure 5e as a crossover in cation and anion densities.

In contrast, the fully covered side gate geometry (Figure 5c) demonstrates no such thickness dependence on ion density (Figure 5f). The gate is completely covered in 10 nm wide and 100 nm thick electrolyte as the remainder of the electrolyte varies in height. The constant gate-to-channel ratio means that the ion density is unaffected by thickness—the same as the top-gated geometry. These findings inform that the electrolyte can be made extremely thin ( $< 10$  nm) without significantly compromising the carrier density as long as the gate is coated in electrolyte, which is likely given that the polymer chains are entangled with the neighboring chains creating a continuous thin film.

Experimentally, ultrathin PEO:CsClO<sub>4</sub> films are prepared on SiO<sub>2</sub> by spin-coating solutions of PEO:CsClO<sub>4</sub> in acetonitrile. To adjust the thickness, solution concentrations were varied from 0.25 to 1 wt %, while holding the spin speed fixed at 7000 rpm. The spin coating was performed for 1 min in an Ar-filled glovebox, followed by annealing at 80 °C for 3 min to remove the excess solvent. A step edge is created between the PEO:CsClO<sub>4</sub> and SiO<sub>2</sub> by making a scratch in the film, and the thickness, ranging from 10–55 nm, is measured across the step edge using AFM (Figure 6a).

QFEG Hall structures are spin coated with  $\sim 10$  and 20 nm PEO:CsClO<sub>4</sub>. Surface characterization of the ultrathin electrolyte is performed using AFM. Despite the small thickness and lateral confinement created because of the contact metals, a continuous electrolyte film is observed as shown in Figure 6c. For the thinnest continuous film, the average thickness is  $\sim 10$  nm as measured across a boundary between bare channel and electrolyte in a zoomed-in AFM topography image (Figure 6d). The average surface roughness is  $\sim 3$  nm. Additional surface characterization for continuous 10–55 nm electrolyte films is reported in the Supporting Information, Part 4. Crystalline structures are detected on the  $\sim 10$  and 20 nm electrolyte, which indicates that the electrolyte is semicrystalline. Conversely, electrolytes with thickness  $> 20$  nm are

smoother and have uniform coverage across the entire spin-coated area.

To assess whether scaling the electrolyte thickness to tens of nanometers compromises the ability to induce charge in the channel, the experimentally measured carrier densities using the ultrathin electrolytes are compared with those measured using the bulk electrolyte. The hole (electron) density using the bulk electrolyte is  $\sim 1.4 \times 10^{13} \text{ cm}^{-2}$  ( $\sim 0.8 \times 10^{13} \text{ cm}^{-2}$ ) for  $V_{SG} = -3$  (+3) V (Figure 6b). 10 and 20 nm PEO:CsClO<sub>4</sub> give similar carrier densities to the bulk throughout the entire  $V_{SG}$  range and are comparable with our previous report (electron densities of  $(0.2\text{--}1) \times 10^{13} \text{ cm}^{-2}$  in graphene) using an  $\sim 1 \mu\text{m}$  electrolyte. Although not measured, the carrier density change at higher gate voltages (e.g.,  $\pm 6$  V) using an ultrathin electrolyte is expected to be similar to densities reported in Figure 4d using bulk electrolyte. Note that the large error in the hole density at  $V_{SG} = -3$  V for the bulk electrolyte is a result of a lower drain current ( $I_D = 2 \mu\text{A}$ ) used during the Hall measurements (Supporting Information, Part 4). To correct this issue,  $I_D = 10 \mu\text{A}$  was applied during the Hall measurements for the 10 and 20 nm electrolyte, resulting in smaller error bars. Additional information about the time-dependent Hall voltage measurement for three different electrolyte thicknesses is given in the Supporting Information, Part 5.

Nearly equivalent carrier densities between ultrathin and bulk electrolytes are promising because the  $R_B C_E$  time constants associated with EDL formation and dissipation will decrease with decreasing electrolyte thickness. While this scaling in speed does not apply to the side-gated geometries investigated here because the gate-to-channel distance is independent of electrolyte thickness, it will apply to a top-gate geometry where gate to channel distance is the electrolyte thickness, which would be needed for VLSI.

## CONCLUSIONS

Finite element modeling is used to calculate ion and carrier densities for EDL-gated FETs by self-consistently solving the mPNP equations for ion transport, along with the drift-diffusion equations for transport in the semiconductor that accounts for density of states. The voltage distribution shows that 50 to 65% of the applied potential drops across the semiconductor, leaving 35 to 50% to drop across the two EDLs. This result suggests that higher carrier densities can be achieved at larger voltages without concern for inducing electrochemical reactions. Indeed, transfer measurements show repeatable  $I_D - V_{SG}$  data without any sudden increase in the gate current, and Hall measurements extended to  $\pm 6$  V increase the electron and hole densities while maintaining no signatures of electrochemistry. We expect this result to apply to any ion-gated FET for which the semiconductor is non-permeable to ions.

In addition to measuring over a large voltage window, the solid polymer electrolyte is scaled to 10 nm. As expected, based on the physics of EDL gating, the steady-state capacitance density is independent of electrolyte thickness. Specifically, both top-gated and fully covered side-gated models give constant carrier densities in the thickness range of 5–100 nm. Here, we experimentally extend this ultrathin film exploration to side-gated, 2D crystal FETs. Electrolyte films with thicknesses down to  $\sim 10$  nm are achieved by spin coating PEO:CsClO<sub>4</sub>. Hall measurements confirm that the sheet carrier density remains constant throughout the measured

thickness range (10 nm–1  $\mu\text{m}$ ). The added benefit of scaling is a faster polarization response because of the reduced  $R_{\text{B}}C_{\text{E}}$  time constant, which is critical for VLSI. Both the large voltage window without electrochemistry and the ultrathin electrolyte scaling results are important for achieving strong electrostatic gate control in 2D FETs and demonstrating progress toward VLSI-relevant dielectric thickness and speed.

## METHODS

**Finite Element Modeling.** Finite element modeling was performed using COMSOL Multiphysics ver. 5.5. The ion transport in the electrolyte, the electron and hole transport in the semiconductor, and the potential distribution in the entire geometry were calculated by simultaneously solving the modified Nernst–Planck equation (mNP), the drift-diffusion equations, and Poisson's equation, respectively. The Fermi–Dirac distribution of the energy states and the parabolic dispersion relation for the density of states were assumed in COMSOL when calculating the electron and hole density. Note that the electric potential across the entire device geometry was solved simultaneously to couple the accumulated ions at the electrolyte/semiconductor interface with the carriers in the semiconductor.

The mNP equation (eq 1) is described as

$$\frac{dc_{\pm}}{dt} - \nabla \left( D_{\pm} \nabla c_{\pm} + D_{\pm} \frac{q}{k_{\text{b}}T} z_{\pm} D_{\pm} \nabla V + \gamma \right) = 0 \quad (1)$$

where  $c_{+}$  ( $c_{-}$ ),  $D_{+}$  ( $D_{-}$ ), and  $z_{+}$  ( $z_{-}$ ) are concentrations ( $\text{mol}/\text{m}^3$ ), diffusivities ( $\text{m}^2/\text{s}$ ), and charge numbers of cations (anions) in the electrolyte, respectively. To calculate the ion concentration, the mNP equation was implemented only for the electrolyte region as a coefficient form partial differential equation. The term  $\gamma$  is the contribution from Kilic et al. to account for the size and therefore limit the packing density of the ions. The steric term ( $\gamma$ ) in eq 1 is described as

$$\gamma = \frac{a^3 D_{\pm} c_{\pm} \nabla (c_{+} + c_{-})}{1 - c_{+} a^3 - c_{-} a^3} \quad (2)$$

where  $a$  is the diameter of the ion which is considered to be equal in this study for both the cations and anions.

The continuity equation for electron and hole current was solved where the electron and hole current density are described by the drift-diffusion equations

$$J_n = -q\mu_n n \nabla V + qD_n \nabla n \quad (3a)$$

$$J_p = -q\mu_p p \nabla V - qD_p \nabla p \quad (3b)$$

where  $\mu_n$  ( $\mu_p$ ) denote the mobility ( $\text{m}^2/(\text{V s})$ ) of electrons (holes),  $n$  ( $p$ ) are the electron (hole) concentrations (electrons or holes/ $\text{m}^3$ ), and  $D_n$  ( $D_p$ ) are the electron (hole) diffusivities ( $\text{m}^2/\text{s}$ ) as described by the Einstein relation. The values of the electronic and physical properties of the semiconductor and electrolyte are summarized in Table 1. All the charge transport from the mNP and the drift-diffusion equations was coupled with each other by the Poisson's equations (eq 4) assuming the continuity of electric potential across the electrolyte–semiconductor boundary.

$$\nabla \cdot (-\epsilon \epsilon_0 \nabla V) = \begin{cases} q(c_{+} - c_{-}) & \text{electrolyte} \\ q(p - n) & \text{semiconductor} \end{cases} \quad (4)$$

where  $\epsilon$  and  $q$  denote the relative permittivity and elementary charge, respectively. Equation 1 was solved using the general form PDE in the mathematics module. The current continuity equation and eqs 3a, 3b, and 4 were solved using the semiconductor module.

Metal contacts to the semiconductor were assumed to be purely ohmic. The source contact was grounded at all times whereas the drain and gate contacts were modeled as a boundary with nonzero electric potential. The potentials of the drain and gate contact were linearly increased from 0 to 100 mV and 0 to  $\pm 3$  V, respectively. The potentials were held constant until steady state was reached. It is challenging to estimate the EDL thickness because of the continuous nature of the ion concentration even with the inclusion of the steric term and Stern layer. Therefore, to calculate the EDL ion densities, the net ion density,  $n_c - n_a$ , along a cut line from the center of the electrolyte to the electrolyte/semiconductor interface was integrated using the trapezoidal rule. This approach ensured that all the ions in the EDL are accounted and the contribution from the ions in the charge neutral bulk electrolyte is excluded. Similarly, the majority carrier densities in the semiconductor were integrated from the backgate semiconductor–oxide interface to the electrolyte/semiconductor interface.

**Electrolyte Preparation and Deposition.** The electrolyte PEO:CsClO<sub>4</sub> was prepared by dissolving 80 mg of PEO ( $M_w = 110000$  g/mol, Polymer Standards Service) and 21 mg of CsClO<sub>4</sub> (99.9%, Sigma-Aldrich) in 10 g of anhydrous acetonitrile (Sigma-Aldrich) to make a 1 wt % solution with 20:1 ether oxygen to Cs<sup>+</sup> molar ratio in an Ar-filled glovebox. The oxygen and water levels were maintained at O<sub>2</sub> < 10 and H<sub>2</sub>O < 0.1 ppm. To prepare a bulk (~1  $\mu\text{m}$ ) film, 40  $\mu\text{L}$  of electrolyte solution was drop casted onto a 1  $\times$  1  $\text{cm}^2$  SiC substrate with graphene Hall structures, and the solvent was naturally evaporated for 5 min at room temperature. The sample was then annealed at 80° C for 3 min to remove the remaining solvent and cooled naturally to room temperature before the electrical measurements. To prepare 10 and 20 nm films, the 1 wt % solution was diluted to 0.25 and 0.5 wt %, respectively; 80  $\mu\text{L}$  of the electrolyte solution was spin coated at 7000 rpm for 60 s, and the solvent was naturally evaporated for 30 min at room temperature before performing the electrical measurements.

**Device Fabrication.** Epitaxial graphene (EG) was grown by the sublimation of Si atoms from the Si face of 6H-SiC semi-insulating substrates (II–VI Advanced Materials Inc.) at 1800 °C. A Heidelberg Maskless Aligner MLA 150 was used to fabricate the EG Hall bars on SiC substrates where each of the devices was isolated utilizing nitrogen gas in a ULvac NE 550 etch tool. SEM was performed after completing the isolation layer. To enhance the adhesive strength of the metal on the EG/SiC surface, the contact regions were gently exposed to O<sub>2</sub> plasma (descumming). Then the isolated devices were contacted with Ti (5 nm) and Au (20 nm) followed by another metallization step of Ti (5 nm) and Au (100 nm), which are deposited using an e-beam evaporator (Temescal). The metallization is done in two steps to avoid the electrode peeling off because of the thick metal near graphene during liftoff.

**Hall Carrier Density Measurements.** Hall measurements were conducted in a Lakeshore cryogenic probe station with a vertical field superconducting magnet using a Keysight B1500A semiconductor parameter analyzer. The temperature of the

sample stage was maintained at 300 K under the chamber vacuum of  $\sim 5 \times 10^{-7}$  Torr. During each measurement, the  $V_{SG}$  was applied and held constant for 900 s to allow ions to reach the steady state before starting the measurement. 2  $\mu$ A of current for the bulk electrolyte and 10  $\mu$ A for the 10 and 20 nm electrolyte were applied between the source and drain with the vertical magnetic field of 0 T, and the Hall voltage was monitored for 200 s. The magnetic field was gradually increased to  $+1 \pm 0.01$  T, and the Hall voltage was monitored for 200 s. The same sequence was repeated by reversing the polarity of the magnetic field to  $-1 \pm 0.01$  T. The measurements at 0 T were subtracted from the Hall voltages at  $B = \pm 1$  T to eliminate the effect of the geometric asymmetry. The same measurement was repeated for all the reported  $V_{SG}$  values. The details of Hall measurements are reported in the [Supporting Information](#), Part 5.

## ASSOCIATED CONTENT

### Supporting Information

The Supporting Information is available free of charge at <https://pubs.acs.org/doi/10.1021/acsami.2c13140>.

Impact of ion size on the calculated carrier density; literature comparison of ion-gated carrier densities in 2D materials; time-dependent  $I_D$  and  $I_{SG}$  for  $V_G = \pm 6$  V; details of the Hall measurements; and surface characterization of additional ultrathin electrolyte films ([PDF](#))

## AUTHOR INFORMATION

### Corresponding Author

**Susan K. Fullerton-Shirey** – Department of Chemical and Petroleum Engineering and Department of Electrical and Computer Engineering, University of Pittsburgh, Pittsburgh, Pennsylvania 15260, United States; [orcid.org/0000-0003-2720-0400](https://orcid.org/0000-0003-2720-0400); Email: [fullerton@pitt.edu](mailto:fullerton@pitt.edu)

### Authors

**Shubham Sukumar Awate** – Department of Chemical and Petroleum Engineering, University of Pittsburgh, Pittsburgh, Pennsylvania 15260, United States; [orcid.org/0002-4726-2169](https://orcid.org/0002-4726-2169)

**Brendan Mostek** – Department of Chemical and Petroleum Engineering, University of Pittsburgh, Pittsburgh, Pennsylvania 15260, United States

**Shalini Kumari** – Department of Materials Science and Engineering and Center for 2D and Layered Materials and Center for Atomically Thin Multifunctional Materials, The Pennsylvania State University, University Park, Pennsylvania 16802, United States; [orcid.org/0000-0001-6457-2858](https://orcid.org/0000-0001-6457-2858)

**Chengye Dong** – Two-Dimensional Crystal Consortium, The Pennsylvania State University, University Park, Pennsylvania 16802, United States

**Joshua A. Robinson** – Department of Materials Science and Engineering, Center for 2D and Layered Materials and Center for Atomically Thin Multifunctional Materials, and Two-Dimensional Crystal Consortium, The Pennsylvania State University, University Park, Pennsylvania 16802, United States; [orcid.org/0000-0002-1513-7187](https://orcid.org/0000-0002-1513-7187)

**Ke Xu** – Department of Chemical and Petroleum Engineering, University of Pittsburgh, Pittsburgh, Pennsylvania 15260, United States; School of Physics and Astronomy and Microsystems Engineering, Rochester Institute of Technology, Rochester, New York 14623, United States; School of

Chemistry and Materials Science, Rochester Institute of Technology, Rochester, New York 14623, United States; [orcid.org/0000-0003-2692-1935](https://orcid.org/0000-0003-2692-1935)

Complete contact information is available at: <https://pubs.acs.org/10.1021/acsami.2c13140>

### Author Contributions

Conceptualization, S.K.F.-S., K.X., S.S.A.; modeling, S.S.A., B.M.; device characterization and electrical measurements, S.S.A.; 2D material synthesis and fabrication, C.D., S.K., J.A.R. The manuscript was written through contributions of all authors. All authors have given approval to the final version of the manuscript.

### Notes

The authors declare no competing financial interest.

## ACKNOWLEDGMENTS

This work was supported in part by an Alfred P. Sloan Foundation Research fellowship, NSF DMR-2011839 Penn State MRSEC Center for Nanoscale Science and NSF DMR-1539916 2D Crystal Consortium - Materials Innovation Platform. The authors thank Jierui Liang, Zhongmou Chao, and Huiran Wang at the University of Pittsburgh for helpful discussions.

## REFERENCES

- (1) Chun, H.; Chung, T. D. Iontronics. *Annual Review of Analytical Chemistry* **2015**, *8*, 441–462.

- (2) Bisri, S. Z.; Shimizu, S.; Nakano, M.; Iwasa, Y. Endeavor of Iontronics: From Fundamentals to Applications of Ion-Controlled Electronics. *Adv. Mater.* **2017**, *29*, 1607054.

- (3) Xu, K.; Fullerton-Shirey, S. K. Electric-double-layer-gated transistors based on two-dimensional crystals: Recent approaches and advances. *JPhys. Materials* **2020**, *3*, 032001.

- (4) Kim, S. H.; Hong, K.; Xie, W.; Lee, K. H.; Zhang, S.; Lodge, T. P.; Frisbie, C. D. Electrolyte-Gated Transistors for Organic and Printed Electronics. *Adv. Mater.* **2013**, *25*, 1822–1846.

- (5) Leighton, C.; Birol, T.; Walter, J. What controls electrostatic vs electrochemical response in electrolyte-gated materials? A perspective on critical materials factors. *APL Materials* **2022**, *10*, 040901.

- (6) Khodagholy, D.; Rivnay, J.; Sessolo, M.; Gurfinkel, M.; Leleux, P.; Jimison, L. H.; Stavrinidou, E.; Herve, T.; Sanaur, S.; Owens, R. M.; Malliaras, G. G. High transconductance organic electrochemical transistors. *Nat. Commun.* **2013**, *4*, 2133.

- (7) Rivnay, J.; Inal, S.; Salleo, A.; Owens, R. M.; Berggren, M.; Malliaras, G. G. Organic electrochemical transistors. *Nat. Rev. Mater.* **2018**, *3*, 17086.

- (8) Chao, Z.; Sezginel, K. B.; Xu, K.; Crouch, G. M.; Gray, A. E.; Wilmer, C. E.; Bohn, P. W.; Go, D. B.; Fullerton-Shirey, S. K. Silver Nanofilament Formation Dynamics in a Polymer-Ionic Liquid Thin Film by Direct Write. *Adv. Funct. Mater.* **2020**, *30*, 1907950.

- (9) Xu, X.; Lv, H.; Liu, H.; Gong, T.; Wang, G.; Zhang, M.; Li, Y.; Liu, Q.; Long, S.; Liu, M. Superior retention of low-resistance state in conductive bridge random access memory with single filament formation. *IEEE Electron Device Lett.* **2015**, *36*, 129–131.

- (10) Melianas, A.; Quill, T. J.; LeCroy, G.; Tuchman, Y.; Loo, H. V.; Keene, S. T.; Giovannitti, A.; Lee, H. R.; Maria, I. P.; McCulloch, I.; Salleo, A. Temperature-resilient solid-state organic artificial synapses for neuromorphic computing. *Sci. Adv.* **2020**, *6*, eabb2958.

- (11) Li, Y.; Yan, H.; Xu, B.; Zhen, L.; Xu, C. Y. Electrochemical Intercalation in Atomically Thin van der Waals Materials for Structural Phase Transition and Device Applications. *Adv. Mater.* **2021**, *33*, 2000581.

- (12) Fuller, E. J.; Gabaly, F. E.; Léonard, F.; Agarwal, S.; Plimpton, S. J.; Jacobs-Gedrim, R. B.; James, C. D.; Marinella, M. J.; Talin, A. A.

Li-Ion Synaptic Transistor for Low Power Analog Computing. *Adv. Mater.* **2017**, *29*, 1604310.

(13) Bediako, D. K.; Rezaee, M.; Yoo, H.; Larson, D. T.; Zhao, S. Y.; Taniguchi, T.; Watanabe, K.; Brower-Thomas, T. L.; Kaxiras, E.; Kim, P. Heterointerface effects in the electrointercalation of van der Waals heterostructures. *Nature* **2018**, *558*, 425–429.

(14) Xiong, F.; Yalon, E.; McClellan, C. J.; Zhang, J.; Aslan, O. B.; Sood, A.; Sun, J.; Andolina, C. M.; Saidi, W. A.; Goodson, K. E.; Heinz, T. F.; Cui, Y.; Pop, E. Tuning electrical and interfacial thermal properties of bilayer MoS<sub>2</sub> via electrochemical intercalation. *Nanotechnology* **2021**, *32*, 265202.

(15) Zhang, J.; Yang, A.; Wu, X.; van de Groep, J.; Tang, P.; Li, S.; Liu, B.; Shi, F.; Wan, J.; Li, Q.; Sun, Y.; Lu, Z.; Zheng, X.; Zhou, G.; Wu, C. L.; Zhang, S. C.; Brongersma, M. L.; Li, J.; Cui, Y. Reversible and selective ion intercalation through the top surface of few-layer MoS<sub>2</sub>. *Nat. Commun.* **2018**, *9*, 5289.

(16) Zhu, J.; Yang, Y.; Jia, R.; Liang, Z.; Zhu, W.; Rehman, Z. U.; Bao, L.; Zhang, X.; Cai, Y.; Song, L.; Huang, R. Ion Gated Synaptic Transistors Based on 2D van der Waals Crystals with Tunable Diffusive Dynamics. *Adv. Mater.* **2018**, *30*, 1800195.

(17) Yadav, N.; Mishra, K.; Hashmi, S. A. Optimization of porous polymer electrolyte for quasi-solid-state electrical double layer supercapacitor. *Electrochim. Acta* **2017**, *235*, 570–582.

(18) Pu, J.; Yomogida, Y.; Liu, K. K.; Li, L. J.; Iwasa, Y.; Takenobu, T. Highly flexible MoS<sub>2</sub> thin-film transistors with ion gel dielectrics. *Nano Lett.* **2012**, *12*, 4013–4017.

(19) Shi, W.; Ye, J.; Zhang, Y.; Suzuki, R.; Yoshida, M.; Miyazaki, J.; Inoue, N.; Saito, Y.; Iwasa, Y. Superconductivity Series in Transition Metal Dichalcogenides by Ionic Gating. *Sci. Rep.* **2015**, *5*, 12534.

(20) Piatti, E.; De Fazio, D.; Daghero, D.; Tamalampudi, S. R.; Yoon, D.; Ferrari, A. C.; Gonnelli, R. S. Multi-Valley Superconductivity in Ion-Gated MoS<sub>2</sub> Layers. *Nano Lett.* **2018**, *18*, 4821–4830.

(21) Cha, S.; Noh, M.; Kim, J.; Son, J.; Bae, H.; Lee, D.; Kim, H.; Lee, J.; Shin, H. S.; Sim, S.; Yang, S.; Lee, S.; Shim, W.; Lee, C. H.; Jo, M. H.; Kim, J. S.; Kim, D.; Choi, H. Generation, transport and detection of valley-locked spin photocurrent in WSe<sub>2</sub>–graphene–Bi<sub>2</sub>Se<sub>3</sub> heterostructures. *Nat. Nanotechnol.* **2018**, *13*, 910–914.

(22) Rodrigo, D.; Limaj, O.; Janner, D.; Etezadi, D.; García De Abajo, F. J.; Pruneri, V.; Altug, H. Mid-infrared plasmonic biosensing with graphene. *Science* **2015**, *349*, 165–168.

(23) Liu, X.; Kang, J. H.; Yuan, H.; Park, J.; Kim, S. J.; Cui, Y.; Hwang, H. Y.; Brongersma, M. L. Electrical tuning of a quantum plasmonic resonance. *Nat. Nanotechnol.* **2017**, *12*, 866–870.

(24) Zou, X.; Fang, G.; Yuan, L.; Tong, X.; Zhao, X. A comparative study of amorphous InGaZnO thin-film transistors with HfO<sub>x</sub>Ny and HfO<sub>2</sub> gate dielectrics. *Semicond. Sci. Technol.* **2010**, *25*, 055006.

(25) İkraim, F. A.; Beck, R. B.; Jakubowski, A. Modeling of SOI-MOS capacitors C-V behavior: Partially- and fully-depleted cases. *IEEE Trans. Electron Devices* **1998**, *45*, 1026–1032.

(26) Vasileska, D.; Schroder, D. K.; Ferry, D. K. Scaled silicon MOSFET's: Degradation of the total gate capacitance. *IEEE Trans. Electron Devices* **1997**, *44*, 584–587.

(27) Chen, C. F.; Park, C. H.; Boudouris, B. W.; Horng, J.; Geng, B.; Girit, C.; Zettl, A.; Crommie, M. F.; Segalman, R. A.; Louie, S. G.; Wang, F. Controlling inelastic light scattering quantum pathways in graphene. *Nature* **2011**, *471*, 617–620.

(28) Sun, Z.; Xu, K.; Liu, C.; Beaumariage, J.; Liang, J.; Fullerton-Shirey, S. K.; Shi, Z. Y.; Wu, J.; Snoke, D. Photoluminescence Switching Effect in a Two-Dimensional Atomic Crystal. *ACS Nano* **2021**, *15*, 19439–19445.

(29) Zhao, M.; Li, J.; Sebek, M.; Yang, L.; Liu, Y. J.; Bosman, M.; Wang, Q.; Zheng, X.; Lu, J.; Teng, J. Electrostatically Tunable Near-Infrared Plasmonic Resonances in Solution-Processed Atomically Thin NbSe<sub>2</sub>. *Adv. Mater.* **2021**, *33*, 2101950.

(30) Dhoot, A. S.; Yuen, J. D.; Heeney, M.; McCulloch, I.; Moses, D.; Heeger, A. J. Beyond the metal-insulator transition in polymer electrolyte gated polymer field-effect transistors. *Proc. Natl. Acad. Sci. U. S. A.* **2006**, *103*, 11834–11837.

(31) Wu, C. L.; Yuan, H.; Li, Y.; Gong, Y.; Hwang, H. Y.; Cui, Y. Gate-Induced Metal-Insulator Transition in MoS<sub>2</sub> by Solid Superionic Conductor LaF<sub>3</sub>. *Nano Lett.* **2018**, *18*, 2387–2392.

(32) Huang, W.; Chen, J.; Wang, G.; Yao, Y.; Zhuang, X.; Pankow, R. M.; Cheng, Y.; Marks, T. J.; Facchetti, A. Dielectric materials for electrolyte gated transistor applications. *J. Mater. Chem. C* **2021**, *9*, 9348–9376.

(33) Chu, L.; Schmidt, H.; Pu, J.; Wang, S.; Özylmaz, B.; Takenobu, T.; Eda, G. Charge transport in ion-gated mono-, bi-, and trilayer MoS<sub>2</sub> field effect transistors. *Sci. Rep.* **2014**, *4*, 7293.

(34) Wang, D.; Zhao, S.; Yin, R.; Li, L.; Lou, Z.; Shen, G. Recent advanced applications of ion-gel in ionic-gated transistor. *npj Flexible Electronics* **2021**, *5*, 13.

(35) Lee, D.; Cho, K. G.; Seol, K. H.; Lee, S.; Choi, S. H.; Lee, K. H. Low voltage, high gain electrolyte-gated complementary inverters based on transfer-printed block copolymer ion gels. *Org. Electron.* **2019**, *71*, 266–271.

(36) Heidarloo, M. A.; Paletti, P.; Jariwala, B.; Robinson, J. A.; Fullerton-Shirey, S. K.; Seabaugh, A. C. Batch-Fabricated WSe<sub>2</sub>-on-Sapphire Field-Effect Transistors Grown by Chemical Vapor Deposition. *IEEE Trans. Electron Devices* **2020**, *67*, 1839–1844.

(37) Fullerton-Shirey, S. K.; Maranas, J. K. Effect of LiClO<sub>4</sub> on the structure and mobility of PEO-based solid polymer electrolytes. *Macromolecules* **2009**, *42*, 2142–2156.

(38) Cheng, L.; Liu, Y. What Limits the Intrinsic Mobility of Electrons and Holes in Two Dimensional Metal Dichalcogenides? *J. Am. Chem. Soc.* **2018**, *140*, 17895–17900.

(39) Sangwan, V. K.; Hersam, M. C. Electronic Transport in Two-Dimensional Materials. *Annu. Rev. Phys. Chem.* **2018**, *69*, 299–325.

(40) Lee, K. H.; Zhang, S.; Lodge, T. P.; Frisbie, C. D. Electrical impedance of spin-coatable ion gel films. *J. Phys. Chem. B* **2011**, *115*, 3315–3321.

(41) Gonzalez-Serrano, K. A.; Seabaugh, A. C. Electrical Properties of 6 to 19 nm Thick Polyethylene Oxide Capacitors for Ion/Electron Functional Devices. *J. Electron. Mater.* **2021**, *50*, 2956–2963.

(42) Xu, K.; Islam, M. M.; Guzman, D.; Seabaugh, A. C.; Strachan, A.; Fullerton-Shirey, S. K. Pulse Dynamics of Electric Double Layer Formation on All-Solid-State Graphene Field-Effect Transistors. *ACS Appl. Mater. Interfaces* **2018**, *10*, 43166–43176.

(43) Feng, X.; Scholz, A.; Tahoori, M. B.; Aghassi-Hagmann, J. An Inkjet-Printed Full-Wave Rectifier for Low-Voltage Operation Using Electrolyte-Gated Indium-Oxide Thin-Film Transistors. *IEEE Trans. Electron Devices* **2020**, *67*, 4918–4923.

(44) Cadilha Marques, G.; Garlapati, S. K.; Dehm, S.; Dasgupta, S.; Hahn, H.; Tahoori, M.; Aghassi-Hagmann, J. Digital power and performance analysis of inkjet printed ring oscillators based on electrolyte-gated oxide electronics. *Appl. Phys. Lett.* **2017**, *111*, 102103.

(45) Li, H. M.; Xu, K.; Bourdon, B.; Lu, H.; Lin, Y. C.; Robinson, J. A.; Seabaugh, A. C.; Fullerton-Shirey, S. K. Electric Double Layer Dynamics in Poly(ethylene oxide) LiClO<sub>4</sub> on Graphene Transistors. *J. Phys. Chem. C* **2017**, *121*, 16996–17004.

(46) Zhao, W.; Bi, S.; Balke, N.; Rack, P. D.; Ward, T. Z.; Kalinin, S. V.; Dai, S.; Feng, G. Understanding Electric Double-Layer Gating Based on Ionic Liquids: From Nanoscale to Macroscale. *ACS Appl. Mater. Interfaces* **2018**, *10*, 43211–43218.

(47) Ueda, A.; Zhang, Y.; Sano, N.; Imamura, H.; Iwasa, Y. Ambipolar device simulation based on the drift-diffusion model in ion-gated transition metal dichalcogenide transistors. *npj Computational Materials* **2020**, *6*, 24.

(48) Paletti, P.; Yue, R.; Hinkle, C.; Fullerton-Shirey, S. K.; Seabaugh, A. Two-dimensional electric-double-layer Esaki diode. *npj 2D Mater. Appl.* **2019**, *3*, 19.

(49) Fathipour, S.; Paletti, P.; Fullerton-Shirey, S. K.; Seabaugh, A. C. Electric-double-layer p–i–n junctions in WSe<sub>2</sub>. *Sci. Rep.* **2020**, *10*, 12890.

(50) Woepel, A.; Xu, K.; Kozhakhmetov, A.; Awate, S.; Robinson, J. A.; Fullerton-Shirey, S. K. Single- versus Dual-Ion Conductors for Electric Double Layer Gating: Finite Element Modeling and Hall-

Effect Measurements. *ACS Appl. Mater. Interfaces* **2020**, *12*, 40850–40858.

(51) Zhang, H.; Berthod, C.; Berger, H.; Giamarchi, T.; Morpurgo, A. F. Band Filling and Cross Quantum Capacitance in Ion-Gated Semiconducting Transition Metal Dichalcogenide Monolayers. *Nano Lett.* **2019**, *19*, 8836–8845.

(52) Briggs, N.; Gebeyehu, Z. M.; Vera, A.; Zhao, T.; Wang, K.; De La Fuente Duran, A.; Bersch, B.; Bowen, T.; Knappenberger, K. L.; Robinson, J. A. Epitaxial graphene/silicon carbide intercalation: A minireview on graphene modulation and unique 2D materials. *Nanoscale* **2019**, *11*, 15440–15447.

(53) Subramanian, S.; Campbell, Q. T.; Moser, S. K.; Kiemle, J.; Zimmerman, P.; Seifert, P.; Sigger, F.; Sharma, D.; Al-Sadeg, H.; Labella, M.; Waters, D.; Feenstra, R. M.; Koch, R. J.; Jozwiak, C.; Bostwick, A.; Rotenberg, E.; Dabo, I.; Holleitner, A. W.; Beechem, T. E.; Wurstbauer, U.; Robinson, J. A. Photophysics and Electronic Structure of Lateral Graphene/MoS<sub>2</sub> and Metal/MoS<sub>2</sub> Junctions. *ACS Nano* **2020**, *14*, 16663–16671.

(54) Efetov, D. K.; Kim, P. Controlling electron-phonon interactions in graphene at ultrahigh carrier densities. *Phys. Rev. Lett.* **2010**, *105*, 256805.

(55) Ye, J.; Craciun, M. F.; Koshino, M.; Russo, S.; Inoue, S.; Yuan, H.; Shimotani, H.; Morpurgo, A. F.; Iwasa, Y. Accessing the transport properties of graphene and its multilayers at high carrier density. *Proc. Natl. Acad. Sci. U. S. A.* **2011**, *108*, 13002–13006.

(56) Saito, Y.; Nakamura, Y.; Bahramy, M. S.; Kohama, Y.; Ye, J.; Kasahara, Y.; Nakagawa, Y.; Onga, M.; Tokunaga, M.; Nojima, T.; Yanase, Y.; Iwasa, Y. Superconductivity protected by spin-valley locking in ion-gated MoS<sub>2</sub>. *Nat. Phys.* **2016**, *12*, 144–149.

(57) Zheliuk, O.; Lu, J. M.; Chen, Q. H.; Yumin, A. A.; Golightly, S.; Ye, J. T. Josephson coupled Ising pairing induced in suspended MoS<sub>2</sub> bilayers by double-side ionic gating. *Nat. Nanotechnol.* **2019**, *14*, 1123–1128.

(58) Xu, H.; Fathipour, S.; Kinder, E. W.; Seabaugh, A. C.; Fullerton-Shirey, S. K. Reconfigurable ion gating of 2H-MoTe<sub>2</sub> field-effect transistors using poly(ethylene oxide)-CsClO<sub>4</sub> solid polymer electrolyte. *ACS Nano* **2015**, *9*, 4900–4910.

(59) Allain, A.; Kis, A. Electron and hole mobilities in single-layer WSe<sub>2</sub>. *ACS Nano* **2014**, *8*, 7180–7185.

(60) Wong, A. T.; Noh, J. H.; Pudasaini, P. R.; Wolf, B.; Balke, N.; Herklotz, A.; Sharma, Y.; Haglund, A. V.; Dai, S.; Mandrus, D.; Rack, P. D.; Ward, T. Z. Impact of gate geometry on ionic liquid gated ionotronic systems. *APL Materials* **2017**, *5*, 042501.

(61) Ren, X.; Wang, Y.; Xie, Z.; Xue, F.; Leighton, C.; Frisbie, C. D. Gate-Tuned Insulator-Metal Transition in Electrolyte-Gated Transistors Based on Tellurene. *Nano Lett.* **2019**, *19*, 4738–4744.

(62) Xu, K.; Liang, J.; Woepel, A.; Bostian, M. E.; Ding, H.; Chao, Z.; McKone, J. R.; Beckman, E. J.; Fullerton-Shirey, S. K. Electric Double-Layer Gating of Two-Dimensional Field-Effect Transistors Using a Single-Ion Conductor. *ACS Appl. Mater. Interfaces* **2019**, *11*, 35879–35887.

(63) Liang, J.; Xu, K.; Toncini, B.; Bersch, B.; Jariwala, B.; Lin, Y. C.; Robinson, J.; Fullerton-Shirey, S. K. Impact of Post-Lithography Polymer Residue on the Electrical Characteristics of MoS<sub>2</sub> and WSe<sub>2</sub> Field Effect Transistors. *Advanced Materials Interfaces* **2019**, *6*, 1801321.

(64) Szymanski, M. Z.; Tu, D.; Forchheimer, R. 2-D Drift-Diffusion Simulation of Organic Electrochemical Transistors. *IEEE Trans. Electron Devices* **2017**, *64*, 5114–5120.

(65) Nikolaev, A.; Gracheva, M. E. Poisson–Nernst–Planck model for an ionic transistor based on a semiconductor membrane. *Journal of Computational Electronics* **2014**, *13*, 818–825.

(66) Xiao, J.; Zhang, Y.; Chen, H.; Xu, N.; Deng, S. Enhanced Performance of a Monolayer MoS<sub>2</sub>/WSe<sub>2</sub> Heterojunction as a Photoelectrochemical Cathode. *Nano-Micro Letters* **2018**, *10*, 60.

(67) Khan, I.; Marfoua, B.; Hong, J. Electric field induced giant valley polarization in two dimensional ferromagnetic WSe<sub>2</sub>/CrSnSe<sub>3</sub> heterostructure. *npj 2D Mater. Appl.* **2021**, *5*, 10.

(68) Ghosh, R. K.; Mahapatra, S. Monolayer transition metal dichalcogenide channel-based tunnel transistor. *IEEE Journal of the Electron Devices Society* **2013**, *1*, 175–180.

(69) Das, S.; Ghosh, A. Ionic conductivity and dielectric permittivity of PEO-LiClO<sub>4</sub> solid polymer electrolyte plasticized with propylene carbonate. *AIP Adv.* **2015**, *5*, 027125.

(70) Niles, D. W.; Stout, J.; Christensen, R.; Rodgers, R. Permittivity of SiO<sub>2</sub> for estimating capacitive delays in focused ion beam circuit edit. *Journal of Vacuum Science & Technology B, Nanotechnology and Microelectronics: Materials, Processing, Measurement, and Phenomena* **2015**, *33*, 012203.

## □ Recommended by ACS

### Tuning Threshold Voltage of Electrolyte-Gated Transistors by Binary Ion Doping

Kyung Gook Cho, Keun Hyung Lee, et al.

OCTOBER 27, 2022

ACS APPLIED MATERIALS & INTERFACES

READ ▶

### Layer-by-Layer Assembly Monitored by PEDOT-Polyamine-Based Organic Electrochemical Transistors

Gonzalo Eduardo Fenoy, Waldemar Alejandro Marmisollé, et al.

NOVEMBER 18, 2022

ACS APPLIED ELECTRONIC MATERIALS

READ ▶

### High Performance, Flexible, and Thermally Stable All-Solid-State Organic Electrochemical Transistor Based on Thermoplastic Polyurethane Ion Gel

Kunqi Hou, Wei Lin Leong, et al.

APRIL 07, 2023

ACS APPLIED ELECTRONIC MATERIALS

READ ▶

### 3 nm Channel MoS<sub>2</sub> Transistors by Electromigration of Metal Interconnection

Hongfeng Wan, Jian Ru Gong, et al.

JANUARY 06, 2023

ACS APPLIED ELECTRONIC MATERIALS

READ ▶

Get More Suggestions >